AS4C64M16D3A-12BCNTR 数据手册

AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Revision History

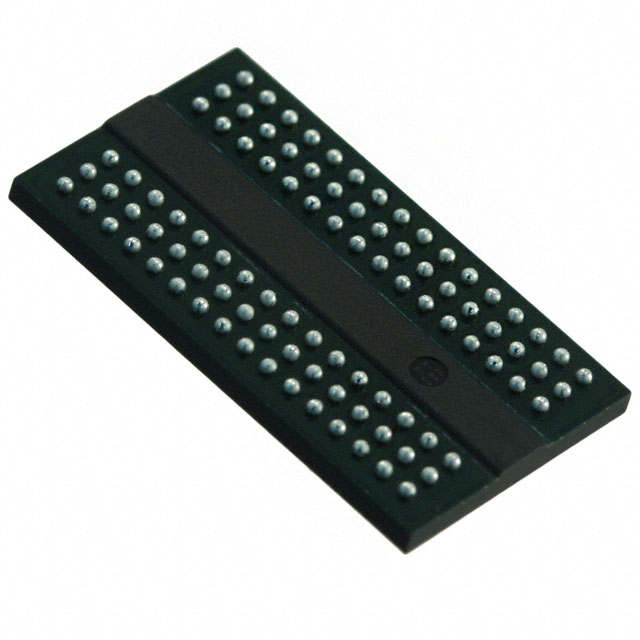

AS4C64M16D3A-12BCN/AS4C64M16D3A-12BIN 96 ball FBGA PACKAGE

Revision

Rev 1.0

Details

Preliminary datasheet

Date

Aug. 2016

Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070 TEL: (650) 610-6800 FAX: (650) 620-9211

Alliance Memory Inc. reserves the right to change products or specification without notice

Confidential

- 1/86 -

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Features

Overview

• JEDEC Standard Compliant

• Power supplies: VDD & VDDQ = +1.5V ± 0.075V

• Operating temperature:

Commercial: 0°C to 95°C (TC)

Industrial :-40°C to 95°C (TC)

• Supports JEDEC clock jitter specification

• Fully synchronous operation

• Fast clock rate: 800MHz

• Differential Clock, CK & CK#

• Bidirectional differential data strobe

- DQS & DQS#

• 8 internal banks for concurrent operation

• 8n-bit prefetch architecture

• Pipelined internal architecture

• Precharge & active power down

• Programmable Mode & Extended Mode registers

• Additive Latency (AL): 0, CL-1, CL-2

• Programmable Burst lengths: 4, 8

• Burst type: Sequential / Interleave

• Output Driver Impedance Control

• 8192 refresh cycles / 64ms

- Average refresh period

7.8μs @ -40℃ ≦TC≦ +85℃

3.9μs @ +85℃ <TC≦ +95℃

The 1Gb Double-Data-Rate-3 DRAMs is double data

rate architecture to achieve high-speed operation. It is

internally configured as an eight bank DRAM.

The 1Gb chip is organized as 8Mbit x 16 I/Os x 8

bank devices. These synchronous devices achieve

high speed double-data-rate transfer rates of up to

1600 Mb/sec/pin for general applications.

The chip is designed to comply with all key DDR3

DRAM key features and all of the control and address

inputs are synchronized with a pair of externally

supplied differential clocks. Inputs are latched at the

cross point of differential clocks (CK rising and CK#

falling). All I/Os are synchronized with differential DQS

pair in a source synchronous fashion.

These devices operate with a single 1.5V ± 0.075V

power supply and are available in BGA packages.

• Write Leveling

• ZQ Calibration

• Dynamic ODT (Rtt_Nom & Rtt_WR)

• RoHS compliant

• Auto Refresh and Self Refresh

• 96-ball 8 x 13 x 1.0mm FBGA package

- Pb and Halogen Free

Table 1. Ordering Information

Product part No

Org

AS4C64M16D3A-12BCN

64M x 16

AS4C64M16D3A-12BIN

64M x 16

Max Clock (MHz)

Package

Commercial 0°C to 95°C

800

96-ball FBGA

Industrial -40°C to 95°C

800

96-ball FBGA

Temperature

Table 2. Speed Grade Information

Confidential

Speed Grade

Clock Frequency

CAS Latency

tRCD (ns)

tRP (ns)

DDR3-1600

800 MHz

11

13.75

13.75

- 2/86 -

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Figure 1. Ball Assignment (FBGA Top View)

1

2

3

7

8

9

A

VDDQ

DQ13

DQ15

DQ12

VDDQ

VSS

B

VSSQ

VDD

VSS

UDQS#.

DQ14

VSSQ

C

VDDQ

DQ11

DQ9

UDQS

DQ10

VDDQ

D

VSSQ

VDDQ

UDM

DQ8

VSSQ

VDD

E

VSS

VSSQ

DQ0

LDM

VSSQ

VDDQ

F

VDDQ

DQ2

LDQS

DQ1

DQ3

VSSQ

G

VSSQ

DQ6

LDQS#

VDD

VSS

VSSQ

H

VREFDQ

VDDQ

DQ4

DQ7

DQ5

VDDQ

J

NC

VSS

RAS#

CK

VSS

NC

K

ODT

VDD

CAS#

CK#

VDD

CKE

L

NC

CS#

WE#

A10/AP

ZQ

NC

M

VSS

BA0

BA2

NC

VREFCA

VSS

N

VDD

A3

A0

A12/BC#

BA1

VDD

P

VSS

A5

A2

A1

A4

VSS

R

VDD

A7

A9

A11

A6

VDD

T

VSS

RESET#

NC

NC

A8

VSS

Confidential

- 3/86 -

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Figure 2. Block Diagram

CK

CKE

Row

Decoder

DLL

CLOCK

BUFFER

CK#

8M x 16

CELL ARRAY

(BANK #0)

Column Decoder

CS#

RAS#

CAS#

WE#

8M x 16

CELL ARRAY

(BANK #1)

Column Decoder

Row

Decoder

COMMAND

DECODER

CONTROL

SIGNAL

GENERATOR

Row

Decoder

RESET#

8M x 16

CELL ARRAY

(BANK #2)

Column Decoder

COLUMN

COUNTER

A12/BC#

Row

Decoder

A10/AP

MODE

REGISTER

8M x 16

CELL ARRAY

(BANK #3)

Column Decoder

A0

Row

Decoder

~

ADDRESS

BUFFER

A9

A11

A12

BA0

BA1

BA2

8M x 16

CELL ARRAY

(BANK #4)

REFRESH

COUNTER

ZQ

CAL

ZQCL

ZQCS

Row

Decoder

Column Decoder

8M x 16

CELL ARRAY

(BANK #5)

Column Decoder

RZQ

LDQS

LDQS#

UDQS

UDQS#

Row

Decoder

VSSQ

DATA

STROBE

BUFFER

8M x 16

CELL ARRAY

(BANK #6)

Column Decoder

DQ

Buffer

DQ0

Row

Decoder

~

DQ15

8M x 16

CELL ARRAY

(BANK #7)

Column Decoder

ODT

Confidential

- 4/86 -

LDM

UDM

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Figure 3. State Diagram

This simplified State Diagram is intended to provide an overview of the possible state transitions and the

commands to control them. In particular, situations involving more than one bank, the enabling or disabling of on-die

termination, and some other events are not captured in full detail

Power

On

Reset

Procedure

MRS,MPR,

Write

Leveling

Initialization

from any

RESET

state

ZQCL

ZQ

Calibration

MRS

ZQCL,ZQCS

Idle

PD

Active

Power

Down

E

X

PD

PRE = Precharge

Precharge

Power

Down

Activating

PREA = Precharge All

PD

X

MRS = Mode Register Set

PD

E

REF = Refresh

RESET = Start RESET Procedure

Bank

Activating

Read = RD, RDS4, RDS8

Read A = RDA, RDAS4, RDAS8

ITE

READ

WR

WRITE

TE

RI

Write A = WRA, WRAS4, WRAS8

RE

AD

A

W

Write = WR, WRS4, WRS8

Refreshing

REF

ACT

ACT = Active

Self

Refresh

SR

SR E

X

Power

applied

ZQCL = ZQ Calibration Long

ZQCS = ZQ Calibration Short

WRITE

AD

RE

PDE = Enter Power-down

PDX = Exit Power-down

SRE = Self-Refresh entry

SRX = Self-Refresh exit

Reading

READ

Writing

A

WRITE A

MPR = Multi-Purpose Register

READ A

ITE

WR

RE

AD

PR

E

,P

RE

A

A

RE

Automatic Sequence

Command Sequence

PRE, PREA

P

E,

PR

Writing

A

A

Reading

Precharging

Confidential

- 5/86 -

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Ball Descriptions

Table 3. Ball Descriptions

Symbol

Type

Description

CK, CK#

Input

Differential Clock: CK and CK# are driven by the system clock. All SDRAM input signals

are sampled on the crossing of positive edge of CK and negative edge of CK#. Output

(Read) data is referenced to the crossings of CK and CK# (both directions of crossing).

CKE

Input

Clock Enable: CKE activates (HIGH) and deactivates (LOW) the CK signal. If CKE goes

LOW synchronously with clock, the internal clock is suspended from the next clock cycle

and the state of output and burst address is frozen as long as the CKE remains LOW.

When all banks are in the idle state, deactivating the clock controls the entry to the Power

Down and Self Refresh modes.

BA0-BA2

Input

Bank Address: BA0-BA2 define to which bank the BankActivate, Read, Write, or Bank

Precharge command is being applied.

A0-A12

Input

Address Inputs: A0-A12 are sampled during the BankActivate command (row address

A0-A12) and Read/Write command (column address A0-A9 with A10 defining Auto

Precharge).

A10/AP

Input

Auto-Precharge: A10 is sampled during Read/Write commands to determine whether

Autoprecharge should be performed to the accessed bank after the Read/Write operation.

(HIGH: Autoprecharge; LOW: no Autoprecharge). A10 is sampled during a Precharge

command to determine whether the Precharge applies to one bank (A10 LOW) or all

banks (A10 HIGH).

A12/BC#

Input

Burst Chop: A12/BC# is sampled during Read and Write commands to determine if burst

chop (on the fly) will be performed. (HIGH - no burst chop; LOW - burst chopped).

CS#

Input

Chip Select: CS# enables (sampled LOW) and disables (sampled HIGH) the command

decoder. All commands are masked when CS# is sampled HIGH. It is considered part of

the command code.

RAS#

Input

Row Address Strobe: The RAS# signal defines the operation commands in conjunction

with the CAS# and WE# signals and is latched at the crossing of positive edges of CK

and negative edge of CK#. When RAS# and CS# are asserted "LOW" and CAS# is

asserted "HIGH," either the BankActivate command or the Precharge command is

selected by the WE# signal. When the WE# is asserted "HIGH," the BankActivate

command is selected and the bank designated by BA is turned on to the active state.

When the WE# is asserted "LOW," the Precharge command is selected and the bank

designated by BA is switched to the idle state after the precharge operation.

CAS#

Input

Column Address Strobe: The CAS# signal defines the operation commands in

conjunction with the RAS# and WE# signals and is latched at the crossing of positive

edges of CK and negative edge of CK#. When RAS# is held "HIGH" and CS# is asserted

"LOW," the column access is started by asserting CAS# "LOW." Then, the Read or Write

command is selected by asserting WE# “HIGH " or “LOW".

WE#

Input

Write Enable: The WE# signal defines the operation commands in conjunction with the

RAS# and CAS# signals and is latched at the crossing of positive edges of CK and

negative edge of CK#. The WE# input is used to select the BankActivate or Precharge

command and Read or Write command.

LDQS,

Input /

LDQS#

Output

Bidirectional Data Strobe: Specifies timing for Input and Output data. Read Data Strobe

is edge triggered. Write Data Strobe provides a setup and hold time for data and DQM.

LDQS is for DQ0~7, UDQS is for DQ8~15. The data strobes LDOS and UDQS are paired

with LDQS# and UDQS# to provide differential pair signaling to the system during both

reads and writes.

UDQS

UDQS#

LDM,

UDM

Confidential

Input

Data Input Mask: Input data is masked when DM is sampled HIGH during a write cycle.

LDM masks DQ0-DQ7, UDM masks DQ8-DQ15.

- 6/86 -

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

DQ0 - DQ15

Input /

Output

Data I/O: The DQ0-DQ15 input and output data are synchronized with positive and

negative edges of DQS and DQS#. TheI/Os are byte-maskable during Writes.

ODT

Input

On Die Termination: ODT (registered HIGH) enables termination resistance internal to

the DDR3 SDRAM. When enabled, ODT is applied to each DQ, DQS, DQS#. The ODT

pin will be ignored if Mode-registers, MR1and MR2, are programmed to disable RTT.

RESET#

Input

Active Low Asynchronous Reset: Reset is active when RESET# is LOW, and inactive

when RESET# is HIGH. RESET# must be HIGH during normal operation. RESET# is a

CMOS rail to rail signal with DC high and low at 80% and 20% of VDD

VDD

Supply

Power Supply: +1.5V ±0.075V

VSS

Supply

Ground

VDDQ

Supply

DQ Power: +1.5V ±0.075V.

VSSQ

Supply

DQ Ground

VREFCA

Supply

Reference voltage for CA

VREFDQ

Supply

Reference voltage for DQ

ZQ

Supply

Reference pin for ZQ calibration.

NC

-

Confidential

No Connect: These pins should be left unconnected.

- 7/86 -

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Operation Mode Truth Table

Table 4. Truth Table (Note (1), (2))

Command

State CKEn-1(3) CKEn DM BA0-2 A10/AP A0-9, 11 A12/BC# CS# RAS# CAS# WE#

Idle(4)

H

H

X

V

Single Bank Precharge

Any

H

H

X

V

L

V

All Banks Precharge

Any

H

H

X

V

H

Write (Fixed BL8 or BC4)

Active(4)

H

H

X

V

L

Write (BC4, on the fly)

Active(4)

H

H

X

V

Write (BL8, on the fly)

Active(4)

H

H

X

Write with Autoprecharge

Active(4)

H

H

Active(4)

H

Active(4)

Read (Fixed BL8 or BC4)

BankActivate

L

L

H

H

V

L

L

H

L

V

V

L

L

H

L

V

V

L

H

L

L

L

V

L

L

H

L

L

V

L

V

H

L

H

L

L

X

V

H

V

V

L

H

L

L

H

X

V

H

V

L

L

H

L

L

H

H

X

V

H

V

H

L

H

L

L

Active(4)

H

H

X

V

L

V

V

L

H

L

H

Read (BC4, on the fly)

Active(4)

H

H

X

V

L

V

L

L

H

L

H

Read (BL8, on the fly)

Active(4)

H

H

X

V

L

V

H

L

H

L

H

Read with Autoprecharge

Active(4)

H

H

X

V

H

V

V

L

H

L

H

Active(4)

H

H

X

V

H

V

L

L

H

L

H

Active(4)

H

H

X

V

H

V

H

L

H

L

H

Idle

H

H

X

V

L

L

L

L

No-Operation

Any

H

H

X

V

V

V

V

L

H

H

H

Device Deselect

Any

H

H

X

X

X

X

X

H

X

X

X

Refresh

Idle

H

H

X

V

V

V

V

L

L

L

H

SelfRefresh Entry

Idle

H

L

X

V

V

V

V

L

L

L

H

SelfRefresh Exit

Idle

L

H

X

X

X

X

X

H

X

X

X

V

V

V

V

L

H

H

H

H

L

X

X

X

X

X

H

X

X

X

V

V

V

V

L

H

H

H

L

H

X

(Fixed BL8 or BC4)

Write with Autoprecharge

(BC4, on the fly)

Write with Autoprecharge

(BL8, on the fly)

(Fixed BL8 or BC4)

Read with Autoprecharge

(BC4, on the fly)

Read with Autoprecharge

(BL8, on the fly)

(Extended) Mode Register Set

Power Down Mode Entry

Power Down Mode Exit

Idle

Any

Row address

OP code

X

X

X

X

H

X

X

X

V

V

V

V

L

H

H

H

Data Input Mask Disable

Active

H

X

L

X

X

X

X

X

X

X

X

Data Input Mask Enable(5)

Active

H

X

H

X

X

X

X

X

X

X

X

Idle

H

H

X

X

H

X

X

L

H

H

L

X

L

H

H

L

ZQ Calibration Long

ZQ Calibration Short

Idle

H

H

X

X

L

X

NOTE 1: V=Valid data, X=Don't Care, L=Low level, H=High level

NOTE 2: CKEn signal is input level when commands are provided.

NOTE 3: CKEn-1 signal is input level one clock cycle before the commands are provided.

NOTE 4: These are states of bank designated by BA signal.

NOTE 5: LDM and UDM can be enabled respectively.

Confidential

- 8/86 -

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Functional Description

The DDR3 SDRAM is a high-speed dynamic random access memory internally configured as an eight-bank

DRAM. The DDR3 SDRAM uses an 8n prefetch architecture to achieve high speed operation. The 8n Prefetch

architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A

single read or write operation for the DDR3 SDRAM consists of a single 8n-bit wide, four clock data transfer at the

internal DRAM core and two corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write operation to the DDR3 SDRAM are burst oriented, start at a selected location, and continue for a

burst length of eight or a ‘chopped’ burst of four in a programmed sequence. Operation begins with the registration

of an Active command, which is then followed by a Read or Write command. The address bits registered coincident

with the Active command are used to select the bank and row to be activated (BA0-BA2 select the bank; A0-A12

select the row). The address bit registered coincident with the Read or Write command are used to select the

starting column location for the burst operation, determine if the auto precharge command is to be issued (via A10),

and select BC4 or BL8 mode ‘on the fly’ (via A12) if enabled in the mode register.

Prior to normal operation, the DDR3 SDRAM must be powered up and initialized in a predefined manner. The

following sections provide detailed information covering device reset and initialization, register definition, command

descriptions and device operation.

Figure 4. Reset and Initialization Sequence at Power-on Ramping

Ta

Tb

Tc

Td

Te

Tf

Tg

Th

Ti

Tj

Tk

CK#

CK

VDD

VDDQ

tCKSRX

T=200µs

T=500µs

RESET#

Tmin=10ns

tIS

CKE

tDLLK

tIS

COMMAND

Note 1

BA

tXPR

tMRD

tMRD

tMRD

tMOD

MRS

MRS

MRS

MRS

MR2

MR3

MR1

MR0

tZQinit

ZQCL

Note 1

VALID

tIS

ODT

VALID

tIS

VALID

Static LOW in case RTT_Nom is enabled at time Tg, otherwise static HIGH or LOW

RTT

NOTE 1. From time point "Td" until "Tk " NOP or DES commands must be applied between MRS and ZQCL commands.

TIME BREAK

Confidential

- 9/86 -

Don't Care

Rev.1.0 Aug.2016

�AS4C64M16D3A-12BIN

AS4C64M16D3A-12BCN

Power-up and Initialization

The Following sequence is required for POWER UP and Initialization

1. Apply power (RESET# is recommended to be maintained below 0.2 x VDD, all other inputs may be undefined).

RESET# needs to be maintained for minimum 200us with stable power. CKE is pulled “Low” anytime before

RESET# being de-asserted (min. time 10ns). The power voltage ramp time between 300mV to VDDmin must be

no greater than 200ms; and during the ramp, VDD>VDDQ and (VDD-VDDQ)