AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

Revision History

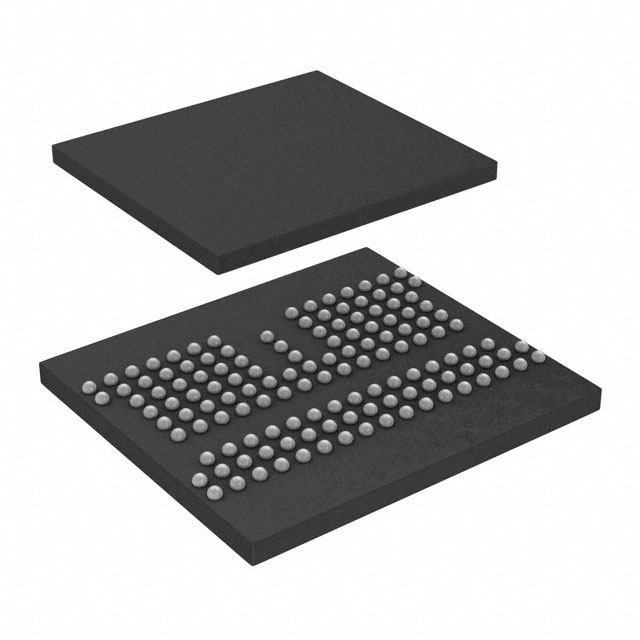

AS4C64M16MD2-25BCN / AS4C32M32MD2-25BCN 134 ball FBGA PACKAGE

Revision

Rev 1.0

Details

Preliminary datasheet

Date

July. 2016

Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070 TEL: (650) 610-6800 FAX: (650) 620-9211

Alliance Memory Inc. reserves the right to change products or specification without notice

Confidential

- 1/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

KEY FEATURE

• Double-data rate architecture; two data transfers per clock cycle

• Bidirectional data strobes (DQS, DQS#), These are transmitted/received with data to be used in capturing data at

the receiver

• Differential clock inputs (CK and CK#)

• Differential data strobes (DQS and DQS#)

• Commands & addresses entered on both positive and negative CK edges; data and data mask referenced to both

edges of DQS

• 8 internal banks for concurrent operation

• Data mask (DM) for write data

• Burst Length: 4 (default), 8 or 16

• Burst Type: Sequential or Interleave

• Read & Write latency : Refer to Table 47

• Auto Precharge option for each burst access

• Configurable Drive Strength

• Auto Refresh and Self Refresh Modes

• Partial Array Self Refresh and Temperature Compensated Self Refresh

• Deep Power Down Mode

• HSUL_12 compatible inputs

• VDD1/VDD2/VDDQ

: 1.8V/1.2V/1.2V

• No DLL : CK to DQS is not synchronized

• Edge aligned data output, center aligned data input

• Auto refresh duty cycle :

- 7.8us for -30 to 85 °C

Table 1. Ordering Information

Part Number

Org

Temperature

MaxClock (MHz)

Package

AS4C64M16MD2-25BCN 64Mx16

Commercial -30°C to +85°C

400

134-ball FBGA

AS4C32M32MD2-25BCN 32Mx32

Commercial -30°C to +85°C

400

134-ball FBGA

Table 2. Speed Grade Information

Speed Grade

Clock Frequency

DDR2L-800

Confidential

400MHz

RL

WL

6

3

- 2/129 -

tRCD (ns)

18

tRP (ns)

18

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

1. Functional Block Diagrams

Control

logic

Command / Address

Multiplex & Decode

CKE

CK

CK#

CS#

CA0

CA1

CA2

CA3

CA4

CA5

CA6

CA7

CA8

CA9

Refresh

Counter

X

X

ROW

address

MUX

Mode

registers

Bank7

Bank6

Bank7

Bank5

Bank6

Bank4

Bank5

Bank3

Bank4

Bank2

Bank3

Bank1

Bank2

Bank0

Bank1

Sense amplifier

Bank0

Sense amplifier

Sense

amplifier

Row

Mem

array amplifier

Sense

Address

Sense amplifier

latch

Sense amplifier

n

&

Sense amplifier

n

decoder

Sense amplifier

Read

n

latch n

4n

3

Column

address

Counter

/latch

Confidential

Column

decoder

DQS,DQS#

CK, CK#

4

4

WRITE 8 4

4

FIFO

Mask

&

4n

4

drivers

4

n

n

4n n

n

CK OUT Data n

n

n

n

CK IN

1

DQ0 DQn-1

INPUT

registers

I/O gating

DM mask logic

y-1

n

MUX DATA DRVRS

DQS

generator

3

Bank

Control

logic

COL0

4

DQS,

DQS#

4

4

n

RCVRS

COL0

DM

- 3/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

2. Ball Descriptions

2-1. Pad Definition and Description

CK, CK#

Name

Type

Input

CKE

Input

CS#

Input

CA0 - CA9

Input

DQ0 - DQ15

(x16)

DQ0 - DQ31

(x32)

DQS0,

DQS0#,

DQS1,

DQS1#

(x16)

DQS0 DQS3,

DQS0# DQS3

(x32)

DM0-DM1

(x16)

DM0 - DM3

(x32)

I/O

VDD1

VDD2

VDDQ

VREF(CA)

Supply

Supply

Supply

Supply

VREF(DQ)

VSS

VSSQ

ZQ

Supply

Supply

Supply

I/O

I/O

Input

Description

Clock: CK and CK# are differential clock inputs. All Double Data Rate (DDR) CA inputs are

sampled on both positive and negative edge of CK. Single Data Rate (SDR) inputs, CS#

and CKE, are sampled at the positive Clock edge.

Clock is defined as the differential pair, CK and CK#. The positive Clock edge is defined by

the crosspoint of a rising CK and a falling CK#. The negative Clock edge is defined by the

crosspoint of a falling CK and a rising CK#.

Clock Enable: CKE HIGH activates and CKE LOW deactivates internal clock signals and

therefore device input buffers and output drivers. Power savings modes are entered and

exited through CKE transitions.

CKE is considered part of the command code. See Command Truth Table for command

code descriptions.

CKE is sampled at the positive Clock edge.

Chip Select: CS# is considered part of the command code. See Command Truth Table

for command code descriptions.

CS# is sampled at the positive Clock edge.

DDR Command/Address Inputs: Uni-directional command/address bus inputs.

CA is considered part of the command code. See Command Truth Table for command code

descriptions.

Data Inputs/Output: Bi-directional data bus

Data Strobe (Bi-directional, Differential): The data strobe is bi-directional (used for read

and write data) and differential (DQS and DQS#). It is output with read data and input with

write data. DQS is edge-aligned to read data and centered with write data.

For x16, DQS0 and DQS0# correspond to the data on DQ0 - DQ7; DQS1 and DQS1# to

the data on DQ8 - DQ15.

For x32 DQS0 and DQS0# correspond to the data on DQ0 - DQ7, DQS1 and

DQS1# to the data on DQ8 - DQ15, DQS2 and DQS2# to the data on DQ16 - DQ23, DQS3

and DQS3# to the data on DQ24 - DQ31.

Input Data Mask: For LPDDR2 devices that do not support the DNV feature, DM is the

input mask signal for write data. Input data is masked when DM is sampled HIGH

coincident with that input data during a Write access. DM is sampled on both edges of

DQS. Although DM is for input only, the DM loading shall match the DQ and DQS (or

DQS#).

DM0 is the input data mask signal for the data on DQ0-7.

For x16 and x32 devices, DM1 is the input data mask signal for the data on DQ8-15.

For x32 devices, DM2 is the input data mask signal for the data on DQ16-23 and DM3 is

the input data mask signal for the data on DQ24-31.

Core Power Supply 1: Core power supply

Core Power Supply 2: Core power supply

I/O Power Supply: Power supply for Data input/output buffers.

Reference Voltage for CA Command and Control Input Receiver: Reference voltage for

all CA0-9, CKE, CS#, CK, and CK# input buffers.

Reference Voltage for DQ Input Receiver: Reference voltage for all Data input buffers

Ground

I/O Ground

Reference Pin for Output Drive Strength Calibration

NOTE : Data includes DQ and DM

Confidential

- 4/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

LPDDR2 SDRAM Addressing

Number of banks

Bank address pins

Auto precharge pin

X16

X32

ITEM

Row addresses

Column addresses

tREFI(µs)

Row addresses

Column addresses

tREFI(µs)

1Gb

8

BA0~BA2

A10/AP

R0-R12

C0-C9

7.8

R0-R12

C0-C8

7.8

NOTE 1. The least-significant column address C0 is not transmitted on the CA bus, and is implied to be zero.

NOTE 2. tREFI values for all bank refresh is Tc = -25~85℃, Tc means Operating Case Temperature.

NOTE 3. Row and Column Address values on the CA bus that are not used are “don’t care.”

Confidential

- 5/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

2-2. Package Dimension : 134-Ball FBGA – 10mm x 11.5mm x 1.0mm (max)

Confidential

- 6/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

2-3. Package Ballout

134Ball FBGA

1

2

3

4

5

6

7

8

9

10

A

DNU

DNU

NB

NB

NB

NB

NB

NB

DNU

DNU

B

DNU

NC

NC

NB

VDD2

VDD1

DQ31

NC

DQ29

NC

DQ26

NC

DNU

C

VDD1

VSS

NC

NB

VSS

VSSQ

VDDQ

DQ25

NC

VSSQ

VDDQ

D

VSS

VDD2

ZQ0

NB

VDDQ

DQ30

NC

DQ27

NC

DQS3

NC

DQS3#

NC

VSSQ

E

VSS

CA9

CA8

NB

DQ28

NC

DQ24

NC

DM3

NC

DQ15

VDDQ

VSSQ

F

NC

CA6

CA7

NB

VSSQ

DQ11

DQ13

DQ14

DQ12

VDDQ

G

VDD2

CA5

Vref(CA)

NB

DQS1#

DQS1

DQ10

DQ9

DQ8

VSSQ

H

NC

VSS

CK#

NB

DM1

VDDQ

NB

NB

NB

NB

J

VSS

NC

CK

NB

VSSQ

VDDQ

VDD2

VSS

Vref(DQ)

NB

K

CKE

NC

NC

NB

DM0

VDDQ

NB

NB

NB

NB

L

CS#

NC

NC

NB

DQS0#

DQS0

DQ5

DQ6

DQ7

VSSQ

M

CA4

CA3

CA2

NB

VSSQ

DQ4

DQ2

DQ1

DQ3

VDDQ

N

VSS

NC

CA1

NB

DQ19

NC

DQ23

NC

DM2

NC

DQ0

VDDQ

VSSQ

P

VSS

VDD2

CA0

NB

VDDQ

DQ17

NC

DQ20

NC

DQS2

NC

DQS2#

NC

VSSQ

R

VDD1

VSS

NC

NB

VSS

VSSQ

VDDQ

DQ22

NC

VSSQ

VDDQ

T

DNU

NC

NC

NB

VDD2

VDD1

DQ16

NC

DQ18

NC

DQ21

NC

DNU

U

DNU

DNU

NB

NB

NB

NB

NB

NB

DNU

DNU

[Top View]

1st Row

2nd Row

x32 Device

x16 Device

Power

ZQ

Ground

NC/DNU

NB

Confidential

- 7/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

3. Functional Description

LPDDR2 is a high-speed SDRAM device internally configured as a 8-Bank memory.

These devices contain the following number of bits:

1 Gb has 1,073,741,824 bits

LPDDR2-S4 uses a double data rate architecture on the Command/Address (CA) bus to reduce the number of

input pins in the system. The 10-bit CA bus contains command, address, and Bank information. Each command

uses one clock cycle, during which command information is transferred on both the positive and negative edge of

the clock.

LPDDR2-S4 uses a double data rate architecture on the DQ pins to achieve high speed operation. The double data

rate architecture is essentially a 4n prefetch architecture with an interface designed to transfer two data bits per DQ

every clock cycle at the I/O pins. A single read or write access for the LPDDR2-S4 effectively consists of a single

4n-bit wide, one clock cycle data transfer at the internal SDRAM core and four corresponding n-bit wide, one-halfclock-cycle data transfers at the I/O pins.

Read and write accesses to the LPDDR2 are burst oriented; accesses start at a selected location and continue for

a programmed number of locations in a programmed sequence.

For LPDDR2-S4 devices, accesses begin with the registration of an Activate command, which is then followed by a

Read or Write command. The address and BA bits registered coincident with the Activate command are used to

select the row and the Bank to be accessed. The address bits registered coincident with the Read or Write

command are used to select the Bank and the starting column location for the burst access.Prior to normal

operation, the LPDDR2 must be initialized..

Confidential

- 8/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

3.1 Simplified LPDDR2 Bus Interface State Diagram

The simplified LPDDR2 bus interface state diagram provides a simplified illustration of allowed state transitions and

the related commands to control them. For a complete definition of the device behavior, the information provided by

the state diagram should be integrated with the truth tables and timing specification.

The truth tables provide complementary information to the state diagram, they clarify the device behavior and the

applied restrictions when considering the actual state of all the banks.

For the command definition, see “LPDDR2 Command Definitions and Timing Diagrams”

Confidential

- 9/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

Simplified LPDDR2 Bus Interface State Diagram

Figure 3.1 LPDDR2 : Simplified Bus Interface State Diagram

NOTE 1 These transitions apply for LPDDR2-SX devices only.

NOTE 2 For LPDDR2-SDRAM in the Idle state, all banks are precharged.

NOTE 3 Use caution with this diagram. It is intented to provide a floorplan of the possible state transitions and commands to

control them, not all details. In particular, situations involving more than one Bank/Row

Confidential

- 10/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

3.2 Power-up, Initialization, and Power-Off

LPDDR2 Devices must be powered up and initialized in a predefined manner. Operational procedures other than

those specified may result in undefined operation

3.2.1 Power Ramp and Device Initialization

The following sequence shall be used to power up an LPDDR2 device.

1. Power Ramp

While applying power (after Ta), CKE shall be held at a logic low level (=< 0.2 x VDD2), all other inputs shall be

between VILmin and VIHmax. The LPDDR2 device will only guarantee that outputs are in a high impedance state

while CKE is held low.

On or before the completion of the power ramp (Tb) CKE must be held low.

DQ, DM, DQS and DQS# voltage levels must be between VSSQ and VDDQ during voltage ramp to avoid latch-up.

CK, CK#, CS#, and CA input levels must be between VSSCA and VDD2 during voltage ramp to avoid latch-up.

The following conditions apply:

Ta is the point where any power supply first reaches 300 mV.

After Ta is reached, VDD1 must be greater than VDD2 - 200 mV.

After Ta is reached, VDD1 and VDD2 must be greater than VDD2 - 200 mV.

After Ta is reached, VDD1 and VDD2 must be greater than VDDQ - 200 mV.

After Ta is reached, VREF must always be less than all other supply voltages.

The voltage difference between any of VSS, VSSQ, and VSSCA pins may not exceed 100 mV.

The above conditions apply between Ta and power-off (controlled or uncontrolled).

Tb is the point when all supply voltages are within their respective min/max operating conditions. Reference

voltages shall be within their respective min/max operating conditions a minimum of 5 clocks before CKE goes high.

Power ramp duration tINIT0 (Tb - Ta) must be no greater than 20 ms.

NOTE VDD2 is not present in some systems. Rules related to VDD2 in those cases do not apply.

2. CKE and clock:

Beginning at Tb, CKE must remain low for at least tINIT1 = 100 ns, after which it may be asserted high. Clock must

be stable at least tINIT2 = 5 x tCK prior to the first low to high transition of CKE (Tc). CKE, CS# and CA inputs must

observe setup and hold time (tIS, tIH) requirements with respect to the first rising clock edge (as well as to the

subsequent falling and rising edges).

The clock period shall be within the range defined for t CKb (18 ns to 100 ns), if any Mode Register Reads are

performed.

Mode Register Writes can be sent at normal clock operating frequencies so long as all AC Timings are

met. Furthermore, some AC parameters (e.g. tDQSCK) may have relaxed timings (e.g. t DQSCKb) before the system

is appropriately configured.

While keeping CKE high, issue NOP commands for at least tINIT3 = 200 us. (Td).

3. Reset command:

After tINIT3 is satisfied, a MRW(Reset) command shall be issued (Td). The memory controller may optionally

issue a Precharge-All command (for LPDDR2-SX) to the MRW Reset command. Wait for at least tINIT4 = 1us while

keeping CKE asserted and issuing NOP commands.

4. Mode Registers Reads and Device Auto-Initialization (DAI) polling:

After tINIT4 is satisfied (Te) only MRR commands and power-down entry/exit commands are allowed.

Therefore, after Te, CKE may go low in accordance to Power-Down entry and exit specification (see “Powerdown” ).

The MRR command may be used to poll the DAI-bit to acknowledge when Device Auto-Initialization is complete or

the memory controller shall wait a minimum of tINIT5 before proceeding.

As the memory output buffers are not properly configured yet, some AC parameters may have relaxed timings

before the system is appropriately configured.

After the DAI-bit (MR0, “DAI”) is set to zero “DAI complete“ by the memory device, the device is in idle state (Tf).

The state of the DAI status bit can be determined by an MRR command to MR0.

All SDRAM devices will set the DAI-bit no later than tINIT5 (10 us) after the Reset command. The memory

controller shall wait a minimum of tINIT5 or until the DAI-bit is set before proceeding.

After the DAI-Bit is set, it is recommended to determine the device type and other device characteristics by issuing

MRR commands (MR0 “Device Information” etc.).

5. ZQ Calibration:

After tINIT5 (Tf), an MRW ZQ Initialization Calibration command may be issued to the memory (MR10). For

Confidential

- 11/129 -

Rev.1.0 July 2016

�!

!

AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

LPDDR2 devices which do not support the ZQ Calibration command, this command shall be ignored. This

command is used to calibrate the LPDDR2 output drivers (RON) over process, voltage, and temperature.

Optionally, the MRW ZQ Initialization Calibration command will update MR0 to indicate RZQ pin connection. In

systems in which more than one LPDDR2 device exists on the same bus, the controller must not overlap ZQ

Calibration commands. The device is ready for normal operation after tZQINIT.

6. Normal Operation:

After tZQINIT (Tg), MRW commands shall be used to properly configure the memory, for example the output buffer

driver strength, latencies etc. Specifically, MR1, MR2, and MR3 shall be set to configure the memory for the target

frequency and memory configuration.

The LPDDR2 device will now be in IDLE state and ready for any valid command.

After Tg, the clock frequency may be changed according to the clock frequency change procedure described in

section “Input clock stop and frequency change” of this specification.

Table 1 – Timing Parameters for initialization

Symbol

Value

min

Unit

max

tINIT0

20

Comment

ms

Maximum Power Ramp Time

Minimum CKE low time after completion of power ramp

tINIT1

100

ns

tINIT2

5

tCK

Minimum stable clock before first CKE high

tINIT3

200

us

Minimum Idle time after first CKE assertion

tINIT4

1

us

Minimum Idle time after Reset command

us

Maximum duration of Device Auto-Initialization

us

ZQ Initial Calibration for LPDDR2-S4 devices

ns

Clock cycle time during boot

tINIT5

10

tZQINIT

1

tCKb

18

100

Ta

Tb

t

INIT2

Tc

Td

Te

Tf

Tg

CK/CK#

t

INIT0

Supplies

t

t

INIT1

INIT3

CKE

t

ISCKE

t

t

INIT4

ZQINIT

t

INIT5

CA

RESET

MRR

MRW

ZQCAL

Valid

RTT

DQ

Figure 3.2 Power Ramp and Initialization Sequence

3.2.2 Initialization after Reset (without Power ramp):

If the RESET command is issued outside the power up initialization sequence, the reinitialization procedure shall

begin with step 3 (Td).

3.2.3 Power-off Sequence

The following sequence shall be used to power off the LPDDR2 device. Unless specified otherwise, these steps are

mandatory and apply to S4 devices.

While removing power, CKE shall be held at a logic low level (=< 0.2 x VDD2), all other inputs shall be between

VILmin and VIHmax. The LPDDR2 device will only guarantee that outputs are in a high impedance state while CKE

is held low. DQ, DM, DQS, and DQS# voltage levels must be between VSSQ and VDDQ during power off

sequence to avoid latch-up. CK, CK#, CS#, and CA input levels must be between VSSCA and VDD2 during power

off sequence to avoid latch-up.

Confidential

- 12/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

Tx is the point where any power supply decreases under its minimum value specified in the DC operating condition

table.

Tz is the point where all power supplies are below 300 mV. After Tz, the device is powered off.

The time between Tx and Tz (tPOFF) shall be less than 2s.

The following conditions apply:

Between Tx and Tz, VDD1 must be greater than VDD2 - 200 mV.

Between Tx and Tz, VDD1 and VDD2 must be greater than VDD2 - 200 mV.

Between Tx and Tz, VDD1 and VDD2 must be greater than VDDQ - 200 mV.

Between Tx and Tz, VREF must always be less than all other supply voltages.

The voltage difference between any of VSS, VSSQ, and VSSCA pins may not exceed 100 mV.

Table 2 – Timing Parameters Power-Off

Symbol

tPOFF

Value

min

max

-

2

Unit

s

Comment

Maximum Power-Off ramp time

3.2.4 Uncontrolled Power-Off Sequence

The following sequence shall be used to power off the LPDDR2 device under uncontrolled condition.

Tx is the point where any power supply decreases under its minimum value specified in the DC operating condition

table. After turning off all power supplies, any power supply current capacity must be zero, except for any static

charge remaining in the system.

Tz is the point where all power supply first reaches 300 mV. After Tz, the device is powered off.

The time between Tx and Tz (tPOFF) shall be less than 2s. The relative level between supply voltages are

uncontrolled during this period.

VDD1 and VDD2 shall decrease with a slope lower than 0.5 V/usec between Tx and Tz.

Uncontrolled power off sequence can be applied only up to 400 times in the life of the device.

Confidential

- 13/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

3.3 Mode Register Definition

3.3.1 Mode Register Assignment and Definition in LPDDR2 SDRAM

Table 3 shows the 16 common mode registers for LPDDR2 SDRAM Table 4 shows only LPDDR2 SDRAM mode

registers. Additionally Table 5 shows RFU mode registers and Reset Command.

Each register is denoted as “R” if it can be read but not written, “W” if it can be written but not read, and “R/W” if it

can be read and written.

Mode Register Read command shall be used to read a register. Mode Register Write command shall be used to

write a register.

Table 3 – Mode Register Assignment in LPDDR2 SDRAM

MR#

MA

Function

Access

OP7

OP6

0

00h

Device Info.

R

(RFU)

1

01h

Device Feature 1

W

nWR(for AP)

2

02h

Device Feature 2

W

(RFU)

RL & WL

3

03h

I/O Config-1

W

(RFU)

DS

4

04h

Refresh Rate

R

5

05h

Basic Config-1

R

LPDDR2 Manufacturer ID

6

06h

Basic Config-2

R

Revision ID1

7

07h

Basic Config-3

R

Revision ID2

8

08h

Basic Config-4

R

9

09h

Test Mode

W

Vendor-Specific Test Mode

10

0Ah

IO Calibration

W

Calibration Code

11:15

0Bh~0Fh

(reserved)

TUF

OP5

OP4

OP3

RZQI

WC

OP2

OP1

OP0

(RFU)

DI

DAI

BT

(RFU)

I/O width

BL

Refresh Rate

Density

Type

(RFU)

Table 4 — Mode Register Assignment in LPDDR2 SDRAM

MR#

MA

Function

Access

OP7

OP6

OP5

OP4

OP3

16

10h

PASR_Bank (S4)

W

Bank Mask

17

11h

PASR_Seg

W

Segment Mask

18:19

12h:13h

(Reserved)

OP2

OP1

OP0

OP1

OP0

(RFU)

Mode Register Assignment in LPDDR2 SDRAM (NVM Part)

MR#

MA

Function

20:31

14h~1Fh

(Do Not Use)

Confidential

Access

OP7

OP6

- 14/129 -

OP5

OP4

OP3

OP2

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

Table 5 – Mode Register Assignment in LPDDR2 SDRAM

MR#

MA

Function

32

20h

33:39

21h:27h

40

28h

41:47:00

29h:2Fh

(Do Not Use)

48:62

30h~3Eh

(Reserved)

63

3Fh

Reset

64:126

40h:7Eh

(Reserved)

127

7Fh

(Do Not Use)

128:190

80h: BEh

191

BFh

192:254

C0h:FEh

255

FFh

DQ Calibration

Pattern A

Access

OP7

OP6

OP5

OP4

OP3

OP2

R

See " DQ Calibration:

R

See " DQ Calibration:

OP1

OP0

(Do Not Use)

DQ Calibration

Pattern B

(RFU)

W

X

(RFU)

Reserved for

(RFU)

Vendor Use)

(Do Not Use)

Reserved for

(RFU)

Vendor Use)

(Do Not Use)

The following notes apply to Tables 3-5:

NOTE 1 RFU bits shall be set to ‘0’ during Mode Register writes.

NOTE 2 RFU bits shall be read as ‘0’ during Mode Register reads.

NOTE 3 All Mode Registers that are specified as RFU or write-only shall return undefined data when read and DQS,DQS# shall be toggled.

NOTE 4 All Mode Registers that are specified as RFU shall not be written.

NOTE 5 Writes to read-only registers shall have no impact on the functionality of the device.

Confidential

- 15/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

MR0 Device Information (MA =00H) :

OP7

OP6

OP5

OP4

OP3

RZQI

(Optional)

RFU

DAI(Device Auto-Initialization

Status)

Read-only

OP0

DI (Device Information)

Read-only

OP1

RZQI ( Built in Self Test for RZQ

Information)

Read -only

OP4:OP3

OP2

OP1

OP0

RFU

DI

DAI

0B: DAI complete

1B: DAI still in progress

0B: S4 SDRAM

1B: Do Not Use

00B : RZQ self test not supported)

01B : ZQ-pin may connect to VDD2 or float

10B : ZQ-pin may short to GND

11B : ZQ-pin self test completed, no error

condition detected

(ZQ-pin may not connect to VDD2 or float nor

short to GND)

1

NOTE 1 RZQI, if supported, will be set upon completion of the MRW ZQ Initialization Calibration command.

NOTE 2 If ZQ is connected to VDD2 to set default calibration, OP[4:3] shall be set to 01. If ZQ is not connected to VDD2,

either OP[4:3]=01 or OP[4:3]=10 might indicate a ZQ-pin assembly error. It is recommended that the assembly error is

corrected.

NOTE 3 In the case of possible assembly error (either OP[4:3]=01 or OP[4:3]=10 per NOTE 4), the LPDDR2 device will

default to factory trim settings for RON, and will ignore ZQ calibration commands. In either case, the system may not function

as intended.

NOTE 4 In the case of the ZQ self-test returning a value of 11b, this result indicates that the device has detected a resistor

connection to the ZQ pin. However, this result cannot be used to validate the ZQ resistor value or that the ZQ resistor tolerance

meets the specified limits (i.e., 240-ohm +/-1%).

Confidential

- 16/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

MR1 Device Feature 1 (MA =01H) :

OP7

OP6

OP5

nWR (for AP)

OP4

WC

OP3

BT

OP2

OP1

BL

OP0

010B: BL4 (default)

BL

Write-only

OP

011B: BL8

110B: BL16

All others : reserved

BT

Write-only

OP

WC

Write-only

OP

nWR

Write-only

OP

0B: Sequential (default)

1

1B: Interleaved

0B: Wrap (default)

1B: No wrap (allowed for SDRAM BL4 only)

001B: nWR =3(default)

010B: nWR =4

011B: nWR =5

100B: nWR =6

101B: nWR =7

110B :nWR =8

All others : reserved

2

NOTE 1 BL 16, interleaved is not an official combination to be supported.

NOTE 2 Programmed value in nWR register is the number of clock cycles which determines when to start internal

precharge operation for a write burst with AP enabled. It is determined by RU(tWR/tCK).

Confidential

- 17/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

Table 6

- Burst Sequence by BL,BT, and WC

W/C

BT

C2

C1

C0

X

X

0B

0B

X

X

1B

0B

X

X

X

0B

X

0B

0B

0B

X

0B

1B

0B

X

1B

0B

0B

X

1B

1B

0B

X

0B

0B

0B

X

0B

1B

0B

X

1B

0B

0B

X

1B

1B

0B

X

X

X

0B

0B

0B

0B

0B

0

1

2

3

4

5

6

7

8

0B

0B

1B

0B

2

3

4

5

6

7

8

9

0B

1B

0B

0B

4

5

6

7

8

9

A

0B

1B

1B

0B

6

7

8

9

A

B

1B

0B

0B

0B

8

9

A

B

C

D

1B

0B

1B

0B

A

B

C

D

E

1B

1B

0B

0B

C

D

E

F

1B

1B

1B

0B

E

F

0

1

X

X

X

0B

X

X

X

0B

wrap

any

nw

any

BL

Burst Cycle Number are Burst Address Sequence

C3

4

seq

wrap

8

int

nw

wrap

2

3

4

0

1

2

3

5

6

7

8

2

3

0

1

y

y+1

y+2

y+3

0

1

2

2

3

4

11

12

13

14

15

16

3

4

5

6

7

4

5

6

7

0

1

5

6

7

0

1

2

3

6

7

0

1

2

3

4

5

0

1

2

3

4

5

6

7

2

3

0

1

6

7

4

5

4

5

6

7

0

1

2

3

6

7

4

5

2

3

0

1

9

10

9

A

B

C

D

E

F

A

B

C

D

E

F

0

1

B

C

D

E

F

0

1

2

3

C

D

E

F

0

1

2

3

4

5

E

F

0

1

2

3

4

5

6

7

F

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

A

B

2

3

4

5

6

7

8

9

A

B

C

D

illegal (not allowed)

any

seq

16

nw

1

int

illegal (not allowed)

any

illegal (not allowed)

1. C0 input is not present on CA bus. It is implied zero.

2. For BL=4, the burst address represents C1 - C0.

3. For BL=8, the burst address represents C2 - C0.

4. For BL=16, the burst address represents C3 - C0.

5. For no-wrap (nw), BL4, the burst shall not cross the page boundary and shall not cross sub-page boundary.

The variable y may start at any address with C0 equal to 0 and may not start at any address in Table 7 for the respective density

and bus width combinations.

Confidential

- 18/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

Table 7 – LPDDR2- SX Non Wrap Restrictions

1Gb

x16

x32

x16

x32

Not across full page boundary

3FE, 3FF, 000, 001

1FE, 1FF, 000, 001

Not across sub page boundary

1FE, 1FF, 200, 201

None

NOTE 1 Non - wrap BL =4 data-orders shown above are prohibited

MR2 Device Feature 2 (MA =02H) :

OP7

OP6

OP5

(RFU)

RL & WL

Writeonly

OP4

OP

MR3 I/O Configuration 1 (MA =03H) :

OP7

OP6

OP5

(RFU)

DS

Writeonly

OP3

MR4 Device Temperature (MA =04H) :

OP7

OP6

OP5

OP4

TUF

(RFU)

OP0

0001B: RL =3 /WL=1(default)

0010B: RL =4 /WL=2

0011B: RL =5 /WL=2

0100B: RL =6 /WL=3

0101B: RL =7 /WL=4

0110B :RL =8 /WL=4

All others : reserved

OP4

OP3

OP

OP2

OP1

RL & WL

OP2

DS

OP1

OP0

0000B: reserved

0001B: 34.3-ohm typical

0010B: 40-ohm typical (default)

0011B: 48-ohm typical

0100B: 60-ohm typical

0101B: reserved for 68.6-ohm typical

0110B :80-ohm typical

0111B :120-ohm typical (optional)

All others : reserved

OP3

OP2

OP1

OP0

SDRAM Refresh Rate

000B: SDRAM Low temperature operating limit exceeded

001B: 4X tREF, 4x tREFlqb, 4x tREFW

010B: 2X tREF, 2x tREFlqb, 2x tREFW

SDRAM Refresh Rate

Readonly

OP

Temperature Update Flag

(TUF)

Readonly

OP

011B: 1X tREF, 1x tREFlqb, 1x tREFW (≤85℃)

100B: Reserved

101B: 0.25X tREF, 0.25x tREFlqb, 0.25x tREFW , do not de-rate

SDRAM AC timing

110B :0.25X tREF, 0.25x tREFlqb, 0.25x tREFW , de-rate SDRAM

AC timing

111B :SDRAM High temperature operating limit exceeded

0B: OP value has not changed since last read of MR4

1B: OP value has changed since last read of MR4

NOTE 1 A Mode Register Read from MR4 will reset OP7 to ‘0’.

NOTE 2 OP7 is reset to ‘0’ at power-up. OP bits are undefined after power-up.

Confidential

- 19/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

NOTE 3 If OP2 equals ‘1’, the device temperature is greater than 85℃

NOTE 4 OP7 is set to ‘1’ if OP2:OP0 has changed at any time since the last read of MR4.

NOTE 5 LPDDR2 might not operate properly when OP[2:0] = 000B or 111B.

NOTE 6 LPDDR2-SX devices shall be de-rated by adding 1.875 ns to the following core timing parameters: tRCD, tRC, tRAS, tRP, and

tRRD. tDQSCK shall be de-rated according to the tDQSCK de-rating in Table 52. Prevailing clock frequency spec and related setup and hold

timings shall remain unchanged.

NOTE 8 See “Temperature Sensor” for information on the recommended frequency of reading MR4.

MR5 Basic Configuration 1 (MA =05H) :

OP7

OP6

OP5

OP4

OP3

LPDDR2 Manufacture ID

LPDDR2 Manufacture ID

Readonly

MR6_Basic Configuration 2 (MA = 06H):

OP7

OP6

OP5

Revision ID1

NOTE 1 MR6 is Vendor Specific

Confidential

Readonly

OP

OP1

OP0

OP1

OP0

0000 0000B : Reserved

0000 0001B : Samsung

0000 0010B : Qimonda

0000 0011B : Elpida

0000 0100B : Etron

0000 0101B : Nanya

0000 0111B : Mosel

0000 1000B : Winbond

0000 1001B : ESMT

0000 1010B : Reserved

0000 1011B : Spansion

0000 1100B : SST

0000 1101B : ZMOS

0000 1110B : Intel

0001 1100B : Alliance

1111 1110B : Numonyx

1111 1111B : Micron

All Others : Reserved

OP4

OP3

Revision ID1

OP

OP2

OP2

0001 0001B: Q-version

- 20/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

MR7 Basic Configuration 3 (MA =07H) :

OP7

OP6

Revision ID2

NOTE 1 MR7 is Vendor Specific

OP5

OP4

OP3

Revision ID2

Readonly

MR8_Basic Configuration 4 (MA = 08B H):

OP7

OP6

OP5

I/O width

OP

OP2

OP1

OP0

OP1

OP0

0000 0000B: A-version

OP4

OP3

Density

OP2

Type

00B: S4 SDRAM

Type

Readonly

OP

01B: Reserved

10B: Do Not Use

11B: Reserved

Density

Readonly

OP

0000B: 64Mb

0001B: 128Mb

0010B: 256Mb

0011B: 512Mb

0100B:

1Gb

0101B:

2Gb

0110B:

4Gb

0111B

8Gb

1000B: 16Gb

1001B: 32Gb

All others : reserved

00B: x32

I/O Width

MR9_Test Mode (MA = 09H):

OP7

OP6

MR10_Calibration (MA = 0AH):

OP7

OP6

Readonly

OP5

OP

01B: x16

10B: x8

11B: not used

OP4

OP3

Vendor-specific Test Mode

OP5

OP4

OP2

OP1

OP3

OP2

Calibration Code

OP1

OP0

OP0

0xFFB: Calibration command after initialization

Calibration Code

Writeonly

0xABB: Long calibration

OP

0x56B: Short calibration

0xC3B: ZQ Reset

Others : Reserved

NOTE 1 Host processor shall not write MR10 with “Reserved” values

NOTE 2 LPDDR2 devices shall ignore calibration command when a “Reserved” value is written into MR10.

NOTE 3 See AC timing table for the calibration latency.

NOTE 4 If ZQ is connected to VSSCA through RZQ, either the ZQ calibration function (see “Mode Register Write ZQ Calibration

Command” ) or default calibration (through the ZQreset command) is supported. If ZQ is connected to VDD2, the device operates with

default calibration, and ZQ calibration commands are ignored. In both cases, the ZQ connection shall not change after power is applied to the

Confidential

- 21/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

device.

NOTE 5 LPDDR2 devices that do not support calibration shall ignore the ZQ Calibration command.

NOTE 6 Optionally, the MRW ZQ Initialization Calibration command will update MR0 to indicate RZQ pin connection.

MR11:15_(Reserved) (MA = 0B H-0FH):

MR16_PASR_Bank Mask (MA = 010 H): S2 and S4 SDRAM only

OP7

OP6

OP5

OP4

OP3

OP2

S4 SDRAM

Bank Mask (4-bank or 8 bank)

OP1

OP0

S4 SDRAM :

0B: refresh enable to the bank (=unmasked,

OP default)

1B: refresh blocked (=masked)

For 4-bank S4 SDRAM, only are used.

4-Bank S4 SDRAM

OP

Bank Mask

8-Bank S4 SDRAM

0

XXXX XXX1

Bank 0

Bank 0

1

XXXX XX1X

Bank 1

Bank 1

2

XXXX X1XX

Bank 2

Bank 2

3

XXXX 1XXX

Bank 3

Bank 3

4

XXX1 XXXX

Bank 4

5

XX1X XXXX

Bank 5

6

X1XX XXXX

Bank 6

7

1XXX XXXX

Bank 7

Writeonly

Bank Mask

1.

MR17_PASR_Segment Mask (MA = 011 H): 1Gb ~ 8Gb S4 SDRAM only

OP7

OP6

OP5

OP4

OP3

OP2

Segment Mask

Segment Mask

Writeonly

OP

OP1

1

OP0

0B: refresh enable to the segment (=unmasked,

default)

1B: refresh blocked (=masked)

1Gb

R12 : 10

2Gb,

4Gb

R13 : 11

Segment

OP

Segment Mask

0

0

XXXX XXX1

000B

1

2

3

4

5

6

7

1

2

3

4

5

6

7

XXXX XX1X

XXXX X1XX

XXXX 1XXX

XXX1 XXXX

XX1X XXXX

X1XX XXXX

1XXX XXXX

001B

010B

011B

100B

101B

110B

111B

8Gb

R14 : 12

NOTE This table indicates the range of row addresses in each masked segment X is do not care for a particular segment

MR18-19_Reserved (MA = 012H - 013H):

MR20-31_Do Not Use, NVM only

MR32_DQ Calibration Pattern A (MA = 20 H):

Reads to MR32 return DQ Calibration Pattern “A”. See “DQ Calibration”.

MR33:39_(Do Not Use) (MA = 21 H-27H):

MR40_DQ Calibration Pattern B (MA = 28 H):

Reads to MR40 return DQ Calibration Pattern “B”. See “DQ Calibration”.

Confidential

- 22/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

MR41:47_(Do Not Use) (MA = 29H-2FH):

MR48:62_(Reserved) (MA = 30H-3EH):

MR63_Reset (MA = 3FH): MRW only

OP7

OP6

OP5

OP4

X

OP3

OP2

OP1

OP0

NOTE1 For additional information on MRW RESET see " Mode Register Write Command "

MR64:126_(Reserved) (MA = 40H-7EH):

MR127_(Do Not Use) (MA = 7FH):

MR128:190_(Reserved for Vendor Use) (MA = 80H-BEH):

MR191_(Do Not Use) (MA = BFH):

MR192:254_(Reserved for Vendor Use) (MA = C0 H-FEH):

MR255_(Do Not Use) (MA = FFH):

Confidential

- 23/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

4. LPDDR2 Command Definitions and Timing Diagrams

4.1 Active Command

4.1.1

LPDDR2-SX: Activate Command

The SDRAM Activate command is issued by holding CS# LOW, CA0 LOW, and CA1 HIGH at the rising edge of the

clock. The bank addresses BA0 - BA2 are used to select the desired bank. The row address R0 through R14 is

used to determine which row to activate in the selected bank. The Activate command must be applied before any

Read or Write operation can be executed. The LPDDR2 SDRAM can accept a read or write command at time

tRCD after the activate command is sent. Once a bank has been activated it must be precharged before another

Activate command can be applied to the same bank. The bank active and precharge times are defined as tRAS

and tRP, respectively. The minimum time interval between successive Activate commands to the same bank is

determined by the RAS cycle time of the device (tRC). The minimum time interval between Activate commands to

different banks is tRRD.

Certain restrictions on operation of the 8-bank devices must be observed. There are two rules. One for restricting

the number of sequential Activate commands that can be issued and another for allowing more time for RAS

precharge for a Precharge All command. The rules are as follows:

• 8-bank device Sequential Bank Activation Restriction : No more than 4 banks may be activated (or refreshed, in

the case of REFpb) in a rolling tFAW window. Converting to clocks is done by dividing tFAW[ns] by tCK[ns], and

rounding up to next integer value. As an example of the rolling window, if RU{ (tFAW / tCK) } is 10 clocks, and an

activate command is issued in clock N, no more than three further activate commands may be issued at or between

clock N+1 and N+9. REFpb also counts as bank-activation for the purposes of tFAW.

• 8-bank device Precharge All Allowance : tRP for a Precharge All command for an 8-bank device shall equal

tRPab, which is greater than tRPpb.

T0

T1

T2

T3

Tn

Tn+1

Tn+2

Tn+3

CK#

CK#

CA[9:0]

Bank n

addr

Bank m

addr

Row addr

Row

Bank n

col addr

Bank n

row addr

Bank n

Col addr

Row addr

t

RRD

t

RCD

t

t

RAS

RP

t

RC

CMD

ACTIVATE

NOP

ACTIVATE

READ

PRECHARGE

NOP

NOP

ACTIVATE

Figure 4.1 — LPDDR2-SX: Activate command cycle: tRCD = 3, tRP = 3, tRRD = 2

NOTE 1 A Precharge-All command uses tRPab timing, while a Single Bank Precharge command uses tRPpb timing. In this

figure, tRP is used to denote either an All-bank Precharge or a Single Bank Precharge.

Tn

Tn+

Tm

Tm+

Tx

Tx+

Ty

Ty+1

Ty+2

Tz

Tz+1

Tz+2

CK#

CK#

CA[9:0]

Bank

A

Bank

A

Bank

B

Bank

B

t

ACTIVATE

NOP

Bank

C

t

RRD

CMD

Bank

C

NOP

Bank

D

Bank

E

Bank

E

t

RRD

ACTIVATE

Bank

D

RRD

ACTIVATE

NOP

ACTIVATE

NOP

NOP

NOP

ACTIVATE

NOP

t

FAW

Figure 4.2 — LPDDR2-SX: tFAW timing

NOTE 1: For 8-bank devices only.

Confidential

- 24/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

4.2 LPDDR2 Command Input Signal Timing Definition

4.2.1 LPDDR2 Command Input Setup and Hold Timing

T1

T0

T2

T3

CK#

CK#

t

IS tIH

t

IS tIH VIH(DC)

CS#

VIL(AC)

CA[9:0]

CMD

CA

rise

CA

fall

NOP

t

IS tIH

CA

rise

VIL(DC)

CA

fall

Command

VIH(AC)

t

IS tIH

CA

rise

CA

fall

NOP

CA

rise

CA

fall

Command

Transitioning data

Don’t Care

NOTE : Setup and hold conditions also apply to the CKE pin. See section related to power down for timing diagrams related to

the CKE pin.

Figure 4.3 — LPDDR2: Command Input Setup and Hold Timing

Confidential

- 25/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

4.3 Read and Write access modes

4.3.1 LPDDR2-SX: Read and Write access modes

After a bank has been activated, a read or write cycle can be executed. This is accomplished by setting CS# LOW,

CA0 HIGH, and CA1 LOW at the rising edge of the clock. CA2 must also be defined at this time to determine

whether the access cycle is a read operation (CA2 HIGH) or a write operation (CA2 LOW).

The LPDDR2 SDRAM provides a fast column access operation. A single Read or Write Command will initiate a

burst read or write operation on successive clock cycles.

For LPDDR2-S4 devices, a new burst access must not interrupt the previous 4-bit burst operation in case of BL = 4

setting. In case of BL = 8 and BL = 16 settings, Reads may be interrupted by Reads and Writes may be interrupted

by Writes provided that this occurs on even clock cycles after the Read or Write command and tCCD is met.

Confidential

- 26/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

4.4 Burst Read Command

The Burst Read command is initiated by having CS# LOW, CA0 HIGH, CA1 LOW and CA2 HIGH at the rising edge

of the clock. The command address bus inputs, CA5r-CA6r and CA1f-CA9f, determine the starting column address

for the burst. The Read Latency (RL) is defined from the rising edge of the clock on which the Read Command is

issued to the rising edge of the clock from which the tDQSCK delay is measured. The first valid datum is available

RL * tCK + tDQSCK + tDQSQ after the rising edge of the clock where the Read Command is issued. The data

strobe output is driven LOW tRPRE before the first rising valid strobe edge. The first bit of the burst is synchronized

with the first rising edge of the data strobe. Each subsequent data-out appears on each DQ pin edge aligned with

the data strobe. The RL is programmed in the mode registers.

Timings for the data strobe are measured relative to the crosspoint of DQS and its complement, DQS#.

RL-1

RL

t

RL+BL/2

t

CH

CL

CK#

CK#

t

t

DQSCKmax

t

HZ(DQS)

t

LZ(DQS)

t

RPRE

RPST

DQS#

DQS#

t

t

QH

QH

t

t

DQSQmax

DQSQmax

DQ

DOUT

DOUT

DOUT

t

DOUT

t

LZ(DQ)

HZ(DQ)

Transitioning data

Figure 4.4 — Data output (read) timing (tDQSCKmax)

NOTE 1 tDQSCK may span multiple clock periods.

NOTE 2 An effective Burst Length of 4 is shown.

RL-1

RL

CK#

CK#

t

RL+BL/2

t

CH

CL

t

t

DQSCKmin

t

LZ(DQS)

HZ(DQS)

t

t

RPRE

RPST

DQS#

DQS#

t

t

QH

QH

t

t

DQSQmax

DQSQmax

DQ

DOUT

DOUT

t

DOUT

DOUT

t

LZ(DQ)

HZ(DQ)

Transitioning data

Figure 4.5 — Data output (read) timing (tDQSCKmin)

NOTE 1 An effective Burst Length of 4 is shown.

Confidential

- 27/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

RL = 5

CA[9:0]

Bank n

col addr

CMD

Col Addr

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

t

DQSCK

DQS#

DQS#

DOUT

A0

DQ

DOUT

A1

DOUT

A2

DOUT

A3

Transitioning data

Figure 4.6 — LPDDR2-SX: Burst read: RL = 5, BL = 4, tDQSCK > tCK

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

RL = 3

CA[9:0]

CMD

Bank n

col addr

Col Addr

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

t

DQSCK

DQS#

DQS#

DQ

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

DOUT

A4

DOUT

A5

DOUT

A6

DOUT

A7

Transitioning data

Figure 4.7 — LPDDR2-SX: Burst read: RL = 3, BL = 8, tDQSCK < tCK

Confidential

- 28/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

Tn

Tn+1

Tn+2

Tn+3

Tn+4

Tn+5

Tn+6

Tn+7

Tn+8

CK#

CK#

RL = 5

CA[9:0]

Bank n

col addr

CMD

Col Addr

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

t

DQSCKn

DQS#

DQS#

DOUT

A0

DQ

DOUT

A1

DOUT

A2

DOUT

A3

32ms maximum...

1

Tm

Tm+1

Tm+2

Tm+3

Tm+4

Tm+5

Tm+6

Tm+7

Tm+8

CK#

CK#

RL = 5

Bank n

col addr

CA[9:0]

CMD

Col Addr

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

t

DQSCKm

DQS#

DQS#

DOUT

A0

DQ

DOUT

A1

DOUT

A2

DOUT

A3

...32ms maximum

Transitioning data

1

Figure 4.8 — LPDDR2: tDQSCKDL timing

NOTE 1 tDQSCKDLmax is defined as the maximum of ABS(tDQSCKn - tDQSCKm) for any {tDQSCKn

,tDQSCKm} pair within any 32ms rolling window.

Confidential

- 29/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

Tn

Tn+1

Tn+2

Tn+3

Tn+4

Tn+5

Tn+6

Tn+7

Tn+8

CK#

CK#

RL = 5

CA[9:0]

Bank n

col addr

CMD

Col Addr

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

t

DQSCKn

DQS#

DQS#

DOUT

A0

DQ

DOUT

A1

DOUT

A2

DOUT

A3

1.6us maximum...

1

Tm

Tm+1

Tm+2

Tm+3

Tm+4

Tm+5

Tm+6

Tm+7

Tm+8

CK#

CK#

RL = 5

Bank n

col addr

CA[9:0]

CMD

Col Addr

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

t

DQSCKm

DQS#

DQS#

DOUT

A0

DQ

DOUT

A1

DOUT

A2

DOUT

A3

...1.6us maximum

Transitioning data

1

Figure 4.9 — LPDDR2: tDQSCKDM timing

NOTE 1 tDQSCKDMmax is defined as the maximum of ABS(tDQSCKn - tDQSCKm) for any

{tDQSCKn,tDQSCKm} pair within any 1.6us rolling window

Confidential

- 30/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

Tn

Tn+1

Tn+2

Tn+3

Tn+4

Tn+5

Tn+6

Tn+7

Tn+8

CK#

CK#

RL = 5

CA[9:0]

Bank n

col addr

CMD

Col Addr

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

t

DQSCKn

DQS#

DQS#

DOUT

A0

DQ

DOUT

A1

DOUT

A2

DOUT

A3

DOU

A

160ns maximum...

1

Tm

Tm+1

Tm+2

Tm+3

Tm+4

Tm+5

Tm+6

Tm+7

Tm+8

CK#

CK#

RL = 5

Bank n

col addr

CA[9:0]

CMD

Col Addr

READ

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

t

DQSCKm

DQS#

DQS#

DQ

DOUT

A2

DOUT

A3

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

...160ns maximum

1

Transitioning data

Figure 4.10 — LPDDR2: tDQSCKDS timing

NOTE 1 tDQSCKDSmax is defined as the maximum of ABS(tDQSCKn - tDQSCKm) for any {tDQSCKn,tDQSCKm} pair for reads

within a consecutive burst within any 160ns rolling window.

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

WL = 1

RL = 3

CA[9:0]

CMD

Bank n

col addr

Bank n

col addr

Col addr

READ

NOP

NOP

NOP

NOP

t

NOP

WRITE

NOP

NOP

t

DQSSmin

BL/2

DQSCK

Col addr

DQS#

DQS#

DQ

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

DIN

A0

DIN

A1

D

Transitioning data

Figure 4.11 — LPDDR2-SX: Burst read followed by burst write: RL = 3, WL = 1, BL = 4

The minimum time from the burst read command to the burst write command is defined by the Read Latency (RL)

Confidential

- 31/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

and the Burst Length (BL). Minimum read to write latency is RL + RU(tDQSCKmax/tCK) + BL/2 + 1 - WL clock

cycles. Note that if a read burst is truncated with a Burst Terminate (BST) command, the effective burst length of

the truncated read burst should be used as “BL” to calculate the minimum read to write delay.

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

RL = 3

CA[9:0]

Bank n

Col Addr a

Col addr a

Bank n

Col Addr b

Col addr b

t

CCD = 2

CMD

READ

NOP

READ

NOP

NOP

NOP

NOP

NOP

NOP

DQS#

DQS#

DOUT

A0

DQ

DOUT

A1

DOUT

A2

DOUT

A3

DOUT

B0

DOUT

B1

DOUT

B2

DOUT

B3

Transitioning data

Figure 4.12 — LPDDR2-SX: Seamless burst read: RL = 3, BL = 4, tCCD = 2

The seamless burst read operation is supported by enabling a read command at every other clock for BL = 4

operation, every 4 clocks for BL = 8 operation, and every 8 clocks for BL=16 operation.

For LPDDR2-SDRAM, this operation is allowed regardless of whether the accesses read the same or different

banks as long as the banks are activated.

4.4.1

Reads interrupted by a read

For LPDDR2-S4 burst read can be interrupted by another read on even clock cycles after the Read command,

provided that tCCD is met

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

RL = 3

CA[9:0]

Bank n

Col Addr a

Col addr a

Bank n

Col Addr b

Col addr b

t

CCD = 2

CMD

READ

NOP

READ

NOP

NOP

NOP

NOP

NOP

NOP

DQS#

DQS#

DQ

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

DOUT

B0

DOUT

B1

DOUT

B2

DOUT

B3

DOUT

B4

DOUT

B5

Transitioning data

Figure 4.13 — LPDDR2-SX: Read burst interrupt example: RL = 3, BL = 8, tCCD = 2

NOTE 1 For LPDDR2-S4 devices, read burst interrupt function is only allowed on burst of 8 and burst of 16.

NOTE 2 For LPDDR2-S4 devices, read burst interrupt may only occur on even clock cycles after the previous commands, provided that

tCCD is met.

NOTE 3 Reads can only be interrupted by other reads or the BST command.

NOTE 4 Read burst interruption is allowed to any bank inside DRAM.

NOTE 5 Read burst with Auto-Precharge is not allowed to be interrupted

NOTE 6 The effective burst length of the first read equals two times the number of clock cycles between the first read and the interrupting

read.

Confidential

- 32/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

4.5 Burst Write Operation

The Burst Write command is initiated by having CS# LOW, CA0 HIGH, CA1 LOW and CA2 LOW at the rising edge

of the clock. The command address bus inputs, CA5r-CA6r and CA1f-CA9f, determine the starting column address

for the burst. The Write Latency (WL) is defined from the rising edge of the clock on which the Write Command is

issued to the rising edge of the clock from which the tDQSS delay is measured. The first valid datum shall be driven

WL * tCK + tDQSS from the rising edge of the clock from which the Write command is issued. The data strobe

signal (DQS) should be driven LOW tWPRE prior to the data input. The data bits of the burst cycle must be applied

to the DQ pins tDS prior to the respective edge of the DQS, DQS# and held valid until tDH after that edge. The

burst data are sampled on successive edges of the DQS, DQS# until the burst length is completed, which is 4, 8, or

16 bit burst.

For LPDDR2-SDRAM devices, tWR must be satisfied before a precharge command to the same bank may be

issued after a burst write operation.

Input timings are measured relative to the crosspoint of DQS and its complement, DQS#.

t

t

WPRE

DQS#

DQS#

DQSH

t

VIH(DC)

VIH(AC)

t

DQSL

WPST

DQS#

DQS

VIH(AC)

DQ

DIN

VIL(AC)

t

DS

VIH(DC)

DIN

VIL(DC) tDS

t

DH

DIN

DH VIL(AC)

t

t

DS

DIN

t

DH VIL(DC) tDS

t

DH

VIH(AC)

VIH(DC)

VIH(AC)

VIH(DC)

VIL(AC)

VIL(DC)

VIL(AC)

VIL(DC)

DM

Don’t Care

Figure 4.14: Data Input (WRITE) Timing

T0

T1

T2

T3

T4

Tx

Tx+1

Ty

Ty+1

CK#

CK#

WL = 1

Bank n

col addr

CA[9:0]

CMD

Col addr

Bank n

row addr

Bank n

WRITE

NOP

t

Case 1: DQSSmax

NOP

NOP

t

t

t

DSS

DQSSmax

NOP

DSS

PRECHARGE

NOP

Row addr

ACTIVATE

NOP

Completion of burst WRITE

DQS#

DQS#

t

WR

DIN

A0

DQ

Case 2: tDQSSmin

DIN

A1

DSH

DSH

DQSSmin

DIN

A3

t

t

t

DIN

A2

t

RP

DQS#

DQS#

t

WR

DQ

DIN

A0

DIN

A1

DIN

A2

DIN

A3

Transitioning data

Figure 4.15 — LPDDR2-SX: Burst write : WL = 1, BL = 4

Confidential

- 33/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

WL = 1

CA[9:0]

Bank m

col addr a

RL = 3

Bank n

col addr b

Col addr a

Col addr b

t

WTR

CMD

WRITE

NOP

NOP

NOP

NOP

NOP

READ

NOP

NOP

DQS#

DQS#

DIN

A0

DQ

DIN

A1

DIN

A2

DIN

A3

Transitioning data

Figure 4.16 — LPDDR2-SX: Burst write followed by burst read: RL=3, WL = 1, BL = 4

NOTE 1 The minimum number of clock cycles from the burst write command to the burst read command for any bank is [WL + 1 + BL/2 +

RU( tWTR/tCK)].

NOTE 2 tWTR starts at the rising edge of the clock after the last valid input datum.

NOTE 3 If a write burst is truncated with a Burst Terminate (BST) command, the effective burst length of the truncated write burst should be

used as “BL” to calculate the minimum write to read delay.

4.5.1

Writes interrupted by a write

For LPDDR2-S4 devices, burst write can only be interrupted by another write on even clock cycles after the Write

command, provided that tCCD(min) is met.

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

WL = 1

CA[9:0]

Bank m

col addr a

Bank n

col addr b

Col addr a

Col addr b

t

CCD = 2

CMD

WRITE

NOP

WRITE

NOP

NOP

NOP

NOP

NOP

NOP

DQS#

DQS#

DQ

DIN

A0

DIN

A1

DIN

A2

DIN

A3

DIN

B0

DIN

B1

DIN

B2

DIN

B3

DIN

B4

DIN

B5

DIN

B6

DIN

B7

Transitioning data

Figure 4.17 — LPDDR2-SX: Write burst interrupt timing: WL = 1, BL = 8, t CCD = 2

NOTE 1 For LPDDR2-S4 devices, write burst interrupt function is only allowed on burst of 8 and burst of 16.

NOTE 2 For LPDDR2-S4 devices, write burst interrupt may only occur on even clock cycles after the previous write commands, provided

that tCCD(min) is met.

NOTE 3 Writes can only be interrupted by other writes or the BST command.

NOTE 4 Write burst interruption is allowed to any bank inside DRAM.

NOTE 5 Write burst with Auto-Precharge is not allowed to be interrupted

NOTE 6 The effective burst length of the first write equals two times the number of clock cycles between the first write and the interrupting

write.

Confidential

- 34/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

4.6 Burst Terminate

The Burst Terminate (BST) command is initiated by having CS# LOW, CA0 HIGH, CA1 HIGH, CA2 LOW, and CA3

LOW at the rising edge of clock. A Burst Teminate command may only be issued to terminate an active Read or

Write burst. Therefore, a Burst Terminate command may only be issued up to and including BL/2 - 1 clock cycles

after a Read or Write command. The effective burst length of a Read or Write command truncated by a BST

command is as follows: Effective burst length = 2 x {Number of clock cycles from the Read or Write Command to

the BST command}

Note that if a read or write burst is truncated with a Burst Terminate (BST) command, the effective burst length of

the truncated burst should be used as “BL” to calculate the minimum read to write or write to read delay.

The BST command only affects the most recent read or write command. The BST command truncates an ongoing

read burst RL * tCK + tDQSCK + tDQSQ after the rising edge of the clock where the Burst Terminate command is

issued. The BST command truncates an ongoing write burst WL * tCK + tDQSS after the rising edge of the clock

where the Burst Terminate command is issued.

For LPDDR2-S4 devices, the 4-bit prefetch architecture allows the BST command to be issued on an even number

of clock cycles after a Write or Read command. Therefore, the effective burst length of Read or Write command

truncated by a BST command is an integer multiple of 4.

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

WL = 1

CA[9:0]

CMD

Bank m

col addr a

Col addr a

WRITE

NOP

NOP

NOP

BST

NOP

NOP

NOP

NOP

WL x tCK + tDQSS

DQS#

DQS#

DQ

DIN

A0

DIN

A1

DIN

A2

DIN

A3

DIN

A4

DIN

A5

DIN

A6

DIN

A7

BST prohibited

Transitioning data

Figure 4.18 — LPDDR2-S4: Burst Write truncated by BST: WL = 1, BL = 16

NOTE 1 The BST command truncates an ongoing write burst WL * tCK + tDQSS after the rising edge of the clock where the

Burst Terminate command is issued.

NOTE 2 For LPDDR2-S4 devices, BST can only be issued an even number of clock cycles after the Write command.

NOTE 3 Additional BST commands are not allowed after T4 and may not be issued until after the next Read or Write command.

Confidential

- 35/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

T0

T1

T2

T3

T4

T5

T6

T7

T8

CK#

CK#

BL = 3

CA[9:0]

CMD

Bank n

col addr a

Col addr a

READ

NOP

NOP

NOP

BST

NOP

NOP

NOP

NOP

RL x tCK + tDQSCK + tDQSQ

DQS#

DQS#

DQ

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

DOUT

A4

DOUT

A5

DOUT

A6

BST prohibited

DOUT

A7

Transitioning data

Figure 4.19 — LPDDR2-S4: Burst Read truncated by BST: RL=3, BL = 16

NOTE 1 The BST command truncates an ongoing read burst RL * tCK + tDQSCK + tDQSQ after the rising edge of the clock

where the Burst Terminate command is issued.

NOTE 2 For LPDDR2-S4 devices, BST can only be issued an even number of clock cycles after the Read command.

NOTE 3 Additional BST commands are not allowed after T4 and may not be issued until after the next Read or Write

command.

Confidential

- 36/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

4.7 Write Data Mask

One write data mask (DM) pin for each data byte (DQ) will be supported on LPDDR2 devices, consistent with the

implementation on LPDDR SDRAMs. Each data mask (DM) may mask its respective data byte (DQ) for any given

cycle of the burst. Data mask has identical timings on write operations as the data bits, though used as input only,

is internally loaded identically to data bits to insure matched system timing.

Data Mask Timing

DQS#

DQS#

DQ

t

t

DS

t

DH

DS

t

DH

VIH(AC)

VIH(DC) VIH(AC)

VIH(DC)

VIL(AC)

VIL(DC) VIL(AC)

VIL(DC)

CMD

Don't care

Data Mask Function, WL = 2, BL = 4 shown, second DQ masked

CK#

CK#

t

WR

WL = 2

CMD

Case 1: tDQSSmin

t

WTR

WRITE

t

DQSSmin

DQS#

DQS#

DQ

DOUT 0

DOUT 1

DOUT 2

DOUT 3

DM

Case 2: tDQSSmax

t

DQSSmax

DQS#

DQS#

DQ

DOUT 0

DOUT 1

DOUT 2

DOUT 3

DM

Don't care

Figure 4.20 — LPDDR2-SX: Write data mask

Confidential

- 37/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

4.8 LPDDR2-SX: Precharge operation

The Precharge command is used to precharge or close a bank that has been activated. The Precharge command

is initiated by having CS# LOW, CA0 HIGH, CA1 HIGH, CA2 LOW, and CA3 HIGH at the rising edge of the clock.

The Precharge Command can be used to precharge each bank independently or all banks simultaneously. For 4bank devices, the AB flag, and the bank address bits, BA0 and BA1, are used to determine which bank(s) to

precharge. For 8-bank devices, the AB flag, and the bank address bits, BA0, BA1, and BA2, are used to determine

which bank(s) to precharge. The bank(s) will be available for a subsequent row access tRPab after an All-Bank

Precharge command is issued and tRPpb after a Single-Bank Precharge command is issued.

In order to ensure that 8-bank devices do not exceed the instantaneous current supplying capability of 4-bank

devices, the Row Precharge time (tRP) for an All-Bank Precharge for 8-bank devices (tRPab) will be longer than

the Row Precharge time for a Single-Bank Precharge (tRPpb). For 4-bank devices, the Row Precharge time (tRP)

for an All-Bank Precharge (tRPab) is equal to the Row Precharge time for a Single-Bank Precharge (tRPpb).

Figure 4-1 shows Activate to Precharge timing.

Table 8 – Bank selection for Precharge by address bits

AB (CA4r)

BA2 (CA9r)

BA1 (CA8r)

BA0 (CA7r)

Precharged Bank(s)

4-bank device

Precharged Bank(s)

8-bank device

0

0

0

0

0

0

0

0

1

0

0

0

0

1

1

1

1

Don't care

0

0

1

1

0

0

1

1

Don't care

0

1

0

1

0

1

0

1

Don't care

Bank 0 only

Bank 1 only

Bank 2 only

Bank 3 only

Bank 0 only

Bank 1 only

Bank 2 only

Bank 3 only

All Banks

Bank 0 only

Bank 1 only

Bank 2 only

Bank 3 only

Bank 4 only

Bank 5 only

Bank 6 only

Bank 7 only

All Banks

4.8.1 LPDDR2-SX: Burst Read operation followed by Precharge

For the earliest possible precharge, the precharge command may be issued BL/2 clock cycles after a Read

command. For an untruncated burst, BL is the value from the Mode Register. For a truncated burst, BL is the

effective burst length. A new bank active (command) may be issued to the same bank after the Row Precharge

time (tRP). A precharge command cannot be issued until after tRAS is satisfied.

For LPDDR2-S4 devices, the minimum Read to Precharge spacing has also to satisfy a minimum analog time from

the rising clock edge that initiates the last 4-bit prefetch of a Read command. This time is called tRTP (Read to

Precharge).

For LPDDR2-S4 devices, tRTP begins BL/2 - 2 clock cycles after the Read command. If the burst is truncated by a

BST command or a Read command to a different bank, the effective “BL” shall be used to calculate when tRTP

begins.

See Table 9 for Read to Precharge timings for LPDDR2-S4

Confidential

- 38/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

T0

T1

T2

CK#

CK#

T3

T4

T5

T6

T7

T8

addr

RL = 3

BL/2

CA[9:0]

Bank m

col addr a

Bank m

row addr

Bank m

Col addr a

t

t

RTP

CMD

READ

NOP

NOP

NOP

Row

RP

PRECHARGE

NOP

NOP

ACTIVATE

NOP

DQS#

DQS#

DOUT

A0

DQ

DOUT

A1

DOUT

A2

DOUT

A3

DOUT

A4

DOUT

A5

DOUT

A6

DOUT

A7

Transitioning data

Figure 4.21 — LPDDR2-S4: Burst read followed by Precharge:

RL = 3, BL = 8, RU(tRTP(min)/tCK) = 2

CK#

CK#

T0

T1

T2

T3

T4

T5

T6

T7

T8

BL/2

RL = 3

CA[9:0]

Bank m

col addr a

Bank m

row addr

Bank m

Col addr a

t

RTP=3

CMD

READ

NOP

Row addr

t

RP

NOP

PRECHARGE

NOP

NOP

ACTIVATE

NOP

NOP

DQS#

DQS#

DQ

DOUT

A0

DOUT

A1

DOUT

A2

DOUT

A3

Transitioning data

Figure 4.22 — LPDDR2-S4: Burst read followed by Precharge: RL = 3, BL = 4, RU(tRTP(min)/tCK) = 3

4.8.2

LPDDR2-SX: Burst Write followed by Precharge

For write cycles, a delay must be satisfied from the time of the last valid burst input data until the Precharge

command may be issued. This delay is known as the write recovery time (tWR) referenced from the completion of

the burst write to the precharge command. No Precharge command to the same bank should be issued prior to the

tWR delay.

LPDDR2-S4 devices write data to the array in prefetch quadruples (prefetch = 4). The beginning of an internal write

operation may only begin after a prefetch group has been latched completely. Therefore, the write recovery time

(tWR) starts at different boundaries for LPDDR2-S4 devices.

For LPDDR2-S4 devices, minimum Write to Precharge command spacing to the same bank is WL + BL/2 + 1 +

RU(tWR/tCK) clock cycles. For an untruncated burst, BL is the value from the Mode Register. For an truncated

burst, BL is the effective burst length.

See Table 9 for Write to Precharge timings for LPDDR2-S4

Confidential

- 39/129 -

Rev.1.0 July 2016

�AS4C64M16MD2-25BCN

AS4C32M32MD2-25BCN

!

!

T0

T1

T2