ASFC4G31M-51BIN

Revision History

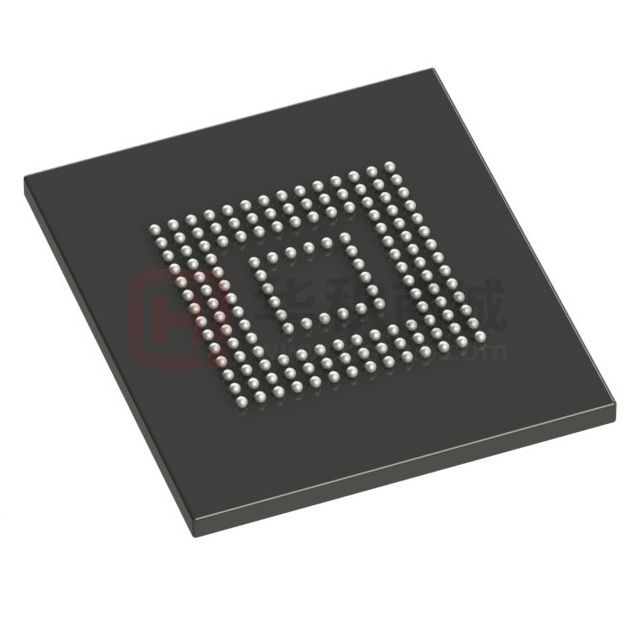

4GB eMMC 153ball FBGA PACKAGE

Revision Details

Rev 1.0

Initial Release

Confidential

Date

Dec. 2021

-1/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

CONTENTS

1 Product Overview ............................................................................................................................................ 5

1.1 Product Description .................................................................................................................................................... 5

1.2 Product Ordering Information .................................................................................................................................. 5

1.3 Key Features................................................................................................................................................................ 6

2 Package Information ........................................................................................................................................ 7

2.1 Package Dimension ..................................................................................................................................................... 7

2.2 Ball & Signal Assignment ............................................................................................................................................. 8

2.3 Product Architecture................................................................................................................................................. 10

3 Technical Notes ..............................................................................................................................................11

3.1 HS400 Interface......................................................................................................................................................... 11

3.2 Partition Management .............................................................................................................................................. 11

3.2.1 Boot Area Partition and RPMB Area Partition ................................................................................................... 11

3.2.2 Enhanced Partition (Area) .................................................................................................................................. 12

3.2.3 User Density ....................................................................................................................................................... 12

3.3 Boot operation .......................................................................................................................................................... 12

3.4 Field Firmware Upgrade (FFU) .................................................................................................................................. 14

3.5 Cache......................................................................................................................................................................... 14

3.6 Packed Commands .................................................................................................................................................... 14

3.7 Secure Delete ............................................................................................................................................................ 14

3.7.1 Sanitize ............................................................................................................................................................... 14

3.7.2 Secure Erase ....................................................................................................................................................... 14

3.7.3 Secure Trim ........................................................................................................................................................ 14

3.8 High Priority Interrupt (HPI) ...................................................................................................................................... 15

3.9 Device Health ............................................................................................................................................................ 15

3.10 Auto Power Saving Mode........................................................................................................................................ 15

3.11 Enhanced Strobe ..................................................................................................................................................... 16

3.12 Performance ........................................................................................................................................................... 16

4 Register Value.................................................................................................................................................17

4.1 OCR Register ............................................................................................................................................................. 17

4.2 CID Register ............................................................................................................................................................... 17

4.2.1 Product name table (In CID Register)................................................................................................................. 18

4.3 RCA Register .............................................................................................................................................................. 19

4.4 CSD Register .............................................................................................................................................................. 19

Confidential

-2/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

4.5 Extended CSD Register (EXT_CSD) ............................................................................................................................ 21

5 AC Parameter .................................................................................................................................................30

5.1 Timing Parameter...................................................................................................................................................... 30

5.2 Bus Timing Specification in HS400 mode .................................................................................................................. 31

5.2.1 HS400 Device Input Timing ................................................................................................................................ 31

5.2.2 HS400 Device Output Timing ............................................................................................................................. 32

5.3 Bus Signal Levels ....................................................................................................................................................... 33

6 DC Parameter .................................................................................................................................................34

6.1 Power Consumption.................................................................................................................................................. 34

6.2 Supply Voltage .......................................................................................................................................................... 34

6.3 Bus Signal Line Load .................................................................................................................................................. 35

7 Power Delivery And Capacitor Specifications ...................................................................................................36

7.1 Power Domains ......................................................................................................................................................... 36

7.2 Capacitor Connection Guidelines .............................................................................................................................. 36

8 Part number system ........................................................................................................................................39

FIGURE CONTENTS

Figure 1. 11.5 x 13.0 x 1.0 (mm) Package Dimension ................................................................................................... 7

Figure 2. eMMC Package Ball Assignment .................................................................................................................... 8

Figure 3. ASFC4G31M-51BIN Block Diagram .............................................................................................................. 10

Figure 4. embedded MultiMediaCard state diagram (boot mode) ............................................................................ 13

Figure 5. embedded MultiMediaCard state diagram (alternative boot mode) .......................................................... 13

Figure 6. HS400 Device Input Timing Diagram............................................................................................................ 31

Figure 7. HS400 Device Output Timing Diagram ......................................................................................................... 32

Figure 8. Bus Signal Levels........................................................................................................................................... 33

Figure 9. Recommended Power Domain Connections ............................................................................................... 38

Confidential

-3/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

TABLE CONTENTS

Table 1. Ordering Information ...................................................................................................................................... 5

Table 2. Ball & Signal Assignment ................................................................................................................................. 8

Table 3. Setting sequence of Boot Area Partition size and RPMB Area Partition size ................................................ 11

Table 4. Capacity according to partition ..................................................................................................................... 12

Table 5. Maximum Enhanced Partition Size................................................................................................................ 12

Table 6. User Density Size ........................................................................................................................................... 12

Table 7. Boot ack, boot data and initialization Time................................................................................................... 13

Table 8. Auto Power Saving Mode enter and exit ...................................................................................................... 15

Table 9. Auto Power Saving Mode and Sleep Mode ................................................................................................... 15

Table 10. Sustained Sequential Performance ............................................................................................................. 16

Table 11. OCR Register ................................................................................................................................................ 17

Table 12. CID Register ................................................................................................................................................. 18

Table 13. Product name table ..................................................................................................................................... 18

Table 14. ASFC4G31M-51BIN Typical CSD Register..................................................................................................... 19

Table 15. ASFC4G31M-51BIN Typical EXT_CSD Register ............................................................................................. 21

Table 16. Timing Parameter ........................................................................................................................................ 30

Table 17. HS400 Device Input Timing ......................................................................................................................... 31

Table 18. HS400 Device Output Timing ...................................................................................................................... 32

Table 19. Bus Signal Levels .......................................................................................................................................... 33

Table 20. Active Power Consumption during operation ............................................................................................. 34

Table 21. Standby Power Consumption in auto power saving mode and standby state ........................................... 34

Table 22. Sleep Power Consumption in Sleep State ................................................................................................... 34

Table 23. Supply Voltage ............................................................................................................................................. 34

Table 24. Bus SIgnal Line Load .................................................................................................................................... 35

Table 25. Capacitance and Resistance for HS400 mode ............................................................................................. 35

Table 26. Power Domains ........................................................................................................................................... 36

Table 27. Part number system .................................................................................................................................... 39

Confidential

-4/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

1 Product Overview

1.1 Product Description

Alliance Memory's 4GB eMMC device (AS04FC) is a high performance embedded MMC solution designed for

embedded NAND flash applications. It supports eMMC/JEDEC 5.1 industry standard and is backward compatible with

eMMC 4.5 & 5.0 version.

AS04FC device contains both MLC NAND flash and eMMC controller. A single 3V supply voltage is for the NAND area

(VCC) with internal regulator and Dual supply voltages 1.8V or 3V (VCCQ) for eMMC controller. Customers find it easy

to use AS04FC without having to consider any changes inside device such as Flash, leading to easier & faster

development of applications (fast time to market).

Alliance Memory’s featured embedded flash management software or FTL(Flash Transition Layer) of eMMC manages

high reliability with noticeable Wear Leveling, Bad Block Management and strong ECC and achieves high

performance.

1.2 Product Ordering Information

Table 1. Ordering Information

Capacities

(GB)

4

Part Number

ASFC4G31M-51BIN

eMMC

NAND

Version

Die

5.1

32Gb x 1

Temperature

Industrial Grade

-40OC ~ 85OC

Package Size

Package

(mm)

Type

11.5x13.0x1.0

153ball

FBGA

Note1. HS200/HS400 can be supported at only VCCQ 1.8V

Confidential

-5/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

1.3 Key Features

Supports features of eMMC5.1 which are defined in JEDEC Standard

- Supported Features : Boot, RPMB, Write Protection, DDR, HS200, Multi-partitioning, Secure Erase/Trim,

Trim, HPI, Background operation, Enhance Reliable Write, Discard, Sanitize, Security features, Partition

types, Packed commands, Real time clock, Dynamic device capacity, Power off notification, Thermal spec,

Cache, HS400, Field Firmware Update, Security Removal type, Device Health Report, Enhanced Strobe,

Command Queuing, Secure Write protection

- Non-supported Features : Large Sector Size (4KB)

Supports Enhanced Strobe feature of new eMMC standard of version 5.1.

Full backward compatibility with previous eMMC 4.41/4.5/5.0 specification and MultiMediaCard

system specification (1bit data bus, multi-eMMC systems)

Programmable bus width : 1bit (Default), 4bit and 8bit Data bus.

MMC I/F Clock Frequency : 0 ~ 200MHz

MMC I/F Boot Frequency : 0 ~ 52MHz

Operating Temperature : -40OC ~ 85OC

Storage Temperature : -40OC ~ 85OC

Operating Power Supply

VCC : 2.7V ~ 3.6V (for NAND Flash Memory)

VCCQ : 1.7V ~ 1.95V or 2.7V ~ 3.6V (for Interface)

Confidential

-6/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

2 Package Information

2.1 Package Dimension

Figure 1. 11.5 x 13.0 x 1.0 (mm) Package Dimension

Confidential

-7/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

2.2 Ball & Signal Assignment

Figure 2. eMMC Package Ball Assignment

1

2

3

4

5

6

7

8

9

10

11

12

13

14

A

NC

NC

DAT0

DAT1

DAT2

VSS

RFU

NC

NC

NC

NC

NC

NC

NC

A

B

NC

DAT3

DAT4

DAT5

DAT6

DAT7

NC

NC

NC

NC

NC

NC

NC

NC

B

C

NC

VDDI

NC

VSSQ

NC

VCCQ

NC

NC

NC

NC

NC

NC

NC

NC

C

D

NC

NC

NC

NC

NC

NC

NC

D

E

NC

NC

NC

RFU

RFU

NC

NC

NC

E

F

NC

NC

NC

VCC

RFU

NC

NC

NC

F

G

NC

NC

RFU

VSS

RFU

NC

NC

NC

G

H

NC

NC

NC

DS

VSS

NC

NC

NC

H

J

NC

NC

NC

VSS

VCC

NC

NC

NC

J

K

NC

NC

NC

RSTN

RFU

NC

NC

NC

K

L

NC

NC

NC

NC

NC

NC

L

M

NC

NC

NC

VCCQ

CMD

CLK

NC

NC

NC

NC

NC

NC

NC

NC

M

N

NC

VSSQ

NC

VCCQ

VSSQ

NC

NC

NC

NC

NC

NC

NC

NC

NC

N

P

NC

NC

VCCQ

VSSQ

VCCQ

VSSQ

RFU

NC

NC

RFU

NC

NC

NC

NC

P

1

2

3

4

5

6

7

8

9

10

11

12

13

14

No

Signal

A3

DAT0

A4

DAT1

A5

DAT2

B2

DAT3

B3

DAT4

Confidential

Type

I/O

VCC

RFU

VSS

RFU

RFU

VSS

RFU

VCC

Table 2. Ball & Signal Assignment

Description

Bidirectional channel used for data transfer

-8/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

B4

DAT5

B5

DAT6

B6

DAT7

Command: A bidirectional channel used for device initialization and command

M5

CMD

I/O

transfers. Command operates in two modes, open-drain for initialization and push-pull

for fast command transfer.

M6

CLK

K5

RSTN

H5

Data

Strobe

E6

VCC

F5

VCC

J10

VCC

K9

VCC

C6

VCCQ

M4

VCCQ

N4

VCCQ

P3

VCCQ

P5

VCCQ

E7

VSS

G5

VSS

H10

VSS

K8

VSS

A6

VSS

J5

VSS

C4

VSSQ

N2

VSSQ

N5

VSSQ

P4

VSSQ

P6

VSSQ

C2

VDDi

I

Clock: Each cycle directs a 1-bit transfer on the command and DAT lines

Hardware reset signal pin

O

Data Strobe : Supports Enhanced strobe of eMMC ver. 5.1

P

Flash I/O and memory power supply

P

Memory controller core and MMC I/F I/O power supply

P

Flash I/O and memory ground connection

P

Memory controller core and MMC I/F ground connection

Internal power node. Connect 0.1uF capacitor from VDDi to ground

NOTE

I/O = Bi-direction, I = Input, O = Output, P = Power/Analog, RFU = Reserved for Future Use

Confidential

-9/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

2.3 Product Architecture

eMMC consists of NAND Flash and Controller. VCCQ is for Controller power and VCC is for Flash power

Figure 3. ASFC4G31M-51BIN Block Diagram

Confidential

-10/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

3 Technical Notes

3.1 HS400 Interface

Support HS400 DDR interface timing mode to achieve a bus speed of 400 MB/s at 200MHz clock frequency with

8bit bus width only and the 1.7 ~ 1.95V VCCQ option. At this mode, the host may need to have an adjustable sampling

point to reliably receive the incoming data, due to the speed. Please refer to JESD84-B50-1 standard for

additional information.

3.2 Partition Management

The device initially consists of two Boot partitions, RPMB(Replay Protected Memory Block) partition and User Data

Area. Both Boot and RPMB area have fixed size of area and can’t be adjusted.

Boot

Partition #1,

RPMB

#2

①

②

Enhanced

User Data

Area

4 General Purpose Partitions (GPP)

③

④

User Density

3.2.1 Boot Area Partition and RPMB Area Partition

The device has fixed size of Boot and RPMB area.

Boot partition size is calculated as (128KB * BOOT_SIZE_MULT)

The size of Boot Area Partition 1 and 2 cannot be set independently. It is set as same value.

RPMB partition size is calculated as (128KB * RPMB_SIZE_MULT).

In RPMB partition, CMD 0, 6, 8, 12, 13, 15, 18, 23, 25 are admitted.

Access Size of RPMB partition is defined as the below:

Table 3. Setting sequence of Boot Area Partition size and RPMB Area Partition size

REL_WR_SEC_C

Description

REL_WR_SEC_C = 1

Access sizes 256B and 512B supported to RPMB partition

REL_WR_SEC_C > 1

Access sizes up to REL_WR_SEC_C * 512B supported to RPMB partition with 256B granularity

Any undefined set of parameters or sequence of commands results in failure access.

If the failure is in data programming case, the data is not programmed.

If the failure occurs in data read case, the read data is ‘0x00’.

Confidential

-11/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Table 4. Capacity according to partition

Device

Boot partition 1

Boot partition 2

RPMB

[KB]

[KB]

[KB]

4,096

4,096

4,096

4GB

3.2.2 Enhanced Partition (Area)

Alliance 4GB eMMC applies SLC Mode for Enhanced User Data Area and it leads to occupying double size of original

set up size if master set some area of User Data Area as enhanced user area. For example, if master set 1MB as

enhanced mode, then, total 2MB of user data area is used for it. Max Enhanced user Data Area follows below formula

of JESD84-B50-1.

Max Enhanced User Data Area size is defined as (MAX_ENH_SIZE_MULT x HC_WP_GRP_SIZE x HC_ERASE_GRP_SIZE x 512Kbytes)

Table 5. Maximum Enhanced Partition Size

Device

LBA [Hex]

LBA [Dec.]

Max. Enhanced Partition Size

4GB

0x390000

3735552

1842MB

3.2.3 User Density

As mentioned in 3.2.2 Enhanced Partition(Area) section, total User Density depends on partition type to be set.

Alliance’s 4GB applies SLC mode for Enhanced user area and so, assigning any size for it occupies double of that

value assigned. For example, assigning 64MB in the SLC mode takes 128MB of capacity in MLC.

Device

LBA [Hex]

4GB

0x720000

Table 6. User Density Size

LBA [Dec.]

7471104

User Partition Size

3648MB

3.3 Boot operation

Device supports not only boot mode but also alternative boot mode. Device supports high speed timing and dual data

rate during boot.

Confidential

-12/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Figure 4. embedded MultiMediaCard state diagram (boot mode)

CLK

CMD

CMD1

DAT[0]

Boot

ACK

Time

S

010

E

RESP

CMD2

RESP

S 512B + CRC E

Boot terminated

Min 8 clocks + 48

clocks = 56 clocks

required from CMD

signal high to next

MMC command.

Boot Data Time

Figure 5. embedded MultiMediaCard state diagram (alternative boot mode)

CLK

CMD

CMD0

DAT[0]

CMD0 Reset

Boot

ACK

Time

Min 74 Clocks

required

after power is

stable to start

boot

command

S

010

E

CMD1

RESP

CMD2

S 512B + CRC E

Boot terminated

CMD1

Time

Boot Data Time

Table 7. Boot ack, boot data and initialization Time

Timing Factor

Value

(1) Boot ACK Time

< 50 ms

(2) Boot Data Time

< 1 sec

(3) Initialization Time

< 1 sec

NOTE

1) The value for this initialization time is for such case which includes partition setting also. For details, please refer

to INI_TIMEOUT_AP in Extended CSD Register of JESD84-B50-1.

Normal initialization time (without partition setting) is completed within 1sec

Confidential

-13/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

3.4 Field Firmware Upgrade (FFU)

Field Firmware Updates (FFU) is for customer’s FW updating in field for those cases of debugging, enhancing and

adding new features of FW itself. The host can download a new version of the firmware into the eMMC device by this

mechanism and whole FFU process can happen without affecting any user/OS data, even in parallel with Host’s

performing other operations.

Refer to JEDEC Standards No. JESD84-B50-1 for additional information.

3.5 Cache

This device supports 128KB of volatile memory as an eMMC cache for performance improvement of both sequential

and random access. For additional information please refer to JESD84-B50 standard.

3.6 Packed Commands

This device supports packed commands feature of eMMC standard version 5.0 and allows the host to pack Read or

Write commands into groups (of single type of operation) and transfer these to the device in a single transfer on the

bus, which leads reducing overall bus overheads and thus, enables optimal system performance.

Please refer to JESD84-B50 for information details.

3.7 Secure Delete

3.7.1 Sanitize

The device supports Sanitize operation for removing data from the unmapped user address space in the device,

physically. Device keeps the sanitize operation until one of the following events occurs, with keeping busy asserted,

Sanitize operation is complete

HPI is used to abort the operation

Power failure

Hardware reset

No data should exist in the unmapped host address space after the sanitize operation is completed.

3.7.2 Secure Erase

This device supports the optional Secure Erase command, which is for backward compatibility reasons, as well as

standard erase command. Host will erase provided range of LBAs and ensure no older copies of this data exist in the

flash with this command.

Please refer to JEDEC Standards No. JESD84-B50 for more information.

3.7.3 Secure Trim

This device supports Secure Trim command which is similar to the Secure Erase command but different in that

performs a secure purge operation on write blocks instead of erase groups. This is for backward compatibility reasons.

Confidential

-14/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

The secure trim command is performed in two steps:

1) Mark the LBA range as candidate for erase.

2) Do Erase the marked address range and then, ensure no old copies are left within that range. .

For additional information refer to JEDEC Standards No. JESD84-B50.

3.8 High Priority Interrupt (HPI)

This device supports High Priority Interrupt and prevent problem of Host being stalled due to too much delayed Write

operation by new paging request of operating system, by user. It will delay the request for new paging until currently

going write operation is completed.

Please refer to JEDEC Standards No. JESD84-B50 for more information.

3.9 Device Health

This device supports Device Health Report feature which is featured to others in that separately report SLC type area

and other area by each bytes of DEVICE_LIFE_TIME_EST_TYP_A[268] and

DEVICE_LIFE_TIME_EST_TYP_A[269], respectively. It can be queried by standard MMC command for getting Extended

CSD structure. Please refer to below and JEDEC Standards No. JESD84-B50 for details.

DEVICE_LIFE_TIME_EST_TYP_A[268], The host may use it to query health information of SLC area

DEVICE_LIFE_TIME_EST_TYP_B[269], The host may use it to query health information of other partition area.

3.10 Auto Power Saving Mode

This device supports Auto Power Saving Mode which can save power consumption. Device will enter this mode if host

does not issue any command during 20ms, after completion of previously issued command.

Any newly issued commands during this mode will be carried normally.

Mode

Auto Power Saving Mode

Table 8. Auto Power Saving Mode enter and exit

Enter Condition

Escape Condition

When previous operation which came from Host is

If Host issues any command

completed and no command is issued during a certain time.

Table 9. Auto Power Saving Mode and Sleep Mode

Auto Power Saving Mode

Sleep Mode

Confidential

NAND Power

ON

ON/OFF

GotoSleep Time

< 100ms

< 1ms

-15/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

3.11 Enhanced Strobe

Alliance 4GB eMMC supports Enhanced Strobe which is new feature of eMMC version 5.1 standard to

synchronize CMD response. Host shall support this feature and it enables faster and more reliable operation.

For more information, please refer to JEDEC Standards No. JESD84-B50.

3.12 Performance

Table 10. Sustained Sequential Performance

Capacity (GB)

Sequential Read (MB/s)

Sequential Write (MB/s)

4

120

50

NOTE

Test Condition: Bus width x8, HS400, 512KB data transfer, Packed Off, Cache On, w/o file

system overhead, measured on Alliance’s internal board at Clean Case(WAI=1)

Confidential

-16/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

4 Register Value

Following sections are for describing all register value of eMMC device at its default in the AS04FC. And these

values here may be updated in later version without notice.

There are defined total six registers in this section: OCR, CID, CSD, EXT_CSD, RCA and DSR. All of them has its own

commands corresponded and for details, please refer JEDEC Standards No. JESD84-B50 for details. The OCR, CID and

CSD registers has information of device and content, while the RCA and DSR registers are for configuring parameters of

device. For the EXT_CSD register, it contains both device specific information and actual configuration parameters.

4.1 OCR Register

The operation conditions register (OCR) contains: VCC voltage profile of the device, access mode indication, status

information bit. The status bit is set when the device finished its power up procedure.

All eMMC devices shall have this register implemented.

Table 11. OCR Register

OCR bit

VCCQ Voltage Window2

Register Value

[6:0]

Reserved

00 00000b

[7]

1.70 ~ 1.95

1b

[14:8]

2.0 ~ 2.6

000 0000b

[23:15]

2.7 ~ 3.6

1 1111 1111b

[28:24]

Reserved

0 0000b

[30:29]

Access Mode

[31]

00b (byte mode) -[2GB]

10b (sector mode) -[*Higher than 2GB only]

eMMC power up status bit (busy)1

NOTE

1) This bit is set to LOW if the eMMC has not finished the power up routine.

2) The voltage for internal flash memory(VCC) should be 2.7 ~ 3.6V regardless of OCR register value.

4.2 CID Register

The device Identification (CID) register is 128bits wide. It contains the device identification information used during the

device identification phase (eMMC protocol). eMMC device shall have a unique identification number.

Users can define their own CID register and the CID contents will be programmed into the eMMC device when

firmware fusing process. After the programming is complete, end users cannot change CID, unless the whole foundry

production program is re-done. Users can install the new downloaded firmware into the device by using FFU (Field

Firmware Update) mode.

Confidential

-17/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Table 12. CID Register

Name

Field

Width

CID-slice

CID Value

Manufacturer ID

MID

8

[127:120]

0x52

6

[119:114]

---

Reserved

Card/BGA

CBX

2

[113:112]

0x01

OEM/Application ID

OID

8

[111:104]

0x52

Product name

PNM

48

[103:56]

Product revision

PRV

8

[55:48]

0x01

Product serial number

PSN

32

[47:16]

---3

Manufacturing date

MDT

8

[15:8]

---4

CRC7 checksum

CRC

7

[7:1]

---5

not used, always ’1’

-

1

[0:0]

---

4GB :” AS04FC”

0x415330344643

NOTE

1),4),5) description are same as eMMC JEDEC standard

2) PRV is composed of the revision count of controller and the revision count of F/W patch

3) A 32 bits unsigned binary integer. (Random and Manufacture Number)

4.2.1 Product name table (In CID Register)

Part Number

ASFC4G31M-51BIN

Confidential

Table 13. Product name table

Density

Product Name in CID Register

PKG

(GB)

(PNM)

Type

4

AS04FC

11.5x13.0x1.0

-18/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

4.3 RCA Register

The writable 16-bit relative device address (RCA) register carries the device address assigned by the host during the

device identification. This address is used for the addressed host-device communication after the device identification

procedure. The default value of the RCA register is 0x0001. The value 0x0000 is reserved to set all devices into the

Stand-by State with CMD7.

4.4 CSD Register

The device Specific Data (CSD) register provides information on how to access the device contents. The CSD defines the

data format, error correction type, maximum data access time, data transfer speed, whether the DSR register can be

used etc. The programmable part of the register (entries marked by W or E) can be changed by CMD27.

The CSD register defines the behavior or of eMMC devices. The eMMC behavior is related to the controller design.

The following table shows a typical CSD definition of ASFC4G31M-51BIN based eMMC. If users need to add on more

features, firmware or hardware modifications may be necessary.

※Note that the register values are preliminary data and may be updated in a later version. And the updated value will

be supported by specified application note later.

Table 14. ASFC4G31M-51BIN Typical CSD Register

Name

Field

Bit

CSD structure

CSD_STRUCTURE

2

System specification version

SPEC_VERS

4

Reserved

2

Data read access-time 1

TAAC

8

Data read access-time 2 in CLK cycles (NSAC x 100)

NSAC

8

Max. bus clock frequency

TRAN_SPEED

8

Device command classes

CCC

12

Max. read data block length

READ_BL_LEN

4

Partial blocks for read allowed

READ_BL_PARTIAL

1

Write block misalignment

WRITE_BLK_MISALIGN 1

Read block misalignment

READ_BLK_MISALIGN

1

DSR implemented

DSR_IMP

1

Reserved

2

Device size

C_SIZE

12

Max read current@VCCQ min

VCCQ_R_CURR_MIN

3

Max read current@VCCQ max

VCCQ_R_CURR_MAX

3

Max write current@VCCQ min

VCCQ_W_CURR_MIN

3

Max write current@VCCQ max

VCCQ_W_CURR_MAX

3

Device size multiplier

C_SIZE_MULT

3

Erase group size

ERASE_GRP_SIZE

5

Erase group size multiplier

ERASE_GRP_MULT

5

Write protect group size

WP_GRP_SIZE

5

Confidential

-19/39-

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Slice

Value Note

3h

[127:126]

4h

[125:122]

[121:120]

27h

[119:112]

[111:104] 01h

32h

[103:96]

0F5h

[95:84]

9h

[83:80]

0h

[79:79]

0h

[78:78]

0h

[77:77]

0h

[76:76]

[75:74]

FFFh

[73:62]

7h

[61:59]

7h

[58:56]

7h

[55:53]

7h

[52:50]

7h

[49:47]

1Fh

[46:42]

1Fh

[41:37]

0Fh

[36:32]

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Name

Write protect group enable

Manufacturer default ECC

Write speed factor

Max. write data block length

Partial blocks for write allowed

Reserved

Content protection application

File format group

Copy flag (OTP)

Permanent write protection

Temporary write protection

File format

ECC code

CRC

Not used, always ‘1’

Field

Bit Type

WP_GRP_ENABLE

1

R

DEFAULT_ECC

2

R

R2W_FACTOR

3

R

WRITE_BL_LEN

4

R

WRITE_BL_PARTIAL

1

R

4

R

CONTENT_PROT_APP

1

R

FILE_FORMAT_GRP

1

R/W

COPY

1

R/W

PERM_WRITE_PROTECT 1

R/W

TMP_WRITE_PROTECT 1 R/W/E

FILE_FORMAT

2

R/W

ECC

2 R/W/E

CRC

7 R/W/E

1

-

Slice

[31:31]

[30:29]

[28:26]

[25:22]

[21:21]

[20:17]

[16:16]

[15:15]

[14:14]

[13:13]

[12:12]

[11:10]

[9:8]

[7:1]

[0:0]

Value Note

1h

0h

2h

9h

0h

0h

0h

0h

0h

0h

0h

0h

-

NOTE

: The type of the CSD Registry entries in the Table 14 is coded as follows.

R: Read only

W: One time programmable and not readable

R/W: One time programmable and readable

W/E: Multiple writable with value kept after power failure, H/W reset assertion and any CMD0 reset and not readable.

R/W/E: Multiple writable with value kept after power failure, H/W reset assertion and any CMD0 reset and readable.

R/W/C_P: Writable after value cleared by power failure and HW/rest assertion (the value not cleared by CMD0 reset)

and readable.

R/W/E_P: Multiple writable with value reset after power failure, H/W reset assertion and any CMD0 reset and readable.

W/E_P: Multiple writable with value reset after power failure, H/W reset assertion and any CMD0 reset and not

readable.

Confidential

-20/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

4.5 Extended CSD Register (EXT_CSD)

The Extended CSD register defines the additional behavior of eMMC devices due to limited CSD information. The

following table shows a typical extended CSD definition of ASFC4G31M-51BIN based eMMC. If users need to add on

more features, firmware or hardware modifications may be necessary.

−Note that the register values are preliminary data and may be updated in a later version. And the updated value will

be supported by specified application note later.

Table 15. ASFC4G31M-51BIN Typical EXT_CSD Register

Name

Field

Byte

Type

Slice

Value

Note

Reserved

-

6

-

[511:506]

-

Extended Security

Commands Error

EXT_SECURITY_ERR

1

R

[505]

0h

Supported command sets

S_CMD_SET

1

R

[504]

1h

Allocated by MMCA

HPI features

HPI_FEATURES

1

R

[503]

1h

HPI type CMD13

Background operations

support

BKOPS_SUPPORT

1

R

[502]

1h

BKOPS supported

Max packed read

commands

Max packed write

commands

MAX_PACKED_READS

1

R

[501]

3Fh

MAX_PACKED_WRITES

1

R

[500]

3Fh

Max. 63 commands

in a packed cmd

Max. 63 commands

in a packed cmd

Data Tag Support

DATA_TAG_SUPPORT

1

R

[499]

1h

Tag Unit Size

TAG_UNIT_SIZE

1

R

[498]

0h

Tag Resources Size

TAG_RES_SIZE

1

R

[497]

0h

Context management

CONTEXT_CAPABILITIES

1

R

[496]

78h

Support Data Tag

Max Tag Size = 8*2

= 16MB

capabilities

Max_Context ID = 8

Large Unit size

LARGE_UNIT_SIZE_M1

1

R

[495]

1h

1MB*2=2MB

Extended partitions

EXT_SUPPORT

1

R

[494]

3h

Support "System

attribute support

code" and

"Non-persistent"

Supported modes

SUPPORTED_MODES

1

R

[493]

1h

FFU features

FFU_FEATURES

1

R

[492]

0h

Operation codes timeout

OPERATION_CODE_TIMEO

UT

1

R

[491]

17h

FFU Argument

FFU_ARG

4

R

Confidential

-21/39-

FFU is supported

(2^23)*100us =

838.86s

[490:487] FFFAFFF0h

Rev.1.0 December 2021

�ASFC4G31M-51BIN

1

R

[486]

1h

177

-

[485:309]

-

CMDQ_SUPPORT

1

R

[308]

1h

CMD Queuing Depth

CMDQ_DEPTH

1

R

[307]

1Fh

Reserved

-

1

-

[306]

4

R

[305:302]

0000h

correctly programmed

NUMBER_OF_FW_SECTOR

S_CORRECTLY_PROGRAM

MED

Vendor proprietary health

report

VENDOR_PROPRIETARY_H

EALTH_REPORT

32

R

[301:270]

TBD

Device life time estimation

type B

Device life time estimation

type A

DEVICE_LIFE_TIME_EST_T

YP_B

DEVICE_LIFE_TIME_EST_T

YP_A

1

R

[269]

1h

1

R

[268]

1h

Pre EOL information

PRE_EOL_INFO

1

R

[267]

1h

Optimal read size

OPTIMAL_READ_SIZE

1

R

[266]

40h

Optimal write size

OPTIMAL_WRITE_SIZE

1

R

[265]

40h

Optimal trim unit size

OPTIMAL_TRIM_UNIT_SIZE

1

R

[264]

7h

Device version

DEVICE_VERSION

2

R

[263:262]

385h

Firmware version

FIRMWARE_VERSION

8

R

[261:254]

Power class for 200MHz,

DDR at VCC=3.6V

PWR_CL_DDR_200_360

1

R

[253]

0h

Cache size

CACHE_SIZE

4

R

[252:249]

0400h

Barrier support

BARRIER_SUPPORT

Reserved

-

CMD Queuing Support

Number of FW sectors

Support barrier

Support CMDQ

32 CMDQ_DEPTH

128KB (depending

on 16KB*CE)

Generic CMD6 timeout

GENERIC_CMD6_TIME

1

R

[248]

5h

5x10ms = 50ms

Power off notification (long)

timeout

Background operations

status

Number of correctly

programmed sectors

POWER_OFF_LONG_TIME

1

R

[247]

64h

BKOPS_STATUS

1

R

[246]

0h

100x10ms =

1000ms

No operations

required

CORRECTLY_PRG_

SECTORS_NUM

4

R

[245:242]

0h

Run Time update

First initialization time after

INI_TIMEOUT_AP

1

R

[241]

0Ah

Initial time out 1s

CACHE_FLUSH_POLICY

1

R

[240]

1h

partitioning

Cache Flushing Policy

Support cache

flushing policy

Power class for 52MHz,

PWR_CL_DDR_52_360

1

DDR at VCC = 3.6V

Confidential

R

[239]

0h

RMS 100mA,

Peak 200mA

-22/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Power class for 52MHz,

1

PWR_CL_DDR_52_195

R

[238]

0h

DDR at VCC = 1.95V

Peak 130mA

PWR_CL_200_195

1

R

[237]

0h

Power class for 200MHz, at PWR_CL_200_130

1

R

[236]

0h

1

R

[235]

0h

Power class for 200MHz at

RMS 65mA,

VCCQ =1.95V, VCC = 3.6V

VCCQ=1.3V, VCC=3.6V

Minimum write

MIN_PERF_DDR_W_8_52

For devices not

performance for 8bit at

reaching the

52MHz in DDR mode

4.8MB/s value

Minimum read performance MIN_PERF_DDR_R_8_52

for 8bit at 52MHz in DDR

mode

1

R

[234]

0h

Reserved

-

1

-

[233]

-

TRIM multiplier

TRIM_MULT

1

R

[232]

02h

For devices not

reaching the

4.8MB/s value

Trim time out

300ms

Secure feature support

SEC_FEATURE_SUPPORT

1

R

[231]

55h

1. Support the

secure and

insecure trim

operations.

2. Support the

automatic secure

purge operation on

retired defective

portions of the

array.

3. Secure purge

operations are

supported.

Secure Erase Multiplier

SEC_ERASE_MULT

1

R

[230]

19h

Secure Trim Multiplier

SEC_TRIM_MULT

1

R

[229]

0Ah

Boot information

BOOT_INFO

1

R

[228]

7h

Reserved

-

1

-

[227]

-

Boot partition size

BOOT_SIZE_MULTI

1

R

[226]

20h

Confidential

-23/39-

32 x 128KB = 4MB

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Access size

ACC_SIZE

1

R

[225]

6h

High-capacity erase unit

HC_ERASE_GRP_SIZE

1

R

[224]

1h

High-capacity erase

timeout

ERASE_TIMEOUT_MULT

1

R

[223]

2h

Reliable write sector count

REL_WR_SEC_C

1

R

[222]

1h

High-capacity write protect

HC_WP_GRP_SIZE

1

R

[221]

10h

Sleep current (VCC)

S_C_VCC

1

R

[220]

7h

Sleep current (VCCQ)

S_C_VCCQ

1

R

[219]

7h

Production state

PRODUCTION_STATE_AWA

1

R

[218]

17h

awareness timeout

RENESS_TIMEOUT

Sleep/awake timeout

S_A_TIMEOUT

Sleep Notification Timeout

SLEEP_NOTIFICATION_TI

ME

1

R

Sector count

SEC_COUNT

4

Secure Write Protect

SECURE_WP_INFO

1

size

super page size =

64 x 512B = 32KB

high capacity erase

group size 1 x

512KB

group size

(2^23)*100us =

838.86s

1

R

[217]

11h

(2^17)*100ns

[216]

0Ch

=13ms

(2^12)*10us =

40.960ms

R

[215:212]

→

4GB : 720000h

R

[211]

1h

Support Secure

Information

write protect

MIN_PERF_W_8_52

1

R

[210]

0h

Minimum read performance MIN_PERF_R_8_52

1

R

[209]

0h

MIN_PERF_W_8_26_4_52

1

R

[208]

0h

Minimum read performance MIN_PERF_R_8_26_4_52

1

R

[207]

0h

1

R

[206]

0h

Minimum write

VCC < 128uA for

sleep

VCCQ < 128uA for

sleep

performance for 8bit

at 52MHz

for 8bit at 52MHz

Minimum write

performance for 8bit at

26MHz, for 4bit at 52MHz

for 8bit at 26MHz, for 4bit at

52MHz

Minimum write

MIN_PERF_W_4_26

performance for 4bit at

26MHz

Confidential

-24/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Minimum read performance MIN_PERF_R_4_26

for 4bit at 26MHz

1

R

[205]

0h

Reserved

-

1

-

[204]

-

Power class for 26 MHz at

PWR_CL_26_360

1

R

[203]

0h

PWR_CL_52_360

1

R

[202]

0h

PWR_CL_26_195

1

R

[201]

0h

PWR_CL_52_195

1

R

[200]

0h

Partition switching timing

PARTITION_SWITCH_TIME

1

R

[199]

1h

1x10ms = 10ms

Out-of-interrupt busy timing

OUT_OF_INTERRUPT_TIME

1

R

[198]

Ah

10x10ms = 100ms

I/O Driver Strength

DRIVER_STRENGTH

1

R

[197]

1Fh

Support

3.6 V 1 R

Power class for 52 MHz at

3.6 V 1 R

Power class for 26 MHz at

1.95 V 1 R

Power class for 52 MHz at

1.95 V 1 R

Type0/Type1/Type2

/Type3/Type4

Device type

DEVICE_TYPE

1

R

[196]

57h

Reserved

-

1

-

[195]

-

CSD STRUCTURE

CSD_STRUCTURE

1

R

[194]

2h

Reserved

-

1

-

[193]

-

Extended CSD revision

EXT_CSD_REV

1

R

[192]

8h

Command set

CMD_SET

1

R/W/E_P

[191]

0h

Reserved

-

1

-

[190]

-

Command set revision

CMD_SET_REV

1

R

[189]

0h

Reserved

-

1

-

[188]

-

Power class

POWER_CLASS

1

R/W/E_P

[187]

0h

Reserved

-

1

-

[186]

-

High-speed interface timing

HS_TIMING

1

R/W/E_P

[185]

0h

Strobe Support

STROBE_SUPPORT

1

R

[184]

1h

Bus width mode

BUS_WIDTH

1

W/E_P

[183]

0h

Reserved

-

1

-

[182]

-

Erased memory content

ERASED_MEM_CONT

1

R

[181]

0h

Reserved

-

1

-

[180]

-

Confidential

-25/39-

Support JEDEC

eMMC v5.1

Support strobe

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Partition configuration

PARTITION_CONFIG

1

R/W/E

R/W/E_P

[179]

0h

Boot configuration

protection

BOOT_CONFIG_PROT

1

R/W

[178]

0h

Boot bus conditions

BOOT_BUS_CONDITIONS

1

R/W/E

[177]

0h

Reserved

-

1

-

[176]

-

High-density erase group

definition

Boot write protection status

registers

ERASE_GROUP_DEF

1

R/W/E

[175]

0h

BOOT_WP_STATUS

1

R

[174]

0h

Boot area write protection

BOOT_WP

1

R/W

[173]

0h

R/W/C_P

register

R/W/C_P

Reserved

-

User area write protection

USER_WP

register

1

-

[172]

-

[171]

0h

1

R/W

R/W/C_P

R/W/E_P

Reserved

-

1

-

[170]

-

FW configuration

FW_CONFIG

1

R/W

[169]

0h

RPMB size

RPMB_SIZE_MULT

1

R

[168]

20h

Write reliability setting

WR_REL_SET

1

R/W

[167]

1Fh

register

Use 1Fh for SPOR;

Use 00h for

performance

WR_REL_PARAM

1

R

[166]

15h

Start sanitize operation

SANITIZE_START

1

W/E_P

[165]

0h

Manually start background

operations

BKOPS_START

1

W/E_P

[164]

0h

Enable background

operations handshake

BKOPS_EN

1

R/W &

R/W/E

[163]

0h

H/W reset function

RST_n_FUNCTION

1

R/W

[162]

0h

HPI management

HPI_MGMT

1

R/W/E_P

[161]

0h

Partitioning support

PARTITIONING_SUPPORT

1

R

[160]

7h

Write reliability parameter

register

Support partitioning

Support enhanced

feature

Support Ext_Attr

Max enhanced area size

Confidential

MAX_ENH_SIZE_MULT

3

-26/39-

R

[159:157]

1D2h

Rev.1.0 December 2021

�ASFC4G31M-51BIN

Partitions attribute

PARTITIONS_ATTRIBUTE

1

R/W

[156]

0h

Partitioning setting

PARTITION_SETTING_

1

R/W

[155]

0h

GP_SIZE_MULT

12

R/W

[154:143]

0h

ENH_SIZE_MULT

3

R/W

[142:140]

0h

ENH_START_ADDR

4

R/W

[139:136]

0h

Reserved

-

1

-

[135]

-

Secure bad block

management

SEC_BAD_BLK_MGMNT

1

R/W

[134]

0h

Production state

PRODUCTION_STATE_AWA

1

R/W/E

[133]

0h

awareness

RENESS

Package Case

TCASE_SUPPORT

1

W/E_P

[132]

0h

Periodic Wake-up

PERIODIC_WAKEUP

1

R/W/E

[131]

0h

Program CID/CSD in DDR

mode support

PROGRAM_CID_CSD_DDR_

SUPPORT

1

R

[130]

0h

Reserved

-

2

TBD

[129:128]

-

Vendor Specific Fields

VENDOR_SPECIFIC_FIELD

64

[127:64]

37FFFFh

Native sector size

NATIVE_SECTOR_SIZE

1

R

[63]

1h

Sector size emulation

USE_NATIVE_SECTOR

1

R/W

[62]

0h

Sector size

DATA_SECTOR_SIZE

1

R

[61]

0h

1st initialization after

INI_TIMEOUT_EMU

1

R

[60]

0Ah

Class 6 commands control

CLASS_6_CTRL

1

R/W/E_P

[59]

0h

Number of addressed

DYNCAP_NEEDED

1

R

[58]

0h

EXCEPTION_EVENTS_CTRL

2

R/W/E_P

[57:56]

00h

COMPLETED

General purpose partition

size

Enhanced user data area

size

Enhanced user data start

address

Temperature is controlled

4KB

Default 512B

100ms*10=1000 ms

disabling sector size

emulation

group to be Released

Exception events control

1. URGENT_BKOPS

status bit is support

2. DYNCAP_NEEDED

status bit is support

3. SYSPOOL_EXHAU

Confidential

-27/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

STED status bit is

support

4. PACKED_FAILURE

status bit is support

2

R

[55:54]

00h

Exception events status

EXCEPTION_EVENTS_STAT

Extended Partitions

Attribute

US

EXT_PARTITIONS_ATTRIBU

TE

2

R/W

[53:52]

00h

Context configuration

CONTEXT_CONF

15

R/W/E_P

[51:37]

0h

Packed command status

PACKED_COMMAND_STAT

US

1

R

[36]

0h

Device Run Time

update

Packed command failure

PACKED_FAILURE_INDEX

1

R

[35]

0h

Device Run Time

update

index

Power Off Notification

Device Run Time

update

POWER_OFF_NOTIFICATIO

1

R/W/E_P

[34]

0h

N

Control to turn the Cache

ON/OFF

CACHE_CTRL

1

R/W/E_P

[33]

0h

Flushing of the cache

FLUSH_CACHE

1

W/E_P

[32]

0h

Control to turn the Barrier

ON/OFF

BARRIER_CTRL

1

R/W

[31]

0h

Mode config

MODE_CONFIG

1

R/W/E_P

[30]

0h

Mode operation codes

MODE_OPERATION_CODE

S

1

W/E_P

[29]

0h

Reserved

-

1

TBD

[28:27]

-

FFU status

FFU_STATUS

1

R

[26]

0h

Pre loading data size

PRE_LOADING_DATA_SIZE

4

R/W/E_P

[25:22]

0h

Max pre loading data size

MAX_PRE_LOADING_DATA

4

R

[21:18]

E90000h

_SIZE

Product state awareness

enablement

PRODUCT_STATE_AWARE

NESS_ENABLEMENT

1

R/W/E &

R

[17]

01h

Secure Removal Type

SECURE_REMOVAL_TYPE

1

R/W & R

[16]

3Bh

Command Queue Mode

CMDQ_MODE_EN

1

R/W/E_P

[15]

0h

Enable

Reserved

Confidential

Manual mode only

Enable by CMDQ

process

-

15

-28/39-

-

[14:0]

-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

NOTE

1. The definitions of cell types are shown as follows: R: Read only.

W: One time programmable and not readable. R/W: One time programmable and readable.

W/E: Multiple writable with value kept after power failure, H/W reset assertion and any CMD0 reset and not readable.

R/W/E: Multiple writable with value kept after power failure, H/W reset assertion and any CMD0 reset and readable.

R/W/C_P: Writable after value cleared by power failure and H/Wrest assertion (the value not cleared by CMD0 reset)

and readable.

R/W/E_P: Multiple writable with value reset after power failure, H/W reset assertion and any CMD0 reset and readable.

W/E_P: Multiple writable with value reset after power failure, H/W reset assertion and any CMD0 reset and not

readable.

2. Reserved bits should be read as “0”.

Confidential

-29/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

5 AC Parameter

5.1 Timing Parameter

Table 16. Timing Parameter

Timing Paramter

Initialization Time (tINIT)

Max. Value

Normal 1)

After partition setting

1 sec

2)

1sec

Read Timeout

150ms

Write Timeout

600ms

Erase Timeout

600ms

Force Erase Timeout

3 min

Secure Erase Timeout

6 sec

Secure Trim step Timeout

6 sec

Trim Timeout

600 ms

Partition Switching Timeout (after Init)

60ms

Power Off Notification (Short) Timeout

50ms

Power Off Notification (Long) Timeout

1000ms

NOTE

1) Normal Initialization Time without partition setting

2) For the Initialization Time after partition setting, refer to INI_TIMEOUT_AP in 6.4 EXT_CSD register

3) All those Timeout Values specified in the above Table are only for testing purposes under specific test case

only and it can vary in real cases. Also, it may be affected may vary due to user environment.

Confidential

-30/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

5.2 Bus Timing Specification in HS400 mode

5.2.1 HS400 Device Input Timing

Figure 6. HS400 Device Input Timing Diagram

tPERIOD

VCCQ

Clock

Input

VT

tCKDCD

tCKMPW

tCKDCD

tCKMPW

VSS

tISU

tIH

tISU

tIH

VCCQ

VIH

DAT[7-0]

Input

VIL

Valid

Window

Valid

Window

VSS

NOTE

1) tISU and tIH are measured at VIL (max) and VIH (min).

2) VIH denotes VIH (min) and VIL denotes VIL (max)

Parameter

Input CLK

Cycle time data transfer mode

Slew rate

Duty cycle distortion

Minimum pulse width

Input DAT (referenced to CLK)

Input set-up time

Input hold time

Slew rate

Confidential

Table 17. HS400 Device Input Timing

Symbol

Min

Max

Unit

tPERIOD

5

-

ns

SR

tCKDCD

tCKMPW

1.125

0.0

2.2

0.3

-

V/ns

ns

ns

tISUddr

tIHddr

SR

0.4

0.4

1.125

-

ns

ns

V/ns

-31/39-

Remark

200MHz(Max), between rising edges

with respect to VT.

Rev.1.0 December 2021

�ASFC4G31M-51BIN

5.2.2 HS400 Device Output Timing

Data Strobe is used to read data (data read and CRC status response read) in HS400 mode. The device output value of

Data Strobe is “High-Z” when the device is not in outputting data(data read, CRC status response). Data Strobe is

toggled only during data read period.

Figure 7. HS400 Device Output Timing Diagram

tPERIOD

VCCQ

Data Strobe

VT

tDSDCD

tDSMPW

tDSDCD

tDSMPW

VSS

tRQ

tRQH

VCCQ

VOH

DAT[7-0]

Output VOL

Valid

Window

Valid

Window

VSS

NOTE

1) VOH denotes VOH (min) and VOL denotes VOL (max).

Parameter

Data Strobe

Cycle time data transfer mode

Table 18. HS400 Device Output Timing

Symbol

Min

Max

Unit

tPERIOD

Slew rate

SR

Duty cycle distortion

tDSDCD

Minimum pulse width

tDSMPW

Read pre-amble

tRPRE

Read post-amble

tRPST

Output DAT (referenced to Data Strobe)

Output skew

tRQ

Output hold skew

tRQH

Slew rate

SR

Confidential

5

-

ns

1.125

0.0

2.0

0.4

0.4

0.2

-

V/ns

ns

ns

tPERIOD

tPERIOD

1.125

0.4

0.4

-

ns

ns

V/ns

-32/39-

Remark

200MHz(max), between rising

edges with respect to VT.

Rev.1.0 December 2021

�ASFC4G31M-51BIN

5.3 Bus Signal Levels

As the bus can be supplied with a variable supply voltage, all signal levels are related to the supply voltage.

Figure 8. Bus Signal Levels

V

VCCQ

Input

High Level

Output

High Level

VOH

VIH

Undefined

VIL

Input

Low Level

VOL

Output

Low Level

VSS

Parameter

Symbol

Open-drain mode

Output HIGH voltage

VOH

Output LOW voltage

VOL

Push-pull mode (High-voltage eMMC)

Output HIGH voltage

VOH

Output LOW voltage

VOL

Input HIGH voltage

VIH

Input LOW voltage

VIL

Push-pull mode (1.70 ~ 1.95 V)

Output HIGH voltage

VOH

Output LOW voltage

VOL

Input HIGH voltage

VIH

Input LOW voltage

VIL

t

Table 19. Bus Signal Levels

Min

Max

Unit

Remark

VCCQ – 0.2

-

0.3

V

V

IOL = 2mA

0.75 x VCCQ

0.625 x VCCQ

VSS – 0.3

0.125 x VCCQ

VCCQ + 0.3

0.25 x VCCQ

V

V

V

V

IOH = –100uA @ VCCQ min

IOL = 100uA @ VCCQ min

VCCQ – 0.45

0.65 x VCCQ 1)

VSS – 0.3

0.45

VCCQ + 0.3

0.35 x VCCQ 2)

V

V

V

V

IOH = –2mA

IOL = 2mA

NOTE

1) Because VOH depends on external resistance value (including outside the package), this value does not apply as

device specification. Host is responsible to choose the external pull-up and open drain resistance value to

meet VOH Min value.

2) 0.7 x VCCQ for MMC4.3 and older revisions.

3) 0.3 x VCCQ for MMC4.3 and older revisions.

Confidential

-33/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

6 DC Parameter

6.1 Power Consumption

Table 20. Active Power Consumption during operation

Density (GB)

NAND Type (MLC)

CTRL (Max RMS,mA)

NAND (Max RMS,mA)

4

32Gb x 1

120

120

NOTE

*

Power Measurement conditions: Bus configuration =x8 @200MHz DDR

* Typical value is measured at Vcc=3.3V, Vccq=1.8V, TA=25°C. Not 100% tested.

* The measurement for max RMS current is the average RMS current consumption over a period of 100ms

Table 21. Standby Power Consumption in auto power saving mode and standby state

CTRL (Ave. RMS, uA)

NAND (Ave. RMS, uA)

Density

NAND Type

(GB)

(MLC)

25°C (Typ)

85°C

25°C (Typ)

85°C

4

32Gb x 1

130

600

40

50

NOTE

* Power Measurement conditions: Bus configuration =x8, No CLK

* Typical value is measured at Vcc=3.3V,Vccq=1.8V TA=25°C. Not 100% tested.

Table 22. Sleep Power Consumption in Sleep State

CTRL (uA)

Density

NAND Type

(GB)

(MLC)

25°C (Typ)

85°C

4

32Gb x 1

130

600

NAND (uA)

refer *1

NOTE

* Power Measurement conditions: Bus configuration =x8, No CLK

* Typical value is measured at Vcc=3.3V, VccQ=1.8V, TA=25°C. Not 100% tested.

*1) In auto power saving mode, NAND power can not be turned off, However in sleep mode NAND power can be

turned off. If NAND power is alive, NAND power is same with that of the Standby state.

6.2 Supply Voltage

Confidential

Symbol

Table 23. Supply Voltage

Min (V)

Max (V)

VCCQ (Low)

1.7

1.95

VCCQ (High)

2.7

3.6

VCC

2.7

3.6

VSS

- 0.5

0.5

-34/39-

Rev.1.0 December 2021

�ASFC4G31M-51BIN

6.3 Bus Signal Line Load

The total capacitance CL of each line of the eMMC bus is the sum of the bus master capacitance CHOST, the bus

capacitance CBUS itself and the capacitance CDEVICE of the eMMC connected to this line:

CL = CHOST + CBUS + CDEVICE

The sum of the host and bus capacitances should be under 20pF.

Parameter

Table 24. Bus Signal Line Load

Symbol

Min

Typ

Max

Unit

Remark

Pull-up resistance for CMD

RCMD

4.7

100

KOhm

to prevent bus floating

Pull-up resistance for DAT0-DAT7

RDAT

10

100

KOhm

to prevent bus floating

Internal pull up resistance DAT1-DAT7

Rint

10

150

KOhm

Single Device capacitance

CDEVICE

6

pF

16

nH

Maximum signal line inductance

to prevent unconnected

lines floating

fPP