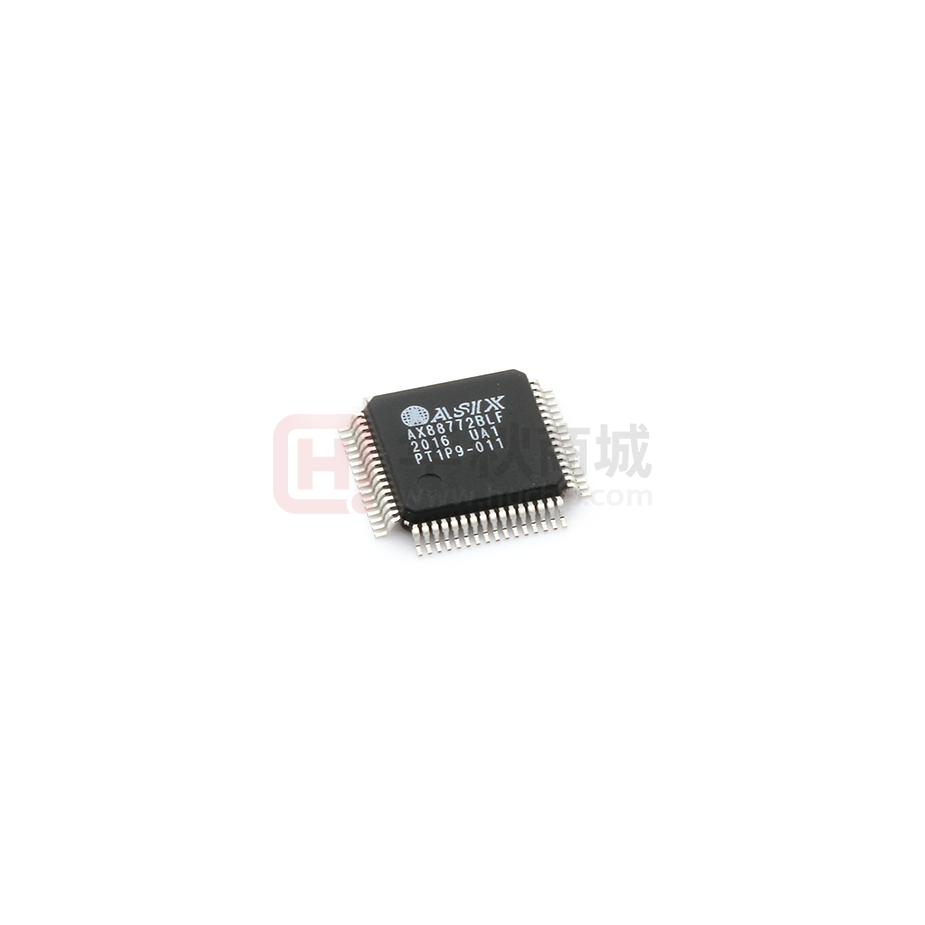

AX88772BLF / AX88772BLI

Low-Power

USB 2.0 to 10/100M Fast Ethernet Controller

Features

Single chip USB 2.0 to 10/100M Fast Ethernet

controller

Single chip USB 2.0 to RMII, support HomePNA

and HomePlug PHY

Single chip USB 2.0 to Reverse-RMII, supports

glueless MAC-to-MAC connections

USB Device Interface

Integrates on-chip USB 2.0 transceiver and

SIE compliant to USB Spec 1.1 and 2.0

Supports USB Full and High Speed modes

with Bus-Power or Self-Power capability

Supports 4 or 6 programmable endpoints on

USB interface

Supports AutoDetach power saving. Detach

from USB host when Ethernet cable is

unplugged

High performance packet transfer rate over

USB bus using proprietary burst transfer

mechanism (US Patent Approval)

Fast Ethernet Controller

Integrates 10/100Mbps Fast Ethernet

MAC/PHY

IEEE

802.3

10BASE-T/100BASE-TX

compatible

IEEE 802.3 100BASE-FX compatible

Supports twisted pair crossover detection and

auto-correction (HP Auto-MDIX)

Embedded SRAM for RX/TX packet

buffering

Supports IPv4/ IPv6 packet Checksum

Offload Engine(COE) to reduce CPU loading,

including IPv4 IP/TCP/UDP/ICMP/IGMP &

IPv6 TCP/UDP/ICMPv6 checksum check &

generation

Supports full duplex operation with IEEE

802.3x flow control and half duplex operation

with back-pressure flow control

Supports 2 VLAN ID filtering, received

VLAN Tag (4 bytes) can be stripped off or

preserved

PHY loop-back diagnostic capability

Document No: AX88772B/V1.06/02/27/13

Support Wake-on-LAN Function

Supports Suspend Mode and Remote Wakeup

via Link-change, Magic packet, MS wakeup

frame and external wakeup pin

Supports Protocol Offload (ARP & NS) for

Windows 7 Networking Power Management

Optional PHY power down during Suspend

Mode

Versatile External Media Interface

Optional RMII interface in MAC mode allows

AX88772B to work with HomePNA and

HomePlug PHY

Optional Reverse-RMII interface in PHY

mode allows AX88772B to support glueless

MAC-to-MAC connections

Advanced Power Management Features

Supports dynamic power management to

reduce power dissipation during idle or light

traffic

Supports very low power Wake-on-LAN

(WOL) mode when the system enters suspend

mode and waits for network events to wake it

up.

Supports 256/512 bytes (93c56/93c66) of serial

EEPROM (for storing USB Descriptors)

Supports embedded Device Descriptors ROM and

512 bytes ID-SRAM (online programmable

memory for USB Device Descriptors, etc) to

save external EEPROM

Supports automatic loading of Ethernet ID, USB

Descriptors and Adapter Configuration from

EEPROM after power-on initialization

Integrates on-chip voltage regulator and only

requires a single 3.3V power supply

Single 25MHz clock input from either crystal or

oscillator source

Integrates on-chip power-on reset circuit

Small form factor with 64-pin LQFP RoHS

compliant package

Operating commercial temperature range 0°C to

70°C or industriure range -40 to +85°C

ASIX ELECTRONICS CORPORATION

4F, NO.8, Hsin Ann Rd., Hsinchu Science Park, Hsin-Chu City, Taiwan, R.O.C. 300

TEL: 886-3-579-9500

FAX: 886-3-579-9558

Released Date: 02/27/2013

http://www.asix.com.tw/

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

Target Applications

PC/Internet

Consumer Electronics

Figure 1

: Target Applications

2

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

Typical System Block Diagrams

Hosted by USB to operate with internal Ethernet PHY only

To USB 2.0 Host I/F

AX88772B

EEPROM

Ethernet PHY

OR

Magnetic

Optical

Fiber

Transceiver

RJ45

Figure 2

: USB 2.0 to LAN Adaptor (MAC mode)

Hosted by USB to operate with either internal Ethernet PHY or RMII (in MAC

mode)

To USB 2.0 Host I/F

AX88772B

EEPROM

Ethernet PHY

MDC MDIO

RMII

OR

Magnetic

PHYceiver

Optical

Fiber

Transceiver

RJ45

Figure 3

: USB 2.0 to Fast Ethernet and external PHYceiver Combo (MAC mode)

3

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

Hosted by USB to operate with either internal Ethernet PHY (in MAC mode) or

Reverse-RMII (in PHY mode)

To USB 2.0 Host I/F

AX88772B

EEPROM

Ethernet PHY

MDC MDIO

Reverse-RMII

(No oscillator or buffer required)

OR

Magnetic

Optical

Fiber

Ethernet MAC

Embedded MCU

Transceiver

RJ45

Figure 4

: Bridging Embedded MCU to USB 2.0 Host Interface (PHY mode)

To USB 2.0 Host I/F

AX88772B

EEPROM

Ethernet PHY

MDC MDIO

Reverse-RMII

(No oscillator or buffer required)

OR

HomePlug

PHY

Magnetic

Optical

Fiber

Transceiver

RJ45

Figure 5

PowerLine

: USB 2.0 to HomePlug Adaptor (PHY mode)

4

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

DISCLAIMER

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical,

including photocopying and recording, for any purpose, without the express written permission of ASIX. ASIX may make

changes to the product specifications and descriptions in this document at any time, without notice.

ASIX provides this document “as is” without warranty of any kind, either expressed or implied, including without

limitation warranties of merchantability, fitness for a particular purpose, and non-infringement.

Designers must not rely on the absence or characteristics of any features or registers marked “reserved”, “undefined” or

“NC”. ASIX reserves these for future definition and shall have no responsibility whatsoever for conflicts or

incompatibilities arising from future changes to them. Always contact ASIX to get the latest document before starting a

design of ASIX products.

TRADEMARKS

ASIX, the ASIX logo are registered trademarks of ASIX Electronics Corporation. All other trademarks are the property of

their respective owners.

5

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

Table of Contents

1

INTRODUCTION .................................................................................................................................................. 10

1.1

1.2

1.3

2

SIGNAL DESCRIPTION ...................................................................................................................................... 12

2.1

2.2

3

GENERAL DESCRIPTION ..................................................................................................................................... 10

BLOCK DIAGRAM .............................................................................................................................................. 10

PINOUT DIAGRAM .............................................................................................................................................. 11

PINOUT DESCRIPTION ........................................................................................................................................ 12

HARDWARE SETTING FOR OPERATION MODE AND MULTI-FUNCTION PINS ...................................................... 15

FUNCTION DESCRIPTION ................................................................................................................................ 17

3.1

USB CORE AND INTERFACE .............................................................................................................................. 17

3.2

10/100M ETHERNET PHY ................................................................................................................................. 17

3.3

MAC CORE ....................................................................................................................................................... 17

3.4

CHECKSUM OFFLOAD ENGINE (COE)................................................................................................................ 18

3.5

OPERATION MODE ............................................................................................................................................. 18

3.6

STATION MANAGEMENT (STA) ......................................................................................................................... 21

3.7

MEMORY ARBITER ............................................................................................................................................ 23

3.8

USB TO ETHERNET BRIDGE ............................................................................................................................... 23

3.8.1

Ethernet/USB Frame Format Bridge ........................................................................................................ 23

3.9

SERIAL EEPROM LOADER ................................................................................................................................ 23

3.10 GENERAL PURPOSE I/O...................................................................................................................................... 23

3.11 CLOCK GENERATION ......................................................................................................................................... 24

3.12 RESET GENERATION .......................................................................................................................................... 25

3.13 VOLTAGE REGULATOR ...................................................................................................................................... 25

4

SERIAL EEPROM MEMORY MAP ................................................................................................................... 26

4.1

DETAILED DESCRIPTION .................................................................................................................................... 27

4.2

INTERNAL ROM DEFAULT SETTINGS ................................................................................................................ 30

4.2.1

Internal ROM Description ........................................................................................................................ 31

4.2.2

External EEPROM Description ................................................................................................................ 33

5

USB CONFIGURATION STRUCTURE ............................................................................................................. 34

5.1

5.2

5.3

6

USB CONFIGURATION ....................................................................................................................................... 34

USB INTERFACE ................................................................................................................................................ 34

USB ENDPOINTS................................................................................................................................................ 34

USB COMMANDS ................................................................................................................................................. 35

6.1

USB STANDARD COMMANDS ............................................................................................................................ 35

6.2

USB VENDOR COMMANDS ................................................................................................................................ 36

6.2.1

Detailed Register Description ................................................................................................................... 38

6.3

INTERRUPT ENDPOINT ....................................................................................................................................... 63

6.4

BULK-OUT TIMER AND MONITOR (BOTM)....................................................................................................... 64

7

EMBEDDED ETHERNET PHY REGISTER DESCRIPTION ......................................................................... 65

7.1

PHY REGISTER DETAILED DESCRIPTION ........................................................................................................... 65

7.1.1

Basic Mode Control Register (BMCR) ..................................................................................................... 66

7.1.2

Basic Mode Status Register (BMSR) ......................................................................................................... 67

7.1.3

PHY Identifier Register 1 (PHYIDR1) ...................................................................................................... 68

7.1.4

PHY Identifier Register 2 (PHYIDR2) ...................................................................................................... 68

7.1.5

Auto Negotiation Advertisement Register (ANAR).................................................................................... 68

7.1.6

Auto Negotiation Link Partner Ability Register (ANLPAR) ...................................................................... 69

7.1.7

Auto Negotiation Expansion Register (ANER) ......................................................................................... 69

8

STATION MANAGEMENT REGISTERS IN PHY MODE ............................................................................. 70

8.1

PHY MODE DETAILED REGISTER DESCRIPTION ................................................................................................ 71

6

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

8.1.1

8.1.2

8.1.3

8.1.4

8.1.5

8.1.6

8.1.7

8.1.8

9

PHY Mode Basic Mode Control Register (PM_BMCR) ........................................................................... 71

PHY Mode Basic Mode Status Register (PM_BMSR) .............................................................................. 72

PHY Mode PHY Identifier Register 1 (PM_PHYIDR1) ............................................................................ 73

PHY Mode PHY Identifier Register 2 (PM_PHYIDR2) ............................................................................ 73

PHY Mode Auto Negotiation Advertisement Register (PM_ANAR) ......................................................... 73

PHY Mode Auto Negotiation Link Partner Ability Register (PM_ANLPAR) ........................................... 74

PHY Mode Auto Negotiation Expansion Register (PM_ANER) ............................................................... 74

PHY Mode Control Register (PM_Control) ............................................................................................. 75

ELECTRICAL SPECIFICATIONS ..................................................................................................................... 76

9.1

DC CHARACTERISTICS ...................................................................................................................................... 76

9.1.1

Absolute Maximum Ratings ...................................................................................................................... 76

9.1.2

Recommended Operating Condition ......................................................................................................... 76

9.1.3

Leakage Current and Capacitance ........................................................................................................... 77

9.1.4

DC Characteristics of 3.3V I/O Pins ........................................................................................................ 77

9.1.5

DC Characteristics of 3.3V with 5V Tolerance I/O Pins .......................................................................... 78

9.1.6

DC Characteristics of Voltage Regulator ................................................................................................. 78

9.1.7

DC Characteristics of Fiber Interface ...................................................................................................... 79

9.2

THERMAL CHARACTERISTICS ............................................................................................................................ 80

9.3

POWER CONSUMPTION ...................................................................................................................................... 80

9.4

POWER-UP SEQUENCE ....................................................................................................................................... 81

9.5

AC TIMING CHARACTERISTICS .......................................................................................................................... 82

9.5.1.

Clock Timing ............................................................................................................................................. 82

9.5.2.

Reset Timing ............................................................................................................................................. 82

9.5.3.

Serial EEPROM Timing ............................................................................................................................ 83

9.5.4.

Station Management Timing ..................................................................................................................... 84

9.5.5.

RMII / Reverse-RMII Timing .................................................................................................................... 85

9.5.6.

10/100M Ethernet PHY Interface Timing ................................................................................................. 86

9.5.7.

USB Transceiver Interface Timing ........................................................................................................... 87

10

10.1

PACKAGE INFORMATION ............................................................................................................................ 89

AX88772B 64-PIN LQFP PACKAGE .................................................................................................................. 89

11

ORDERING INFORMATION .......................................................................................................................... 90

12

REVISION HISTORY ....................................................................................................................................... 91

APPENDIX A. DEFAULT WAKE-ON-LAN (WOL) READY MODE .................................................................... 92

APPENDIX B. ETHERNET PHY POWER AND RESET CONTROL .................................................................... 95

APPENDIX C. EXTERNAL EEPROM / INTERNAL ROM / INTERNAL ID-SRAM OF VENDER

DESCRIPTIONS SELECTION .................................................................................................................................... 97

7

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

List of Figures

FIGURE 1

FIGURE 2

FIGURE 3

FIGURE 4

FIGURE 5

FIGURE 6

FIGURE 7

FIGURE 8

FIGURE 9

FIGURE 10

FIGURE 11

FIGURE 12

FIGURE 13

FIGURE 14

FIGURE 15

FIGURE 16

FIGURE 17

FIGURE 18

FIGURE 19

FIGURE 20

FIGURE 21

FIGURE 22

FIGURE 23

FIGURE 24

: TARGET APPLICATIONS ................................................................................................................................. 2

: USB 2.0 TO LAN ADAPTOR (MAC MODE) .................................................................................................... 3

: USB 2.0 TO FAST ETHERNET AND EXTERNAL PHYCEIVER COMBO (MAC MODE) ........................................ 3

: BRIDGING EMBEDDED MCU TO USB 2.0 HOST INTERFACE (PHY MODE)..................................................... 4

: USB 2.0 TO HOMEPLUG ADAPTOR (PHY MODE) .......................................................................................... 4

: BLOCK DIAGRAM ........................................................................................................................................ 10

: PINOUT DIAGRAM ........................................................................................................................................ 11

: INTERNAL DATA PATH DIAGRAM OF 10/100M ETHERNET PHY AND RMII/REVERSE-RMII INTERFACES .. 17

: RMII TO EXTERNAL PHY CHIP WITH 50MHZ OSC .................................................................................... 19

: RMII INTERFACE TO EXTERNAL PHY CHIP ............................................................................................. 19

: REVERSE-RMII TO EXTERNAL MAC DEVICE WITH 50MHZ OSC .......................................................... 20

: REVERSE-RMII INTERFACE TO EXTERNAL MAC DEVICE ....................................................................... 20

: INTERNAL CONTROL MUX OF STATION MANAGEMENT INTERFACE IN MAC MODE ............................... 21

: INTERNAL CONTROL MUX OF STATION MANAGEMENT INTERFACE IN PHY MODE ................................ 22

: ONE EXTERNAL 1M OHM RESISTOR ON 25MHZ CRYSTAL OSCILLATOR IS NECESSARY ............................ 25

: WATER LEVEL SETTING FOR FLOW CONTROL ........................................................................................... 29

: MULTICAST FILTER EXAMPLE ................................................................................................................. 43

: MULTICAST FILTER ARRAY HASHING ALGORITHM ................................................................................. 44

: MULTICAST FILTER ARRAY BIT MAPPING ............................................................................................... 44

: 802.1Q VLAN PACKET FORMAT ............................................................................................................. 54

: STATION MANAGEMENT FRAME FOR PHY MODE ................................................................................... 70

: ETHERNET PHY OSCILLATOR/PLL BLOCK DIAGRAM ............................................................................. 95

: ETHERNET PHY POWER-UP & RESET TIMING DIAGRAM ......................................................................... 96

: EXTERNAL EEPROM / INTERNAL ROM / INTERNAL ID-SRAM OF VENDER DESCRIPTIONS SELECTION 98

8

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

List of Tables

TABLE 1

TABLE 2

TABLE 3

TABLE 4

TABLE 5

TABLE 6

TABLE 7

TABLE 8

TABLE 9

TABLE 10

TABLE 11

TABLE 12

TABLE 13

TABLE 14

TABLE 15

: PINOUT DESCRIPTION .................................................................................................................................. 14

: MFA_3 ~ MFA_0 PIN CONFIGURATION ....................................................................................................... 15

: PHY_ID DEFINITION SOURCE ..................................................................................................................... 18

: THE EXTERNAL 25MHZ CRYSTAL UNITS SPECIFICATIONS .......................................................................... 24

: SERIAL EEPROM MEMORY MAP ................................................................................................................ 26

: INTERNAL ROM MEMORY MAP .................................................................................................................. 30

: INTERNAL ROM DESCRIPTION .................................................................................................................... 31

: USB STANDARD COMMAND REGISTER MAP ............................................................................................... 35

: USB VENDOR COMMAND REGISTER MAP ................................................................................................... 37

: WAKE-UP FRAME ARRAY REGISTER (WUD3~0) STRUCTURE DEFINITION ............................................. 50

: VID1, VID2 SETTING TO FILTER RECEIVED PACKET ................................................................................ 53

: EMBEDDED ETHERNET PHY REGISTER MAP ........................................................................................... 65

: STATION MANAGEMENT REGISTER MAP IN PHY MODE ......................................................................... 70

: POWER CONSUMPTION ............................................................................................................................. 80

: REMOTE WAKEUP TRUTH TABLE ............................................................................................................ 93

9

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

1 Introduction

1.1

General Description

The AX88772B Low-power USB 2.0 to 10/100M Fast Ethernet controller is a high performance and highly integrated

ASIC which enables low cost, small form factor, and simple plug-and-play Fast Ethernet network connection capability

for desktops, notebook PC’s, Ultra-Mobile PC’s, docking stations, game consoles, digital-home appliances, and any

embedded system using a standard USB port.

The AX88772B features a USB interface to communicate with a USB Host Controller and is compliant with USB

specification V1.1 and V2.0. The AX88772B implements a 10/100Mbps Ethernet LAN function based on IEEE802.3,

and IEEE802.3u standards with embedded SRAM for packet buffering. The AX88772B integrates an on-chip

10/100Mbps Ethernet PHY to simplify system design.

The AX88772B provides an optional Multi-Function-Bus portion A and B (MFA and MFB) for external PHY or external

MAC for different application purposes. The MFA/MFB can be a reduce-media-independent interface (RMII) for

implementing HomePlug, HomePNA, etc. functions. The MFA/MFB can also be a Reverse Reduced-MII

(Reverse-RMII) for glueless MAC-to-MAC connections to any MCU with Ethernet MAC RMII interface. In addition, the

MFA/MFB can be configured as general purpose I/O.

1.2 Block Diagram

Packet Buffer

SRAM

Memory

Arbiter

COE

MAC

Core

10/100M

Ethernet

PHY

ID SRAM

EECS

EECK

EEDIO

SEEPROM

Loader I/F

USB to

Ethernet

Bridge

PHY/MAC

mode Bridge

General Purpose

I/O

3.3 to 1.8V

Regulator

USB Core and Interfaces

PLL Clock

Generators

XTL25P, XTL25N

Figure 6

MFB1~7 for

RMII or Rev-RMII

MFA0, 1 for

MDC / MDIO

STA

GPIO_2~0,

MFB0, etc.

RXIP/RXIN

TXOP/TXON

Power-On-Reset

& Reset Gen.

DP/DM

RESET_N

: Block Diagram

10

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

1.3 Pinout Diagram

MFB2

MFB1

MFB0

VCCK

GND

EECK

EECS

EEDIO

TCLK_1

TCLK_0

TCLK_EN

VCC3IO

RESET_N

TEST1

TEST0

GND

64-pin LQFP package

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

32 MFB3

31 MFB4

30 MFB5

29 MFB6

28 MFB7

27 GPIO_0/PME

26 GPIO_1

25 GPIO_2

24 VCCK

23 EXTWAKEUP_N

22 GND

21 MFA3/PHY_N

20 VCCK

19 MFA2/RMII_N

18 MFA1/MDIO

17 MFA0/MDC

Figure 7

VCC3IO

GND

GND18A

TXON

RSET_BG

9 10 11 12 13 14 15 16

TXOP

GND18A

8

VCC18A

XTL25N

6 7

RXIN

5

RXIP

4

GND18A

3

SD

2

VCC3A3

1

XTL25P

AX88772B

VCC18A

VCCK

V_BUS

V18F

VCC3R3

GND3R3

GND33A_PLL

GND33A_H

DP

DM

RREF

VCC33A_PLL

VCC33A_H

X2

X1

GND18A_PLL

VCC18A_PLL

: Pinout Diagram

11

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

2 Signal Description

The following abbreviations apply to the following pin description table.

I18

I3

I5

O3

B5

P

Input, 1.8V

Input, 3.3V

Input, 3.3V with 5V tolerant

Output, 3.3V

Bi-directional I/O, 3.3V with 5V tolerant

Power Pin

AI

Analog Input

AO Analog Output

AB Analog Bi-directional I/O

PU

Internal Pull Up (75K)

PD

Internal Pull Down (75K)

S

Schmitt Trigger

T

Tri-stateable

Note: Every output or bi-directional I/O pin is 8mA driving strength.

2.1 Pinout Description

Pin Name

Type

Pin No

DP

DM

V_BUS

RREF

AB

AB

I5/PD/S

AI

56

57

50

58

EECK

B5/PD/

T

38

EECS

B5/PD/

T

39

EEDIO

B5/PU/

T

40

XTL25P

I18

2

XTL25N

RXIP

RXIN

TXOP

TXON

RSET_BG

O18

AB

AB

AB

AB

AO

3

9

10

12

13

5

RESET_N

I5/PU/S

45

EXTWAKEUP_N

I5/PU/S

23

GPIO_2

GPIO_1

B5/PD

B5/PD

25

26

Pin Description

USB Interface

USB 2.0 data positive pin.

USB 2.0 data negative pin.

VBUS pin input. Please connect to USB bus power.

For USB PHY’s internal biasing. Please connect to analog GND through a

resistor (12.1Kohm ±1%).

Serial EEPROM Interface

EEPROM Clock. EECK is an output clock to EEPROM to provide timing

reference for the transfer of EECS, and EEDIO signals. EECK only drive

high / low when access EEPROM otherwise keep at tri-state and internal

pull-down.

EEPROM Chip Select. EECS is asserted high synchronously with respect to

rising edge of EECK as chip select signal. EECS only drive high / low when

access EEPROM otherwise keep at tri-state and internal pull-down.

EEPROM Data In. EEDIO is the serial output data to EEPROM’s data input

pin and is synchronous with respect to the rising edge of EECK. EEDIO

only drive high / low when access EEPROM otherwise keep at tri-state and

internal pull-up.

Ethernet PHY Interface

25Mhz ± 0.005% crystal or oscillator clock input. This clock is needed for

the embedded 10/100M Ethernet PHY to operate.

25Mhz crystal or oscillator clock output.

Receive data input positive pin for both 10BASE-T and 100BASE-TX.

Receive data input negative pin for both 10BASE-T and 100BASE-TX.

Transmit data output positive pin for both 10BASE-T and 100 BASE-TX

Transmit data output negative pin for both 10BASE-T and 100 BASE-TX

For Ethernet PHY’s internal biasing. Please connect to GND through a

12.1Kohm ±1% resistor.

Misc. Pins

Chip reset input. Active low. This is the external reset source used to reset

this chip. This input feeds to the internal power-on reset circuitry, which

provides the main reset source of this chip. After completing reset,

EEPROM data will be loaded automatically.

Remote-wakeup trigger from external pin. EXTWAKEUP_N should be

asserted low for more than 2 cycles of 25MHz clock to be effective.

General Purpose Input/ Output Pin 2.

General Purpose Input/ Output Pin 1. This pin is default as input pin after

power-on reset. This pin is also for Default WOL Ready Mode setting;

please refer to section 2.2 Settings.

12

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

GPIO_0/PME

B5/PD

27

MFB7

B5/PU

I5

I5

MFB6

B5/PU

I5

I5

MFB5/

REF50

B5/PU

B5

MFB4

31

MFB0

B5/PU

O3

O3

B5/PU

O3

O3

B5/PU

O3

O3

B5/PU

I5

I5

B5/PU

MFA3/

PHY_N

O3

I5/PU

21

MFA2/

RMII_N

O3

I5/PU

19

MFA1/

MDIO

O3

B5/PU

18

28

29

30

MFB3

MFB2

MFB1

32

33

34

35

General Purpose Input/ Output Pin 0 or PME (Power Management Event).

This pin is default as input pin after power-on reset. GPIO_0 also can be

defined as PME output to indicate wake up event detected. Please refer to

section 2.2 Settings.

This is a multi-function pin. Please refer to section 2.2 Settings.

MFB7:

RMII

: RXD0

Reverse_RMII : TXD0

This is a multi-function pin. Please refer to section 2.2 Settings.

MFB6:

RMII

: RXD1

Reverse_RMII : TXD1

This is a multi-function pin. Please refer to section 2.2 Settings.

MFB5:

When RMII enable, The REF50 in/out direction is determined by EEPROM

Flag [1] setting. Please refer to section 2.2 Settings.

This is a multi-function pin. Please refer to section 2.2 Settings.

RMII

: TXD0

Reverse_RMII : RXD0

This is a multi-function pin. Please refer to section 2.2 Settings.

RMII

: TXD1

Reverse_RMII : RXD1

This is a multi-function pin. Please refer to section 2.2 Settings.

RMII

: TXEN

Reverse_RMII : CRSDV

This is a multi-function pin. Please refer to section 2.2 Settings.

RMII

: CRSDV

Reverse_RMII : TXEN

This is a GPIO pin. Please refer to section 2.2 Settings.

It is a multi-function pin. The default is USB Speed indicator. When USB

bus is in Full speed, this pin will tri-state continuously. When USB bus is in

High speed, this pin drives low continuously. This pin tri-state and drive low

in turn (blinking) to indicate TX data transfer going on whenever the host

controller sends bulk out data transfer.

MFB1~7 bus is determined by setting of this input pin when MFA2 sets 0:

0: Reverse_RMII (PHY mode).

1: RMII (MAC mode).

Please refer to PIN configuration of MFA and MFB in section 2.2 Settings.

It is a multi-function pin. The default is Link status LED indicator.

This pin drives low continuously when the Ethernet link is up and drives low

and high in turn (blinking) when Ethernet PHY is in receiving or

transmitting state.

MFB1~7 function is determined by setting of this input pin:

0: Reverse_RMII/RMII .

1: MFB bus as GPIO function.

Please refer to PIN configuration of MFA and MFB in section 2.2 Settings.

It is a multi-function pin. The default is Ethernet speed LED indicator.

This pin drives low when the Ethernet PHY is in 100BASE-TX mode and

drives high when in 10BASE-T mode.

This pin can perform as MDIO when enabling Reverse_RMII/RMII.

13

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

MFA0/

MDC

SD

TEST0

TEST1

X1

X2

TCLK_EN

TCLK_0

TCLK_1

VCC3R3

GND3R3

V18F

VCCK

VCC3IO

GND

VCC33A_H

GND33A_H

VCC33A_PLL

GND33A_PLL

VCC3A3

VCC18A

GND18A

VCC18A_PLL

GND18A_PLL

O3

17

It is a multi-function pin. The default is Full Duplex and collision detected

LED indicator.

This pin drives low when the Ethernet PHY is in full-duplex mode and

drives high when in half duplex mode. When in half duplex mode and the

Ethernet PHY detects collision, it will be driven low (or blinking).

This pin can perform as MDC when enabling Reverse_RMII/RMII:

RMII

: Output.

Reverse_RMII : Input.

7 Fiber signal detected

Twisted pair operation: Please connect to GND directly or through a

resistor.

Fiber operation: Please connect to the fiber transceiver signal detect output

pin.

Please refer to Section 9.1.7 for the detailed SD signal DC Characteristics

spec.

I5/S

47 Test pin. For normal operation, user should connect to ground.

I5/S

46 Test pin. For normal operation, user should connect to ground.

I3

62 Test pin. For normal operation, user should connect to ground.

O3

61 Test pin. No connection

I5/PD/S 43 Test pin. For normal operation, user should keep this pin NC.

I5/PD

42 Test pin. For normal operation, user should keep this pin NC.

I5/PD

41 Test pin. For normal operation, user should keep this pin NC.

On-chip Regulator Pins

P

52 3.3V Power supply to on-chip 3.3V to 1.8V voltage regulator.

P

53 Ground pin of on-chip 3.3V to 1.8V voltage regulator.

P

51 1.8V voltage output of on-chip 3.3V to 1.8V voltage regulator.

Power and Ground Pins

P

20, 24, 36, 49 Digital Core Power. 1.8V.

P

16, 44

Digital I/O Power. 3.3V.

P

15, 22, 37, 48 Digital Ground.

P

60

Analog Power for USB transceiver. 3.3V.

P

55

Analog Ground for USB transceiver.

P

59

Analog Power for USB PLL. 3.3V.

P

54

Analog Ground for USB PLL.

P

6

Analog Power for Ethernet PHY bandgap. 3.3V.

P

1, 11

Analog Power for Ethernet PHY and 25Mhz crystal oscillator.

1.8V.

P

4, 8, 14

Analog Ground for Ethernet PHY and 25Mhz crystal oscillator.

P

64

Analog Power for USB PLL. 1.8V.

P

63

Analog Ground for USB PLL.

O3

I5/PU

I

Table 1

: Pinout Description

14

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

2.2 Hardware Setting For Operation Mode and Multi-Function Pins

The following hardware settings define the desired function or interface modes of operation for some multi-function pins.

The logic level shown on setting pin below is loaded from the chip I/O pins during power on reset based on the setting of

the pin’s pulled-up (as logic ‘1’) or pulled-down (as logic ‘0’) resister on the schematic.

Chip Operation Mode setting :

Pin# 19, Pin #21

1x (default)

01

00

Operation Modes

MAC mode

Internal PHY

MAC mode

RMII

PHY mode

Reverse-RMII

Remarks

The Chip Operation Mode is determined by Pin# 19

(MFA2/RMII_N) and Pin #21 (MFA3/PHY_N) value of

AX88772B, which is called hardware setting.

EECK pin: USB force to Full Speed mode :

EECK

0

1

Description

Normal operation (default).

USB force to Full Speed mode. External pull-up resistor must be 4.7Kohm.

GPIO_1 pin: Determines whether this chip will go to Default WOL Ready Mode after power on reset. The WOL

stands for Wake-On-LAN.

GPIO_1

0

1

Description

Normal operation mode (default, see Note 1).

Enable Default WOL Ready Mode. Notice that the external pulled-up resistor must be 4.7Kohm.

For more details, please refer to APPENDIX A. Default Wake-On-LAN (WOL) Ready Mode

Note 1: This is the default with internal pulled-down resistor and doesn’t need an external one.

EEPROM Flag [12]: Defines the multi-function pin GPIO_0 / PME

GPIO_0 is a general purpose I/O normally controlled by vendor commands. Users can change this pin to operate as a PME

(Power Management Event) for remote wake up purpose. Please refer to 4.1.2 Flag of bit 12 (PME_PIN).

MFA_3 ~ MFA_0 pins: There are 4 multi-function pins for LED display purpose and as GPIO control by vendor

command.

PIN Name

Default definition

Vendor Command

LED_MUX

Vendor Command

VMFAIO

RMII_N enable

MFA3

MFA2

MFA1

MFA0

LED_USB indicater

LED_Ethernet_LINK_Active

LED_Ethernet_Speed

LED_Ethernet_Duplex_Collision

Sel_LED3

Sel_LED2

Sel_LED1

Sel_LED0

MFAIO_3

MFAIO_2

MFAIO_1

MFAIO_0

MDIO

MDC

Table 2

: MFA_3 ~ MFA_0 pin configuration

15

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

PIN configuration of MFA and MFB

Pin# 19

Pin #21

MFA2/RMII_N

MFA3/PHY_N

1: MFB7~MFB0 1: MAC Mode

0: RMII

0: PHY Mode

1

X

1

X

1

X

1

X

1

X

1

X

1

X

1

X

1

X

Description

PIN

Name

MFB0

MFB1

MFB2

MFB3

MFB4

MFB5

MFB6

MFB7

MFA0

1

X

MFA1

1

X

MFA2

1

X

MFA3

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

MFB0

MFB1

MFB2

MFB3

MFB4

MFB5

MFB6

MFB7

MFA0

MFA1

MFB0

MFB1

MFB2

MFB3

MFB4

MFB5

MFB6

MFB7

MFA0

MFA1

Function

Pin Type

MFBIO0

MFBIO1

MFBIO2

MFBIO3

MFBIO4

MFBIO5

MFBIO6

MFBIO7

Refer to MFA

Configuration

Refer to MFA

Configuration

Refer to MFA

Configuration

Refer to MFA

Configuration

MFBIO0

CRSDV

TXEN

TXD1

TXD0

REF50

RXD1

RXD0

MDC

MDIO

MFBIO0

TXEN

CRSDV

RXD1

RXD0

REF50

TXD1

TXD0

MDC

MDIO

Bidirection, controlled by MFBIOEN0

Bidirection, controlled by MFBIOEN1

Bidirection, controlled by MFBIOEN2

Bidirection, controlled by MFBIOEN3

Bidirection, controlled by MFBIOEN4

Bidirection, controlled by MFBIOEN5

Bidirection, controlled by MFBIOEN6

Bidirection, controlled by MFBIOEN7

Bidirection, controlled by MFBIOEN0

Input

Output

Output

Output

Input/Output control by EEPROM flag[1]

Input

Input

Output

I/O

Bidirection, controlled by MFBIOEN0

Input

Output

Output

Output

Input/Output control by EEPROM flag[1]

Input

Input

Input

I/O

16

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

3 Function Description

3.1 USB Core and Interface

The USB core and interface contains a USB 2.0 transceiver, serial interface engine (SIE), USB bus protocol handshaking

block, USB standard command, vendor command registers, logic for supporting bulk transfer, and an interrupt transfer,

etc. The USB interface is used to communicate with a USB host controller and is compliant with USB specification V1.1

and V2.0.

3.2 10/100M Ethernet PHY

The 10/100M Fast Ethernet PHY is compliant with IEEE 802.3 and IEEE 802.3u standards. It contains an on-chip crystal

oscillator, PLL-based clock multiplier, and a digital phase-locked loop for data/timing recovery. It provides

over-sampling mixed-signal transmit drivers compliant with 10/100BASE-TX transmit wave shaping / slew rate control

requirements. It has a robust mixed-signal loop adaptive equalizer for receiving signal recovery. It contains a baseline

wander corrective block to compensate data dependent offset due to AC coupling transformers. It supports

auto-negotiation and auto-MDIX functions.

3.3 MAC Core

The MAC core supports 802.3 and 802.3u MAC sub-layer functions, such as basic MAC frame receive and transmit, CRC

checking and generation, filtering, forwarding, flow-control in full-duplex mode, and collision-detection and handling in

half-duplex mode, etc. It provides a reduce-media-independent interface (RMII) for implementing Fast Ethernet and

HomePNA functions.

The MAC core interfaces to external RMII/Reverse-RMII interfaces and the embedded 10/100M Ethernet PHY. The

selection among the interfaces is done via setting Pin# 19 (MFA2/RMII_N) and Pin #21 (MFA3/PHY_N) of AX88772B

package pinout during power on reset (see 2.2) and using the USB vendor command, Software Interface Selection

register. Figure 8 shows the data path diagram of 10/100M Ethernet PHY and RMII/Reverse-RMII interfaces to MAC

core.

RX

10/100

Ethernet PHY

TX

RMII/Reverse

-RMII

MAC

Core

Figure 8

RXIP/RXIN

TXOP/TXON

REFCLK, RXD [1:0], CRSDV,

TXD [1:0], TXEN

: Internal Data path Diagram of 10/100M Ethernet PHY and RMII/Reverse-RMII Interfaces

17

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

3.4

Checksum Offload Engine (COE)

The Checksum Offload Engine (COE) supports IPv4, IPv6, layer 4 (TCP, UDP, ICMP, ICMPv6 and IGMP) header

processing functions and real time checksum calculation in hardware

The COE supports the following features in layer 3:

IP header parsing, including IPv4 and IPv6

IPv6 routing header type 0 supported

IPv6 in IPv4 tunnel supported

IPv4 header checksum check and generation (There is no checksum field in IPv6 header)

Version error detecting on RX direction for IP packets with version != 4 or 6

Detecting on RX direction for IP packets with error header checksum

The COE supports the following features in layer 4:

TCP and UDP checksum check and generation for non-fragmented packet

ICMP, ICMPv6 and IGMP message checksum check and generation for non-fragmented packet

Packet filtering or checksum error indication on RX direction for TCP/UDP/ICMP/ICMPv6/IGMP packets

with error checksum

3.5 Operation Mode

For simple USB 2.0 to Ethernet applications, user can use the AX88772B, which operates with internal Ethernet PHY.

AX88772B supports following three operation modes: (Ref. 2.2 Hardware Setting For Operation Mode And

Multi-Function Pins)

1.

MAC mode

2.

PHY mode

Below provides a detailed description for the three operation modes:

In MAC mode, the AX88772B Ethernet block is configured as an Ethernet MAC. From a system application

standpoint, AX88772B can be used as a USB 2.0 to LAN Adaptor (see Figure 2) or a USB 2.0 to Fast Ethernet and

HomePNA Combo (see Figure 3).

In MAC mode, the AX88772B internal datapath can work with internal Ethernet PHY or RMII interface by setting

Software Interface Selection register. Note that the PHY_ID for the internal Ethernet PHY and external one are

defined in below Table 3. Please refer to below Figure 9, Figure 10 for RMII example.

In PHY mode, the AX88772B Ethernet block is configured as an Ethernet PHY interface. In this case, an external

microcontroller with Ethernet MAC can interface with AX88772B as if it were to interface with an Ethernet PHY

chip, and AX88772B can act as a USB to Reverse-RMII bridge chip for the microcontroller to provide USB 2.0

device interface for some system applications (see Figure 4).

Please refer to below Figure 11, Figure 12 for Reverse-RMII example.

STA PHY_ID

Embedded Ethernet PHY

PHY_ID [4:0]

External Media Interface

PHY_ID [4:0]

MAC mode

10h

PHY mode

10h

{Secondary PHY_ID

[4:0]}

{Secondary PHY_ID [4:1], 0}

Note: The value of Secondary PHY_ID [4:0] is defined in EEPROM memory map 4.1.6

Table 3

: PHY_ID Definition Source

18

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

External RMII PHY chip

AX88772B

(MAC mode

with RMII)

34

29

28

33

32

31

17

18

30

CRSDV

RXD1

RXD0

CRSDV

RXD1

RXD0

TXEN

TXD1

TXD0

TXEN

TXD1

TXD0

MDC

MDIO

MDC

MDIO

REF50

REF_CLK

50MHz

OSC

Figure 9

: RMII to External PHY chip with 50MHz OSC

External RMII PHY chip

AX88772B

(MAC mode

with RMII)

34

29

28

CRSDV

RXD1

RXD0

CRSDV

RXD1

RXD0

33

32

31

TXEN

TXD1

TXD0

TXEN

TXD1

TXD0

17

18

MDC

MDIO

MDC

MDIO

30

REF50

REF_CLK

Figure 10

: RMII Interface to External PHY chip

19

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

TXEN

TXD1

TXD0

Ethernet MAC RMII of

Embedded MCU

TX_EN

TXD1

TXD0

33

32

31

CRSDV

RXD1

RXD0

CRS_DV

RXD1

RXD0

17

18

MDC

MDIO

MDC

MDIO

30

REF50

REF_CLK

AX88772B

34

(PHY mode

29

with Rev-RMII) 28

50MHz

OSC

Figure 11

: Reverse-RMII to External MAC Device with 50MHz OSC

TXEN

TXD1

TXD0

Ethernet MAC RMII of

Embedded MCU

TX_EN

TXD1

TXD0

33

32

31

CRSDV

RXD1

RXD0

CRS_DV

RXD1

RXD0

17

18

MDC

MDIO

MDC

MDIO

30

REF50

REF_CLK

AX88772B

34

(PHY mode

29

with Rev-RMII) 28

Figure 12

: Reverse-RMII Interface to External MAC Device

20

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

3.6 Station Management (STA)

The Station Management interface provides a simple, two-wire, serial interface to connect to a managed PHY device for

the purpose of controlling the PHY and gathering status from the PHY. The Station Management interface allows

communicating with multiple PHY devices at the same time by identifying the managed PHY with 5-bit, unique PHY_ID.

The PHY ID of the embedded 10/100M Ethernet PHY is being pre-assigned to “1_0000”.

The Figure 13 shows the internal control MUX of the Station Management interface when doing read in MAC operation

mode, the “mdin” signal will be driven from the embedded 10/100M Ethernet PHY only if PHY ID matches with

“1_0000”, otherwise, it will always be driven from the external MDIO pin of the ASIC.

The Station Management unit also reports the basic PHY status when operating in PHY mode acting as a PHY role (see

Figure 14). For detailed register description, please refer to the Station Management Registers in PHY mode (section 0).

Embedded 10/100M

Ethernet PHY

PHY_ID = 1_0000

(Registers refer to

Table 12)

Station Management

accessed from USB

Vendor Command

External Media Interface (EMI)

PHY ID = {Secondary PHY_ID

[4:0]}

MDC

mdout

MDIO

mdin

Station Management to

be accessed through

Reverse-RMII in PHY

mode

(Registers refer to

Table 13)

Figure 13

PM_mdc

Fixed to ‘0’

PM_mdout

PM_mdin

Fixed to ‘0’

: Internal Control MUX of Station Management Interface in MAC mode

21

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

Embedded 10/100M

Ethernet PHY

PHY_ID = 1_0000

(Registers refer to Table 12)

mdc

Station Management

accessed from USB

Vendor Command

mdout

mdin

Fixed to ‘1’

Station Management to be

accessed through MFB bus in

PHY mode

PHY ID = {Secondary

PHY_ID [4:1], 0}

(Registers refer to Table 13)

Figure 14

PM_mdc

External Media Interface (EMI)

MDC

PM_mdout

PM_mdin

MDIO

: Internal Control MUX of Station Management Interface in PHY mode

22

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

3.7 Memory Arbiter

The memory arbiter block is responsible for storing received MAC frames into on-chip SRAM (packet buffer) and then

forwarding it to the USB bus upon request from the USB host via Bulk In transfer. It also monitors the packet buffer usage

in full-duplex mode for triggering PAUSE frame (or in half-duplex mode to activate Backpressure jam signal)

transmission out on TX direction. The memory arbiter block is also responsible for storing MAC frames received from the

USB host via Bulk Out transfer and scheduling transmission out towards Ethernet network.

3.8 USB to Ethernet Bridge

The USB to Ethernet bridge block is responsible for converting Ethernet MAC frame into USB packets or vice-versa. This

block supports proprietary burst transfer mechanism (US Patent Approval) to offload software burden and to offer very

high packet transfer throughput over USB bus.

3.8.1

Ethernet/USB Frame Format Bridge

6

DA

Ethernet Frames

Super-size network packet

4

Length header

6

SA

6

6

DA

SA

2

0~1500

Length/type

Data

2

0~1500

Length/type

4

6

6

FC

S

DA

SA

4

Length header

Data

2

0~1500

Length/type

6

6

DA

SA

4

Data

2

FC

S

0~1500

Length/type

bytes

Data

USB Frames

IN/OUT

Data

Ack

IN/OUT

Data

USB packet having

the maximun packet

size

Ack

IN/OUT

Data

Ack

USB packet having

the maximun packet

size

USB packet having

the maximun packet

size

IN/OUT

Data

Short packet

3.9 Serial EEPROM Loader

The serial EEPROM loader is responsible for reading configuration data automatically from the external serial EEPROM

after power-on reset. If the content of EEPROM offset 0x00 (low byte of first word) is 0x00 or 0xFF, the Serial EEPROM

Loader will not auto-load the EEPROM. If the content of EEPROM offset 0x18 (low byte of 18th word) is not equal to

(0xFF - SUM [EEPROM offset 07H ~ 0EH]). In that case, the chip internal default value will be used to configure the chip

operation setting and to respond to USB commands, etc.

3.10 General Purpose I/O

There are 3 general-purpose I/O pins (named GPIO_0/1/2), 8 multi-function pins group B (named MFB0/1/2/3/4/5/6/7)

and 4 multi-function pins group A (named MFA0/1/2/3) provided by this ASIC.

23

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

Ack

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

3.11 Clock Generation

The AX88772B integrates internal oscillator circuits for 25Mhz, respectively, which allow the chip to operate cost

effectively with just external 25Mhz crystals. There are also three PLL circuits integrated in the chip to generate precise

clocks.

The external 25Mhz crystal or oscillator, via pins XTL25P/XTL25N, provides the reference clock to the other two

internal PLL circuit to generate a free-run 100Mhz clock source for the Reverse-RMII/RMII modes of AX88772B and a

125Mhz clock source for the embedded Ethernet PHY use.

The AX88772B can provide REF50 (50Mhz output) in Reverse-RMII/RMII modes. This output clock is derived from the

internal 100Mhz PLL circuit.

The external 25Mhz Crystal spec is listed in below table. For more details on crystal timing, please refer to 9.5.1 Clock

Timing and AX88772B Demo board schematic reference.

Parameter

Nominal Frequency

Oscillation Mode

Frequency Tolerance (@25℃)

Frequency Stability Over Operating

Temperature Range

Equivalent Series Resistance

Load Capacitance

Symbol

Typical Value

Fo

25.000000MHz

Fundamental

±30ppm

±30ppm

ESR

CL

70 Ohm max.

20pF

0℃ ~ +70℃, Commerical version

Operation Temperature Range

-40℃ ~ +85℃, Industrial version

±3ppm/year

Aging

Table 4

: The external 25MHz Crystal Units specifications

For the 25MHz oscillator, its feedback resistor isn’t

integrated into the 25MHz oscillator, so it is necessary

to add feedback resistor on external circuit.

AX88772B

XTL25P

XTL25N

25MHz

24

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

To implement the external circuits of 25MHz crystal please refer to below. One external 1Mohm resistor on 25MHz

crystal oscillator is required.

Figure 15

: One external 1M ohm resistor on 25MHz crystal oscillator is necessary

3.12 Reset Generation

The AX88772B integrates an internal power-on-reset circuit, which can simplify the external reset circuitry on PCB

design. The power-on-reset circuit generates a reset pulse to reset system logic after 1.8V core power ramping up to 1.2V

(typical threshold). The external hardware reset input pin, RESET_N, is fed directly to the input of the power-on-reset

circuit and can also be used as additional hardware reset source to reset the system logic. For more details on RESET_N

timing, please refer to 9.5.2 Reset Timing.

3.13 Voltage Regulator

The AX88772B contains an internal 3.3V to 1.8V low-dropout-voltage and low-standby-current voltage regulator. The

internal regulator provides up to 150mA of driving current for the 1.8V core/analog power of the chip to satisfy the

worst-case power consumption scenario. For more details on voltage regulator DC characteristic, please refer to 9.1.6 DC

Characteristics of Voltage Regulator.

25

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

4 Serial EEPROM Memory Map

EEPROM

OFFSET

00H

HIGH BYTE

LOW BYTE

0x5A

0x15

01H

Flag

02H

Length of High-Speed Device Descriptor (bytes)

EEPROM Offset of High-Speed Device Descriptor

03H

04H

Length of High-Speed Configuration Descriptor

(bytes)

Node ID 1

EEPROM Offset of High-Speed Configuration

Descriptor

Node ID 0

05H

Node ID 3

Node ID 2

06H

Node ID 5

Node ID 4

07H

Language ID High Byte

Language ID Low Byte

08H

Length of Manufacture String (bytes)

EEPROM Offset of Manufacture String

09H

Length of Product String (bytes)

EEPROM Offset of Product String

0AH

Length of Serial Number String (bytes)

EEPROM Offset of Serial Number String

0BH

Length of Configuration String (bytes)

EEPROM Offset of Configuration String

0CH

Length of Interface 0 String (bytes)

EEPROM Offset of Interface 0 String

0DH

Length of Interface 1/0 String (bytes)

EEPROM Offset of Interface 1/0 String

0EH

Length of Interface 1/1 String (bytes)

EEPROM Offset of Interface 1/1 String

0FH

EtherPhyMode PHY Register Offset 1 for

[2:0]

Interrupt Endpoint

10H

100

5’b0

PHY Register Offset 2 for Interrupt

Endpoint

11H

Max Packet Size High

Byte[10:8]

Secondary PHY_Type [7:5] and PHY_ID [4:0]

Max Packet Size Low Byte[7:0]

Primary PHY_Type [7:5] and PHY_ID [4:0]

12H

Pause Frame Free Buffers High Water Mark

Pause Frame Free Buffers Low Water Mark

13H

Length of Full-Speed Device Descriptor (bytes)

EEPROM Offset of Full-Speed Device Descriptor

14H

15H~17H

Length of Full-Speed Configuration Descriptor

(bytes)

Reserved

EEPROM Offset of Full-Speed Configuration

Descriptor

Reserved

18H

Ethernet PHY Power Saving Configuration

EEPROM Checksum

Note: To store the endpoint 5 descriptors, 93C66 (512-byte) is recommended.

Table 5

: Serial EEPROM Memory Map

The value of EEPROM Checksum field, EEPROM offset 0x18 (low byte) = (0xFF - SUM [EEPROM offset 07H ~

0EH])

The value of Ethernet PHY Power Saving Configuration field (i.e. high byte of EEPROM offset 0x18) is equal to 2nd

byte of Vendor Command 0x20. The AX88772B driver will read this field from high byte of EEPROM offset 0x18

and then writes it to 2nd byte of Vendor Command 0x20 at the end of driver initialization routine and during Suspend

mode configuration. This field doesn’t affect AX88772B before the driver writes it to Vendor Command 0x20.

Ethernet PHY Power Saving Configuration field

Bit15

WOLLP

Bit14

0

Bit13

IPFPS

Bit12

AutoDetach

Bit11

IPCOPSC

Bit10

IPCOPS

Bit9

IPPSL_1

26

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

Bit8

IPPSL_0

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

4.1 Detailed Description

The following sections provide detailed descriptions for some of the fields in serial EEPROM memory map. For other

fields not covered here, please refer to the AX88772B EEPROM User Guide for more details.

4.1.1 Word Count for Preload (00h)

The number of words to be preloaded by the EEPROM loader = 15h.

4.1.2 Flag (01h)

Bit 15

PME_IND

Bit 7

TACE

Bit 14

PME_TYP

Bit 6

RDCE

Bit 13

PME_POL

Bit 5

EPOM

Bit 12

PME_PIN

Bit 4

BOTM_EN

Bit 11

PHY_ISO

Bit 3

1

Bit 10

1

Bit 2

RWU

Bit 9

TDPE

Bit 1

REF50_O

Bit 8

CEM

Bit 0

SP

SP: Self-Power (for USB standard command Get Status)

1: Self power (default).

0: Bus power.

REF50_O: RMII reference 50MHz clock direction

1: Sets AX88772B provides RMII reference 50MHz clock.

0: Sets AX88772B RMII reference clock source from external 50MHz clock source (default).

RWU: Remote Wakeup support.

1: Indicate that this device supports Remote Wakeup (default).

0: Not support.

BOTM_EN: Enable the bulk-type endpoint for BOTM

1: Enable (default). Please refer to 0 .

0: Disable.

EPOM: Embedded PHY copper/fiber Operation Mode

1: Sets embedded PHY in copper mode (default).

0: Sets embedded PHY in fiber mode

RDCE: RX Drop CRC Enable.

1: CRC byte is dropped on received MAC frame forwarding to host (default).

0: CRC byte is not dropped.

TACE: TX Append CRC Enable.

1: CRC byte is generated and appended by the ASIC for every transmitted MAC frame (default).

0: CRC byte is not appended.

CEM: Capture Effective Mode.

1: Capture effective mode enables (default).

0: Disabled.

TDPE: Test Debug Port Enable.

1: Enable test debug port for chip debug purpose.

0: Disable test debug port and the chip operate in normal function mode (default).

PHY_ISO: Set RMII bus to isolate mode when operating in PHY mode.

1: Set RMII bus to isolate mode (default). AX88772B can be in isolate mode when operating in PHY mode with

Reverse-RMII. Following output pins are tri-stated in isolate mode.

In Reverse-RMII mode: RXD [1:0] and CRSDV, RXER, except for REF50.

0: Set RMII bus to non-isolate mode.

27

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

PME_PIN: PME / GPIO_0

1: Set GPIO_0 pin as PME (default).

0: GPIO_0 pin is controlled by vendor command.

PME_POL: PME pin active Polarity.

1: PME active high.

0: PME active low (default).

PME_TYP: PME I/O Type.

1: PME output is a Push-Pull driver.

0: PME output to function as an open-drain buffer (default).

PME_IND: PME indication.

1: A 1.363ms pulse active when detecting wake-up event.

0: A static signal active when detecting wake-up event (default).

4.1.3 Node ID (04~06h)

The Node ID 0 to 5 bytes represent the MAC address of the device, for example, if MAC address = 01-23-45-67-89-ABh,

then Node ID 0 = 01, Node ID 1 = 23, Node ID 2 = 45, Node ID 3 = 67, Node ID 4 = 89, and Node ID 5 = AB.

Default values: Node ID {0, 1, 2, 3, 4, 5} = 0x000E_C687_7201.

4.1.4 PHY Register Offset for Interrupt Endpoint (0Fh)

Bit 15

Bit 14

Bit 13

EtherPhyMode

Bit 7

Bit 6

Bit 5

100

Bit 12

Bit 11

Bit 10

Bit 9

PHY Register Offset 1

Bit 3

Bit 2

Bit 1

PHY Register Offset 2

Bit 4

Bit 8

Bit 0

PHY Register Offset 1: Fill in PHY’s Register Offset of Primary PHY here. Upon each Interrupt Endpoint issued, its

register value will be reported in byte# 5 and 6 of Interrupt Endpoint packet (default = 00101)

PHY Register Offset 2: Fill in PHY’s Register Offset of Primary PHY here. Upon each Interrupt Endpoint issued, its

register value will be reported in byte# 7 and 8 of Interrupt Endpoint packet (default = 00000)

EtherPhyMode: as below table (default = 000),

EtherPhyMode [2:0]

000

001

010

011

100

101

110

Function

Auto-negotiation enable with all capabilities

Auto-negotiation with 100BASE-TX FDX / HDX ability

Auto-negotiation with 10BASE-TX FDX / HDX ability

Reserved

Manual selection of 100BASE-TX FDX

Manual selection of 100BASE-TX HDX

Manual selection of 10BASE-T FDX

111

Manual selection of 10BASE-T HDX

Note:

1. EtherPhyMode is used to set the operation mode of embedded Ethernet PHY directly. For normal operation

mode, set them to 000.

2. This value is latched into embedded Ethernet PHY right after it leaves reset. After that, software driver can

still make change Ethernet PHY link ability through vendor command PHY Write Register to access

embedded Ethernet PHY register.

28

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

4.1.5 Max Packet Size High/Low Byte (10h)

Fill the maximum RX/TX MAC frame size supported by this ASIC. The number must be even number in terms of bytes

and should be less than or equal to 2048 bytes (default = 0600h).

4.1.6 Primary/Secondary PHY_Type and PHY_ID (11h)

The 3 bits PHY_Type field for both Primary and Secondary PHY is defined as follows,

000: 10/100M Ethernet PHY or 1M HomePNA PHY.

111: non-supported PHY. For example, the High Byte value of “E0h” means that secondary PHY is not supported.

Default values: Primary {PHY_Type, PHY_ID} = 10h. Secondary {PHY_Type, PHY_ID} = E0h. Note that the PHY_ID

of the embedded 10/100M Ethernet PHY is being assigned to “10h”.

Secondary PHY_ID always defines The PHY_ID of External Media Interface (EMI) and Secondary PHY_TYPE is not

used in that case. Please refer to Table 3 for more information.

4.1.7 Pause Frame Free Buffers High Water and Low Water Mark (12H)

When operating in full-duplex mode, correct setting of this field is very important and can affect the overall packet receive

throughput performance a great deal. The High Water Mark is the threshold to trigger sending Pause frame and the Low

Water Mark is the threshold to stop sending Pause frame. Note that each free buffer count here represents 128 bytes of

packet storage space in SRAM.

These setting values are also used in half-duplex mode to activate Backpressure to send /stop jam signal.

Total free buffer count = 128

Stop sending Pause frame when free buffer > Low Water Mark (default = 42h)

Start sending Pause frame when free buffer < High Water Mark (default = 24h)

Total free buffer count = 0

Figure 16

: Water level setting for flow control

4.1.8 Power-Up Steps

After power-on reset, AX88772B will automatically perform the following steps to the Ethernet PHYs via MDC/MDIO

lines (only take effect when Chip Operation Mode is in MAC mode with external PHY on RMII interface).

1. Write to PHY_ID of 00h with PHY register offset 00h to power down all PHYs attached to station management

interface.

2. Write to Primary PHY_ID with PHY register offset 00h to power down Primary PHY.

3. Write to Secondary PHY_ID with PHY register offset 00h to power down Secondary PHY.

Notice that enabling Default WOL Ready Mode (see 2.2 GPIO_1 Settings) will disable above power-up step (to prevent

external Ethernet PHY on RMII interface from entering power-down mode), if external PHY is used.

29

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

4.2 Internal ROM Default Settings

AX88772B supports some default settings inside chip hardware to enable it to communicate with USB host

controller during enumeration when the AX88772B EEPROM is blank (prior to being programmed) or the value of

EEPROM Checksum field is wrong. The default settings inside chip facilitate users to update the EEPROM content

through a Windows PC during R&D validation process or program a blank EEPROM mounted on target system PCB

during manufacturing process.

Below table shows AX88772B’s internal default settings being used in the case of blank EEPROM or EEPROM

with wrong checksum value on board. Each of the address offset contains 16-bit data from left to right representing

the low-byte and high-byte, respectively. For example, in offset address 0x01, the ‘FD’ is low-byte data and the ‘1D’

is high-byte data.

Offset

Address

0x00

0x08

0x10

0x18

0x20

0x28

0x30

0x38

0x40

0x48

0x50

0x58

0x60

0x68

0x70

0x78

0x80

0x88~FF

0

8

15 00

6E 22

00 06

FF 08

12 01

03 01

FF FF

02 00

07 05

00 02

09 02

00 07

07 05

05 02

53 00

2E 00

41 00

FF FF

1

9

FD 1D

7F 12

10 E0

0E 03

00 02

09 02

00 07

07 05

05 02

FF FF

35 00

07 05

03 02

40 00

49 00

20 00

58 00

FF FF

Table 6

2

A

20 12

19 0E

42 24

30 00

FF FF

35 00

07 05

03 02

00 02

00 08

01 01

81 03

40 00

00 DD

58 00

43 00

38 00

FF FF

3

B

29 35

44 04

47 12

30 00

00 40

01 01

81 03

00 02

00 FF

95 0B

04 E0

08 00

00 07

FF FF

20 00

6F 00

38 00

FF FF

4

C

00 0E

44 04

50 35

30 00

95 0B

04 E0

08 00

00 07

04 03

2B 77

02 09

A0 07

05 84

AA AA

45 00

72 00

37 00

FF FF

5

D

C6 87

44 04

FF FF

30 00

2B 77

02 09

0B 07

05 84

30 00

01 00

04 00

05 82

02 40

BB BB

6C 00

70 00

37 00

FF FF

6

E

72 01

44 04

00 00

30 00

01 00

04 00

05 82

02 00

FF FF

01 02

00 05

02 40

00 00

22 03

65 00

2E 00

32 00

FF FF

7

F

09 04

80 05

FF FF

31 00

01 02

00 05

02 00

02 00

12 01

03 01

FF FF

00 00

07 05

41 00

63 00

12 03

42 00

FF FF

: Internal ROM Memory Map

Note:

1. The default high-byte data of offset 0x00 is 0x00.

2. The bulk out endpoint 5 enabled since bit 4 (BOTM_EN) of offset 01h is set to 1.

3. The default PID/VID is 772Bh/0B95h.

4. The default MAC address is 00-0E-C6-87-72-01, but the real MAC address is 00-00-00-00-00-00 that was

auto-loaded from the AX88772B internal ROM default setting into the AX88772B Node ID register. User

should manually assign a valid MAC address through the AX88772B driver parameter or by setting AX88772B

Node ID register for normal network operation.

5. The default Manufacture string is “ASIX Elec. Corp.”.

6. The default Product string is “AX88772B”.

7. The default Serial Number is “000001”.

8. The default operation mode is set to Self-Power and Remote Wakeup enabled.

9. Max Power setting to 4mA. Expressed in 2mA (for example, 0x02 indicates for 4mA)

10. The default “AutoDetach” function is disabled and set to Cable Off Power Saving Level 0.

11. The default value of EEPROM Checksum field is 0xFF.

30

Copyright © 2010-2013 ASIX Electronics Corporation. All rights reserved.

�AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

4.2.1 Internal ROM Description

The internal ROM is a fixed value. User can’t modify it.

Field Definition