BCM8705

®

SERIAL 10-GBE/FIBRE CHANNEL TRANSCEIVER WITH WIS LAYER AND

XAUI™ INTERFACE

SUMMARY OF BENEFITS

FEATURES

• Fully integrated CMU, CDR, SerDes, limiting amplifier,

EyeOpener®, and 4-lane XAUI™ interface

• PMD interface supported serial rates: 9.953/10.3125/

10.5188-Gbps

• Receive equalization on XAUI and 10G serial interfaces

• Transmit pre-emphasis and amplitude control on XAUI interface

• 10G PMD interface phase and decision threshold adjust

• WIS layer for EOS/WAN applications

• SONET performance monitoring

• Supports Broadcom’s StrataXGS® Ethernet switches service

aware flow control (SAFC) protocol

SONET) application

• Universal design for 10-GbE, SONET, and 10 GFC for

XENPAK/X2 module

• Compliant to XENPAK/X2 3.0 and XPAK MSA optical

module standards

• Integrated and compact design allows for high-density line

card applications

• Upgrade path for existing Broadcom LAN PHY transceivers

• Build-in features reduce external components

• Meets and exceeds industry standard

• IEEE 802.3™ae serial Ethernet transceiver (LAN/WAN PHY),

MDIO Clause 45 management interface with extended indirect

address register access

• 10-Gigabit Fibre Channel draft, rev 3.0

• Support for XFP/XFI interfaces

• Support for XENPAK/X2 3.0 and XPAK MSA optical module

standards

• Additional features

•

•

•

•

•

•

• Best performance for LAN (10-GbE) and WAN (OC-192

• Clean-up PLL

• 2.5V voltage regulator output

• In-rush current limits

APPLICATIONS

• XENPAK, X2, XPAK modules

Jumbo packets support in WAN mode

Reference clock output for XFP module reference clock

I2C master to control XFP module from device

Staged power-up mode to minimize in-rush current

Loopback modes supporting IEEE standards modes

Built-in self-test (BIST) and PRBS generator/checker

• Interface to XFP modules

• LAN/MAN/WAN switch/routers

• Pin-compatible with the BCM8704

• Low power: LAN mode 900 mW, WAN mode 1.0W to 1.1W

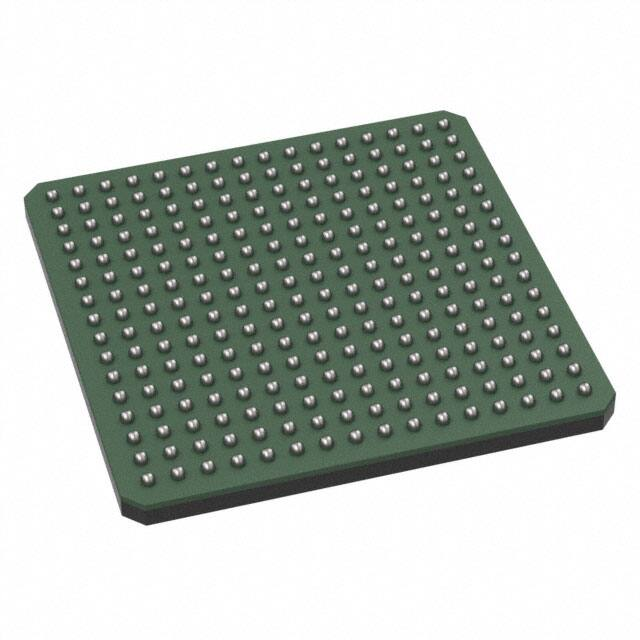

• Available in 13-mm x 13-mm and 17-mm x 17-mm plastic BGA

• Hubs and repeaters

• Network interface cards (NICs)

(Pb-free version also available)

BCM8705 Block Diagram

XAUI

BCM8705

MAC

MDC MDIO

Management

Interface

9.953/10.3125/10.5188

Gbps

WIS

XGXS

Media

Access

Controller

Interface

PCS/PMA

RS

XGXS

OTX

ORX

Optical

PMD

EEPROM

�OVERVIEW

System/MAC Interface

XAUI

outputs

X[A:D]OP/N

Differential CML

XAUI

inputs

X[A:D]IP/N

AC-coupled

internally biased

differential CML

Line/Fiber-Optic Module Interface

AC-coupled

internally biased

differential CML

PPDOUT

PCOP/N

Differential CML

XPDOUT

External VCXO

PEXTCLKP/N

XEXTCLKP/N

PVCOXP/N

PDOP/N

AC-coupled

internally biased

differential LVPECL

SYSRSTB

RSTB

MDC

MDIO

PRTAD[4:0]

Control

and

Status

PLOSB/A1

PMD Analog

XAUI

CMOS

LASI

TXONOFF

JTAG

TRSTB

JTCK

TMS

TDI

TDO

10G Serial

Outputs

CDR Loop

Filter

PMD

2WENB

CONFIG[1:0]

SDA

SCL

VCPCDR

VCNCDR

10G Serial

Inputs

CMOS

PCDRLK

PCMULK

REFCLKOUT

2-Wire

interface

PDIP/N

CMOS

OPTXENB0/1

OPTXRST0/1

OPRXLOS

OPBIASFLT

OPTMPFLT

OPPWFLT

OPTXFLT

OPRXFLT

OPOUTLVL

OPINLVL

Optics

Control

and

Status

BCM8705 Fully Integrated Interface

The BCM8705 Ethernet/Fibre Channel/SONET LAN/WAN PHY is a

fully integrated serialization/deserialization (9.953/10.3125/

10.5188-Gbps) interface device performing the extension functions for a

10-gigabit serial Ethernet reconciliation sublayer (RS) interface. The

XGXS, PCS, and PMA functions include 8B/10B coding, 64B/66B

coding, SerDes, WIS, clock multiplication unit (CMU), and clock and

data recovery (CDR).

On-chip clock synthesis is performed by the high-frequency low-jitter

phase-locked loops for the PMD and XAUI output retimers. Individual

PMD and XAUI clock recovery is performed on the device by

synchronizing directly to their respective incoming data streams. Elastic

buffers are provided to allow the XAUI and PMD interfaces to operate

in asynchronous configuration. Only an external 155.52/156.25/

159.38-MHz oscillator is required for the reference clock input.

For WAN applications, a WIS-compliant framer with flexible clocking

modes allows transmission of Ethernet traffic over a WAN network.

The BCM8705 is available in a 13-mm × 13-mm, 256-pin FBGA with a

0.8-mm ball pitch and also in a 17-mm x 17-mm, 256-pin 1-mm ball

pitch RoHS-compliant package.

Broadcom®, the pulse logo, Connecting everything®, the Connecting everything logo, EyeOpener®,

and StrataXGS® are among the trademarks of Broadcom Corporation and/or its affiliates in the United

States, certain other countries and/or the EU. Any other trademarks or trade names mentioned are the

property of their respective owners.

®

BROADCOM CORPORATION

16215 Alton Parkway, P.O. Box 57013

Irvine, California 92619-7013

© 2006 by BROADCOM CORPORATION. All rights reserved.

8705-PB02-R

04/17/06

Phone: 949-450-8700

Fax: 949-450-8710

E-mail: info@broadcom.com

Web: www.broadcom.com

�

很抱歉,暂时无法提供与“BCM8705BIFBG”相匹配的价格&库存,您可以联系我们找货

免费人工找货