PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Features

Description

ÎÎPhase jitter filter for PCIe 3.0/ 2.0/ 1.0 application

Pericom Semiconductor's PI6CDBL402B is a PCIe 3.0 compliant

high-speed, low-noise differential clock buffer designed to be

companion to PCIe 3.0 clock generator. It is backward compatible with PCIe 1.0 and 2.0 specification.

ÎÎLow power consumption with independent output power

supply 1.8V~3.3V

ÎÎLow skew < 60ps

ÎÎLow cycle-to-cycle jitter - 45ps (typ.) @100MHz

The device distributes the differential SRC clock from PCIe 3.0

clock generator to four differential pairs of clock outputs either

with or without PLL. The clock outputs are controlled by input

selection of PWRDWN# and SMBus, SCLK and SDA.

ÎÎ< 1 ps additive RMS phase jitter

ÎÎOutput Enable for all outputs

ÎÎProgrammable PLL Bandwidth

ÎÎ100 MHz PLL Mode operation

ÎÎ1 - 400 MHz Bypass Mode operation

ÎÎ3.3V Operation

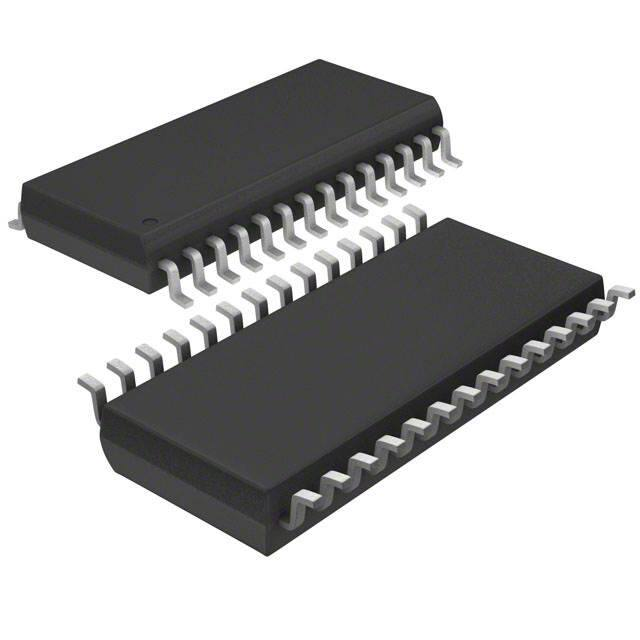

ÎÎPackaging (Pb-free and Green):

-28-Pin TSSOP (L28)

Block Diagram

OE_INV

OE_0 & OE_3

PWRDWN#

SCLK

SDA

Pin Configuration

Output

Control

OUT0

OUT0#

OUT1

OUT1#

SMBus

Controller

OUT2

OUT2#

PLL/BYPASS#

OUT3

OUT3#

SRC

SRC#

PLL_BW#

VDD

SRC

SRC#

GND

VDDO

OUT0

OUT0#

OE_0

OUT1

OUT1#

VDDO

PLL/BYPASS#

PLL/BYPASS#

SCLK

SDA

PLL

All trademarks are property of their respective owners.

15-0083

1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDD_ A

GNDA

NC

OE_INV

VDDO

OUT3

OUT3#

OE_3

OUT2

OUT2#

VDDO

PLL_BW#

VDD

PWRDWN#

www.pericom.com 06/30/15

�PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Pin Description

Pin #

Pin Name

Type

Description

2, 3

SRC & SRC#

Input

0.7V Differential SRC input from PI6C410 clock synthesizer

3.3V LVTTL input for enabling outputs, active high.

8, 21

OE_0 & OE_3

Input

OE_0 for OUT0 / OUT0#

OE_3 for OUT3 / OUT3#

3.3V LVTTL input for inverting the OE and PWRDWN# pins.

25

OE_INV

Input

When 0 = same stage

When 1 = OE_0, OE_3, PWRDWN# inverted.

6, 7, 9, 10, 19, 20, 22, 23

OUT[0:3] & OUT[0:3]#

Output

0.7V Differential outputs, refer Power Management Table for

detail output status

12

PLL/BYPASS#

Input

3.3V LVTTL input for selecting fan-out of PLL operation.

13

SCLK

Input

SMBus compatible SCLOCK input

14

SDA

I/O

SMBus compatible SDATA

26

NC

17

PLL_BW#

Input

3.3V LVTTL input for selecting the PLL bandwidth

15

PWRDWN#

Input

3.3V LVTTL input for Power Down operation, active low

5, 11, 18, 24

VDDO

Power

Power supply for outputs, range from 1.8V~3.3V

4

GND

Ground

Ground for Outputs

27

GNDA

Ground

Ground for PLL

28

VDD_A

Power

3.3V Power Supply for PLL

1, 16

VDD

Power

3.3V Power Supply for PLL

All trademarks are property of their respective owners.

No Connect

15-0083

2

www.pericom.com 06/30/15

�PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Power Management Table

Output[0]/ Output[3] state choose

OE_INV

PWRDWN#

Byte0/Bit7

OE_0/OE_3(Pin) OE(SMBus bit)

OUT0/ OUT3

OUT0#/ OUT3#

0

X

X

0

X

LOW

LOW

0

X

X

X

0

LOW

LOW

0

0

0

1

1

HIGH

LOW

0

0

1

X

X

LOW

LOW

0

1

X

1

1

Clock output

Clock output

1

X

X

1

X

LOW

LOW

1

X

X

X

0

LOW

LOW

1

1

0

0

1

HIGH

LOW

1

1

1

X

X

LOW

LOW

1

0

X

0

1

Clock output

Clock output

Output[1]/ Output[2] state choose

OE_INV

PWRDWN#

Byte0/Bit7

OE(Pin)

OE(SMBus bit)

OUT1/ OUT2

OUT1#/ OUT2#

0

X

X

NA

0

LOW

LOW

0

0

0

NA

1

HIGH

LOW

0

0

1

NA

X

LOW

LOW

0

1

X

NA

1

Clock output

Clock output

1

X

X

NA

0

LOW

LOW

1

1

0

NA

1

HIGH

LOW

1

1

1

NA

X

LOW

LOW

1

0

X

NA

1

Clock output

Clock output

Notes:

1. all registers can’t be written/read during PWRDWN# active

Serial Data Interface (SMBus)

This part is a slave only device that supports blocks read and block write protocol using a single 7-bit address and read/write bit as

shown below.

Read and write block transfers can be stopped after any complete byte transfer by issuing STOP.

Address Assignment

A6

A5

A4

A3

A2

A1

A0

W/R

1

1

0

1

1

1

0

0/1

Data Protocol

1 bit

7 bits

1

1

8 bits

1

8 bits

1

8 bits

1

Start

bit

Slave

Addr

R/W

Ack

Register

offset

Ack

Byte

Count

=N

Ack

Data

Byte 0

Ack

…

8 bits

1

1 bit

Data

Byte N

-1

Ack

Stop bit

Notes:

1. Register offset for indicating the starting register for indexed block write and indexed block read. Byte Count in write mode cannot be 0.

All trademarks are property of their respective owners.

15-0083

3

www.pericom.com 06/30/15

�PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Data Byte 0: Control Register

Bit

Descriptions

0

Reserved

Type

Power Up Condition

Output(s) Affected

Source Pin

NA

PLL/BYPASS#

1

0 = Fanout

RW

1 = PLL

OUT[0:3], OUT[0:3]#

NA

RW

1 = Low

OUT[0:3], OUT[0:3]#

NA

1 = PLL

PLL Bandwidth

2

0 = High Bandwidth,

1 = Low Bandwidth

3

Reserved

NA

4

Reserved

NA

5

Reserved

NA

6

Reserved

NA

7

PD_Mode

Refer Power Management Table

RW

0

OUT[0:3], OUT[0:3]#

NA

Type

Power Up Condition

Output(s) Affected

Source Pin

Data Byte 1: Control Register

Bit

Descriptions

0

Reserved

1

OUTPUTS enable

RW

1 = Enabled

OUT0, OUT0#

NA

2

1 = Enabled

0 = Disabled

RW

1 = Enabled

OUT1, OUT1#

NA

3

Reserved

NA

4

Reserved

NA

5

OUTPUTS enable

RW

1 = Enabled

OUT2, OUT2#

NA

6

1 = Enabled

0 = Disabled

RW

1 = Enabled

OUT3, OUT3#

NA

7

Reserved

All trademarks are property of their respective owners.

NA

NA

15-0083

4

www.pericom.com 06/30/15

�PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Data Byte 2: Control Register

Bit

Descriptions

Type

Power Up Condition

Output(s) Affected

Source Pin

0

Reserved

NA

1

Reserved

NA

2

Reserved

NA

3

Reserved

NA

4

Reserved

NA

5

Reserved

NA

6

Reserved

NA

7

Reserved

NA

Data Byte 3: Control Register

Bit

Descriptions

Type

Power Up Condition

Output(s) Affected

Source Pin

Type

Power Up Condition

Output(s) Affected

Source Pin

0

R

0

NA

NA

1

R

0

NA

NA

2

R

0

NA

NA

R

0

NA

NA

R

0

NA

NA

5

R

1

NA

NA

6

R

0

NA

NA

7

R

0

NA

NA

0

RW

1

RW

2

RW

3

4

Reserved

RW

RW

5

RW

6

RW

7

RW

Data Byte 4: Control Register

Bit

3

4

Descriptions

Pericom ID

All trademarks are property of their respective owners.

15-0083

5

www.pericom.com 06/30/15

�PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Power Down (PWRDWN# assertion)

PWRDWN#

OUT

OUT#

Figure 1. Power down sequence

Power Down (PWRDWN# De-assertion)

Tstable

200 mV

4. DIF_IN input

5. The differential input clock must be running for the SMBus to be active

Electrical Characteristics–DIF 0.7V Low Power HCSL Outputs (TA = -40~85oC; VDD = 3.3V+/-10%;

VDDO = 3.3V+/-10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for Loading Conditions)

Symbol

Parameters

Condition

Trf

Slew rate1,2,3

VHIGH

Voltage High

VLOW

Voltage Low

Vmax

1,7

1,7

Statistical measurement on single-ended signal using

oscilloscope math function. (Scope averaging on)

Min.

Type

Max.

Units

1.1

2

4.5

V/ns

660

950

mV

-150

200

mV

1150

mV

1

Max Voltage

Measurement on single ended signal using

Vmin

1

Min Voltage

absolute value. (Scope averaging off)

-300

mV

Vswing

Vswing

Scope averaging off

300

mV

Crossing Voltage

(abs)

Vcross_abs

Scope averaging off

250

Crossing Voltage

(var)

Δ-Vcross

Scope averaging off

1,2,7

550

mV

140

mV

Note:

1. Guaranteed by design and characterization, not 100% tested in production.

2. Measured from differential waveform

3. Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

4. Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point

where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

5. Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and

Clock# falling).

6. The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross_min/max (Vcross absolute) allowed. The intent is

to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

7. At default SMBus settings.

All trademarks are property of their respective owners.

15-0083

10

www.pericom.com 06/30/15

�PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Electrical Characteristics–Current Consumption (TA = -40~85oC; VDD = 3.3V+/-10%; VDDO = 3.3V+/10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for Loading Conditions)

Symbol

Parameters

Condition

IDDOP

Operating Supply Current1

IDDPD

Powerdown Current1,2

Min.

Type

Max.

Units

Total power consumption, All outputs active

@100MHz, typical value under VDDO = 1.8V

50

60

mA

Total power consumption, All outputs active

@100MHz PLL bypass mode, typical value

under VDDO = 1.8V

24

28

mA

1.3

mA

Total power consumption, Outputs Low

Note:

1. Guaranteed by design and characterization, not 100% tested in production.

2. Input clock stopped.

Electrical Characteristics–Output Duty Cycle, Jitter, Skew and PLL Characterisitics (TA =

-40~85oC; VDD = 3.3V+/-10%; VDDO = 3.3V+/-10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for

Loading Conditions)

Symbol

Parameters

Condition

Min.

tDC

Duty Cycle

Measured differentially, PLL Mode

45

tDCD

Duty Cycle Distortion1,3

Measured differentially, Bypass Mode

@100MHz

-1.3

Bypass Mode, VT = 50%

PLL Mode VT = 50%

tpdBYP

tpdPLL

1

Skew, Input to Output1,4

tskew

Skew, Output to Output

tjcyc-cyc

Jitter, Cycle to cycle1,2

1,2

Type

Max.

Units

55

%

1.3

%

2500

5000

ps

-260

260

ps

PLL Mode VT = 50%

60

ps

PLL mode

60

ps

Additive Jitter in Bypass Mode

25

ps

0

Note:

1. Guaranteed by design and characterization, not 100% tested in production.

2. Measured from differential waveform

3. Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

4. All outputs at default slew rate

5. The MIN/TYP/MAX values of each BW setting track each other, i.e., Low BW MAX will never occur with Hi BW MIN.

All trademarks are property of their respective owners.

15-0083

11

www.pericom.com 06/30/15

�PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Electrical Characteristics–Phase Jitter Parameters (TA = -40~85oC; VDD = 3.3V+/-10%; VDDO =

3.3V+/-10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for Loading Conditions)

Symbol

Parameters

Condition

Min.

PCIe Gen 11,2,3

tjphPCIeG1

PCIe Gen 2 Lo Band

tjphPCIeG2

10kHz < f < 1.5MHz1,2

Phase Jitter,

PLL Mode

PCIe Gen 2 High Band

1.5MHz < f < Nyquist (50MHz)1,2

PCIe Gen 3

tjphPCIeG3

(PLL BW of 2-4MHz, CDR = 10MHz)

1,2,3,4

Type

Industry

Limit

34

86

0.9

3

2.2

3.1

0.5

1

tjphSGMII

125MHz, 1.5MHz to 20MHz, -20dB/decade rollover <

1.5MHz, -40db/decade rolloff > 10MHz1,6

1.9

NA

tjphPCIeG1

PCIe Gen 11,2,3

0.6

N/A

0.1

N/A

0.05

N/A

0.05

N/A

0.15

N/A

PCIe Gen 2 Lo Band

tjphPCIeG2

Additive

Phase Jitter,

Bypass Mode

tjphPCIeG3

tjphSGMII

10kHz < f < 1.5MHz

1,2,5

PCIe Gen 2 High Band

1.5MHz < f < Nyquist (50MHz)

1,2,5

PCIe Gen 3

(PLL BW of 2-4MHz, CDR = 10MHz)

1,2,4,5

125MHz, 1.5MHz to 10MHz, -20dB/decade rollover <

1.5MHz, -40db/decade rolloff > 10MHz1,6

Units

ps

(p-p)

ps

(rms)

ps

(rms)

ps

(rms)

ps

(rms)

ps

(p-p)

ps

(rms)

ps

(rms)

ps

(rms)

ps

(rms)

Note:

1. Applies to all outputs, with device driven by 9FG432AKLF or equivalent.

2. See http://www.pcisig.com for complete specs

3. Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12.

4. Subject to final ratification by PCI SIG.

5. For RMS figures, additive jitter is calculated by solving the following equation: Additive jitter = SQRT[(total jitter)^2 - (input jitter)^2]

6. Applies to all differential outputs

All trademarks are property of their respective owners.

15-0083

12

www.pericom.com 06/30/15

�PI6CDBL402B

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Packaging Mechanical: 28-Pin TSSOP (L)

DOCUMENT CONTROL NO.

PD - 1313

REVISION: D

28

DATE: 03/09/05

.169

.177

4.3

4.5

.004

.008

1

.378

.386

9.6

9.8

0.45

0.75

0.09

0.20

.018

.030

.252

BSC

6.4

1

.047

1.20

Max

SEATING

PLANE

.0256

BSC

0.65

.007

.012

0.19

0.30

.002

.006

0.05

0.15

Pericom Semiconductor Corporation

3545 N. 1st Street, San Jose, CA 95134

1-800-435-2335 • www.pericom.com

Note:

1. Package Outline Exclusive of Mold Flash and Metal Burr

2. Controlling dimentions in millimeters

3. Ref: JEDEC MO-153F/AE

DESCRIPTION: 28-Pin, 173-Mil Wide, TSSOP

PACKAGE CODE: L

Ordering Information(1-3)

Ordering Code

Package Code

Package Description

PI6CDBL402BLIE

LE

28-pin, 173-mil wide (TSSOP)

PI6CDBL402BLIEX

LE

28-pin, 173-mil wide (TSSOP), Tape & Reel

Notes:

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

2. E = Pb-free and Green

3. Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336

All trademarks are property of their respective owners.

15-0083

13

www.pericom.com 06/30/15

�