PI74STX1G79

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

SOTiny Gate STX

Single Positive-Edge-Triggered

D-Type Flip-Flop

Features

Description

High-speed: tPD = 2.4ns typical into 50pF @ 5V VCC

The PI74STX1G79 is a Single Positive-Edge-Triggered D-Type

Flip-Flop that operates over the 1.65V to 5.5V VCC operating range.

Broad operating range: VCC = 1.65V 5.5V

Pericoms PI74STX series of products are produced using the

Companys advanced submicron technology.

Power down high-impedance inputs/outputs

High output drive: ±24mA at 3V VCC

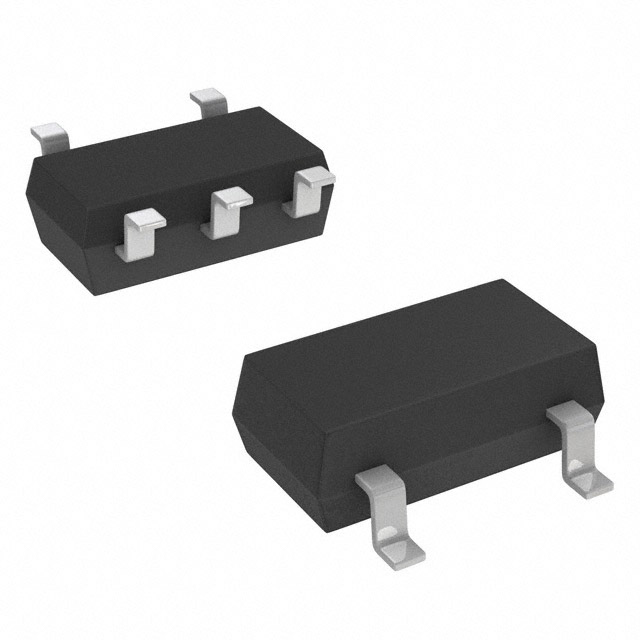

Package: 5-pin space saving SOT23 and SC70

Block Diagram

Pinout

DIN

1

CLK

2

GND

3

5-Pin

T, C

5

VCC

4

QOUT

DIN

Pin Description

Recommended Operating Conditions(1)

Parame te r

Pin Name s

D e s cription

CLK

Clock

Supply Voltage (VCC)

DIN

Input

Q OUT

O utput

Function Table

Inputs

D

Q

H

L

X

H

L

Q0

M in. M ax.

5.5

Input Voltage (VIN)

0

5.5

Output Voltage (VOUT)

0

VCC

Operating Temperature

40

85

VCC = 1.8V,

2.5V±0.2V

0

20

VCC = 3.3V,

±0.3V

0

10

VCC =5.0V,

±0.5V

0

5

Input Rise and

Fall Time (tr,tf)

Note:

H = HIGH Voltage Level

L = LOW Voltage Level

X = Dont Care

↑ = LOW-to-HIGH Transition

Q0 = Level of Q before the indicated steady-state input

conditions were established

Condition

1.65

Output

CLK

L

QOUT

CLK

Units

V

°C

ns/V

Note:

1. Unused inputs must be held HIGH or LOW. They may not float.

1

PS8569A

01/31/02

�PI74STX1G79

SOTiny Gate STX Single Positive

Edge-Triggered D-Type Flip-Flop

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

Absolute Maximum Ratings

DC VCC/GND Current (ICC/IGND) ................................ ±50mA

Storage Temperature (TSTG) .......................... 65°C to +150°C

Junction Lead Temperature (IOS) ................................... 200°C

Power Dissipation SOT23 ............................................ 200mW

SC70 ............................................... 150mW

Supply Voltage (VCC) .......................................... 0.5V to +6V

DC Input Voltage (VIN) ....................................... 0.5V to +6V

DC Output Voltage (VOUT) ................................. 0.5V to +6V

DC Input Diode Current (IIK) ........................ 50mA to 20mA

DC Output Diode Current (IOK) .................... 50mA to 20mA

DC Output Current (IOUT) ........................................... ±50mA

Note:

Absolute maximum ratings are DC values beyond which the device may be damaged or have its useful life impaired. The datasheet

specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and

output/input loading variables. Pericom does not recommend operation outside datasheet specifications.

DC Electrical Characteristics (Over supply voltage and operating temperature ranges, unless otherwise specified)

TA = +25°C

Symbol

Parame te r

VCC (V)

VIH

HIGH Level

Input Voltage

1.65- 1.95

2.3- 5.5

VIL

LOW Level

Input Voltage

1.65- 1.95

2.3- 5.5

VOH

HIGH Level

Output Voltage

1.65

1.8

2.3

3.0

4.5

1.65

2.3

3.0

3.0

4.5

VOL

LOW Level

Output Voltage

IIN

Input Leakage

Current

IOFF

Power Off

Leakage Current

ICC

Quiescent Supply

Current

1.65

1.8

2.3

3.0

4.5

Conditions

M in.

Typ.

TA = 40 to +85°C

M ax.

0.75VCC

0.70VCC

M in.

0.25VCC

0.30VCC

IOH = 100µA

1.55

1.7

2.2

2.

4.4

1.65

1.79

2.29

2.99

4.5

1.55

1.9

2.4

2.3

4.4

IOH =

IOH =

IOH =

IOH =

IOH =

1.29

1.9

2.4

2.3

3.8

1.52

2.13

2.71

2.55

4.20

1.29

1.9

2.4

2.3

3.8

4mA

8mA

16mA

24mA

32mA

VIN = VIH IOL = 100µA

V

0.01

0.01

0.01

0.00

0.00

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.08

0.10

0.18

0.28

0.28

0.24

0.3

0.4

0.55

0.55

0.24

0.3

0.4

0.55

0.55

1.65

2.3

3.0

3.0

4.5

IOL =

IOL =

IOL =

IOL =

IOL =

0- 5.5

VIN = 5.5V, GND

1

1

1

1

VIN or VOUT = 5.5V

1

1

1

1

0.0

4mA

8mA

16mA

24mA

32mA

1.65- 5.5 VIN = 5.5V, GND

2.0

2

Units

0.75VCC

0.70VCC

0.25VCC

0.30VCC

VIN = VIL

M ax.

µA

20

PS8569A

01/31/02

�PI74STX1G79

SOTiny Gate STX Single Positive

Edge-Triggered D-Type Flip-Flop

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

AC Electrical Characteristics

TA = 40°C to

+85°C

TA = +25°C

Symbol

fMAX

tPLH,

tPHL

Parame te r

Maximum Clock Frequency

Propagation Delay CLK to QOUT

Setup Time, CLK to DIN

tS

Fig.

N o.

VCC (V)

Conditions

M in.

1.8 ±0.15

2.5 ±0.2

3.3 ±0.3

5.0 ±0.5

CL = 50pF,

RL = 500 ohms

100

125

150

150

1.8 ±0.15

2.5 ±0.2

3.3 ±0.3

5.0 ±0.5

CL = 15pF,

RL = 1 Mohm

3.0

1.8

1.5

1.0

6.6

3.7

2.8

2.1

7.2

4.1

3.2

2.6

3.0

1.8

1.5

1.0

7.9

4.5

3.5

2.9

1

3

3.3 ±0.3

5.0 ±0.5

CL = 50pF,

RL = 500 ohms

1.5

1.0

3.3

2.4

4.5

3.2

1.5

1.0

5.0

3.5

1

3

1.8 ±0.15

2.5 ±0.2

3.3 ±0.3

5.0 ±0.5

CL = 50pF,

RL = 500 ohms

4.0

2.0

1.5

1.1

3.0

1.5

1.1

0.9

0

0

0

0

tH

Hold Time, CLK to DIN

1.8 ±0.15

2.5 ±0.2

3.3 ±0.3

5.0 ±0.5

CL = 50pF,

RL = 500 ohms

0.4

0.5

0.5

0.5

tW

Pulse Width, CLK

1.8 ±0.15

2.5 ±0.2

3.3 ±0.3

5.0 ±0.5

CL = 50pF,

RL = 500 ohms

2.5

2.5

2.5

2.5

Typ.

M ax.

M in.

M ax.

100

125

150

150

Units

MHz

ns

1

3

1

4

0.4

0.5

0.5

0.5

1

4

2.5

2.5

2.5

2.5

1

4

Capacitance(3)

Symbol

Parame te r

Typ.

M ax.

Units

Conditions

CIN

Input Capacitance

3

VCC = Open, VIN = 0V or VCC

COUT

Output Capacitance

4

VCC = 3.3V, VIN = 0V or VCC

Power Dissipation Capacitance(4)

8

10

12

14

CPD

pF

VCC

VCC

VCC

VCC

=

=

=

=

1.8V

2.5V

3.3V

5.0V

Notes:

3. TA = +25°C, f= 1 MHz

4. CPD is defined as the value of the internal equivalent capacitance which is derived from dynamic operating current consumption

(ICCD) at no output loading and operating at 50% duty cycle (see Figure 2). CPD is related to ICCD dynamic operating current by

the expression: ICCD = (CPD)(VCC)(fIN) + (ICC static).

3

PS8569A

01/31/02

�PI74STX1G79

SOTiny Gate STX Single Positive

Edge-Triggered D-Type Flip-Flop

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

AC Loading and Waveforms

VCC

VCC

A

CLK

QOUT

DIN

CL

CLK

RL

QOUT

DIN

CL includes load and stray capacitance

Input PRR = 1.0 MHz; tW = 500ns

Input = AC Waveform; tr = tf = 1.8ns;

PRR = 10 MHz; Duty Cycle = 50%

Figure 1. AC Test Circuit

Figure 2. ICCD Test Circuit

tr = 3ns

90%

CLK

tf = 3ns

VCC

90%

50%

50%

10%

10%

GND

tW

VCC

90%

90%

DIN

10%

10%

tPLH

GND

VOH

QOUT

50%

50%

VOL

tPHL

Figure 3. AC Waveforms

tr

tf = tr

很抱歉,暂时无法提供与“PI74STX1G79CX”相匹配的价格&库存,您可以联系我们找货

免费人工找货