User's Guide

SLOU332B – January 2012 – Revised March 2015

AFE5803EVM (Revision E ) Evaluation Module

This document assists users in evaluating the AFE5803 highly integrated analog front-end devices

through the use of the AFE5803EVM Evaluation Module. Included are setup instructions, printed-circuit

board art, bill of materials, and schematics.

Contents

Overview ...................................................................................................................... 2

Default Configuration ........................................................................................................ 2

Software Installation and Operation ....................................................................................... 3

Test Setup .................................................................................................................... 4

Power Up AFE5803 ......................................................................................................... 5

Launch AFE5803 GUI ....................................................................................................... 6

Launch TSW1400 GUI ...................................................................................................... 7

Test AFE5803 ................................................................................................................ 8

8.1

Step 1: Time Domain ............................................................................................... 8

8.2

Step 2: Single Tone FFT ......................................................................................... 11

9

External ADC Sampling Clock ............................................................................................ 12

10

External Vcntl ............................................................................................................... 14

11

Board Configuration ........................................................................................................ 15

11.1 Input/Output, Power Supply, and USB ......................................................................... 15

11.2 ADC Clock.......................................................................................................... 16

11.3 Vcntl Control Input ................................................................................................ 17

11.4 LEDs ................................................................................................................ 18

11.5 Miscellaneous Test Points ....................................................................................... 19

12

EVM Printed-Circuit Board Layouts and Schematics .................................................................. 20

12.1 Schematics ......................................................................................................... 26

13

Bill of Materials ............................................................................................................. 35

Appendix A

High Speed Data Converter Pro (HSDCPro) Installation ................................................... 39

1

2

3

4

5

6

7

8

List of Figures

1

AFE5803EVM Basic Configuration ........................................................................................ 3

2

HW Setup With Connection Between TSW1400EVM and AFE5803 ................................................. 4

3

Default Conditions Screen .................................................................................................. 6

4

User Interface: Single FFT Format ....................................................................................... 11

5

External ADC Sampling Clock Configuration ........................................................................... 12

6

External Vcntl Configuration .............................................................................................. 14

7

I/O, PWR, and USB Connector ........................................................................................... 15

8

AFE5803EVM Jumper Locations......................................................................................... 16

9

Vcntl .......................................................................................................................... 17

10

AFE5803EVM LED Location .............................................................................................. 18

11

AFE5803EVM Test Point Locations ..................................................................................... 19

12

Top Layer - Signal.......................................................................................................... 20

13

Second Layer - Ground.................................................................................................... 21

14

Third Layer - Power ........................................................................................................ 22

15

Fourth Layer - Signal

......................................................................................................

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

AFE5803EVM (Revision E ) Evaluation Module

Copyright © 2012–2015, Texas Instruments Incorporated

23

1

�Overview

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

www.ti.com

.......................................................................................................

Bottom Layer - Signal ......................................................................................................

Schematic 1 of 9 ...........................................................................................................

Schematic 2 of 9 ...........................................................................................................

Schematic 3 of 9 ...........................................................................................................

Schematic 4 of 9 (Not applicable to AFE5803) ........................................................................

Schematic 5 of 9 ...........................................................................................................

Schematic 6 of 9(Not applicable to AFE5803) .........................................................................

Schematic 7 of 9 ...........................................................................................................

Schematic 8 of 9(Not applicable to AFE5803) .........................................................................

Schematic 9 of 9 ...........................................................................................................

HSDCPro Install (Begin)...................................................................................................

HSDCPro Install (Install Directory) .......................................................................................

HSDCPro Install (TI License Agreement) ...............................................................................

HSDCPro Install (NI License Agreement) ...............................................................................

HSDCPro Install (Start Installation) ......................................................................................

HSDCPro Install (Installation Progress) .................................................................................

HSDCPro Install (Installation Complete) ................................................................................

HSDCPro Install (h) ........................................................................................................

HSDCPro Install ............................................................................................................

Fifth Layer - Ground

24

25

26

27

28

29

30

31

32

33

34

39

40

41

42

43

44

45

46

46

List of Tables

1

1

Input/Output, Power, and USB ........................................................................................... 15

2

PGATestMode, ADC Clock

3

Vcntl .......................................................................................................................... 17

4

LED Indicators .............................................................................................................. 18

..............................................................................................

16

5

Test Points .................................................................................................................. 19

6

Bill of Materials

.............................................................................................................

35

Overview

This document is intended to guide users step-by-step through the AFE5803EVM Evaluation Module

(EVM) setup and test . The EVM is shipped with a default configuration from the manufacturer. With this

configuration, the onboard CMOS clock is used for a analog-to-digital converter sampling clock. No

external clock generator is required. Users need to provide the input signal for measurement from a signal

generator.

Detail explanation regarding the jumpers, connectors, and test points appear in Section 11. The graphical

user interface (GUI) can be downloaded from the TI Web site.

2

Default Configuration

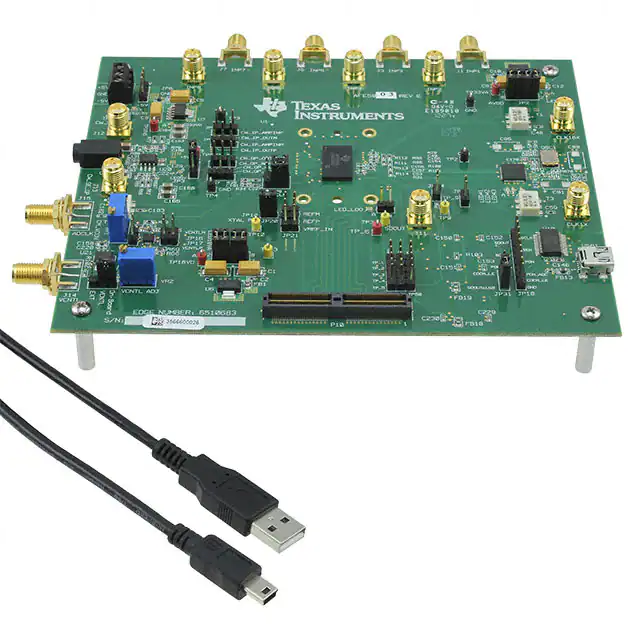

Figure 1 shows the default configuration of the EVM from the factory. The accompanying list identifies the

basic components on the EVM board.

2

AFE5803EVM (Revision E ) Evaluation Module

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

�Software Installation and Operation

www.ti.com

Figure 1. AFE5803EVM Basic Configuration

1.

2.

3.

4.

5.

6.

3

P1 – Power supplies connector.

JP1, JP2, and JP3 are set to enable 3.3-V, 1.8-V, and 5-V power supplies to device.

JP9: enables onboard CMOS clock.

JP10: Power supply for onboard CMOS clock oscillator.

JP15: Enables onboard VCNT.

JP31 always set as Figure 1.

Software Installation and Operation

The AFE5803EVM GUI (SLOC260) can be downloaded from the TI Web site. Follow the directions in

ReadMeFirst.pdf file to install GUI and device driver

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

AFE5803EVM (Revision E ) Evaluation Module

Copyright © 2012–2015, Texas Instruments Incorporated

3

�Test Setup

4

www.ti.com

Test Setup

Two EVMs are required to evaluate the AFE5803 device. The following illustration shows the exact setup

of these two boards and external connectors. For the default configuration as shown in Figure 1, it is

unnecessary to have an external sampling clock and external Vcntl supply. The onboard CMOS clock and

onboard Vcntl are used.

Figure 2. HW Setup With Connection Between TSW1400EVM and AFE5803

4

AFE5803EVM (Revision E ) Evaluation Module

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

�Power Up AFE5803

www.ti.com

5

Power Up AFE5803

Power up the AFE5803EVM by applying +5 V and –5 V to the P1 connector. After power up is complete,

four green LEDS and two red LEDS are turned on as shown in the following illustration.

LED 1.8V

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

AFE5803EVM (Revision E ) Evaluation Module

Copyright © 2012–2015, Texas Instruments Incorporated

5

�Launch AFE5803 GUI

6

www.ti.com

Launch AFE5803 GUI

Launch the AFE5803 graphic user interface (GUI), select the ADC page to observe the default condition.

Figure 3 shows the default conditions on the ADC page.

Figure 3. Default Conditions Screen

6

AFE5803EVM (Revision E ) Evaluation Module

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

�Launch TSW1400 GUI

www.ti.com

7

Launch TSW1400 GUI

Launch the TSW1400 GUI. For information on how to download this GUI see . The Message window

displays the following message to indicate that the setup of the TSW1400EVM and AFE5803EVM is

working properly. If a different message or an error message appears, contact TI FAE.

Select AFE5803, 14 bits, MSB first from the GUI.

ADC Sampling Rate is fixed at 40 MHz; this is the onboard CMOS clock frequency.

ADC Input Frequency – enter 2M, and the GUI calculates the real coherent frequency to 2.00439453M.

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

AFE5803EVM (Revision E ) Evaluation Module

Copyright © 2012–2015, Texas Instruments Incorporated

7

�Test AFE5803

www.ti.com

8

Test AFE5803

8.1

Step 1: Time Domain

•

Select the Time Domain page from the TSW1400 GUI.

Display Time Domain

Display Time/Frequency Domain

Make sure to check

8

AFE5803EVM (Revision E ) Evaluation Module

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

�Test AFE5803

www.ti.com

•

From the AFE5803 GUI, go to the ADC page, and then select Ramp.

•

Press the Capture button on the TSW1400 GUI. This displays a ramping waveform on the TSW1400

GUI display area as shown in the following illustration.

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

AFE5803EVM (Revision E ) Evaluation Module

Copyright © 2012–2015, Texas Instruments Incorporated

9

�Test AFE5803

•

•

•

10

www.ti.com

Repeat for Channel 2 and Channel 8.

If each channel has the output as shown in the following illustration, proceed with the next

step; otherwise, contact the TI FAE to troubleshoot the problem.

On the AFE5803 GUI, change Test Pattern from Ramp to None for the next step.

AFE5803EVM (Revision E ) Evaluation Module

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

�Test AFE5803

www.ti.com

8.2

Step 2: Single Tone FFT

•

•

•

•

•

•

•

Select the Single Tone FFT page at the TSW1400 GUI.

Connect Channel 1 of the AFE5803EVM to a signal generator through an LP filter. If an LP filter is not

present, the result will not be good.

Set the amplitude of the signal generator to -25dBm.

Set the frequency of the signal generator to 2.00439453M to match the GUI.

Change the window option to Hanning. This is because the input signal and the onboard CMOS clock

are noncoherent.

Press the Capture button to get the test result.

Repeat for Channel 2 through Channel 8.

Hanning

Figure 4. User Interface: Single FFT Format

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

AFE5803EVM (Revision E ) Evaluation Module

Copyright © 2012–2015, Texas Instruments Incorporated

11

�External ADC Sampling Clock

9

www.ti.com

External ADC Sampling Clock

To

1.

2.

3.

use the external clock generator to test the AFE5803, perform the following steps.

Reconfigure JP9 as shown in the following illustration. The rest of the jumpers remain the same.

Connect the external generator as shown in Figure 5.

Set the generator output to 40 MHz, 13 dBm.

Figure 5. External ADC Sampling Clock Configuration

12

AFE5803EVM (Revision E ) Evaluation Module

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

�External ADC Sampling Clock

www.ti.com

4. If the generators for the ADC clock and input signal are synchronous, then choose Rectangular as the

Windowing option; otherwise, use Hanning or Hamming.

5. The test procedure is the same for the CMOS ADC clock.

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

AFE5803EVM (Revision E ) Evaluation Module

Copyright © 2012–2015, Texas Instruments Incorporated

13

�External Vcntl

10

www.ti.com

External Vcntl

•

•

JP15 needs to be reconfigured to short the leftmost two pins.

A power supply is required to be connected as shown in Figure 6.

Figure 6. External Vcntl Configuration

14

AFE5803EVM (Revision E ) Evaluation Module

SLOU332B – January 2012 – Revised March 2015

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

�Board Configuration

www.ti.com

11

Board Configuration

11.1 Input/Output, Power Supply, and USB

Figure 7. I/O, PWR, and USB Connector

Table 1