bq24083

www.ti.com .............................................................................................................................................................. SLUS848A – MAY 2008 – REVISED APRIL 2009

1A, LI-ION, LI-POL BATTERY CHARGER WITH ADJUSTABLE BATTERY VOLTAGE

FEATURES

1

• Pin Select Battery Voltage (4.06V/4.2V)

• Integrated Power FET and Current Sensor for

Up to 1A Charge Applications From AC

Adapter

• Precharge Conditioning With Safety Timer

• Charge and Power-Good Status Output

• Automatic Sleep Mode for Low Power

Consumption

• Integrated Charge-Current Monitor

• Fixed 7-Hour Fast Charge Safety Timer

• Ideal for Low-Dropout Charger Designs for

Single-Cell Li-Ion or Li-Pol Packs in

Space-Limited Portable Applications

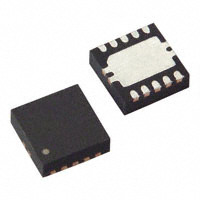

• Small 3-mm × 3-mm SON Package

2

APPLICATIONS

•

•

•

•

DESCRIPTION

The bq24083 is highly integrated and flexible Li-Ion

linear charge device targeted at space-limited charger

applications. It offers an integrated power FET and

current sensor, high-accuracy current and voltage

regulation, charge status, and charge termination, in

a single monolithic device. An external resistor sets

the magnitude of the charge current. The bq24083

has an option of two output battery charge voltages:

4.06 V and 4.2 V.

The device charges the battery in three phases:

conditioning, constant current, and constant voltage.

Charge is terminated based on minimum current. An

internal charge timer provides a backup safety for

charge termination. The device automatically restarts

the charge if the battery voltage falls below an

internal threshold. The device automatically enters

sleep mode when the ac adapter is removed.

PDAs, MP3 Players

Digital Cameras

Internet Appliances

Smartphones

AC

Adapter

VDC

GND

C1

0.1 mF

PACK+

bq24080

1

IN

C2

0.1 µF

OUT 10

PACK–

2

NC

CE

9

3

STAT1

PG

8

4

STAT2 VBSEL 7

5

VSS

Battery Pack

+

System

System

Interface

RSET

ISET

6

1.13 kW

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2008–2009, Texas Instruments Incorporated

�bq24083

SLUS848A – MAY 2008 – REVISED APRIL 2009 .............................................................................................................................................................. www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

ORDERING INFORMATION

TJ

CHARGE

REGULATION

VOLTAGE (V)

FUNCTIONS

FAST-CHARGE

TIMER (HOURS)

–40°C to 125°C

4.2/ 4.06

CE , PG, and VBSEL

7

(1)

(2)

PART

NUMBER (1) (2)

MARKINGS

bq24083DRCT

CFZ

bq24083DRCR

The DRC package is available taped and reeled only in quantities of 3,000 devices per reel.

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

Web site at www.ti.com.

DISSIPATION RATINGS

(1)

PACKAGE

RθJA

RθJC

TA < 40°C

POWER RATING

DERATING FACTOR

ABOVE TA = 40°C

DRC (1)

46.87 °C/W

4.95 °C/W

1.5 W

0.021 W/°C

This data is based on using the JEDEC High-K board and the exposed die pad is connected to a copper pad on the board. This is

connected to the ground plane by a 2- × 3-via matrix.

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted (1)

VALUE

VI

Input voltage (2)

IN, CE, ISET, OUT, PG, STAT1, STAT2, VBSEL

Output sink/source current

Output current

V

STAT1, STAT2, PG

15

mA

OUT

1.5

TA

Operating free-air temperature range

TJ

Junction temperature range

Tstg

Storage temperature

(1)

(2)

UNIT

–0.3 to 7

A

°C

–40 to 125

°C

–65 to 150

°C

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltages are with respect to VSS.

RECOMMENDED OPERATING CONDITIONS

VCC

Supply voltage

TJ

Operating junction temperature range

2

Submit Documentation Feedback

MIN

MAX

4.5

6.5

UNIT

V

0

125

°C

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

�bq24083

www.ti.com .............................................................................................................................................................. SLUS848A – MAY 2008 – REVISED APRIL 2009

ELECTRICAL CHARACTERISTICS

over 0°C ≤ TJ ≤ 125°C and recommended supply voltage (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

1.2

2

2

5

UNIT

INPUT CURRENT

ICC(VCC)

VCC current

VCC > VCC(min)

ICC(SLP)

Sleep current

Sum of currents into OUT pin,

VCC < V(SLP)

ICC(STBY)

Standby current

CE = High, 0°C ≤ TJ ≤ 85°C

IIB(OUT)

Input current on OUT pin

Charge DONE, VCC > VCC(MIN)

150

1

mA

µA

5

VOLTAGE REGULATION VO(REG) + V(DO−MAX) ≤ VCC, I(TERM) < IO(OUT) ≤ 1 A

VO(REG)

Output voltage

4.06

VBSEL = LO

4.2

TA = 25°C

Voltage regulation accuracy

V(DO)

VBSEL = HI

−0.35%

0.35%

−1%

1%

VO(OUT) = VO(REG), IO(OUT) = 1 A

VO(REG) + V(DO)) ≤ VCC

Dropout voltage (V(IN) − V(OUT))

V

350

500

mV

1000

mA

V

CURRENT REGULATION

IO(OUT)

Output current range (1)

VI(OUT) > V(LOWV),

VI(IN) − VI(OUT) > V(DO), VCC ≥ 4.5 V

V(SET)

Output current set voltage

Voltage on ISET pin, VCC ≥ 4.5 V,

VI ≥ 4.5 V, VI(OUT) > V(LOWV),

VI − VI(OUT) > V(DO)

K(SET)

Output current set factor

50

2.463

2.5

2.538

50 mA ≤ IO(OUT) ≤ 1 A

307

322

337

10 mA ≤ IO(OUT) < 50 mA

296

320

346

1 mA ≤ IO(OUT) < 10 mA

246

320

416

PRECHARGE AND SHORT-CIRCUIT CURRENT REGULATION

V(LOWV)

IO(PRECHG)

V(PRECHG)

Precharge to fast-charge transition

threshold

Voltage on OUT pin

2.8

3

3.2

V

Deglitch time for fast-charge to precharge

transition

VCC(MIN) ≥ 4.5 V, tFALL = 100 ns,

10-mV overdrive,

VI(OUT) decreasing below threshold

250

375

500

ms

Precharge range (2)

0 V < VI(OUT) < V(LOWV), t < t(PRECHG)

100

mA

Precharge set voltage

Voltage on ISET pin, VO(REG) = 4.2 V,

0 V < VI(OUT) > V(LOWV), t < t(PRECHG)

270

mV

100

mA

5

240

255

TERMINATION DETECTION

I(TERM)

Charge termination detection range (3)

VI(OUT) > V(RCH), t < t(TRMDET)

V(TERM)

Charge termination detection set voltage

Voltage on ISET pin, VO(REG) = 4.2 V,

VI(OUT) > V(RCH), t < t(TRMDET)

235

250

265

mV

tTRMDET

Deglitch time for termination detection

VCC(MIN) ≥ 4.5 V, tFALL = 100 ns

charging current decreasing below

10-mV overdrive

250

375

500

ms

(1)

(2)

(3)

5

See Equation 2 in the Function Description section.

See Equation 1 in the Function Description section.

See Equation 4 in the Function Description section.

Submit Documentation Feedback

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

3

�bq24083

SLUS848A – MAY 2008 – REVISED APRIL 2009 .............................................................................................................................................................. www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

over 0°C ≤ TJ ≤ 125°C and recommended supply voltage (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VO(REG)

– 0.115

VO(REG)

− 0.10

VO(REG)

− 0.085

250

375

500

ms

0.25

V

BATTERY RECHARGE THRESHOLD

V(RCH)

Recharge threshold

t(DEGL)

Deglitch time for recharge detect

VCC(MIN) ≥ 4.5 V, tFALL = 100 ns

decreasing below or increasing above

threshold, 10-mV overdrive

V

STAT1, STAT2, and PG OUTPUTS

VOL

Low-level output saturation voltage

IO = 5 mA

VBSEL, CE and TE INPUTS

VIL

Low-level input voltage

0

VIH

High-level input voltage

1.4

IIL

CE and TE low-level input current

–1

IIH

CE and TE high-level input current

IIL

VBSEL low-level input current

VBSEL = 0 (LOW)

IIH

VBSEL high-level input current

VBSEL = VCC (HI)

0.4

1

–20

40

V

µA

µA

TIMERS

t(PRECHG)

Precharge time

t(CHG)

Charge time

I(FAULT)

Timer fault recovery current

1,584

1,800

2,016

22,176

25,200

28,224

s

s

µA

200

SLEEP COMPARATOR

V(SLP)

Sleep-mode entry threshold voltage

V(SLPEXIT)

Sleep-mode exit threshold voltage

2.3 V ≤ VI(OUT) ≤ VO(REG)

Sleep-mode entry deglitch time

V(IN) decreasing below threshold,

tFALL = 100 ns, 10-mV overdrive

VCC ≤ VI(OUT)

+ 80 mV

VCC ≥ VI(OUT)

+ 190

250

375

500

V

ms

THERMAL SHUTDOWN THRESHOLDS

T(SHTDWN)

Thermal trip threshold

Thermal hysteresis

165

TJ increasing

°C

15

UNDERVOLTAGE LOCKOUT

UVLO

Undervoltage lockout

Decreasing VCC

Hysteresis

4

2.4

2.5

27

Submit Documentation Feedback

2.6

V

mV

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

�bq24083

www.ti.com .............................................................................................................................................................. SLUS848A – MAY 2008 – REVISED APRIL 2009

PIN CONFIGURATION

DRC PACKAGE

(TOP VIEW)

VSS

5

STAT2 STAT1

3

4

NC

IN

2

1

9

10

CE

OUT

bq24083

6

7

8

ISET VBSEL PG

TERMINAL FUNCTIONS

TERMINAL

NAME

I/O

DESCRIPTION

NO.

CE

9

I

Charge enable input (active-low)

N.C.

2

–

No Connection. Leave this pin unconnected. Used for internal test purposes.

IN

1

I

Adapter dc voltage. Connect minimum 0.1-µF capacitor to VSS.

ISET

6

I

Charge current. External resistor to VSS sets precharge and fast-charge current, and also the termination

current value. Can be used to monitor the charge current.

OUT

10

O

Charge current output. Connect minimum 0.1-µF capacitor to VSS.

PG

8

O

Power-good status output (open-drain)

STAT1

3

O

STAT2

4

O

VBSEL

7

I

Voltage output selection. (HI = 4.06 V, LO = 4.2 V)

VSS

5

–

Ground

–

There is an internal electrical connection between the exposed thermal pad and the VSS pin of the device.

The exposed thermal pad must be connected to the same potential as the VSS pin on the printed-circuit

board. Do not use the thermal pad as the primary ground input for the device. The VSS pin must be

connected to ground at all times.

Thermal pad

–

Charge status outputs (open-drain)

Submit Documentation Feedback

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

5

�bq24083

SLUS848A – MAY 2008 – REVISED APRIL 2009 .............................................................................................................................................................. www.ti.com

FUNCTIONAL BLOCK DIAGRAM

Note: (1)

IN

OUT

ISET

V(PRECHG)

V(SET)

VO(REG)

V(RCH)

V(LOWV)

Note: (1)

Note: (1)

Note: (1)

V(TERM)

VBSEL

4.06 V

VIN

4.2 V

VI(OUT) + V(SLP)

Note: (1)

UVLO

Charge

Control,

Timers,

and

Status

STAT1

CE

STAT2

PG

VSS

(1)

6

Signal deglitched

Submit Documentation Feedback

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

�bq24083

www.ti.com .............................................................................................................................................................. SLUS848A – MAY 2008 – REVISED APRIL 2009

TYPICAL CHARACTERISTICS

DROPOUT VOLTAGE

vs

JUNCTION TEMPERATURE

450

IO(OUT) = 1000 mA

400

Dropout Voltage - mV

350

IO(OUT) = 750 mA

300

250

IO(OUT) = 500 mA

200

150

IO(OUT) = 250 mA

100

50

0

0

50

100

TJ - Junction Temperature - oC

Figure 1.

150

Figure 2. VIN Hot-Plug Power-Up Sequence

Submit Documentation Feedback

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

7

�bq24083

SLUS848A – MAY 2008 – REVISED APRIL 2009 .............................................................................................................................................................. www.ti.com

TYPICAL CHARACTERISTICS (continued)

Figure 3. Charge Enable Power-Up Sequence (CE = High-to-Low)

Figure 4. Battery Hot-Plug During Charging Phase

8

Submit Documentation Feedback

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

�bq24083

www.ti.com .............................................................................................................................................................. SLUS848A – MAY 2008 – REVISED APRIL 2009

TYPICAL CHARACTERISTICS (continued)

(1)

No battery – In termination deglitch prior to STAT1 going high. VOUT (VBAT) cycling between charge and done prior to screen capture.

(2)

Stat1 goes high – In done state

(3)

2-V battery is inserted during the charge done state.

(4)

Charging is initiated – STAT1 goes low and charge current is applied.

(5)

Battery is removed – VOUT goes into regulation, IOUT goes to zero, and termination deglitch timer starts running (same as state 1).

(6)

Deglitch timer expires – charge done is declared.

Figure 5. Battery Hot-Plug and Removal Power Sequence

Submit Documentation Feedback

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

9

�bq24083

SLUS848A – MAY 2008 – REVISED APRIL 2009 .............................................................................................................................................................. www.ti.com

FUNCTIONAL DESCRIPTION

The device supports a precision Li-Ion, Li-Pol charging system suitable for single cells. Figure 6 shows a typical

charge profile, and Figure 7 shows an operational flow chart.

Preconditioning

Phase

Current Regulation Phase

Voltage Regulation and Charge Termination Phase

Regulation

Voltage

Regulation

Current

Minimum

Charge

Voltage

PreConditioning

and Term

Detect

Charge

Voltage

Charge

Complete

Charge

Current

Safety Timer

M0066-01

Figure 6. Typical Charging Profile

10

Submit Documentation Feedback

Copyright © 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :bq24083

�bq24083

www.ti.com .............................................................................................................................................................. SLUS848A – MAY 2008 – REVISED APRIL 2009

POR

SLEEP MODE

VCC > VI(OUT)

checked at all

times?

No

Indicate SLEEP

MODE

Yes

VI(OUT)