DLPC910

DLPC910

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER

2020

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

www.ti.com

DLPC910 Digital DMD Controller

1 Features

•

•

•

•

•

•

•

•

•

Operates the following DLP ® DMD Chips

– DLP9000X DMD

– DLP9000XUV DMD

– DLP6500 DMD

User-selectable input clock rate

– 400 MHz or 480 MHz with the DLP9000X and

DLP9000XUV

– 400 MHz with the DLP6500

Continuous streaming input data

– Up to 61 gigabits per second with the

DLP9000X and DLP9000XUV

– Up to 24 gigabits per second with the DLP6500

Enables high-speed pattern rates

– Up to 15 kHz binary patterns per second with

the DLP9000X and DLP9000XUV

– Up to 11.5 kHz binary patterns per second with

the DLP6500

8-Bit gray scale pattern rates

– Up to 1.8 kHz with the DLP9000X and

DLP9000XUV with modulated illumination

– Up to 1.4 kHz with the DLP6500 with

modulated illumination

64-Bit 2x LVDS data bus interface

Random DMD row addressing and Load4 loading

Compatible with a variety of user-defined

application processors or FPGAs

I2C interface for control and status queries

3 Description

The DLPC910 is a digital controller for three DMDs:

the DLP9000X, DLP9000XUV, and DLP6500. The

DLPC910 provides customers a high-speed data and

control interface for the DMD to enable binary pattern

rates up to 15 kHz with the DLP9000X/DLP9000XUV

DMDs, and 11.5 kHz with the DLP6500 DMD. These

fast pattern rates set DLP technology apart from other

spatial light modulators and offer customers a

strategic advantage for equipment needing fast,

accurate, and programmable light steering capability.

The DLPC910 provides the required mirror clocking

pulses and timing information to the DMD. The unique

capability and value offered by the DLPC910 device

makes it well suited to support a wide variety of

lithography, industrial, and advanced display

applications.

In DLP-based electronics solutions, image data is

100% digital from the DLPC910 input port to the

projected image. The image stays in digital form and

is never converted into an analog signal. The

DLPC910 processes the digital input image and

converts the data into a format needed by the DMD

for proper display. The DMD then steers the light to

the location determined by the pixel data loaded into

the DMD.

For complete electrical and mechanical specifications

of the DLPC910, see the Virtex®-5 product

specification at www.xilinx.com.

Device Information (1)

2 Applications

•

•

•

Lithography

– Direct imaging

– Flat panel display

– Printed circuit board manufacturing

Industrial

– 3D printing

– 3D scanners for machine vision

– Quality control

Displays

– 3D imaging

– Augmented reality and information overlay

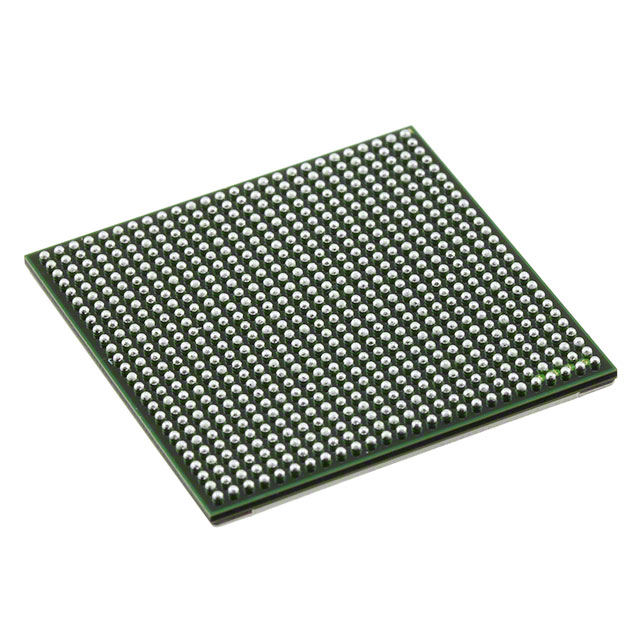

PART NUMBER

DLPC910

(1)

PACKAGE

FCBGA (676)

BODY SIZE (NOM)

27.00 mm × 27.00 mm

For all available packages, see the orderable addendum at

the end of the data sheet.

Typical Application Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

Submit Document Feedback

Copyright

© 2020 Texas

Instruments

Incorporated

intellectual

property

matters

and other important disclaimers. PRODUCTION DATA.

1

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Pin Configuration and Functions...................................4

Pin Functions.................................................................... 5

6 Specifications................................................................ 15

6.1 Absolute Maximum Ratings...................................... 15

6.2 ESD Ratings............................................................. 15

6.3 Recommended Operating Conditions.......................15

6.4 Thermal Information..................................................16

6.5 Electrical Characteristics...........................................16

6.6 Timing Requirements................................................ 16

7 Detailed Description......................................................18

7.1 Overview................................................................... 18

7.2 Functional Block Diagram......................................... 18

7.3 Feature Description...................................................18

7.4 Device Functional Modes..........................................26

7.5 Register Map.............................................................40

8 Application and Implementation.................................. 47

8.1 Application Information............................................. 47

8.2 Typical Application.................................................... 47

9 Power Supply Recommendations................................52

9.1 Power Supply Distribution and Requirements.......... 52

9.2 Power Down Requirements...................................... 52

10 Layout...........................................................................53

10.1 Layout Guidelines................................................... 53

10.2 Layout Example...................................................... 57

11 Device and Documentation Support..........................59

11.1 Device Support........................................................59

11.2 Documentation Support.......................................... 59

11.3 Support Resources................................................. 59

11.4 Trademarks............................................................. 59

11.5 Electrostatic Discharge Caution.............................. 60

11.6 Glossary.................................................................. 60

12 Mechanical, Packaging, and Orderable

Information.................................................................... 60

4 Revision History

Changes from Revision C (March 2020) to Revision D (September 2020)

Page

• Updated Description section for DDC_DCLK_(A,B,C,D)_DP(N,P), DDC_DIN_(A,B,C,D)(1-15)_DP(N,P), and

DVALID_(A,B,C,D)_DP(N,P) from "100-Ω internal LVDS termination." to "100-Ω external LVDS termination

required...............................................................................................................................................................5

• Updated I/O Type section for LOAD4_ENZ from LVCMOS33_I to LVCMOS25_I.............................................. 5

• Updated I/O Type section for DMD_IRQ from LVCMOS33_O to LVCMOS25_O...............................................5

• Corrected HBM and CDM values. ................................................................................................................... 15

• Corrected "...during which time RST_ACTIVE is asserted." to "...during which time RST_ACTIVE is NOT

asserted."..........................................................................................................................................................21

• Updated section name from "DMD Power Down" to "DMD Mirror Float". Removed outdated information about

power down...................................................................................................................................................... 21

• Removed "After PWR_FLOAT is asserted, a Mirror Clocking Pulse is issued, or a mirror Float operation is

requested" ........................................................................................................................................................23

• Updated I2C terminology to "primary" and "secondary" throughout section. ................................................... 24

• Updated performance plot for DLP6500 DMD (Figure 8-4) ............................................................................. 50

• Updated performance plot for DLP9000X/DLP9000XUV DMD (Figure 8-3).................................................... 50

Changes from Revision B (November 2016) to Revision C (March 2020)

Page

• Changed title from DLPC910 Digital Controller to DLPC910 Digital DMD Controller ........................................1

• Added new DLP9000XUV DMD as DLPC910 supported DMD (multiple places).............................................. 1

• Updated "DDC_IIC_x" signal names to "DDC_I2C_x" in multiple locations....................................................... 5

• Added missing DLPC_DOUTBUSY pin to complete the listing of all 676 pins of DLPC910.............................. 5

• Added missing unconnected pins to complete the listing of all 676 pins of DLPC910....................................... 5

• Corrected signal name RESETZ to RESET_RSTZ ......................................................................................... 18

• Deleted package code FLS from DMD callout for readability .......................................................................... 18

• Added section describing DDC_Version output pins ....................................................................................... 23

• Corrected I2C version from 1.0-1995 to 1.0-1992. ...........................................................................................24

• Combined Figure 8 and Figure 9 into new Figure 7-6 to incorporate Application Note/Tech Advisory dlpa092

(DLPC910 / DLPR910A - Continuous Row Command Operation). .................................................................34

2

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�www.ti.com

•

•

•

•

•

•

•

DLPC910

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

Added DLP9000XUV to DMD Characteristics Table ....................................................................................... 35

Changed "Connected DMD ID" to "Connected DMD TYPE" to match nomenclature of DMD_TYPE_[3:0] input

pins .................................................................................................................................................................. 40

Added explanation that DDC_VERSION_(2:0) output values are mirrored in DESTOP_VERSION register... 43

Corrected signal name RESETZ to RESET_RSTZ in DLP9000X block diagram ........................................... 47

Corrected signal name RESETZ to RESET_RSTZ in DLP6500 block diagram ..............................................47

Added DLP9000XUV to Figure 9-1 - changed previous sentence to clarify one DMD per DLPC910/DLPR910.

..........................................................................................................................................................................52

Added DLP9000XUV link to Related Documentation section ..........................................................................59

Changes from Revision A (October 2015) to Revision B (November 2016)

Page

• Simplified datasheet title.....................................................................................................................................1

• Added family of supported DMDs in Section 1 .................................................................................................. 1

• Updated supply current values in Section 6.5. ................................................................................................ 16

• Indicated how SPEED_SEL should be set when DLP6500 is used in Section 7.3.2 ...................................... 18

• Added reference to the Section 9.2 in Section 7.3.6.4 .................................................................................... 21

• Replaced DMD part number and row count with variable VRes in Section 7.3.6.5.1 ......................................22

• Indicated how SPEED_SEL should be set when DLP6500 is used in Section 7.3.10.3 ................................. 25

• Added cross reference to Table 7-11 in Section 7.4 ........................................................................................ 26

• Added cross reference to Table 7-11 in Section 7.4.1 ..................................................................................... 26

• Added pixel mapping tables for both DMDs in Section 7.4.1 ...........................................................................26

• Added single row write example for the DLP6500 in Section 7.4.1.1 .............................................................. 34

• Added DLP6500 to Table 7-11 .........................................................................................................................35

• Added the number of row cycles required to clear the entire DMD for the DLP6500 in Section 7.4.3 ............ 37

• Added DLP6500 to Table 7-13 .........................................................................................................................37

• Added cross reference to Table 7-11 in Section 7.4.4 ..................................................................................... 37

• Added additional description for activating buses in Section 7.5.1.9 ...............................................................45

• Added DLP6500 DMD to application details to Section 8.2 .............................................................................47

• Added cross reference to Table 7-11 in Section 8.2.1.1 .................................................................................. 49

• Replaced references to part numbers with DMD in Section 8.2.1.2 ................................................................ 49

• Associated performance plot with appropriate DMD (Figure 8-3).....................................................................50

• Added performance plot for DLP6500 DMD (Figure 8-4)................................................................................. 50

• Added power down requirements and increased the minimum 300 µs to 500 µs for maintaining power levels

in Section 9.2 ................................................................................................................................................... 52

• Added Table 9-1, Figure 9-2, Figure 9-3 ..........................................................................................................52

Changes from Revision * (September 2015) to Revision A (October 2015)

Page

• Changed the device from: Product Preview to Production Data.........................................................................1

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

3

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

5 Pin Configuration and Functions

Figure 5-1. ZYR Package 676-Pin FCBGA Top View

4

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

I/O Type Descriptions

I/O TYPE

DESCRIPTION

PWR

Power

GND

Ground

LVDS_25_NI

LVDS 2.5-V negative input

LVDS_25_PI

LVDS 2.5-V positive input

LVDS_25_NO

LVDS 2.5-V negative output

LVDS_25_PO

LVDS 2.5-V positive output

LVCMOS25_I

LVCMOS 2.5-V input

LVCMOS25_O

LVCMOS 2.5-V output

LVCMOS25_B

LVCMOS 2.5-V bidirectional

LVCMOS33_I

LVCMOS 3.3-V input

LVCMOS33_O

LVCMOS 3.3-V output

LVCMOS33_B

LVCMOS 3.3-V bidirectional

LVDCI_33_O

Low-voltage digitally controlled impedance 3.3-V output

NC

No connection

Pin Functions

PIN

NAME

CTRL_RSTZ

NO.

F9

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

LVCMOS25_I

Lo = 0

-

DLPC910 Reset.

DESCRIPTION

AA10

LVCMOS33_I

Hi = 1

-

DLPC910 Secondary I2C Address Lo =

0x34, Hi = 0x36. Includes Internal pull-up.

DDC_I2C_SCL

Y8

LVCMOS33_B

-

-

DLPC910 Secondary I2C Clock.

Requires an external 1-kΩ pull-up

resistor.

DDC_I2C_SDA

AA8

LVCMOS33_B

-

DDC_I2C_SCL

DLPC910 Secondary I2C Data. Requires

an external 1-kΩ pull-up resistor.

DDC_I2C_ADDR_SEL

CLKIN_R

E10

LVCMOS25_I

-

Reference clock

50-MHz Reference Clock

RESET_ADDR0

AD18

LVDCI_33_O

Hi

-

Connect to DMD RESET_ADDR0

RESET_ADDR1

AC18

LVDCI_33_O

Hi

-

Connect to DMD RESET_ADDR1

RESET_ADDR2

AC17

LVDCI_33_O

Hi

-

Connect to DMD RESET_ADDR2

RESET_ADDR3

AC16

LVDCI_33_O

Hi

-

Connect to DMD RESET_ADDR3

RESET_MODE0

AC13

LVDCI_33_O

Hi

-

Connect to DMD RESET_MODE0

RESET_MODE1

AD13

LVDCI_33_O

Hi

-

Connect to DMD RESET_MODE1

RESET_SEL0

AD15

LVDCI_33_O

Hi

-

Connect to DMD RESET_SEL0

RESET_SEL1

AC14

LVDCI_33_O

Hi

-

Connect to DMD RESET_SEL1

RESET_STROBE

AD10

LVDCI_33_O

Hi

-

Connect to DMD RESET_STROBE

RESET_OEZ

AD14

LVDCI_33_O

Lo

-

Connect to DMD RESET_OEZ

RESET_IRQZ

AD8

LVCMOS33_I

Lo

-

Connect to DMD RESET_IRQZ

RESET_RSTZ

AB10

LVDCI_33_O

Lo

-

Connect to DMD PWRDNZ and RESETZ

inputs

SCPCLK

AC7

LVDCI_33_O

-

-

Connect to DMD SCP_CLK

SCPDI

AC8

LVCMOS33_I

-

SCPCLK

Connect to DMD SCP_DO

SCPDO

AC9

LVDCI_33_O

-

SCPCLK

Connect to DMD SCP_DI

DMD_SCPENZ

AB9

LVDCI_33_O

Lo

SCPCLK

Connect to DMD SCP_ENZ

DMD_TYPE_0

G11

LVCMOS25_O

Hi

-

Attached DMD Type bit 0

DMD_TYPE_1

G12

LVCMOS25_O

Hi

-

Attached DMD Type bit 1

DMD_TYPE_2

H11

LVCMOS25_O

Hi

-

Attached DMD Type bit 2

DMD_TYPE_3

H12

LVCMOS25_O

Hi

-

Attached DMD Type bit 3

BLKAD_0

E12

LVCMOS25_I

Hi

DDC_DCLK_[A,B,C,D]

Block Address bit 0

BLKAD_1

D13

LVCMOS25_I

Hi

DDC_DCLK_[A,B,C,D]

Block Address bit 1

BLKAD_2

E13

LVCMOS25_I

Hi

DDC_DCLK_[A,B,C,D]

Block Address bit 2

BLKAD_3

F13

LVCMOS25_I

Hi

DDC_DCLK_[A,B,C,D]

Block Address bit 3

BLKMD_0

H13

LVCMOS25_I

Hi

DDC_DCLK_[A,B,C,D]

Block Mode Bit 0

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

5

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

6

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

H14

LVCMOS25_I

Hi

DDC_DCLK_[A,B,C,D]

Block Mode Bit 1

D14

LVCMOS25_I

Hi

-

DMD Row Address bit 0

ROWAD_1

D15

LVCMOS25_I

Hi

-

DMD Row Address bit 1

ROWAD_2

E15

LVCMOS25_I

Hi

-

DMD Row Address bit 2

ROWAD_3

F14

LVCMOS25_I

Hi

-

DMD Row Address bit 3

ROWAD_4

G14

LVCMOS25_I

Hi

-

DMD Row Address bit 4

ROWAD_5

E16

LVCMOS25_I

Hi

-

DMD Row Address bit 5

ROWAD_6

F15

LVCMOS25_I

Hi

-

DMD Row Address bit 6

ROWAD_7

G15

LVCMOS25_I

Hi

-

DMD Row Address bit 7

ROWAD_8

E17

LVCMOS25_I

Hi

-

DMD Row Address bit 8

ROWAD_9

F17

LVCMOS25_I

Hi

-

DMD Row Address bit 9

ROWAD_10

G16

LVCMOS25_I

Hi

-

DMD Row Address bit 10

ROWMD_0

H17

LVCMOS25_I

Hi

-

DMD Row Mode bit 0

ROWMD_1

H16

LVCMOS25_I

Hi

-

DMD Row Mode bit 1

DDC_DCLK_A_DPN

B21

LVDS_25_NI

-

-

DDC_DCLK_A_DPP

C21

LVDS_25_PI

-

-

Input Bus A Clock. 100-Ω external LVDS

termination required.

DDC_DCLK_B_DPN

A7

LVDS_25_NI

-

-

DDC_DCLK_B_DPP

B7

LVDS_25_PI

-

-

DDC_DCLK_C_DPN

K20

LVDS_25_NI

-

-

DDC_DCLK_C_DPP

K21

LVDS_25_PI

-

-

DDC_DCLK_D_DPN

L5

LVDS_25_NI

-

-

DDC_DCLK_D_DPP

K5

LVDS_25_PI

-

-

DDC_DCLKOUT_A_DPN

N1

LVDS_25_NO

-

-

DDC_DCLKOUT_A_DPP

M1

LVDS_25_PO

-

-

DDC_DCLKOUT_B_DPN

Y5

LVDS_25_NO

-

-

DDC_DCLKOUT_B_DPP

Y6

LVDS_25_PO

-

-

DDC_DCLKOUT_C_DPN

AA22

LVDS_25_NO

-

-

DDC_DCLKOUT_C_DPP

AB22

LVDS_25_PO

-

-

DDC_DCLKOUT_D_DPN

M26

LVDS_25_NO

-

-

DDC_DCLKOUT_D_DPP

M25

LVDS_25_PO

-

-

DDC_DIN_A0_DPN

A15

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A0_DPP

A14

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A1_DPN

B14

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A1_DPP

C14

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A2_DPN

B16

LVDS_25_NI

-

DDC_DCLK_A

NAME

NO.

BLKMD_1

ROWAD_0

DESCRIPTION

Input Bus B Clock. 100-Ω external LVDS

termination required.

Input Bus C Clock. 100-Ω external LVDS

termination required.

Input Bus D Clock. 100-Ω external LVDS

termination required.

Output Bus A Clock to DMD.

Output Bus B Clock to DMD.

Output Bus C Clock to DMD.

Output Bus D Clock to DMD.

DDC_DIN_A2_DPP

B15

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A3_DPN

C16

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A3_DPP

D16

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A4_DPN

A17

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A4_DPP

B17

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A5_DPN

C17

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A5_DPP

D18

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A6_DPN

A19

LVDS_25_NI

-

DDC_DCLK_A

Input Bus A Data bit 0.

100-Ω external LVDS termination

required.

Input Bus A Data bit 1.

100-Ω external LVDS termination

required.

Input Bus A Data bit 2.

100-Ω external LVDS termination

required.

Input Bus A Data bit 3.

100-Ω external LVDS termination

required.

Input Bus A Data bit 4.

100-Ω external LVDS termination

required.

Input Bus A Data bit 5.

100-Ω external LVDS termination

required.

Input Bus A Data bit 6.

100-Ω external LVDS termination

required.

DDC_DIN_A6_DPP

A18

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A7_DPN

C18

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A7_DPP

B19

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A8_DPN

D19

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A8_DPP

C19

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A9_DPN

B20

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A9_DPP

A20

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A10_DPN

A22

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A10_DPP

B22

LVDS_25_PI

-

DDC_DCLK_A

Input Bus A Data bit 10.

100-Ω external LVDS termination

required.

DDC_DIN_A11_DPN

A24

LVDS_25_NI

-

DDC_DCLK_A

Input Bus A Data bit 11.

Submit Document Feedback

Input Bus A Data bit 7.

100-Ω external LVDS termination

required.

Input Bus A Data bit 8.

100-Ω external LVDS termination

required.

Input Bus A Data bit 9.

100-Ω external LVDS termination

required.

Copyright © 2020 Texas Instruments Incorporated

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

DESCRIPTION

A23

LVDS_25_PI

-

DDC_DCLK_A

100-Ω external LVDS termination

required.

DDC_DIN_A12_DPN

C23

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A12_DPP

B24

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A13_DPN

C24

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A13_DPP

D24

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A14_DPN

A25

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A14_DPP

B25

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_A15_DPN

C26

LVDS_25_NI

-

DDC_DCLK_A

DDC_DIN_A15_DPP

B26

LVDS_25_PI

-

DDC_DCLK_A

DDC_DIN_B0_DPN

A12

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B0_DPP

A13

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B1_DPN

B12

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B1_DPP

C13

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B2_DPN

D10

LVDS_25_NI

-

DDC_DCLK_B

NAME

NO.

DDC_DIN_A11_DPP

DDC_DIN_B2_DPP

D11

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B3_DPN

C12

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B3_DPP

C11

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B4_DPN

A10

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B4_DPP

B11

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B5_DPN

D9

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B5_DPP

C9

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B6_DPN

B10

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B6_DPP

B9

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B7_DPN

A8

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B7_DPP

A9

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B8_DPN

D6

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B8_DPP

D5

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B9_DPN

C7

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B9_DPP

C6

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B10_DPN

B6

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B10_DPP

B5

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B11_DPN

D4

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B11_DPP

D3

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B12_DPN

B4

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B12_DPP

C4

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B13_DPN

C3

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B13_DPP

C2

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B14_DPN

A3

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B14_DPP

A2

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_B15_DPN

B2

LVDS_25_NI

-

DDC_DCLK_B

DDC_DIN_B15_DPP

B1

LVDS_25_PI

-

DDC_DCLK_B

DDC_DIN_C0_DPN

E20

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C0_DPP

E21

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C1_DPN

F20

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C1_DPP

G20

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C2_DPN

H19

LVDS_25_NI

-

DDC_DCLK_C

Input Bus A Data bit 12.

100-Ω external LVDS termination

required.

Input Bus A Data bit 13.

100-Ω external LVDS termination

required.

Input Bus A Data bit 14.

100-Ω external LVDS termination

required.

Input Bus A Data bit 15.

100-Ω external LVDS termination

required.

Input Bus B Data bit 0.

100-Ω external LVDS termination

required.

Input Bus B Data bit 1.

100-Ω external LVDS termination

required.

Input Bus B Data bit 2.

100-Ω external LVDS termination

required.

Input Bus B Data bit 3.

100-Ω external LVDS termination

required.

Input Bus B Data bit 4.

100-Ω external LVDS termination

required.

Input Bus B Data bit 5.

100-Ω external LVDS termination

required.

Input Bus B Data bit 6.

100-Ω external LVDS termination

required.

Input Bus B Data bit 7.

100-Ω external LVDS termination

required.

Input Bus B Data bit 8.

100-Ω external LVDS termination

required.

Input Bus B Data bit 9.

100-Ω external LVDS termination

required.

Input Bus B Data bit 10.

100-Ω external LVDS termination

required.

Input Bus B Data bit 11.

100-Ω external LVDS termination

required.

Input Bus B Data bit 12.

100-Ω external LVDS termination

required.

Input Bus B Data bit 13.

100-Ω external LVDS termination

required.

Input Bus B Data bit 14.

100-Ω external LVDS termination

required.

Input Bus B Data bit 15.

100-Ω external LVDS termination

required.

Input Bus C Data bit 0.

100-Ω external LVDS termination

required.

Input Bus C Data bit 1.

100-Ω external LVDS termination

required.

DDC_DIN_C2_DPP

J19

LVDS_25_PI

-

DDC_DCLK_C

Input Bus C Data bit 2.

100-Ω external LVDS termination

required.

DDC_DIN_C3_DPN

E23

LVDS_25_NI

-

DDC_DCLK_C

Input Bus C Data bit 3.

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

7

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

8

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

DESCRIPTION

E22

LVDS_25_PI

-

DDC_DCLK_C

100-Ω external LVDS termination

required.

DDC_DIN_C4_DPN

F23

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C4_DPP

F22

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C5_DPN

G22

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C5_DPP

G21

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C6_DPN

J20

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C6_DPP

J21

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C7_DPN

H22

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C7_DPP

H21

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C8_DPN

J23

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C8_DPP

H23

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C9_DPN

K22

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C9_DPP

K23

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C10_DPN

M19

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C10_DPP

M20

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C11_DPN

M21

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C11_DPP

M22

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C12_DPN

N19

LVDS_25_NI

-

DDC_DCLK_C

NAME

NO.

DDC_DIN_C3_DPP

DDC_DIN_C12_DPP

P19

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C13_DPN

N21

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C13_DPP

N22

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C14_DPN

P20

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C14_DPP

P21

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_C15_DPN

N23

LVDS_25_NI

-

DDC_DCLK_C

DDC_DIN_C15_DPP

P23

LVDS_25_PI

-

DDC_DCLK_C

DDC_DIN_D0_DPN

T3

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D0_DPP

R3

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D1_DPN

R5

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D1_DPP

R6

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D2_DPN

R7

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D2_DPP

P6

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D3_DPN

N3

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D3_DPP

P3

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D4_DPN

P4

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D4_DPP

P5

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D5_DPN

N6

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D5_DPP

N7

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D6_DPN

N4

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D6_DPP

M4

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D7_DPN

M7

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D7_DPP

L7

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D8_DPN

K7

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D8_DPP

K6

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D9_DPN

J4

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D9_DPP

J5

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D10_DPN

H7

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D10_DPP

J6

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D11_DPN

G4

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D11_DPP

H4

LVDS_25_PI

-

DDC_DCLK_D

Submit Document Feedback

Input Bus C Data bit 4.

100-Ω external LVDS termination

required.

Input Bus C Data bit 5.

100-Ω external LVDS termination

required.

Input Bus C Data bit 6.

100-Ω external LVDS termination

required.

Input Bus C Data bit 7.

100-Ω external LVDS termination

required.

Input Bus C Data bit 8.

100-Ω external LVDS termination

required.

Input Bus C Data bit 9.

100-Ω external LVDS termination

required.

Input Bus C Data bit 10.

100-Ω external LVDS termination

required.

Input Bus C Data bit 11.

100-Ω external LVDS termination

required.

Input Bus C Data bit 12.

100-Ω external LVDS termination

required.

Input Bus C Data bit 13.

100-Ω external LVDS termination

required.

Input Bus C Data bit 14.

100-Ω external LVDS termination

required.

Input Bus C Data bit 15.

100-Ω external LVDS termination

required.

Input Bus D Data bit 0.

100-Ω external LVDS termination

required.

Input Bus D Data bit 1.

100-Ω external LVDS termination

required.

Input Bus D Data bit 2.

100-Ω external LVDS termination

required.

Input Bus D Data bit 3.

100-Ω external LVDS termination

required.

Input Bus D Data bit 4.

100-Ω external LVDS termination

required.

Input Bus D Data bit 5.

100-Ω external LVDS termination

required.

Input Bus D Data bit 6.

100-Ω external LVDS termination

required.

Input Bus D Data bit 7.

100-Ω external LVDS termination

required.

Input Bus D Data bit 8.

100-Ω external LVDS termination

required.

Input Bus D Data bit 9.

100-Ω external LVDS termination

required.

Input Bus D Data bit 10.

100-Ω external LVDS termination

required.

Input Bus D Data bit 11.

100-Ω external LVDS termination

required.

Copyright © 2020 Texas Instruments Incorporated

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

DESCRIPTION

G5

LVDS_25_NI

-

DDC_DCLK_D

H6

LVDS_25_PI

-

DDC_DCLK_D

Input Bus D Data bit 12.

100-Ω external LVDS termination

required.

DDC_DIN_D13_DPN

G7

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D13_DPP

G6

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D14_DPN

F4

LVDS_25_NI

-

DDC_DCLK_D

DDC_DIN_D14_DPP

F5

LVDS_25_PI

-

DDC_DCLK_D

DDC_DIN_D15_DPN

E5

LVDS_25_NI

-

DDC_DCLK_D

NAME

NO.

DDC_DIN_D12_DPN

DDC_DIN_D12_DPP

DDC_DIN_D15_DPP

E6

LVDS_25_PI

-

DDC_DCLK_D

DDC_DOUT_A0_DPN

AE2

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A0_DPP

AF2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A1_DPN

AD1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A1_DPP

AE1

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A2_DPN

AC1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A2_DPP

AC2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A3_DPN

AB1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A3_DPP

AB2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A4_DPN

Y2

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A4_DPP

AA2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A5_DPN

W1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A5_DPP

Y1

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A6_DPN

V1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A6_DPP

V2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A7_DPN

U1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A7_DPP

U2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A8_DPN

R2

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A8_DPP

T2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A9_DPN

N2

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A9_DPP

M2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A10_DPN

K1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A10_DPP

L2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A11_DPN

K2

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A11_DPP

K3

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A12_DPN

J3

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A12_DPP

H3

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A13_DPN

H2

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A13_DPP

J1

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A14_DPN

H1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A14_DPP

G1

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_A15_DPN

G2

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_DOUT_A15_DPP

F2

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_DOUT_B0_DPN

AE5

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B0_DPP

AE6

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B1_DPN

AD3

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B1_DPP

AD4

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B2_DPN

AD5

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B2_DPP

AD6

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B3_DPN

AC3

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B3_DPP

AC4

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B4_DPN

AB5

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B4_DPP

AB6

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B5_DPN

AB7

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B5_DPP

AC6

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B6_DPN

AA5

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B6_DPP

AA4

LVDS_25_PO

-

DDC_DCLKOUT_B

Copyright © 2020 Texas Instruments Incorporated

Input Bus D Data bit 13.

100-Ω external LVDS termination

required.

Input Bus D Data bit 14.

100-Ω external LVDS termination

required.

Input Bus D Data bit 15.

100-Ω external LVDS termination

required.

Output Bus A Data bit 0 to DMD.

Output Bus A Data bit 1 to DMD.

Output Bus A Data bit 2 to DMD.

Output Bus A Data bit 3 to DMD.

Output Bus A Data bit 4 to DMD.

Output Bus A Data bit 5 to DMD.

Output Bus A Data bit 6 to DMD.

Output Bus A Data bit 7 to DMD.

Output Bus A Data bit 8 to DMD.

Output Bus A Data bit 9 to DMD.

Output Bus A Data bit 10 to DMD.

Output Bus A Data bit 11 to DMD.

Output Bus A Data bit 12 to DMD.

Output Bus A Data bit 13 to DMD.

Output Bus A Data bit 14 to DMD.

Output Bus A Data bit 15 to DMD.

Output Bus B Data bit 0 to DMD.

Output Bus B Data bit 1 to DMD.

Output Bus B Data bit 2 to DMD.

Output Bus B Data bit 3 to DMD.

Output Bus B Data bit 4 to DMD.

Output Bus B Data bit 5 to DMD.

Output Bus B Data bit 6 to DMD.

Submit Document Feedback

9

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

AA7

LVDS_25_NO

-

DDC_DCLKOUT_B

Y7

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B8_DPN

Y3

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B8_DPP

W3

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B9_DPN

W4

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B9_DPP

V4

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B10_DPN

W6

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B10_DPP

W5

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B11_DPN

V7

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B11_DPP

V6

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B12_DPN

U4

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B12_DPP

V3

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B13_DPN

T4

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B13_DPP

T5

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B14_DPN

U6

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B14_DPP

U5

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_B15_DPN

U7

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_DOUT_B15_DPP

T7

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_DOUT_C0_DPN

T22

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C0_DPP

T23

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C1_DPN

R20

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C1_DPP

R21

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C2_DPN

T19

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C2_DPP

T20

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C3_DPN

U21

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C3_DPP

U22

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C4_DPN

U20

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C4_DPP

U19

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C5_DPN

V23

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C5_DPP

V24

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C6_DPN

V22

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C6_DPP

V21

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C7_DPN

W19

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C7_DPP

V19

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C8_DPN

W23

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C8_DPP

W24

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C9_DPN

Y22

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C9_DPP

Y23

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C10_DPN

Y20

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C10_DPP

Y21

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C11_DPN

AA24

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C11_DPP

AA23

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C12_DPN

AA19

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C12_DPP

AA20

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C13_DPN

AC24

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C13_DPP

AB24

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C14_DPN

AC19

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C14_DPP

AD19

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_C15_DPN

AC22

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_DOUT_C15_DPP

AC23

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_DOUT_D0_DPN

AB26

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D0_DPP

AC26

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D1_DPN

AA25

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D1_DPP

AB25

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D2_DPN

Y26

LVDS_25_NO

-

DDC_DCLKOUT_D

NAME

NO.

DDC_DOUT_B7_DPN

DDC_DOUT_B7_DPP

10

Submit Document Feedback

DESCRIPTION

Output Bus B Data bit 7 to DMD.

Output Bus B Data bit 8 to DMD.

Output Bus B Data bit 9 to DMD.

Output Bus B Data bit 10 to DMD.

Output Bus B Data bit 11 to DMD.

Output Bus B Data bit 12 to DMD.

Output Bus B Data bit 13 to DMD.

Output Bus B Data bit 14 to DMD.

Output Bus B Data bit 15 to DMD.

Output Bus C Data bit 0 to DMD.

Output Bus C Data bit 1 to DMD.

Output Bus C Data bit 2 to DMD.

Output Bus C Data bit 3 to DMD.

Output Bus C Data bit 4 to DMD.

Output Bus C Data bit 5 to DMD.

Output Bus C Data bit 6 to DMD.

Output Bus C Data bit 7 to DMD.

Output Bus C Data bit 8 to DMD.

Output Bus C Data bit 9 to DMD.

Output Bus C Data bit 10 to DMD.

Output Bus C Data bit 11 to DMD.

Output Bus C Data bit 12 to DMD.

Output Bus C Data bit 13 to DMD.

Output Bus C Data bit 14 to DMD.

Output Bus C Data bit 15 to DMD.

Output Bus D Data bit 0 to DMD.

Output Bus D Data bit 1 to DMD.

Output Bus D Data bit 2 to DMD.

Copyright © 2020 Texas Instruments Incorporated

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

NAME

NO.

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

DDC_DOUT_D2_DPP

Y25

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D3_DPN

W26

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D3_DPP

W25

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D4_DPN

U26

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D4_DPP

V26

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D5_DPN

U25

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D5_DPP

U24

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D6_DPN

T25

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D6_DPP

T24

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D7_DPN

R26

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D7_DPP

R25

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D8_DPN

P24

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D8_DPP

P25

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D9_DPN

N24

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D9_DPP

M24

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D10_DPN

L25

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D10_DPP

L24

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D11_DPN

K26

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D11_DPP

K25

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D12_DPN

J26

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D12_DPP

J25

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D13_DPN

J24

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D13_DPP

H24

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D14_DPN

H26

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D14_DPP

G26

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_DOUT_D15_DPN

G25

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_DOUT_D15_DPP

G24

LVDS_25_PO

-

DDC_DCLKOUT_D

DDC_SCTRL_AN

R1

LVDS_25_NO

-

DDC_DCLKOUT_A

DDC_SCTRL_AP

P1

LVDS_25_PO

-

DDC_DCLKOUT_A

DDC_SCTRL_BN

AA3

LVDS_25_NO

-

DDC_DCLKOUT_B

DDC_SCTRL_BP

AB4

LVDS_25_PO

-

DDC_DCLKOUT_B

DDC_SCTRL_CN

W20

LVDS_25_NO

-

DDC_DCLKOUT_C

DDC_SCTRL_CP

W21

LVDS_25_PO

-

DDC_DCLKOUT_C

DDC_SCTRL_DN

N26

LVDS_25_NO

-

DDC_DCLKOUT_D

DDC_SCTRL_DP

P26

LVDS_25_PO

-

DDC_DCLKOUT_D

DVALID_A_DPN

D20

LVDS_25_NI

-

DDC_DCLK_A

DVALID_A_DPP

D21

LVDS_25_PI

-

DDC_DCLK_A

DVALID_B_DPN

C8

LVDS_25_NI

-

DDC_DCLK_B

DVALID_B_DPP

D8

LVDS_25_PI

-

DDC_DCLK_B

DVALID_C_DPN

L19

LVDS_25_NI

-

DDC_DCLK_C

DVALID_C_DPP

L20

LVDS_25_PI

-

DDC_DCLK_C

DVALID_D_DPN

L3

LVDS_25_NI

-

DDC_DCLK_D

DESCRIPTION

Output Bus D Data bit 3 to DMD.

Output Bus D Data bit 4 to DMD.

Output Bus D Data bit 5 to DMD.

Output Bus D Data bit 6 to DMD.

Output Bus D Data bit 7 to DMD.

Output Bus D Data bit 8 to DMD.

Output Bus D Data bit 9 to DMD.

Output Bus D Data bit 10 to DMD.

Output Bus D Data bit 11 to DMD.

Output Bus D Data bit 12 to DMD.

Output Bus D Data bit 13 to DMD.

Output Bus D Data bit 14 to DMD.

Output Bus D Data bit 15 to DMD.

Output Bus A Serial Control to DMD.

Output Bus B Serial Control to DMD.

Output Bus C Serial Control to DMD.

Output Bus D Serial Control to DMD.

Input Bus A Data Valid Signal.

100-Ω external LVDS termination

required.

Input Bus B Data Valid Signal.

100-Ω external LVDS termination

required.

Input Bus C Data Valid Signal.

100-Ω external LVDS termination

required.

L4

LVDS_25_PI

-

DDC_DCLK_D

Input Bus D Data Valid Signal.

100-Ω external LVDS termination

required.

DDC_VERSION_0

F18

LVCMOS25_O

Hi

-

DLPC910 Firmware Rev Number bit 0

DDC_VERSION_1

G17

LVCMOS25_O

Hi

-

DLPC910 Firmware Rev Number bit 1

DDC_VERSION_2

H18

LVCMOS25_O

Hi

-

DLPC910 Firmware Rev Number bit 2

SPEED_SEL_0

H8

LVCMOS25_I

Hi

-

SPEED_SEL_1

H9

LVCMOS25_I

Hi

-

SPEED_SEL[1:0]

= 00 400MHz

= 01 480MHz

= 10, 11 Reserved Includes internal pullups. SPEED_SEL[1:0] must be set to 00

when connecting the DLPC910 with a

DLP6500.

VSP_ENABLE

E8

LVCMOS25_I

Hi

-

Reserved. Do not connect. Includes

internal pull-up.

ECP2_FINISHED

E25

LVCMOS25_O

Hi

-

DLPR910 Initialization complete.

Connected to LED.

DVALID_D_DPP

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

11

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

AA17

LVCMOS25_O

Hi = On

-

Power Indicator LED Output.

AB17

LVCMOS25_O

Hi = On

-

Heartbeat Indicator LED Output.

F25

LVCMOS25_I

Lo

-

DMD Reset Pulse Watchdog Timer

Enable

PWR_FLOAT

G9

LVCMOS25_I

Hi

-

Park DMD mirrors.

NS_FLIP

F19

LVCMOS25_I

Hi

-

Top/Bottom image flip on DMD

COMP_DATA

G19

LVCMOS25_I

Hi

DDC_DCLK_[A,B,C,D]

Compliment Data (0 1)

INIT_ACTIVE

E26

LVCMOS25_O

Hi

-

DLPC910 Initialization Routine Active

RST_ACTIVE

G10

LVCMOS25_O

Hi

-

DMD Mirror Clocking Pulse in progress

RST2BLKZ

E18

LVCMOS25_I

Hi

-

Dual and Quad Block control

NAME

NO.

VLED0

VLED1

WDT_ENBLZ

DESCRIPTION

TST_PT_0

Y12

LVCMOS33_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_1

AA12

LVCMOS33_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_2

Y13

LVCMOS33_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_3

AA13

LVCMOS33_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_4

AA14

LVCMOS33_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_5

AB14

LVCMOS33_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_6

AA15

LVCMOS33_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_7

AB15

LVCMOS33_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_8

C1

LVCMOS25_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_9

D1

LVCMOS25_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_10

E1

LVCMOS25_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_11

E2

LVCMOS25_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_12

E3

LVCMOS25_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_13

F3

LVCMOS25_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_14

E7

LVCMOS25_O

-

-

No connect. For access to test point

output route to test via.

TST_PT_15

F7

LVCMOS25_O

-

-

No connect. For access to test point

output route to test via.

DLPC_VRN_BANK4

AB12

DCI Reference Voltage

-

-

Requires an external 49.9-Ω pull-up

resistor to 3.3 V.

DLPC_VRP_BANK4

AC11

DCI Reference Voltage

-

-

Requires an external 49.9-Ω pull-down

resistor to GND.

LOAD4_ENZ

D25

LVCMOS25_I

Lo

-

Signal enables the Load-4 functionality of

the DMD. Includes internal pull-up.

DMD_IRQ

D26

LVCMOS25_O

Hi

-

Signal indicates a DMD voltage is

inactive. Includes internal pull-up

DLPC_VBATT

K18

LVCMOS33_I

-

-

DLPC910 VBATT reference. Connect to

GND.

DLPC_DONE

K10

LVCOMS33_O

-

-

DLPC910 Initialization configuration

complete. Connect to DLPR910 CEZ pin.

Requires 4.7-kΩ pull-up to 3.3 V.

DLPC_HSWAPEN

L18

LVCMOS33_I

-

-

DLPC910 Configuration. Requires 4.7kΩ pull-up to 3.3 V.

DDC_M0

W18

LVCMOS33_I

-

-

DLPC910 Configuration. Connect to GND

DDC_M1

Y17

LVCMOS33_I

-

-

DLPC910 Configuration. Connect to GND

DDC_M2

V18

LVCMOS33_I

-

-

DLPC910 Configuration. Connect to GND

INTB_DDC

J11

LVCMOS25_O

Hi

-

DLPC910 Configuration. Connect to

DLPR910 OE/RESET. Requires 4.7-kΩ

pull-up to 3.3 V.

PROGB_DDC

J18

LVCMOS25_O

Hi

-

DLPC910 Configuration. Connect to

DLPR910 CF. Requires 4.7-kΩ pull-up

to 3.3 V.

12

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

DESCRIPTION

J10

LVCMOS25_O

-

PROM_CCK_DDC

Configuration PROM Clock. Connect to

DLPR910 CLK. Connects to center of

voltage divider (100/100-Ω 3.3 V and

GND).

PROM_D0_DDC

K11

LVCMOS25_I

-

PROM_CCK_DDC

Configuration PROM Data in. Connected

to DLPR910 Data 0 (D0)

DLPC_DOUTBUSY

W11

LVCMOS25_I

-

-

Configuration PROM Busy. Connect to

test via for debug only.

RDWR_B

P18

LVCMOS25_I

-

-

DLPC910 Configuration. Requires 1-kΩ

pull-down to ground.

TCK_JTAG

U11

LVCMOS33_I

-

TCK_JTAG

JTAG Clock. Connects to DLPC910,

DLPR910, and JTAG header TCK (if user

has JTAG they must build their chain

accordingly)

TDO_DDC

W10

LVCMOS33_O

-

TCK_JTAG

JTAG Data out of DLPC910. Connects to

JTAG return TDO on JTAG header

TDO_XCF16DDC

V11

LVCMOS33_I

-

TCK_JTAG

JTAG Data out of DLPR910 to DLPC910.

Connects to DLPR910 TDO (DLPC910

internal signal TDI_0)

TMS_JTAG

V12

LVCMOS33_I

Hi

TCK_JTAG

NAME

NO.

PROM_CCK_DDC

JTAG. Connects to DLPC910, DLPR910,

and JTAG

header TMS

VCCAUX

J8, K17, L8, M17, N8, P17,

R8, T17, U8, V17, W8, W16

PWR

-

-

Aux Power. VCC_2P5V

VCCINT

H15, J12, J14, J16, K9, K13,

K15, L10, L12, L14, L16, M9,

M11, M15, N10, N12, N16,

P9, P11, P15, R10, R12,

R16, T9, T11, T13, T15, U10,

U12, U14, U16, V9, V13,

V15, W14, Y15

PWR

-

-

Power. VCC_1P0V

VCCO_0

Y9, W12

PWR

-

-

VCCO_2

AA16, AD17

PWR

VCCO_4

AB13, AC10

PWR

-

-

VCCO_1

C10, F11

PWR

-

-

VCCO_3

D17, E14

PWR

-

-

VCCO_11

F21, H25, J22

PWR

-

-

VCCO_12

H5, J2, L6

PWR

-

-

VCCO_13

M23, N20, R24

PWR

-

-

VCCO_14

R4, V5, W2

PWR

-

-

VCCO_15

B23,C20, E24

PWR

-

-

VCCO_16

D7, E4, G8

PWR

-

-

VCCO_17

T21, V25, W22

PWR

-

-

VCCO_18

AA6, AB3, AD7

PWR

-

-

VCCO_21

AC20, AB23, AE24

PWR

-

-

A1, A6, A11, A16, A21, A26,

AA1, AA11, AA21, AA26,

AB8, AB18, AC5, AC15,

AC25, AD2, AD12, AD22,

AE4, AE9, AE14, AE19, AF1,

AF6, AF11, AF16, AF21,

AF26, B3, B8, B13, B18, C5,

C15, C25, D2, D12, D22, E9,

E19, F1, F6, F16, F26, G3,

G13, G18, G23, H10, H20,

J7, J9, J13, J15, J17, K4, K8,

K12, K14, K16, K19, K24,

L1, L9, L11, L13, L15, L17,

L21, L26, M3, M8, M10,

GND

-

-

GND

Power. VCC_3P3V

Power. VCC_2P5V

M12, M16, M18, N5, N9,

N11, N15, N17, N25, P2, P7,

P8, P10, P12, P16, P22, R9,

R11, R15, R17, R19, T1, T6,

T8, T10, T12, T14, T16, T26,

U3, U9, U13, U15, U17, U18,

U23, V8, V10, V14, V16,

V20, W7, W9, W13, W15,

W17, Y4, Y14, Y16, Y19,

Y24, M13, M14, N13, N14,

P13, P14, R13, R14, N18,

R18, T18

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

13

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

PIN

NAME

NO.

I/O TYPE

ACTIVE

(HI OR LO)

CLOCK SYSTEM

DESCRIPTION

RESERVED_AC12

AC12

LVCMOS33_O

-

-

Route to via for access to pin output.

RESERVED_AD11

AD11

LVCMOS33_O

-

-

Route to via for access to pin output.

RESERVED_AA9

AA9

LVCMOS33_I

-

-

Includes internal pull-up

RESERVED_Y10

Y10

LVCMOS33_I

-

-

Includes internal pull-up

RESERVED_Y11

Y11

LVCMOS33_I

-

-

Includes internal pull-up

AB11

LVCMOS33_I

-

-

Includes internal pull-up

RESERVED_F10

F10

LVCMOS33_I

-

-

Includes internal pull-up

RESERVED_F8

F8

LVCMOS33_I

-

-

Includes internal pull-up

A4, A5, AA18, AB16, AB19,

AB20, AB21, AC21, AD9,

AD16, AD20, AD21, AD23,

AD24, AD25, AD26, AE3,

AE7, AE8, AE10, AE11,

AE12, AE13, AE15, AE16,

AE17, AE18, AE20, AE21,

AE22, AE23, AE25, AE26,

AF3, AF4, AF5, AF7, AF8,

AF9, AF10, AF12, AF13,

AF14, AF15, AF17, AF18,

AF19, AF20, AF22, AF23,

AF24, AF25, C22, D23, E11,

F12, F24, L22, L23, M5, M6,

R22, R23, Y18

NC

-

-

No Connection.

Unused Pins.

RESERVED_AB11

UNUSED

14

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

6 Specifications

6.1 Absolute Maximum Ratings

See (1)

MIN

MAX

UNIT

ELECTRICAL

VCCINT

Supply voltage range (2)

VCCO

VCCAUX

VI

Input voltage range (3)

VO

Output voltage range (4)

–0.50

1.1

–0.50

3.75

V

–0.50

3.0

3.3 V

–0.95

4.05

2.5 V

–0.75

VCCO + 0.50

3.3 V

–0.30

VCCO – 0.40

2.5 V

–0.30

VCCO – 0.40

125

°C

–65

150

°C

V

V

ENVIRONMENTAL

TJ

Junction temperature

Tstg

Storage temperature (ambient)

(1)

(2)

(3)

(4)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under

Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

All voltage values are with respect to GND.

Applies to external input and bidirectional buffers.

Applies to external output and bidirectional buffers.

6.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC

JS-001-2010, all pins (1)

+ 2000

Charged device model (CDM), per JEDEC specification

JESD22-C101, all pins (2)

+ 400

UNIT

V

Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001-2010. JEDEC document JEP155 states that 500V HBM

allows safe manufacturing with a standard ESD control process.

Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe

manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

ELECTRICAL

VCCINT

1-V supply voltage, core logic

0.95

1.00

1.05

V

VCCO

2.5-V supply voltage, I/O for VCCO_1,3,11,12,13,14,15,16,17,18,21

1.14

2.50

3.45

V

VCCO

3.3-V supply voltage, I/O for VCCO_0,2,4

VCCAUX 2.5-V supply voltage, I/O

VI

Input voltage

Output voltage

3.30

3.45

V

2.500

2.625

V

3.3-V DCI and CMOS for VCCO_0,2,4

0

VCCO

2. 5-V CMOS for

VCCO_1,3,11,12,13,14,15,16,17,18,21

0

VCCO

0.3

2.2

3.3-V DCI and CMOS for VCCO_0,2,4

0

VCCO

2.5-V CMOS for

VCCO_1,3,11,12,13,14,15,16,17,18,21

0

VCCO

2.5-V LVDS

VO

3.0

2.375

Copyright © 2020 Texas Instruments Incorporated

V

V

Submit Document Feedback

15

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

over operating free-air temperature range (unless otherwise noted)

MIN

2.5-V LVDS

TA

Operating ambient temperature

NOM

MAX

UNIT

0.825

1.675

0

85

°C

6

W

ENVIRONMENTAL

PD

Continuous total power dissipation

6.4 Thermal Information

DLPC910

THERMAL METRIC

(1)

ZYR (FCBGA)

UNIT

676 PINS

RθJA

Junction-to-ambient thermal resistance (2)

12.1

°C/W

RθJC

Junction-to-case thermal resistance

3.2

°C/W

RθJB

Junction-to-board thermal resistance

0.19

°C/W

(1)

(2)

Refer to the XC5VLX30 product specifications at www.xilinx.com for complete thermal specifications.

In still air.

6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

PARAMETER

VIH

High-level input voltage

3.3-V CMOS

VIL

Low-level input voltage

3.3-V CMOS

VOH

High-level output voltage

3.3-V DCI and CMOS

VOL

Low-level output voltage

3.3-V DCI and CMOS

MIN

TYP

MAX

UNIT

2.0

V

0.8

V

0.4

V

2.9

V

VIH

High-level input voltage

2.5-V CMOS

VIL

Low-level input voltage

2.5-V CMOS

1.7

V

VOH

High-level output voltage

VOL

Low-level output voltage

CI

Input capacitance

ICCINT

1V Supply voltage range, core supply

1430

2100

mA

ICCO +

ICCAUX

2.5V Supply voltage range, I/O supply

1650

2300

mA

ICCO

3.3V Supply voltage range, I/O supply

180

mA

0.7

2.5-V interface

V

VCCO – 0.4

2.5-V LVDS

V

1.38

2.5-V interface

0.4

2.5-V LVDS

V

1.03

2.5-V interface

8

2.5-V LVDS

8

pF

6.6 Timing Requirements

(see (1))

MIN

fcd

Clock frequency, DCLKIN_n

NOM

(2)

MAX

UNIT

400

MHz

480

fcr

Clock frequency, CLK_R

tc

Cycle time, DCLKIN_n

tw(H)

Pulse duration, high

16

Submit Document Feedback

50

50% to 50% reference

points (signal)

MHz

fcd = 400 MHz

2.5

fcd = 480 MHz

2.083

fcd = 400 MHz

1.25

fcd = 480 MHz

1.042

ns

ns

Copyright © 2020 Texas Instruments Incorporated

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

(see (1))

MAX

UNIT

tw(L)

Pulse duration, low

50% to 50% reference

points (signal)

fcd = 400 MHz

MIN

1.25

ns

fcd = 480 MHz

1.042

tt

Transition time, tt = tf /tr

20% to 80% reference

points (signal)

fcd = 400 MHz

0.6

tjp

Period Jitter DCLKIN_n (3)

tsk

(1)

(2)

(3)

(4)

NOM

fcd = 480 MHz

ns

0.5

100

ps

Skew, DIN_A(15-0) to DCLKIN_A

-100

Skew, DIN_B(15-0) to DCLKIN_B

-100

100

100

Skew, DIN_C(15-0) to DCLKIN_C

-100

100

Skew, DIN_D(15-0) to DCLKIN_D

-100

100

Skew, DVALID_n to DCLKIN_n↑

-100

100

Skew, BLKMD BLKAD to

DCLKIN_n↑ (4)

-100

100

Skew, ROWMD or ROWAD to

DCLKIN_n↑ (4)

-100

100

Skew, STEPVCC to DCLKIN↑ (4)

-100

100

ps

It is recommended that the COMP_DATA, NS_FLIP and RST2BLK flags be set to one value and not adjusted during normal system

operation.

Preferred DDC_DCLK _n duty cycle = 50%

This is the deviation in period from ideal period due solely to high frequency jitter.

First edge of DDC_DIN*, ROW*, and BLK* should be synchronous to DVALID rising edge.

tsk

tw(H)

DCLKIN

50%

tsk

tt

tc

tw(L)

50%

Cycle 1

50%

80%

20%

Cycle#CLKS/

ROW

50%

DVALID

DDR Data

Control

Figure 6-1. Input Interface Timing

Note

Dynamic changes to RST2BLK, NS_FLIP and COMP_DATA during normal operation are not

recommended.

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

17

�DLPC910

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

www.ti.com

7 Detailed Description

7.1 Overview

The DLPC910 digital controller provides a reliable high speed data pipe to the DMD, where the digital input on

the LVDS interface is configured for the required timing requirements of the DMD. The DMD reflects light by

using 1-bit binary encoded patterns, where each mirror is a pixel-to-mirror mapping of the pattern.

7.2 Functional Block Diagram

7.3 Feature Description

7.3.1 Input LVDS Interface

The data input interface consists of four input data buses: DDC_DIN_A, DDC_DIN_B, DDC_DIN_C, and

DDC_DIN_D. Each bus contains 16 differential pairs which are synchronous to the rising and falling edges of its

associated DDC_DCLK signal.

7.3.2 Data Clock

The data clock interface consists of four differential pairs: DDC_DCLK_A, DDC_DCLK_B, DDC_DCLK_C, and

DDC_DCLK_D. Each must operate continuously. All signals associated with the data clock should be

synchronous to these signals. For example, DDC_DIN_A and DVALID_A should be synchronous to the rising

edge of DDC_DCLK_A. This clock should be valid prior to releasing CTRL_RSTZ. DDC_DCLK is a DDR clock

with data loaded on both rising and falling edges of DDC_DCLK. The jitter on this clock is specified in Timing

Requirements. When connecting the DLPC910 with a DLP6500, SPEED_SEL[1:0] inputs must be set to

"00".

7.3.3 Data Valid

The data valid interface consists of four differential pairs: DVALID_A, DVALID _B, DVALID _C, and DVALID _D.

The DVALID signal should be asserted synchronous to the data it is meant to frame. DVALID can be asserted

as:

18

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�DLPC910

www.ti.com

•

•

•

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

Framing individual row loads with breaks between rows, or

Framing block loads - for example, the DLP9000X/DLP9000XUV with 16 blocks allows framing 100

contiguous row loads, or

Framing the entire DMD load where the DVALID stays active for all DMD row loads with zero invalid data

between rows.

If the DVALID frames DMD blocks or the entire DMD, assure that the block and row control signals are adjusted

at the proper locations in the data stream. Refer to Block Mode Operation for further information.

7.3.4 Interface Training

The DLPC910 detects the phase differences between the ½ speed clock (used in the device driving the LVDS

data) and the internally generated ½ speed data clocks to select a clock phase for data capture. This is done by

supplying a simple repeating pattern on all of the data inputs while the INIT_ACTIVE output of the DLPC910 is

high/active. The details of the training pattern are described below.

Figure 7-1 shows a simple block diagram of the training pattern insertion logic.

Sys Clk

IO Clk

System Data

0

4:1 Serdes

Dout

Training Data

(0100)

1

Din 3:0

INIT_ACTIVE

Figure 7-1. Block Diagram of Training Pattern Logic

The expected training pattern is 0100. In Figure 7-2, the data input to the 4:1 SERDES cells is captured on the

rising edge of the ½ speed system clock. The output latency shown is based on the documentation for the Xilinx

SERDES cells. Individual implementation may vary depending on the type of cells, technology, and design

technique used.

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

19

�DLPC910

www.ti.com

DLPS064D – SEPTEMBER 2015 – REVISED SEPTEMBER 2020

½ Speed

System CLK

Full Speed

IO CLK

4:1

SERDES Data

(at the interface)

0100

0100

0100

0100

0100

Output Data

Figure 7-2. Training Pattern Alignment

Note

In Xilinx FPGAs (due to the construction of the ISERDES and OSERDES cells) a pattern of 0010

needs to be applied to the output/transmitting SERDES cells data pins (D1 = 0, D2 = 0, D3 = 1, D4 =

0) in order to receive a result of 0100 (Q1 = 0, Q2 = 1, Q3 = 0, Q4 = 0) at the input/receiving SERDES

cell.

The patterns should be applied on all of the data and DVALID pins. In this respect, the interface is treated as a

17 bit interface with DVALID being the 17th data bit. The receiving logic in the DLPC910 adjusts the clock phase

until the correct pattern is seen at the inputs. This allows DLPC910 to correctly select a clock phase for data

capture and will contribute to a more robust interface. It is important that the training pattern is applied to the

DVALID and data inputs of the DLPC910 before reset to the device is de-asserted, as training commences

immediately on the de-assertion of reset. The INIT_ACTIVE signal is asserted while the device is held in reset in

order to help facilitate this behavior.

7.3.5 Row and Block Interface

7.3.5.1 Row Mode

The DMD incorporates single row write operations using a row address counter that is randomly addressable.