DS90UB933-Q1

DS90UB933-Q1

SNLS546E – AUGUST 2016 – REVISED

NOVEMBER 2020

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

www.ti.com

DS90UB933-Q1 FPD-Link III Serializer for 1-MP/60-fps Cameras 10/12 Bits,100 MHz

1 Features

3 Description

•

The DS90UB933-Q1 device offers an FPD-Link III

interface with a high-speed forward channel and a

bidirectional control channel for data transmission

over a single coaxial cable or differential pair. The

DS90UB933-Q1 device incorporates differential

signaling on both the high-speed forward channel and

bidirectional control channel data paths. The

serializer/deserializer pair is targeted for connections

between imagers and video processors in an

electronic control unit (ECU). This device is ideally

suited for driving video data requiring up to 12-bit pixel

depth plus two synchronization signals along with

bidirectional control channel bus.

•

•

•

•

•

•

•

•

•

•

AEC-Q100 qualified for automotive applications

with the following results:

– Device temperature grade 2: –40°C to +105°C

ambient operating temperature

37.5-MHz to 100-MHz input pixel clock support

Robust Power-Over-Coaxial (PoC) operation

Programmable data payload:

– 10-Bit payload up to 100-MHz

– 12-Bit payload up to 100-MHz

Continuous low latency bidirectional control

interface channel with I2C support at 400-kHz

Embedded clock with DC-balanced coding to

support AC-coupled interconnects

Capable of driving up to 15-m coaxial or Shielded

Twisted-Pair (STP) cables

4 Dedicated General-Purpose Input/Output (GPIO)

1.8-V, 2.8-V or 3.3-V compatible parallel inputs on

serializer

Single power supply at 1.8-V

ISO 10605 and IEC 61000-4-2 ESD compliant

2 Applications

•

•

•

Automotive

– Surround View Systems (SVS)

– Front Cameras (FC)

– Rear View Cameras (RVC)

– Sensor fusion

– Driver Monitor Cameras (DMS)

– Remote satellite RADAR, ToF, and LIDAR

sensors

Security and surveillance

Machine vision applications

Parallel

Data In

10 or 12

Using TI’s embedded clock technology allows

transparent full-duplex communication over a single

differential pair, carrying asymmetrical-bidirectional

control channel information. This single serial stream

simplifies transferring a wide data bus over PCB

traces and cable by eliminating the skew problems

between parallel data and clock paths. This

significantly saves system cost by narrowing data

paths that in turn reduce PCB layers, cable width, and

connector size and pins. Internal DC-balanced

encoding/decoding is used to support AC-coupled

interconnects.

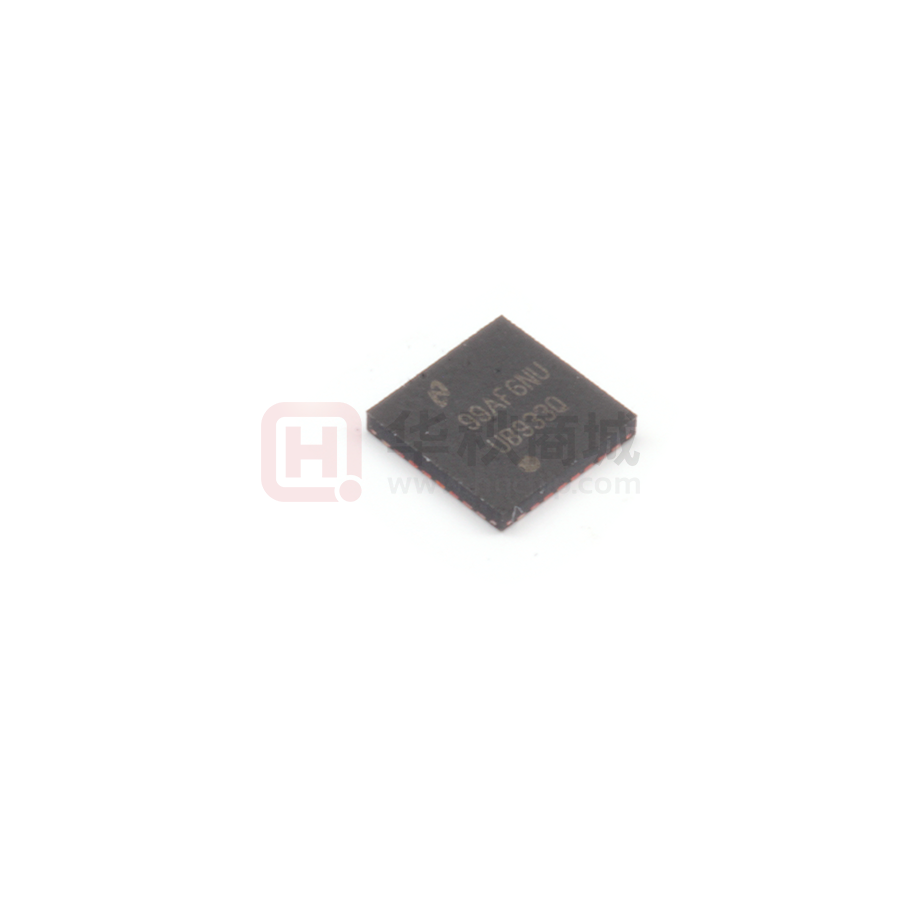

Device Information

PART NUMBER(1)

DS90UB933-Q1

(1)

PACKAGE

WQFN (32)

HSYNC,

VSYNC

Parallel

Data Out

10 or 12

FPD-Link III

DS90UB933-Q1

Bidirectional

Control Channel

4

GPO

2

Bidirectional

Control Bus

5.00 mm × 5.00 mm

For all available packages, see the orderable addendum at

the end of the data sheet.

2

HD Image

Sensor

BODY SIZE (NOM)

Serializer

DS90UB934-Q1

or

DS90UB964-Q1

2

HSYNC,

VSYNC

4

Image Signal

Processor

(ISP)

GPIO

2

Deserializer

Bidirectional

Control Bus

Simplified Schematic

An©IMPORTANT

NOTICEIncorporated

at the end of this data sheet addresses availability, warranty, changes, use in

safety-critical

applications,

Copyright

2020 Texas Instruments

Submit

Document

Feedback

intellectual property matters and other important disclaimers. PRODUCTION DATA.

1

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Pin Configuration and Functions...................................4

Pin Functions.................................................................... 4

6 Specifications.................................................................. 6

6.1 Absolute Maximum Ratings........................................ 6

6.2 ESD Ratings............................................................... 6

6.3 Recommended Operating Conditions.........................6

6.4 Thermal Information....................................................7

6.5 Electrical Characteristics.............................................7

6.6 Recommended Serializer Timing For PCLK............. 10

6.7 AC Timing Specifications (SCL, SDA) - I2CCompatible.................................................................. 11

6.8 Bidirectional Control Bus DC Timing

Specifications (SCL, SDA) - I2C-Compatible.............. 11

6.9 Serializer Switching Characteristics..........................12

6.10 Timing Diagrams..................................................... 14

6.11 Typical Characteristics............................................ 16

7 Detailed Description......................................................17

7.1 Overview................................................................... 17

7.2 Functional Block Diagram......................................... 17

7.3 Feature Description...................................................17

7.4 Device Functional Modes..........................................21

7.5 Programming............................................................ 26

7.6 Register Maps...........................................................30

8 Application and Implementation.................................. 37

8.1 Application Information............................................. 37

8.2 Typical Applications.................................................. 39

9 Power Supply Recommendations................................42

10 Layout...........................................................................43

10.1 Layout Guidelines................................................... 43

10.2 Layout Example...................................................... 44

11 Device and Documentation Support..........................46

11.1 Documentation Support.......................................... 46

11.2 Receiving Notification of Documentation Updates.. 46

11.3 Support Resources................................................. 46

11.4 Trademarks............................................................. 46

11.5 Electrostatic Discharge Caution.............................. 46

11.6 Glossary.................................................................. 46

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision D (January 2020) to Revision E (November 2020)

Page

• Added register 0x27[3] to register map.............................................................................................................30

• Clarified PDB voltage level for t3 and t4 in Power-Up Sequencing from 90% VPDB to PDB VIH ...................... 37

• Changed Power-Up Sequencing alternative programming steps (t3*) to add NCLK reset............................... 37

• Clarified Power-Up Sequencing alternative programming steps (t3*) to remove delay between I2C commands

..........................................................................................................................................................................37

Changes from Revision C (November 2019) to Revision D (January 2020)

Page

• Clarified GPO2 description by removing statement about leaving pin open if unused ...................................... 4

• Added maximum power up timing constraint between VDD_n and PDB ........................................................ 37

• Added recommended software programming steps if VDD_n to PDB maximum power up timing constraint

can not be met ................................................................................................................................................. 37

Changes from Revision B (September 2018) to Revision C (November 2019)

Page

• Added register 0x27[5] to register map ............................................................................................................30

Changes from Revision A (December 2016) to Revision B (September 2018)

Page

• Added recommendation to ensure GPO2 is low when PDB goes high.............................................................. 4

• Added external clock input frequency range ......................................................................................................6

• Added strap pin input current specification for MODE and IDX pins ................................................................. 7

• Updated TJIT1 PCLK input jitter in the external oscillator mode........................................................................ 10

• Added that 0.45UI TJIT2 maximum is when used with DS90UB934-Q1 and added new foot note ..................10

• Added clarification on MODE pin description in PCLK from imager mode ...................................................... 22

• Updated the MODE setting values to ratio from voltage...................................................................................22

• Updated IDX setting values to ratio from voltage............................................................................................. 27

• Added register "TYPE" column per legend ......................................................................................................30

2

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�www.ti.com

•

•

•

•

•

•

•

•

•

•

DS90UB933-Q1

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

Added type and default value to the reserved register bits that were missing this information........................ 30

Added that register 0x00[7:1] does not auto update IDX strapped address .................................................... 30

Added description for 0x05 bits 1 and 0 (TX_MODE_12b and TX_MODE_10b)............................................. 30

Added reference to Power over Coax Application report..................................................................................37

Clarified description on PDB pin usage during power up ................................................................................ 37

Added paragraph to explain setting registers if GPO2 state is not determined when PDB goes high ............ 37

Added GPO2 to suggested power-up sequencing diagram ............................................................................ 37

timing constraint for PDB to GPO2 delay ........................................................................................................ 37

Revised coax connection diagram to include pulldown resistor for GPO2 ...................................................... 39

Revised STP connection diagram to include pulldown resistor for GPO2 .......................................................41

Changes from Revision * (August 2016) to Revision A (December 2016)

Page

• Changed Product Preview to Production Data release...................................................................................... 1

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

3

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

16

15

GPO[0]

14

VDDCML

13

DOUT+

12

DIN[1]

GPO[1]

DOUT-

11

DIN[2]

GPO[2]/

CLKOUT

DIN[3]

GPO[3]/

CLKIN

DIN[4]

DIN[0]

DIN[5]

17

VDDT

VDDPLL

PDB

DAP = GND

DS90UB933-Q1

Serializer

2

3

4

5

6

7

PCLK

SCL

SDA

ID[x]

RES

8

MODE

1

VSYNC

DIN[11]

18

HSYNC

DIN[10]

19

32

DIN[9]

20

10

DIN[8]

21

9

25

26

27

VDDD

22

29

DIN[7]

23

30

DIN[6]

24

31

VDDIO

28

5 Pin Configuration and Functions

Figure 5-1. RTV Package 32-Pin WQFN Top View

Pin Functions

PIN

NAME

I/O

NO.

DESCRIPTION

LVCMOS PARALLEL INTERFACE

19,20,21,22,

23,24,26,27,

29,30,31,32

Inputs,

LVCMOS

w/ pulldown

Parallel data Inputs. For 10-bit MODE, parallel inputs DIN[0:9] are active. DIN[10:11] are

inactive and should not be used. Any unused inputs (including DIN[10:11]) must be No

Connect. For 12-bit MODE, parallel inputs DIN[0:11] are active. Any unused inputs must be

No Connect.

HSYNC

1

Input,

LVCMOS

w/ pulldown

Horizontal SYNC input. Note: HS transition restrictions: 1. 12-bit mode: No HS restrictions

(raw) 2. 10-bit mode: HS restricted to no more than one transition per 10 PCLK cycles.

Leave open if unused.

VSYNC

2

Input,

LVCMOS

w/ pulldown

Vertical SYNC input. Note: VS transition restrictions: 1. 12-bit mode: No VS restrictions (raw)

2. 10-bit mode: VS restricted to no more than one transition per 10 PCLK cycles. Leave

open if unused.

PCLK

3

Input,

LVCMOS

w/ pulldown

Pixel clock input pin. Strobe edge set by TRFB control register 0x03[0].

DIN[0:11]

GENERAL PURPOSE OUTPUT (GPO)

GPO[1:0]

GPO[2]/

CLKOUT

4

16,15

17

Output,

LVCMOS

General-purpose output pins can be configured as outputs, used to control and respond to

various commands. GPO[1:0] can be configured to be the outputs for input signals coming

from GPIO[1:0] pins on the deserializer or can be configured to be outputs of the local

register on the serializer. Leave open if unused.

Output,

LVCMOS

GPO[2] pin can be configured to be the output for input signal coming from the GPIO[2] pin

on the deserializer or can be configured to be the output of the local register on the

Serializer. It can also be configured to be the output clock pin when the DS90UB933-Q1

device is used in the external oscillator mode. See Section 7.4 for a detailed description of

External Oscillator mode. It is recommended to pull GPO2 to GND with a minimum 40-kΩ

resistor to ensure GPO2=LOW when PDB transitions from LOW to HIGH.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

PIN

NAME

GPO[3]/

CLKIN

I/O

NO.

18

DESCRIPTION

GPO[3] can be configured to be the output for input signals coming from the GPIO[3] pin on

the deserializer or can be configured to be the output of the local register setting on the

Input/Output,

serializer. It can also be configured to be the input clock pin when the DS90UB933-Q1

LVCMOS

serializer is working with an external oscillator. See Section 7.4 for a detailed description of

external oscillator mode. Leave open if unused.

BIDIRECTIONAL CONTROL BUS - I2C-COMPATIBLE

SCL

4

Input/Output, Clock line for the bidirectional control bus communication

Open Drain SCL requires an external pullup resistor to V(VDDIO).

SDA

5

Input/Output, Data line for the bidirectional control bus communication

Open Drain SDA requires an external pullup resistor to V(VDDIO).

MODE

8

Device mode select

Resistor (Rmode) to ground and 10-kΩ pullup to 1.8 V rail. MODE pin on the serializer can

Input, analog

be used to select whether the system is running off the PCLK from the imager or an external

oscillator. See details in Table 7-2.

IDX

6

Device ID Address Select

Input, analog The IDX pin on the serializer is used to assign the I2C device address. Resistor (RID) to

Ground and 10-kΩ pullup to 1.8 V rail. See Table 7-6.

CONTROL AND CONFIGURATION

PDB

9

Input,

LVCMOS

w/ pulldown

RES

7

Input,

LVCMOS

w/ pulldown

Power-down mode input pin

PDB = H, Serializer is enabled and is ON.

PDB = L, Serializer is in power down mode. When the serializer is in power down, the PLL is

shut down, and IDD is minimized. Programmed control register data is NOT retained and

reset to default values.

Reserved

This pin MUST be tied LOW.

FPD–Link III INTERFACE

DOUT+

DOUT-

13

Input/Output, Non-inverting differential output, bidirectional control channel input. The interconnect must

CML

be AC coupled with a 0.1-µF capacitor.

12

Inverting differential output, bidirectional control channel input. The interconnect must be AC

Input/Output, coupled with a 0.1-µF capacitor. For applications using single-ended coaxial interconnect,

CML

place a 0.047-µF AC-coupling capacitor in series with a 50-Ω resistor before terminating to

GND.

POWER AND GROUND(1)

VDDPLL

10

Power,

Analog

PLL power, 1.8 V ±5%.

VDDT

11

Power,

Analog

Tx analog power, 1.8 V ±5%.

VDDCML

14

Power,

Analog

CML and bidirectional channel driver power, 1.8 V ±5%.

VDDD

28

Power, Digital Digital Power, 1.8 V ±5%.

VDDIO

25

Power, Digital

Power for I/O stage. The single-ended inputs and SDA, SCL are powered from V(VDDIO).

VDDIO can be connected to a 1.8 V ±5% or 2.8 V ±10% or 3.3 V ±10%.

DAP

Ground, DAP

DAP must be grounded. DAP is the large metal contact at the bottom side, located at the

center of the WQFN package. Connected to the ground plane (GND) with at least 9 vias.

VSS

(1)

See Section 8.1.2.

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

5

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

MIN

MAX

UNIT

Supply voltage – V(VDD_n) (V(VDDPLL), V(VDDT), V(VDDCML), V(VDDD))

–0.3

2.5

V

Supply voltage – V(VDDIO)

−0.3

4

V

LVCMOS input voltage

−0.3

V(VDDIO) + 0.3

V

FPD-Link III I/O voltage – V(VDD_n)

–0.3

V(VDD_n) + 0.3

V

150

°C

150

°C

Junction temperature

Storage temperature, Tstg

(1)

−65

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Section 6.3.

Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

VALUE

Human body model (HBM), per AEC

HBM ESD Classification Level 3B

Q100-002(1)

Charged device model (CDM), per AEC

Q100-011

CDM ESD Classification Level C6

V(ESD)

Electrostatic

discharge

(IEC 61000-4-2)

D R = 330 Ω, Cs = 150 pF

(ISO10605)

RD = 330 Ω, Cs = 150/330 pF

RD = 2 KΩ, Cs = 150/330 pF

(1)

UNIT

±8000

Corner pins (1, 8, 9, 16, 17, 24, 25, 32)

±1000

Other pins

Air Discharge

(DOUT+, DOUT-, RIN+, RIN-)

±25000

Contact Discharge

(DOUT+, DOUT-, RIN+, RIN-)

±7000

Air Discharge

(DOUT+, DOUT-, RIN+, RIN-)

±15000

Contact Discharge

(DOUT+, DOUT-, RIN+, RIN-)

±8000

V

AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

Supply voltage, V(VDD_n)

LVCMOS supply voltage

Supply noise(1)

Power-Over-Coax Supply

Noise

V(VDDIO)= 1.8 V

NOM

MAX

UNIT

1.71

1.8

1.89

V

1.71

1.8

1.89

V

V(VDDIO)= 3.3 V

3

3.3

3.6

V(VDDIO)= 2.8 V

2.52

2.8

3.08

V(VDD_n) = 1.8 V

25

V(VDDIO) = 1.8 V

25

mVp-p

V(VDDIO) = 3.3 V

50

ƒ = 30 Hz - 1 KHz, trise > 100 µs

Measured differentially between DOUT+ and DOUT–

(coax mode only)

35

mVp-p

ƒ = 1 KHz - 50 MHz

Measured differentially between DOUT+ and DOUT(coax mode only)

35

mVp-p

Operating free air temperature, TA

6

MIN

105

°C

PCLK clock frequency - 10-bit mode

50

100

MHz

PCLK clock frequency - 12-bit mode

37.5

100

MHz

Submit Document Feedback

–40

25

Copyright © 2020 Texas Instruments Incorporated

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

External clock input frequency to GPO3 - 10-bit mode

25

50

MHz

External clock input frequency to GPO3 - 12-bit mode

25

66.67

MHz

(1)

Supply noise testing was done with minimum capacitors (as shown on Figure 8-9, Figure 8-5 on the PCB. A sinusoidal signal is AC

coupled to the V(VDD_n) (1.8 V) supply with amplitude = 25 mVp-p measured at the device V(VDD_n) pins. Bit error rate testing of input to

the serializer and output of the deserializer with 10-meter cable shows no error when the noise frequency on the serializer is less than

1 MHz. The deserializer, on the other hand, shows no error when the noise frequency is less than 750 kHz.

6.4 Thermal Information

DS90UB933-Q1

THERMAL METRIC(1)

RTV (WQFN)

UNIT

32 PINS

RθJA

Junction-to-ambient thermal resistance

34.9

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

8.8

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

3.4

°C/W

RθJB

Junction-to-board thermal resistance

23.4

°C/W

ψJT

Junction-to-top characterization parameter

0.3

°C/W

ψJB

Junction-to-board characterization parameter

8.8

°C/W

(1)

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report (SPRA953).

6.5 Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.(1) (2) (3)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

LVCMOS DC SPECIFICATIONS 3.3 V I/O (SER INPUTS, GPIO, CONTROL INPUTS AND OUTPUTS)

VIH

High level input voltage

VIN = 3 V to 3.6 V

2

VIL

Low level input voltage

VIN = 3 V to 3.6 V

GND

IIN

Input current

VIN = 0 V or 3.6 V, VIN = 3 V to 3.6 V

VOH

High level output voltage V(VDDIO) = 3 V to 3.6 V, IOH = −4 mA

VOL

Low level output voltage V(VDDIO) = 3 V to 3.6 V, IOL = 4 mA

IOS

Output short-circuit

current

VOUT = 0 V

Serializer

GPO outputs

IOZ

Tri-state output current

PDB = 0 V,

VOUT = 0 V or V(VDDIO)

Serializer

GPO outputs

CGPO

Pin capacitance

GPO [3:0]

–20

VIN

±1

V

0.8

V

20

µA

2.4

V(VDDIO)

V

GND

0.4

V

–15

–20

mA

20

1.5

µA

pF

LVCMOS DC SPECIFICATIONS 1.8 V I/O (SER INPUTS, GPIO, CONTROL INPUTS AND OUTPUTS)

VIH

High level input voltage

VIN = 1.71 V to 1.89 V

0.65 VIN

VIN

VIL

Low level input voltage

VIN = 1.71 V to 1.89 V

GND

0.35 VIN

IIN

Input current

VIN = 0 V or 1.89 V, VIN = 1.71 V to 1.89 V

VOH

High level output voltage V(VDDIO) = 1.71 V to 1.89 V, IOH = −4 mA

VOL

Low level output voltage V(VDDIO) = 1.71 V to 1.89 V IOL = 4 mA

IOS

Output short-circuit

current

VOUT = 0 V

Serializer

GPO outputs

IOZ

Tri-state output current

PDB = 0 V,

VOUT = 0 V or V(VDDIO)

Serializer

GPO outputs

CGPO

Pin capacitance

GPO [3:0]

IIN_STRAP

Strap pin input current

VIN = 0 V to VDD_n

–20

±1

20

µA

V(VDDIO) –

0.45

V(VDDIO)

V

GND

0.45

V

–11

–20

mA

20

1.5

MODE, IDX

V

–1

µA

pF

1

µA

LVCMOS DC SPECIFICATIONS 2.8 V I/O (SER INPUTS, GPIO, CONTROL INPUTS AND OUTPUTS)

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

7

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

Over recommended operating supply and temperature ranges unless otherwise specified.(1) (2) (3)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

VIH

High level input voltage

VIN = 2.52 V to 3.08 V

0.7 VIN

VIN

VIL

Low level input voltage

VIN = 2.52 V to 3.08 V

GND

0.3 VIN

IIN

Input current

VIN = 0 V or 3.08 V, VIN = 2.52 V to 3.08 V

VOH

High level output voltage V(VDDIO) = 2.52 V to 3.08 V, IOH = −4 mA

VOL

Low level output voltage V(VDDIO) =2.52 V to 3.08V IOL = 4 mA

IOS

Output short-circuit

current

VOUT = 0 V

Serializer

GPO outputs

IOZ

Tri-state output current

PDB = 0 V,

VOUT = 0 V or V(VDDIO)

Serializer

GPO outputs

CGPO

Pin capacitance

GPO [3:0]

–20

±1

UNIT

V

20

µA

V(VDDIO) - 0.4

V(VDDIO)

V

GND

0.4

V

–11

–20

mA

20

1.5

µA

pF

CML DRIVER DC SPECIFICATIONS (DOUT+, DOUT–)

VOD

Differential output

voltage

RL = 100 Ω (Figure 6-6)

640

824

VOUT

Single-ended output

voltage

RL = 50 Ω (Figure 6-6)

320

412

ΔVOD

Differential output

voltage unbalance

RL = 100 Ω

VOS

Output offset voltage

RL = 100 Ω (Figure 6-6)

ΔVOS

Offset voltage unbalance RL = 100 Ω

IOS

Output short-circuit

current

DOUT+ = 0 V or DOUT– = 0 V

Differential internal

termination resistance

Differential across DOUT+ and DOUT–

80

100

120

Single-ended

termination resistance

DOUT+ or DOUT–

40

50

60

RT

VID-BC

VIN-BC

Back channel differential

input voltage

Back channel singleended input voltage

mV

1

50

V(VDD_n) –

(VOD /2)

1

mV

V

50

–26

mV

mA

Ω

260

mV

130

mV

Back Channel Frequency = 5.5 MHz(4)

SERIALIZER SUPPLY CURRENT

IDDT

IDDT

8

Serializer (Tx)

V(VDD_n) supply current

(includes load current)

Serializer (Tx)

V(VDD_n) supply current

(includes load current)

Submit Document Feedback

RL = 100 Ω

WORST CASE pattern

(Figure 6-2)

RL = 100 Ω

RANDOM PRBS-7

pattern

V(VDD_n) = 1.89 V

V(VDDIO) = 3.6 V

ƒ = 100 MHz, 12-bit

mode

Default registers

76

95

mA

V(VDD_n) = 1.89 V

V(VDDIO) = 3.6 V

ƒ = 75 MHz, 12-bit

mode

Default registers

61

80

mA

V(VDD_n) = 1.89 V

V(VDDIO) = 3.6 V

ƒ = 100 MHz, 12-bit

mode

Default Registers

80

V(VDD_n) = 1.89 V

V(VDDIO) = 3.6 V

ƒ = 75 MHz, 12-bit

mode

Default Registers

64

mA

Copyright © 2020 Texas Instruments Incorporated

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

Over recommended operating supply and temperature ranges unless otherwise specified.(1) (2) (3)

PARAMETER

I(VDDIO)T

IDDTZ

I(VDDIO)TZ

(1)

(2)

(3)

(4)

Serializer (Tx)

V(VDDIO) supply current

(includes load current)

TEST CONDITIONS

RL = 100 Ω

WORST CASE pattern

(Figure 6-2)

Serializer (Tx) supply

current power down

PDB = 0 V; All other

LVCMOS inputs = 0 V

Serializer (Tx) V(VDDIO)

supply current power

down

PDB = 0 V; All other

LVCMOS inputs = 0 V

TYP

MAX

V(VDDIO) = 1.89 V

ƒ = 75 MHz, 12-bit

mode

Default Registers

MIN

UNIT

1.5

3

V(VDDIO) = 3.6 V

ƒ = 75 MHz, 12-bit

mode

Default registers

5

8

V(VDDIO)=1.89 V

Default registers

300

1000

µA

V(VDDIO) = 3.6 V

Default registers

300

1000

µA

V(VDDIO) = 1.89 V

Default registers

15

100

µA

V(VDDIO) = 3.6 V

Default registers

15

100

µA

mA

The Electrical Characteristics tables list verified specifications under the listed Section 6.3 except as otherwise modified or specified by

the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not verified.

Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground

except VOD and ΔVOD which are differential voltages.

Typical values represent most likely parametric norms at 1.8 V or 3.3 V, TA = 25°C, and at the Section 6.3 at the time of product

characterization and are not verified.

The back channel frequency (MHz) listed is the frequency of the internal clock used to generate the encoded back channel data

stream. The data rate (Mbps) of the encoded back channel stream is the back channel frequency divided by 2.

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

9

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

6.6 Recommended Serializer Timing For PCLK

Over recommended operating supply and temperature ranges unless otherwise specified.(1) (2)

PARAMETER

tTCP

Transmit clock period

TEST CONDITIONS

PIN / FREQ

10-bit mode

50 MHz – 100 MHz

12-bit mode

37.5 MHz - 100 MHz

MIN

NOM

MAX

7.52

T

20

ns

10

T

26.67

ns

tTCIH

Transmit clock

input high time

0.4T

0.5T

0.6T

tTCIL

Transmit clock

input low time

0.4T

0.5T

0.6T

10-bit mode

50 MHz – 100 MHz

0.05T

0.25T

0.3T

tCLKT

PCLK input transition time

(Figure 6-7)

12-bit mode

37.5 MHz – 100 MHz

0.05T

0.25T

0.3T

tJIT0

PCLK input jitter (3)

(PCLK from imager mode)

LPF = ƒ/20, CDR PLL Loop BW = ƒPCLK = 37.5

ƒ/15, BER = 1E-10

– 100 MHz(5)

tJIT1

PCLK input jitter(3)

(External oscillator mode)

LPF = ƒ/20, CDR PLL Loop BW = ƒPCLK = 37.5

ƒ/15, BER = 1E-10

– 100 MHz(5)

tJIT2

LPF = ƒ/20, CDR PLL Loop BW = ƒOSC = 25 –

External oscillator jitter(3) (4) ƒ/15, BER = 1E-10, paired with

66.67 MHz(6)

DS90UB934-Q1 deserializer

ΔOSC

External Oscillator

Frequency Stability

ƒOSC = 25 –

66.67 MHz(6)

tDC

CLKOUT duty cycle

(external oscillator mode)

ƒOSC = 25 –

66.67 MHz(6)

(1)

(2)

(3)

(4)

(5)

(6)

10

UNIT

0.45

UI

0.45

UI

1T

±50

45%

50%

ppm

55%

Recommended input timing requirements are input specifications and not tested in production.

T is the period of the PCLK.

Typical values represent most likely parametric norms at 1.8 V or 3.3 V, TA = 25°C, and at Section 6.3 at the time of product

characterization and are not verified.

0.45UI maximum when used with DS90UB934-Q1 deserializer. When used with DS90UB914A-Q1 deserializer, the maximum is 0.3UI.

ƒPCLK denotes input PCLK frequency to the device.

ƒOSC denotes input external oscillator frequency to the device (GPO3/CLKIN).

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

6.7 AC Timing Specifications (SCL, SDA) - I2C-Compatible

Over recommended supply and temperature ranges unless otherwise specified. (Figure 6-1)

PARAMETER

TEST CONDITIONS

MIN

NOM

MAX

UNIT

100

kHz

400

kHz

RECOMMENDED INPUT TIMING REQUIREMENTS

ƒSCL

Standard mode

SCL Clock Frequency

tLOW

Fast mode

SCL Low Period

tHIGH

SCL high period

Standard mode

4.7

µs

Fast mode

1.3

µs

Standard mode

4.0

µs

Fast mode

0.6

µs

Standard mode

4.0

µs

tHD:STA

Hold time for a start or a repeated start

condition

0.6

µs

tSU:STA

Setup time for a start or a repeated start Standard mode

condition

Fast mode

4.7

µs

0.6

µs

tHD:DAT

Data hold time

Standard mode

0

3.45

µs

Fast mode

0

900

ns

tSU:DAT

Data setup time

tSU:STO

Setup time for stop condition

tBUF

Bus free time between stop and start

tr

SCL and SDA rise time

tf

SCL and SDA fall time

Fast mode

Standard mode

250

ns

Fast mode

100

ns

Standard mode

4.0

µs

Fast mode

0.6

µs

Standard mode

4.7

µs

Fast mode

1.3

µs

Standard mode

1000

ns

Fast mode

300

ns

Standard mode

300

ns

Fast mode

300

ns

6.8 Bidirectional Control Bus DC Timing Specifications (SCL, SDA) - I2C-Compatible

Over recommended supply and temperature ranges unless otherwise specified(1)

PARAMETER

TEST CONDITIONS

MIN

NOM

MAX

UNIT

RECOMMENDED INPUT TIMING REQUIREMENTS

VIH

Input high level

SDA and SCL

0.7 × V(VDDIO)

VIL

Input low level

SDA and SCL

GND

VHY

Input hysteresis

VOL

Output low level(2)

IIN

Input current

tR

SDA rise time-READ

tF

SDA fall time-READ

CIN

(1)

(2)

V(VDDIO)

0.3 × V(VDDIO)

> 50

SDA, V(VDDIO) = 1.8 V, IOL= 0.9 mA

0

0.36

0

0.4

SDA, RPU = 10 kΩ, Cb ≤ 400 pF

(Figure 6-1)

SDA or SCL

−10

V

mV

SDA, V(VDDIO) = 3.3 V, IOL= 1.6 mA

SDA or SCL, VIN= V(VDDIO) OR GND

V

10

430

V

µA

ns

20

ns

10ms after the power

sequence is complete (V PDB > PDB V IH) with no delay between write commands. This step will cause a brief

restart of the forward channel output:

•

•

•

Write Register 0x27 = 0x28

Write Register 0x27 = 0x20

Write Register 0x27 = 0x00

8.1.3 AC Coupling

The SER/DES supports only AC-coupled interconnects through an integrated DC-balanced decoding scheme.

External AC-coupling capacitors must be placed in series in the FPD-Link III signal path as shown in Figure 8-2.

For applications utilizing single-ended 50-Ω coaxial cable, the unused data pin (DOUT–, RIN–) must utilize a

0.047-µF capacitor and must be terminated with a 50-Ω resistor. For high-speed FPD–Link III transmissions, the

smallest available package should be used for the AC-coupling capacitor. This helps minimize degradation of

signal quality due to package parasitics.

DOUT+

RIN+

DOUT-

RIN-

SER

DES

Copyright © 2016, Texas Instruments Incorporated

Figure 8-2. AC-Coupled Connection (STP)

DOUT+

RIN+

SER

DES

DOUT-

50Q

50Q

RIN-

Copyright © 2016, Texas Instruments Incorporated

Figure 8-3. AC-Coupled Connection (Coaxial)

8.1.4 Transmission Media

The DS90UB933/934/964 chipset is intended to be used in a point-to-point configuration through a shielded

coaxial cable. The serializer and deserializer provide internal termination to minimize impedance discontinuities.

The interconnect (cable and connectors) must have a differential impedance of 100 Ω, or a single-ended

impedance of 50 Ω. The maximum length of cable that can be used is dependent on the quality of the cable

(gauge, impedance), connector, board(discontinuities, power plane), the electrical environment (for example,

power stability, ground noise, input clock jitter, PCLK frequency, etc.). The resulting signal quality at the receiving

end of the transmission media may be assessed by monitoring the differential eye opening of the serial data

stream. A differential probe should be used to measure across the termination resistor at the CMLOUTP/N pins.

38

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

�DS90UB933-Q1

www.ti.com

SNLS546E – AUGUST 2016 – REVISED NOVEMBER 2020

Contact TI for a channel specification regarding cable loss parameters and further details on adaptive equalizer

loss compensation.

8.2 Typical Applications

8.2.1 Coax Application

DS90UB933-Q1

VDDIO

VDDIO

C8

1.8 V

VDDT

C3

C4

C13

C9

1.8 V

DIN0

DIN1

DIN2

DIN3

DIN4

DIN5

DIN6

LVCMOS

Parallel

Bus

DIN7

DIN8

DIN9

DIN10

DIN11

HS

VS

PCLK

1.8 V

VDDPLL

C5

FB1

1.8 V

VDDCML

C6

C11

C15

C7

C12

FB2

1.8 V

VDDD

C1

Serial

FPD-Link III

Interface

DOUT+

DOUTC2

1.8 V

R1

VDDIO

C14

C10

RTERM

MODE

R2

R3

10 kQ

ID[X]

PDB

R4

C18

GPO[0]

GPO[1]

GPO[2]

GPO[3]

GPO

Control

Interface

RPD

VDDIO

RPU

I2C

Bus

Interface

RPU

SCL

FB3

SDA

FB4

C16

C17

Optional

Optional

RES

DAP (GND)

NOTE:

C1 = 0.1 µF (50 WV)

C2 = 0.047 µF (50 WV)

C3:C7 = 0.01 µF

C8:C12 = 0.1 µF

C13, C14 = 4.7 µF

C15 = 22 µF

C16 - C17 = >100 pF

C18 = 1 µF

RTERM = 50 Ÿ

RPU = 1 kŸ to 4.7 kŸ

RPD minimum =40 kŸ

R1, R2 (see MODE Setting Table)

R3, R4 (see ID[x] Setting Table)

FB1:FB4: Impedance = 1 kŸ (@ 100 MHz)

low DC resistance (100 pF

C18 = 1 µF

RPU = 1 kŸ to 4.7 kŸ

RPD minimum =40 kŸ

R1, R2 (see MODE Setting Table)

R3, R4 (see ID[x] Setting Table)

FB1:FB4: Impedance = 1 kŸ (@ 100 MHz)

low DC resistance (