LM25184-Q1

LM25184-Q1

SNVSBJ6A – MARCH 2020 – REVISED

AUGUST 2020

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

www.ti.com

LM25184-Q1 42-VIN PSR Flyback DC/DC Converter with 65-V, 4.1-A MOSFET

1 Features

3 Description

•

The LM25184-Q1 is a primary-side regulated (PSR)

flyback converter with high efficiency over a wide

input voltage range of 4.5 V to 42 V. The isolated

output voltage is sampled from the primary-side

flyback voltage. The high level of integration results in

a simple, reliable, and high-density design with only

one component crossing the isolation barrier.

Boundary conduction mode (BCM) switching enables

a compact magnetic solution and better than ±1.5%

load and line regulation performance. An integrated

65-V power MOSFET provides output power up to 15

W with enhanced headroom for line transients.

•

•

•

•

•

•

AEC-Q100-qualified for automotive applications

– Device temperature grade 1: –40°C to 125°C

ambient temperature range

Functional Safety-Capable

– Documentation available to aid functional safety

system design

Designed for reliable and rugged applications

– Wide input voltage range of 4.5 V to 42 V

– Robust solution with only one component

crossing the isolation barrier

– ±1.5% total output regulation accuracy

– Optional VOUT temperature compensation

– –40°C to +150°C junction temperature range

Integration reduces solution size and cost

– Integrated 65-V, 0.11-Ω power MOSFET

– No optocoupler or transformer auxiliary winding

required for VOUT regulation

High-efficiency PSR flyback operation

– Quasi-resonant MOSFET turnoff in BCM

– Single- and multi-output implementations

Ultra-low conducted and radiated EMI signatures

– Soft switching avoids diode reverse recovery

– Optimized for CISPR 25 Class 5 requirement

Create a custom flyback regulator design using

WEBENCH® Power Designer

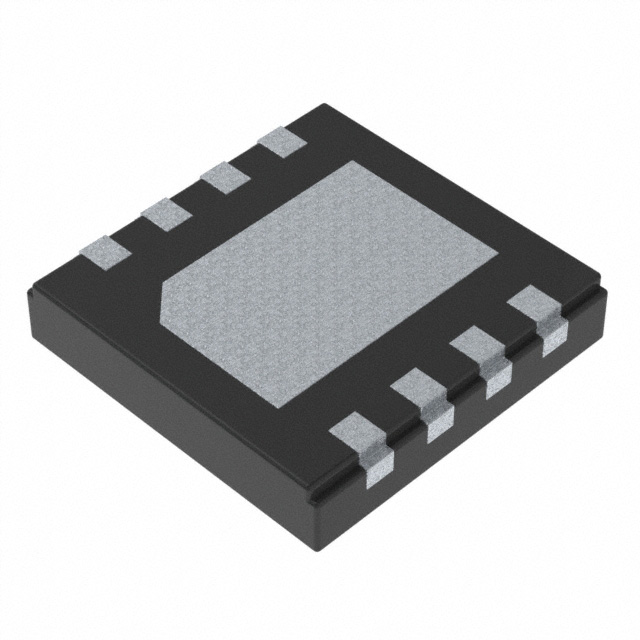

The LM25184-Q1 converter is qualified to automotive

AEC-Q100 grade 1 and is available in 8-pin WSON

package with 0.8-mm pin pitch and wettable flanks.

Device Information

2 Applications

•

•

•

The LM25184-Q1 simplifies the implementation of

isolated DC/DC supplies with optional features to

optimize performance for the target end equipment.

The output voltage is set by one resistor, while an

optional resistor improves output voltage accuracy by

negating the thermal coefficient of the flyback diode

voltage drop. Additional features include an internallyfixed or externally-programmable soft-start, precision

enable input with hysteresis for adjustable line UVLO,

hiccup-mode overload protection, and thermal

shutdown protection with automatic recovery.

PART NUMBER (1)

Automotive HEV/EV powertrain systems

Sub-AM band automotive body electronics

Traction inverter: IGBT and SiC driver supplies

VIN = 4.5 V...42 V

T1

DFLY

LM25184-Q1

(1)

PACKAGE

WSON (8)

BODY SIZE (NOM)

4.00 mm × 4.00 mm

For all available packages, see the orderable addendum at

the end of the data sheet.

95

VOUT = 12 V

90

CIN

COUT

47 F

1:1

DF

VIN

10 F

EN/UVLO

SW

LM25184-Q1

RFB

124 k:

FB

GND

80

75

70

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

65

60

RSET

RSET

SS/BIAS

85

Efficiency (%)

DZ

12.1 k:

TC

0

200

400

600

800

Load Current (mA)

1000

1200

D001

Typical Efficiency, VOUT = 12 V

Typical Application

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

Submit Document Feedback

Copyright

© 2020 Texas

Instruments

Incorporated

intellectual

property

matters

and other important disclaimers. PRODUCTION DATA.

Product Folder Links: LM25184-Q1

1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Pin Configuration and Functions...................................3

Pin Functions.................................................................... 3

6 Specifications.................................................................. 4

6.1 Absolute Maximum Ratings ....................................... 4

6.2 ESD Ratings .............................................................. 4

6.3 Recommended Operating Conditions ........................4

6.4 Thermal Information ...................................................4

6.5 Electrical Characteristics ............................................5

6.6 Typical Characteristics................................................ 6

7 Detailed Description........................................................9

7.1 Overview..................................................................... 9

7.2 Functional Block Diagram........................................... 9

7.3 Feature Description.....................................................9

7.4 Device Functional Modes..........................................15

8 Application and Implementation.................................. 16

8.1 Application Information............................................. 16

8.2 Typical Applications.................................................. 16

9 Power Supply Recommendations................................31

10 Layout...........................................................................32

10.1 Layout Guidelines................................................... 32

10.2 Layout Examples.................................................... 33

11 Device and Documentation Support..........................34

11.1 Device Support........................................................34

11.2 Documentation Support.......................................... 35

11.3 Receiving Notification of Documentation Updates.. 35

11.4 Support Resources................................................. 35

11.5 Trademarks............................................................. 35

11.6 Electrostatic Discharge Caution.............................. 36

11.7 Glossary.................................................................. 36

12 Mechanical, Packaging, and Orderable

Information.................................................................... 37

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision * (March 2020) to Revision A (August 2020)

Page

• Changed device status from Advance Information to Production Data.............................................................. 1

• Updated the numbering format for tables, figures and cross-references throughout the document...................1

2

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

5 Pin Configuration and Functions

SW

1

8

GND

FB

2

7

RSET

VIN

3

6

TC

EN/UVLO

4

5

SS/BIAS

Figure 5-1. 8-Pin WSON NGU Package With Wettable Flanks (Top View)

Pin Functions

PIN

NO.

NAME

I/O(1)

DESCRIPTION

1

SW

P

Switch node that is internally connected to the drain of the N-channel power MOSFET. Connect to

the primary-side switching terminal of the flyback transformer.

2

FB

I

Primary-side feedback pin. Connect a resistor from FB to SW. The ratio of the FB resistor to the

resistor at the RSET pin sets the output voltage.

3

VIN

P/I

Input supply connection. Source for internal bias regulators and input voltage sensing pin.

Connect directly to the input supply of the converter with short, low impedance paths.

4

EN/UVLO

I

Enable input and undervoltage lockout (UVLO) programming pin. If the EN/UVLO voltage is below

1 V, the converter is in shutdown mode with all functions disabled. If the EN/UVLO voltage is

greater than 1 V and below 1.5 V, the converter is in standby mode with the internal regulator

operational and no switching. If the EN/UVLO voltage is above 1.5 V, the start-up sequence

begins.

5

SS/BIAS

I

Soft start or bias input. Connect a capacitor from SS/BIAS to GND to adjust the output start-up

time and input inrush current. If SS/BIAS is left open, the internal 6-ms soft-start timer is activated.

Connect an external supply to SS/BIAS to supply bias to the internal voltage regulator and enable

internal soft start.

6

TC

I

Temperature compensation pin. Tie a resistor from TC to RSET to compensate for the

temperature coefficient of the forward voltage drop of the secondary diode, thus improving

regulation at the secondary-side output.

7

RSET

I

Reference resistor tied to GND to set the reference current for FB. Connect a 12.1-kΩ resistor

from RSET to GND.

8

GND

G

Analog and power ground. Ground connection of internal control circuits and power MOSFET.

(1)

P = Power, G = Ground, I = Input, O = Output

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

3

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

6 Specifications

6.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted)(1)

MIN

Input voltage

Output voltage

MAX

VIN to GND

–0.3

45

EN/UVLO to GND

–0.3

45

TC to GND

–0.3

6

SS/BIAS to GND

–0.3

14

FB to GND

–0.3

45.3

FB to VIN

–0.3

0.3

RSET to GND

–0.3

3

SW to GND

–1.5

70

SW to GND (20-ns transient)

–3

UNIT

V

V

Operating junction temperature, TJ

–40

150

°C

Storage temperature, Tstg

–55

150

°C

(1)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under

Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

6.2 ESD Ratings

VALUE

Human body model (HBM), per AEC Q100-002

HBM ESD Classification Level 2 (1)

V(ESD)

(1)

Electrostatic discharge

Charged device model (CDM), per

AEC Q100-011

CDM ESD Classification Level C4B

UNIT

±2000

All pins except 1, 4,

5, and 8

±500

Pins 1, 4, 5, and 8

±750

V

AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted)

MIN

VIN

Input voltage

VSW

VEN/UVLO

VSS/BIAS

SS/BIAS voltage

TJ

Operating junction temperature

NOM

MAX

4.5

UNIT

42

V

SW voltage

65

V

EN/UVLO voltage

42

V

–40

13

V

150

°C

6.4 Thermal Information

LM25184-Q1

THERMAL

METRIC(1)

NGU (WSON)

UNIT

8 PINS

RΘJA

Junction-to-ambient thermal resistance

40.9

°C/W

RΘJC(top)

Junction-to-case (top) thermal resistance

36.9

°C/W

RΘJB

Junction-to-board thermal resistance

17.7

°C/W

ΨJT

Junction-to-top characterization parameter

0.4

°C/W

ΨJB

Junction-to-board characterization parameter

17.7

°C/W

RΘJC(bot)

Junction-to-case (bottom) thermal resistance

2.7

°C/W

(1)

4

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics report.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

6.5 Electrical Characteristics

Typical values correspond to TJ = 25°C. Minimum and maximum limits aaply over the full –40°C to 150°C

junction temperature range unless otherwise indicated. VIN = 12 V and VEN/UVLO = 2 V unless otherwise stated.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

SUPPLY CURRENT

ISHUTDOWN

VIN shutdown current

VEN/UVLO = 0 V

1.8

IACTIVE

VIN active current

VEN/UVLO = 2.5 V, VRSET = 1.8 V

260

375

µA

µA

IACTIVE-BIAS

VIN current with BIAS connected

VSS/BIAS = 5 V

25

50

µA

0.8

1

V

1.53

V

ENABLE AND INPUT UVLO

VSD-FALLING

Shutdown threshold

VEN/UVLO falling

VSD-RISING

Standby threshold

VEN/UVLO rising

0.3

V

VUV-RISING

Enable threshold

VEN/UVLO rising

1.45

1.5

VUV-HYST

Enable voltage hysteresis

VEN/UVLO falling

0.04

0.05

IUV-HYST

Enable current hysteresis

VEN/UVLO = 1.6 V

4.2

5

1.194

1.21

V

5.5

µA

FEEDBACK

IRSET

RSET current

RRSET = 12.1 kΩ

VRSET

RSET regulation voltage

RRSET = 12.1 kΩ

VFB-VIN1

FB to VIN voltage

IFB = 80 µA

VFB-VIN2

FB to VIN voltage

IFB = 120 µA

100

µA

1.22

–50

V

mV

50

mV

SWITCHING FREQUENCY

FSW-MIN

Minimum switching frequency

12

kHz

FSW-MAX

tON-MIN

Maximum switching frequency

350

kHz

Minimum switch on-time

140

ns

DIODE THERMAL COMPENSATION

VTC

TC voltage

ITC = ±10 µA, TJ = 25°C

1.2

1.27

V

ISW = 100 mA, TJ = 25°C

0.11

0.135

Ω

POWER SWITCHES

RDS(on)

MOSFET on-state resistance

SOFT-START AND BIAS

ISS

SS ext capacitor charging current

5

µA

tSS

Internal SS time

6

ms

VBIAS-UVLO-

BIAS enable voltage

VSS/BIAS rising

4.25

BIAS UVLO hysteresis

VSS/BIAS falling

130

RISE

VBIAS-UVLOHYST

4.45

V

mV

CURRENT LIMIT

ISW-PEAK

Peak current limit threshold

3.6

4.1

4.4

A

THERMAL SHUTDOWN

TSD

Thermal shutdown threshold

TSD-HYS

Thermal shutdown hysteresis

TJ rising

175

°C

10

°C

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

5

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

6.6 Typical Characteristics

VIN = 24 V, VEN/UVLO = 2 V (unless otherwise stated).

95

12.6

90

12.4

Output Voltage (V)

Efficiency (%)

85

80

75

70

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

65

200

400

600

800

Load Current (mA)

1000

12

11.8

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

11.6

11.4

60

0

12.2

1200

0

200

400

600

800 1000

Load Current (mA)

1400

1600

D003

See Figure 8-1

See Figure 8-1

Figure 6-1. Efficiency versus Load

VSW 10 V/div

Figure 6-2. Output Voltage versus Load

VSW 10 V/div

1 Ps/div

1 Ps/div

See Figure 8-1

1200

D001

VIN = 13.5 V, IOUT = 1 A

Figure 6-3. Switching Waveform in BCM

See Figure 8-1

VIN = 13.5 V, IOUT = 0.5 A

Figure 6-4. Switching Waveform in DCM

VOUT 2 V/div

VOUT 2 V/div

IOUT 0.2 A/div

IOUT 0.2 A/div

VEN/UVLO 10 V/div

VIN 10 V/div

4 ms/div

4 ms/div

See Figure 8-1

See Figure 8-1

Figure 6-5. Start-up Characteristic

6

Figure 6-6. ENABLE ON/OFF Characteristic

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

102

104

101

102

RSET Current (PA)

RSET Current (PA)

www.ti.com

100

99

98

98

0

6

12

18

24

Input Voltage (V)

30

36

96

-50

42

EN/UVLO Threshold Voltage (V)

TC Voltage (V)

25

50

75

100

Junction Temperature (qC)

125

150

D005

1.54

1.6

1.4

1.2

1

-25

0

25

50

75

100

Junction Temperature (qC)

125

1.52

1.5

1.48

1.46

1.44

1.42

1.4

-50

150

VEN/UVLO Rising

VEN/UVLO Falling

-25

0

25

50

75

100

Junction Temperature (qC)

125

Figure 6-10. EN/UVLO Threshold Voltages versus

Temperature

160

5.2

155

Minimum on-time (ns)

5.3

5.1

5

4.9

4.8

150

D007

D006

Figure 6-9. TC Voltage versus Temperature

4.7

-50

0

Figure 6-8. RSET Current versus Temperature

1.8

0.8

-50

-25

D004

Figure 6-7. RSET Current versus Input Voltage

EN/UVLO Hysteresis Current (PA)

100

150

145

140

135

-25

0

25

50

75

100

Junction Temperature (qC)

125

150

130

-50

-25

D008

Figure 6-11. EN/UVLO Hysteresis Current versus

Temperature

0

25

50

75

100

Junction Temperature (qC)

125

150

D011

Figure 6-12. Minimum Switch On-Time versus

Temperature

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

7

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

380

Max. Switching Frequency (kHz)

Min. Switching Frequency (kHz)

13

12.5

12

11.5

11

-50

-25

0

25

50

75

100

Junction Temperature (qC)

125

150

360

350

340

330

320

-50

-25

D012

Figure 6-13. Minimum Switching Frequency versus

Temperature

8

370

0

25

50

75

100

Junction Temperature (qC)

125

150

D013

Figure 6-14. Maximum Switching Frequency

versus Temperature

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

7 Detailed Description

7.1 Overview

The LM25184-Q1 primary-side regulated (PSR) flyback converter is a high-density, cost-effective solution for

automotive and industrial systems requiring less than 15 W of isolated DC/DC power. This compact, easy-to-use

flyback converter with low IQ can be applied over a wide input voltage range from 4.5 V to 42 V, with operation

down to 3.5 V after start-up. Innovative frequency and current amplitude modulation enables high conversion

efficiency across the entire load and line range. Primary-side regulation of the isolated output voltage using

sampled values of the primary winding voltage eliminates the need for an opto-coupler or an auxiliary

transformer winding for feedback. Regulation performance that rivals that of traditional opto-coupler solutions is

achieved without the associated cost, solution size, and reliability concerns. The LM25184-Q1 converter services

a wide range of applications including automotive on-board chargers and IGBT-based motor drives for HEV/EV

systems.

7.2 Functional Block Diagram

VIN

NP : NS

CIN

EN/UVLO

DZ

LM25184-Q1

5 PA

BIAS

REGULATOR

Standby

1.5 V

1.45 V

DFLY

VOUT

COUT

SS/BIAS

VDD

VIN

VDD UVLO

Shutdown

DF

SAMPLED

FEEDBACK

1.1 V

VIN

THERMAL

SHUTDOWN

FB

65-V Power

MOSFET

RSET

gm

COMP

SW

VDD

VREF

TRIMMED

REFERENCE

RTC

CONTROL

LOGIC

RSET

FB

ILIM

TC

4.1 A

TC

REGULATION

VDD

GND

RFB

SS/BIAS

Internal SS

CSS

7.3 Feature Description

7.3.1 Integrated Power MOSFET

The LM25184-Q1 is a flyback dc/dc converter with integrated 65-V, 4.1-A N-channel power MOSFET. During the

MOSFET on-time, the transformer primary current increases from zero with a slope of VIN / LMAG (where LMAG is

the transformer primary-referred magnetizing inductance) while the output capacitor supplies the load current.

When the high-side MOSFET is turned off by the control logic, the switch (SW) voltage VSW swings up to

approximately VIN + (NPS × VOUT), where NPS = NP/NS is the primary-to-secondary turns ratio of the transformer.

The magnetizing current flows in the secondary side through the flyback diode, charging the output capacitor

and supplying current to the load. Duty cycle D is defined as tON / tSW, where tON is the MOSFET conduction

time and tSW is the switching period.

Figure 7-1 shows a typical schematic of the LM25184-Q1 PSR flyback circuit. Components denoted in red are

optional depending on the application requirements.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

9

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

T1

DFLY

VIN

VOUT

DCLAMP

COUT

RUV1

CIN

EN/UVLO

RUV2

NP : NS

DF

VIN

DOUT

SW

RFB

LM25184

FB

GND

RSET

SS/BIAS

CSS

RTC

RSET

TC

Figure 7-1. LM25184-Q1 Flyback Converter Schematic (Optional Components in Red)

7.3.2 PSR Flyback Modes of Operation

The LM25184-Q1 uses a variable-frequency, peak current-mode (VFPCM) control architecture with three

possible modes of operation as illustrated in Figure 7-2.

Frequency

foldback mode

(FFM)

Discontinuous conduction mode (DCM)

Boundary conduction mode (BCM)

400

Switching Frquency (kHz)

350

300

250

200

150

100

50

0

0

20

40

60

80

100

% Total Rated Output Power

Figure 7-2. Three Modes of Operation Illustrated by Variation of Switching Frequency With Load

The LM25184-Q1 operates in boundary conduction mode (BCM) at heavy loads. The power MOSFET turns on

when the current in the secondary winding reaches zero, and the MOSFET turns off when the peak primary

current reaches the level dictated by the output of the internal error amplifier. As the load is decreased, the

frequency increases to maintain BCM operation. Equation 1 gives the duty cycle of the flyback converter in BCM.

10

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

VOUT

D

VIN

VD ˜ NPS

VOUT

VD ˜ NPS

(1)

where

•

VD is the forward voltage drop of the flyback diode as its current approaches zero

Equation 2 gives the output power in BCM, where the applicable switching frequency and peak primary current

are specified by Equation 3 and Equation 4, respectively.

LMAG ˜ IPRI-PK(BCM)

POUT(BCM)

FSW(BCM)

2

˜ FSW(BCM)

2

(2)

1

§L

IPRI-PK(BCM) ˜ ¨ MAG

¨ VIN

©

IPRI-PK(BCM)

2 ˜ VOUT

LMAG

NPS ˜ VOUT

VD

·

¸¸

¹

(3)

VD ˜ IOUT

VIN ˜ D

(4)

As the load decreases, the LM25184-Q1 clamps the maximum switching frequency to 350 kHz, and the

converter enters discontinuous conduction mode (DCM). The power delivered to the output in DCM is

proportional to the peak primary current squared as given by Equation 5 and Equation 6. Thus, as the load

decreases, the peak current reduces to maintain regulation at 350-kHz switching frequency.

POUT(DCM)

IPRI-PK(DCM)

DDCM

LMAG ˜ IPRI-PK(DCM)

2

2

2 ˜ IOUT ˜ VOUT

˜ FSW(DCM)

(5)

VD

LMAG ˜ FSW(DCM)

(6)

LMAG ˜ IPRI-PK(DCM) ˜ FSW(DCM)

VIN

(7)

At even lighter loads, the primary-side peak current set by the internal error amplifier decreases to a minimum

level of 0.82 A, or 20% of its 4.1-A peak value, and the MOSFET off-time extends to maintain the output load

requirement. The system operates in frequency foldback mode (FFM), and the switching frequency decreases

as the load current is reduced. Other than a fault condition, the lowest frequency of operation of the LM25184Q1 is 12 kHz, which sets a minimum load requirement of approximately 0.5% full load.

7.3.3 Setting the Output Voltage

To minimize output voltage regulation error, the LM25184-Q1 senses the reflected secondary voltage when the

secondary current reaches zero. The feedback (FB) resistor, which is connected between SW and FB is

determined using Equation 8, where RSET is nominally 12.1 kΩ.

RFB

VOUT

VD ˜ NPS ˜

RSET

VREF

(8)

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

11

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

7.3.3.1 Diode Thermal Compensation

The LM25184-Q1 employs a unique thermal compensation circuit that adjusts the feedback setpoint based on

the thermal coefficient of the forward voltage drop of the flyback diode. Even though the output voltage is

measured when the secondary current is effectively zero, there is still a non-zero forward voltage drop

associated with the flyback diode. Select the thermal compensation resistor using Equation 9.

RTC ª¬k: º¼

RFB ¬ªk: ¼º

NPS

˜

3

TCDiode ª¬mV qC º¼

(9)

The temperature coefficient of the diode voltage drop may not be explicitly provided in the diode data sheet, so

the effective value can be estimated based on the measured output voltage shift over temperature when the TC

resistor is not installed.

7.3.4 Control Loop Error Amplifier

The inputs of the error amplifier include a level-shifted version of the FB voltage and an internal 1.21-V reference

set by the resistor at RSET. A type-2 internal compensation network stabilizes the converter. In BCM operation

when the output voltage is in regulation, an on-time interval is initiated when the secondary current reaches zero.

The power MOSFET is subsequently turned off when an amplified version of the peak primary current exceeds

the error amplifier output.

7.3.5 Precision Enable

The precision EN/UVLO input supports adjustable input undervoltage lockout (UVLO) with hysteresis for

application specific power-up and power-down requirements. EN/UVLO connects to a comparator with a 1.5-V

reference voltage and 50-mV hysteresis. An external logic signal can be used to drive the EN/UVLO input to

toggle the output on and off for system sequencing or protection. The simplest way to enable the LM25184-Q1 is

to connect EN/UVLO directly to VIN. This allows the LM25184-Q1 to start up when VIN is within its valid operating

range. However, many applications benefit from using resistor divider RUV1 and RUV2 as shown in Figure 7-3 to

establish a precision UVLO level.

LM25184

VCC

VIN

5 A

RUV1

EN/UVLO

+

RUV2

1.5 V

1.45 V

UVLO

Comparator

Figure 7-3. Programmable Input Voltage UVLO With Hysteresis

12

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

Use Equation 10 and Equation 11 to calculate the input UVLO voltages turnon and turnoff voltages, respectively.

VIN(on)

VIN(off)

§

RUV1 ·

VUV-RISING ¨ 1

¸

© RUV2 ¹

(10)

§

RUV1 ·

VUV-FALLING ¨ 1

¸ IUV-HYST ˜ RUV1

© RUV2 ¹

(11)

where

•

•

VUV-RISING and VUV-FALLING are the UVLO comparator thresholds

IUV-HYST is the hysteresis current

The LM25184-Q1 also provides a low-IQ shutdown mode when the EN/UVLO voltage is pulled below a baseemitter voltage drop (approximately 0.6 V at room temperature). If the EN/UVLO voltage is below this hard

shutdown threshold, the internal LDO regulator powers off, and the internal bias-supply rail collapses, shutting

down the bias currents of the LM25184-Q1. The LM25184-Q1 operates in standby mode when the EN/UVLO

voltage is between the hard shutdown and precision-enable thresholds.

7.3.6 Configurable Soft Start

The LM25184-Q1 has a flexible and easy-to-use soft-start control pin, SS/BIAS. The soft-start feature prevents

inrush current impacting the LM25184-Q1 and the input supply when power is first applied. This is achieved by

controlling the voltage at the output of the internal error amplifier. Soft start is achieved by slowly ramping up the

target regulation voltage when the device is first enabled or powered up. Selectable and adjustable start-up

timing options include a 6-ms internally-fixed soft start and an externally-programmable soft start.

The simplest way to use the LM25184-Q1 is to leave SS/BIAS open. The LM25184-Q1 employs an internal softstart control ramp and starts up to the regulated output voltage in 6 ms.

However, in applications with a large amount of output capacitance, higher VOUT, or other special requirements,

the soft-start time can be extended by connecting an external capacitor CSS from SS/BIAS to GND. A longer

soft-start time further reduces the supply current needed to charge the output capacitors while sourcing the

required load current. When the EN/UVLO voltage exceeds the UVLO rising threshold and a delay of 20 µs

expires, an internal current source ISS of 5 µA charges CSS and generates a ramp to control the primary current

amplitude. Calculate the soft-start capacitance for a desired soft-start time, tSS, using Equation 12.

CSS ¬ªnF ¼º

5 ˜ t SS ¬ªms ¼º

(12)

CSS is discharged by an internal FET when switching is disabled by EN/UVLO or thermal shutdown.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

13

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

7.3.7 External Bias Supply

DFLY

T1

VIN

VOUT

DCLAMP

COUT

RUV1

CIN

DF

VIN

EN/UVLO

RUV2

RSET

NP : NS

SW

RFB

LM25184

GND

FB

DBIAS1

SS/BIAS

DBIAS2

RSET

TC

DOUT

12 V

CBIAS

22 nF

NP : NAUX

Figure 7-4. External Bias Supply Using Transformer Auxiliary Winding

The LM25184-Q1 has an external bias supply feature that reduces input quiescent current and increases

efficiency. When the voltage at SS/BIAS exceeds a rising threshold of 4.25 V, bias power for the internal LDO

regulator can be derived from an external voltage source or from a transformer auxiliary winding as shown in

Figure 7-4. With a bias supply connected, the LM25184-Q1 then uses its internal soft-start ramp to control the

primary current during start-up.

When using a transformer auxiliary winding for bias power, the total leakage current related to diodes DBIAS1 and

DBIAS2 in Figure 7-4 must be less than 1 µA across the full operating temperature range.

7.3.8 Minimum On-Time and Off-Time

When the internal power MOSFET is turned off, the leakage inductance of the transformer resonates with the

SW node parasitic capacitance. The resultant ringing behavior can be excessive with large transformer leakage

inductance and can corrupt the secondary zero-current detection. To prevent such a situation, a minimum switch

off-time, designated as tOFF-MIN, of a maximum of 425 ns is set internally to ensure proper functionality. This sets

a lower limit for the transformer magnetizing inductance as discussed in Section 8.2.1.2.

Furthermore, noise effects as a result of power MOSFET turnon can impact the internal current sense circuit

measurement. To mitigate this effect, the LM25184-Q1 provides a blanking time after the MOSFET turns on.

This blanking time forces a minimum on-time, tON-MIN, of 140 ns.

7.3.9 Overcurrent Protection

In case of an overcurrent condition on the isolated output or outputs, the output voltage drops lower than the

regulation level since the maximum power delivered is limited by the peak current capability on the primary side.

The peak primary current is maintained at 4.1 A (plus an amount related to the 100-ns propagation delay of the

current limit comparator) until the output decreases to the secondary diode voltage drop to impact the reflected

signal on the primary side. At this point, the LM25184-Q1 assumes the output cannot be recovered and recalibrates its switching frequency to 9 kHz until the overload condition is removed. The LM25184-Q1 responds

with similar behavior to an output short circuit condition.

For a given input voltage, Equation 13 gives the maximum output current prior to the engagement of overcurrent

protection. The typical threshold value for ISW-PEAK from Section 6.5 is 4.1 A.

14

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

IOUT(max)

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

K

˜

ISW-PEAK

2 § VOUT

¨

© VIN

1 ·

¸

NPS ¹

(13)

7.3.10 Thermal Shutdown

Thermal shutdown is an integrated self-protection to limit junction temperature and prevent damage related to

overheating. Thermal shutdown turns off the device when the junction temperature exceeds 175°C to prevent

further power dissipation and temperature rise. Junction temperature decreases after shutdown, and the

LM25184-Q1 restarts when the junction temperature falls to 165°C.

7.4 Device Functional Modes

7.4.1 Shutdown Mode

EN/UVLO facilitates ON and OFF control for the LM25184-Q1. When VEN/UVLO is below approximately 0.6 V, the

device is in shutdown mode. Both the internal LDO and the switching regulator are off. The quiescent current in

shutdown mode drops to 3 μA at VIN = 24 V. The LM25184-Q1 also employs internal bias rail undervoltage

protection. If the internal bias supply voltage is below its UV threshold, the converter remains off.

7.4.2 Standby Mode

The internal bias rail LDO regulator has a lower enable threshold than the converter itself. When VEN/UVLO is

above 0.6 V and below the precision-enable threshold (1.5 V typically), the internal LDO is on and regulating.

The precision enable circuitry is turned on once the internal VCC is above its UV threshold. The switching action

and voltage regulation are not enabled until VEN/UVLO rises above the precision enable threshold.

7.4.3 Active Mode

The LM25184-Q1 is in active mode when VEN/UVLO is above the precision-enable threshold and the internal bias

rail is above its UV threshold. The LM25184-Q1 operates in one of three modes depending on the load current

requirement:

1. Boundary conduction mode (BCM) at heavy loads

2. Discontinuous conduction mode (DCM) at medium loads

3. Frequency foldback mode (FFM) at light loads

Refer to Section 7.3.2 for more detail.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

15

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

8 Application and Implementation

Note

Information in the following applications sections is not part of the TI component specification, and TI

does not warrant its accuracy or completeness. TI’s customers are responsible for determining

suitability of components for their purposes. Customers should validate and test their design

implementation to confirm system functionality.

8.1 Application Information

The LM25184-Q1 requires only a few external components to convert from a wide range of supply voltages to

one or more isolated output rails. To expedite and streamline the process of designing of a LM25184-Q1-based

converter, a comprehensive LM25184-Q1 quick-start calculator is available for download to assist the designer

with component selection for a given application. WEBENCH® online software is also available to generate

complete designs, leveraging iterative design procedures and access to comprehensive component databases.

The following sections discuss the design procedure for both single- and dual-output implementations using

specific circuit design examples.

As mentioned previously, the LM25184-Q1 also integrates several optional features to meet system design

requirements, including precision enable, input UVLO, programmable soft start, output voltage thermal

compensation, and external bias supply connection. Each application incorporates these features as needed for

a more comprehensive design.

The application circuits detailed in Section 8.2 show LM25184-Q1 configuration options suitable for several

application use cases. Refer to the LM25184EVM-S12 EVM user's guide for more detail.

8.2 Typical Applications

For step-by-step design procedures, circuit schematics, bill of materials, PCB files, simulation and test results of LM25184-Q1-powered

implementations, refer to the TI Reference Design library.

8.2.1 Design 1: Wide VIN, Low IQ PSR Flyback Converter Rated at 12 V, 1 A

The schematic diagram of a 12-V, 1-A PSR flyback converter is given in Figure 8-1.

VIN = 6 V...42 V

T1

DFLY

VOUT = 12 V

IOUT = 1 A

DCLAMP

20 V

RUV1

COUT

4x

22 F

261 k:

CIN

10 F

EN/UVLO

RUV2

97.1 k:

SW

RFB

121 k:

LM25184

GND

SS/BIAS

FB

RSET

CSS

47 nF

1:1

7 PH

DF

VIN

DOUT

13 V

RTC

RSET

261 k:

12.1 k:

TC

Figure 8-1. Schematic for Design 1 With VIN(nom) = 24 V, VOUT = 12 V, IOUT = 1 A

16

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

8.2.1.1 Design Requirements

The required input, output, and performance parameters for this application example are shown in Table 8-1.

Table 8-1. Design Parameters

DESIGN PARAMETER

VALUE

Input voltage range

6 V to 36 V

Input UVLO thresholds

5.5 V on, 4 V off

Output voltage

12 V

Rated load current, VIN ≥ 13.5 V

1A

Output voltage regulation

±1.5%

Output voltage ripple

< 120 mV pk-pk

The target full-load efficiency is 89% based on a nominal input voltage of 24 V and an isolated output voltage of

12 V. The LM25184-Q1 is chosen to deliver a fixed 12-V output voltage set by resistor RFB connected between

the SW and FB pins. The input voltage turnon and turnoff thresholds are established by RUV1 and RUV2. The

required components are listed in Table 8-2. Transformers for other single-output designs are listed in Table 8-3.

Table 8-2. List of Components for Design 1

REF DES

QTY

SPECIFICATION

VENDOR

PART NUMBER

CIN

1

10 µF, 50 V, X7R, 1210, ceramic

TDK

CNA6P1X7R1H106K250AE

TDK

CNA6P1X7R1H106K250AE

Taiyo Yuden

TMK325B7226MM-PR

COUT1

4

22 µF, 25 V, X7R, 1210, ceramic

COUT2

0

100 µF, 16 V, ±20%, electrolytic

Kemet

T598D107M016ATE050

CSS

1

47 nF, 16 V, X7R, 0402

Std

Std

DCLAMP

1

Zener, 20 V, 3 W, SMA

3SMAJ5932B

Micro Commercial

DF, DFLY

2

Schottky diode, 60 V, 3 A, SOD-123FL

FSV360FP

OnSemi

DOUT

1

Zener, 13 V, 2%, SOD-523

BZX585-B13

Nexperia

RFB

1

121 kΩ, 1%, 0402

Std

Std

RSET

1

12.1 kΩ, 1%, 0402

Std

Std

RTC

1

261 kΩ, 1%, 0402

Std

Std

RUV1

1

261 kΩ, 1%, 0603

Std

Std

RUV2

1

97.6 kΩ, 1%, 0402

Std

Std

Coilcraft

ZA9672-BE

T1

1

Sumida

12387-T162

U1

1

7 μH, 5 A, 1 : 1, 13 mm × 11 mm × 10 mm

7 μH, 5 A, 1 : 1, 9.8 mm × 9.5 mm ×10.6 mm

Würth Electronik

750318701

LM25184-Q1 PSR flyback converter, AEC-Q100

Texas Instruments

LM25184QNGURQ1

Table 8-3. Magnetic Components for Single-Output Designs

OUTPUT VOLTAGE RANGE

TURNS RATIO

LMAG, ISAT

3.3 V to 5 V

3:1

9 µH, 5 A

5 V to 12 V

1:1

7 µH, 5 A

12 V to 24 V

1:2

7 µH, 5 A

24 V to 48 V

1:3

9 µH, 5 A

3.3 V to 6 V

2:1

7 µH, 5 A

DIMENSIONS

VENDOR

PART NUMBER

ZA9671-BE

13 × 11 × 10 mm

ZA9672-BE

Coilcraft

ZA9673-BE

ZA9674-BE

12 × 10 × 6 mm

ZB1067-AE

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

17

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

8.2.1.2 Detailed Design Procedure

8.2.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LM25184-Q1 device with WEBENCH® Power Designer.

1. Start by entering the input voltage (VIN), output voltage (VOUT), and output current (IOUT) requirements.

2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time

pricing and component availability.

In most cases, these actions are available:

• Run electrical simulations to see important waveforms and circuit performance

• Run thermal simulations to understand board thermal performance

• Export customized schematic and layout into popular CAD formats

• Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

8.2.1.2.2 Custom Design With Excel Quickstart Tool

Use the LM25184-Q1 quick-start calculator to select components based on the converter specifications.

8.2.1.2.3 Flyback Transformer – T1

Choose a turns ratio of 1 : 1 based on an approximate 70% max duty cycle at minimum input voltage using

Equation 14, rounding up or down as needed. While the maximum duty cycle can approach 80% if a particularly

wide input voltage application is needed, it increases the peak current stress of the secondary-side components.

NPS

VIN(min)

DMAX

˜

1 DMAX VOUT VD

0.7

5V

˜

1 0.7 12 V + 0.3 V

0.95

(14)

Select a magnetizing inductance based on the minimum off-time constraint using Equation 15. Choose a value

of 7 µH to allow some margin for this application. Specify a saturation current of 5 A, above the maximum switch

current specification of the LM25184-Q1.

LMAG t

VOUT

VD ˜ NPS ˜ t OFF-MIN

ISW-PEAK(FFM)

12 V + 0.3 V ˜ 1˜ 425ns

0.82 A

6.4 +

(15)

Note that a higher magnetizing inductance provides a larger operating range for BCM and FFM, but the leakage

inductance can increase based on a higher number of primary turns, NP. Equation 16 and Equation 17 give the

primary and secondary winding RMS currents, respectively.

IPRI-RMS

ISEC-RMS

D

˜ IPRI-PK

3

(16)

2 ˜ IOUT ˜ IPRI-PK ˜ NPS

3

(17)

Find the maximum output current for a given turns ratio using Equation 18, where η is the efficiency and the

typical value for ISW-PEAK is the 4.1-A switch peak current threshold. Iterate by increasing the turns ratio if the

output current capability is too low at minimum input voltage, checking that the SW voltage rating of 65 V is not

exceeded at maximum input voltage.

18

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

K

IOUT(max)

ISW-PEAK

˜

2 § VOUT

¨

© VIN

-°0.95 A at VIN

®

°¯1.25 A at VIN

0.92

4.1A

˜

2 § 12 V 1 ·

¨

¸

© VIN 1 ¹

1 ·

¸

NPS ¹

12 V

24 V

(18)

8.2.1.2.4 Flyback Diode – DFLY

The flyback diode reverse voltage is given by Equation 19.

VD-REV t

VIN(max)

NPS

42 V

1

VOUT

12 V

54 V

(19)

Select a 60-V, 3-A Schottky diode for this application to account for inevitable diode voltage overshoot and

ringing related to the resonance of transformer leakage inductance and diode parasitic capacitance. Connect an

appropriate RC snubber circuit (for example, 100 Ω and 22 pF) across the flyback diode if needed, particularly if

the transformer leakage inductance is high. Also, choose a flyback diode with current rating that aligns with the

maximum peak secondary winding current of NPS × ISW-PEAK.

8.2.1.2.5 Leakgae Inductance Clamp Circuit – DF, DCLAMP

Connect a diode-Zener clamp circuit across the primary winding to limit the peak switch voltage after MOSFET

turnoff below the maximum level of 65 V, as given by Equation 20.

VDZ(clamp)

VSW(max)

VIN(max)

(20)

Choose a 20-V zener diode for DCLAMP to give a clamp voltage of approximately 1.5 times the reflected output

voltage, as specified by Equation 21. This provides a balance between the maximum switch voltage excursion

and the leakage inductance demagnetization time. Select a Zener diode with low package parasitic inductance

to manage the high slew-rate current during the switch turnoff transition.

VDZ(clamp)

1.5 ˜ NPS ˜ VOUT

VD

1.5 ˜ 1˜ 12 V

0.4 V

18.6 V

(21)

Choose an ultra-fast switching diode or Schottky diode for DF with reverse voltage rating greater than the

maximum input voltage and forward current rating of 3 A or higher.

8.2.1.2.6 Output Capacitor – COUT

The output capacitor determines the voltage ripple at the converter output, limits the voltage excursion during a

load transient, and sets the dominant pole of the small-signal response of the converter. Select an output

capacitance using Equation 22 to limit the ripple voltage amplitude to less than 1% of the output voltage at

minimum input voltage and maximum load.

2

COUT t

LMAG ˜ ISW-PEAK

2 ˜ 'VOUT ˜ VOUT

§1 D ·

˜¨

¸

© 2 ¹

2

7 +˜

2

§ 1 0.7 ·

˜

2 ˜ 120mV ˜ 12 V ¨© 2 ¸¹

$

2

30 )

(22)

Mindful of the voltage coefficient of ceramic capacitors, select four 22-µF, 25-V capacitors in 1210 case size with

X7S or better dielectric. Assuming operation in BCM, calculate the capacitive ripple voltage at the output using

Equation 23.

'VOUT

LMAG ˜ IOUT

2

2 ˜ COUT ˜ VOUT ˜ NPS

2

§1 D ·

˜¨

¸

©1 D ¹

2

2

LMAG ˜ IOUT

2 ˜ 'VOUT ˜ VOUT

ª 1

˜«

«¬ NPS

2 ˜ VOUT

VIN

VD º

»

»¼

2

(23)

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

19

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

Equation 24 gives an expression for the output capacitor RMS ripple current.

ICOUT-RMS

IOUT ˜

2 ˜ NPS ˜ IPRI-PK

3 ˜ IOUT

1

(24)

8.2.1.2.7 Input Capacitor – CIN

Select an input capacitance using Equation 25 to limit the ripple voltage amplitude to less than 5% of the input

voltage when operating at nominal input voltage.

CIN

§ D·

IPRI-PK ˜ D ˜ ¨ 1

2 ¸¹

©

t

2 ˜ FSW ˜ 'VIN

2

(25)

Substituting the input current at full load, switching frequency, peak primary current, and peak-to-peak ripple

specification gives CIN greater than 5 μF. Considering the voltage coefficient of ceramic capacitors, select a 10µF, 50-V, X7R ceramic capacitor in 1210 case size. Equation 26 gives the input capacitor RMS ripple current.

D ˜ IPRI-PK

4

1

˜

2

3 ˜D

ICIN-RMS

(26)

8.2.1.2.8 Feedback Resistor – RFB

Select a feedback resistor, designated RFB, of 121 kΩ based on the secondary winding voltage at the end of the

flyback conduction interval (the sum of the 12-V output voltage and the Schottky diode forward voltage drop as

its current approaches zero) reflected by the transformer turns ratio of 1 : 1.

RFB

VOUT

VD ˜ NPS

0.1 mA

12 V 0.2 V ˜ 1

122 k:

0.1 mA

(27)

8.2.1.2.9 Thermal Compensation Resistor – RTC

Select a resistor for output voltage thermal compensation, designated RTC, based on Equation 28.

RTC ª¬k: º¼

RFB ¬ªk: º¼

NPS

˜

3

TCDiode ª¬ mV qC º¼

121 k: ˜ 3

1˜ 1.4

261 k:

(28)

8.2.1.2.10 UVLO Resistors – RUV1, RUV2

Given VIN(on) and VIN(off) as the input voltage turnon and turnoff thresholds of 5.5 V and 4 V, respectively, select

the upper and lower UVLO resistors using the following expressions:

VIN(on) ˜

RUV1

RUV2

RUV1 ˜

VUV-FALLING

VUV-RISING

IUV-HYST

VIN(off)

VUV-RISING

VIN(on) VUV-RISING

5.5 V ˜

263k: ˜

1.45 V

1.5 V

5 $

4V

1.5 V

5.5 V 1.5 V

263k:

(29)

98.6k:

(30)

The nearest standard E96 resistor values for RUV1 and RUV2 are 261 kΩ and 97.6 kΩ, respectively. Calculate the

actual input voltage turnon and turnoff thresholds as follows:

20

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

VIN(on)

VIN(off)

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

§

RUV1 ·

VUV-RISING ¨ 1

¸

© RUV2 ¹

§

261 k: ·

1.5 V ¨ 1

¸

97.6k: ¹

©

§

RUV1 ·

VUV-FALLING ¨ 1

¸ IUV-HYST ˜ RUV1

© RUV2 ¹

5.51V

§

261 k: ·

1.45 V ¨ 1

¸ 5 $˜

97.6k: ¹

©

(31)

N:

9

(32)

8.2.1.2.11 Soft-Start Capacitor – CSS

Connect an external soft-start capacitor for a specific soft-start time. In this example, select a soft-start

capacitance of 47 nF based on Equation 12 to achieve a soft-start time of 9 ms.

For technical solutions, industry trends, and insights for designing and managing power supplies, please refer to TI's Power Management

technical articles.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

21

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

8.2.2 Application Curves

Unless otherwise stated, application performance curves were taken at TA = 25°C.

95

95

90

90

85

Efficiency (%)

Efficiency (%)

85

80

75

70

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

65

80

75

70

65

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

60

55

60

50

0

200

400

600

800

Load Current (mA)

1000

1200

1

10

100

Load Current (mA)

D001

Figure 8-2. Efficiency (Linear Scale)

1000

D002

Figure 8-3. Efficiency (Log Scale)

12.6

12.4

12.4

Output Voltage (V)

Output Voltage (V)

12.2

12.2

12

11.8

11.8

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

11.6

200

400

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

11.6

11.4

0

12

600

800 1000

Load Current (mA)

1200

1400

1600

D003

Figure 8-4. Load Regulation (Linear Scale)

1

10

100

Load Current (mA)

1000 2000

D004

Figure 8-5. Load Regulation (Log Scale)

VOUT 2 V/div

VOUT 2 V/div

IOUT 0.2 A/div

IOUT 0.2 A/div

VEN/UVLO 10 V/div

VIN 10 V/div

4 ms/div

VIN stepped to 24 V

12-Ω Load

Figure 8-6. Start-up Characteristic

22

4 ms/div

VIN = 24 V

12-Ω Load

Figure 8-7. Enable ON and OFF Characteristic

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

VSW 10 V/div

VSW 10 V/div

1 Ps/div

VIN = 13.5 V

IOUT = 1 A

1 Ps/div

VIN = 24 V

Figure 8-8. Switch Node Voltage

IOUT = 1 A

Figure 8-9. Switch Node Voltage

VSW 10 V/div

VOUT 0.2 V/div

IOUT 0.5 A/div

200 Ps/div

1 Ps/div

VIN = 36 V

IOUT = 1 A

VIN = 24 V

Figure 8-10. Switch Node Voltage

Figure 8-11. Load Transient, 0.1 A to 1 A, 0.1 A/µs

VOUT 0.2 V/div

VOUT 0.2 V/div

IOUT 0.5 A/div

IOUT 0.5 A/div

200 Ps/div

200 Ps/div

VIN = 13.5 V

VIN = 6 V

Figure 8-12. Load Transient, 0.1 A to 1 A, 0.1 A/µs

Figure 8-13. Load Transient, 0.1 A to 0.5 A, 0.1 A/µs

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

23

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

Average detector

Peak detector

Peak detector

Average detector

Start 150 kHz

VIN = 24 V

Stop 30 MHz

150 kHz to 30 MHz

IOUT = 1 A

LIN = 4.7 µH

VIN = 24 V

CIN = 10 µF

IOUT = 1 A

Figure 8-14. CISPR 25 Class 5 Conducted EMI Plot

24

Start 30 MHz

Stop 108 MHz

30 MHz to 108 MHz

LIN = 4.7 µH

CIN = 10 µF

Figure 8-15. CISPR 25 Class 5 Conducted EMI Plot

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

8.2.3 Design 2: PSR Flyback Converter With Dual Outputs of 15 V and –8 V at 0.5 A

The schematic diagram of a dual-output flyback converter intended for isolated IGBT and SiC MOSFET gate

drive power supply applications is given in Figure 8-16.

VIN = 4.5 V...42 V

T1

DFLY1

VOUT1 = 15 V

IOUT1 = 0.5 A

DCLAMP

20 V

CIN

10 F

EN/UVLO

1 : 1.5 : 0.8

DF

VIN

DOUT1

18 V

COUT1

2x

22 F

7 PH

SW

COUT2

2x

47 F

RFB

LM25184

102 k:

DOUT2

9.1 V

VOUT2 = ±8 V

FB

GND

SS/BIAS

IOUT2 = ±0.5 A

DFLY2

RSET

RTC

RSET

221 k:

12.1 k:

TC

Figure 8-16. Schematic for Design 2 With VIN(nom) = 13.5 V, VOUT1 = 15 V, VOUT2 = –8 V, IOUT = 0.5 A

8.2.3.1 Design Requirements

The required input, output, and performance parameters for this application example are shown in Table 8-4.

Table 8-4. Design Parameters

DESIGN PARAMETER

VALUE

Input voltage range (steady state)

4.5 V to 42 V

Output 1 voltage and current (at VIN ≥ 24 V)

15 V, 0.5 A

Output 2 voltage and current (at VIN ≥ 24 V)

–8 V, 0.5 A

Input UVLO thresholds

4.5 V on, 4 V off

Output voltage regulation

±2%

The target full-load efficiency of this LM25184-Q1 design is 89% based on a nominal input voltage of 13.5 V and

isolated output voltages of 15 V and –8 V sharing a common return. The selected flyback converter components

are cited in Table 8-5, including the following:

•

•

•

•

A multi-winding flyback transformer

Input and output capacitors

Flyback rectifying diodes

A flyback converter IC

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

25

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

Table 8-5. List of Components for Design 2

REF DES

QTY

CIN

1

COUT1

2

SPECIFICATION

10 µF, 50 V, X7R, 1210, ceramic, AEC-Q200

22 µF, 25 V, X7R, 1210, ceramic, AEC-Q200

47 μF, 16 V, X7S, 1210, Ceramic

COUT2

2

47 μF, 16 V, X7R, 1210, Ceramic

DCLAMP

1

VENDOR

PART NUMBER

TDK

CNA6P1X7R1H106K250AE

Taiyo Yuden

UMJ325KB7106KMHP

TDK

CGA6P3X7R1E226M250AB

Taiyo Yuden

TMK325B7226KMHT

Murata

GRM32EC81C476KE15L

Taiyo Yuden

EMK325AC6476MM-P

Murata

GRM32ER71A476KE15L

Taiyo Yuden

LMK325B7476MM-TR

Kemet

C1210C476K8RAC7800

Zener, 20 V, 3 W, SMA

3SMAJ5932B

Micro Commercial

DF, DFLY2

1

Schottky diode, 60 V, 3 A, SOD-123FL

FSV360FP

OnSemi

DFLY1

2

Schottky diode, 100 V, 1 A, POWERDI123

DFLS1100-7

Diodes Inc.

DOUT1

1

Zener, 18 V, 5%, SOD-523, AEC-Q101

BZX585-C18

Nexperia

DOUT2

1

Zener, 9.1 V, 5%, SOD-523, AEC-Q101

BZX585-C9V1

Nexperia

RFB

1

102 kΩ, 1%, 0402

Std

Std

RSET

1

12.1 kΩ, 1%, 0402

Std

Std

RTC

1

T1

1

U1

1

221 kΩ, 1%, 0402

Std

Std

7 μH, 5 A, 1 : 1.5 : 0.8, 9.2 mm × 9.8 mm × 9.8 mm

Würth Electronik

750318704

7 μH, 5 A, 1 : 1.5 : 0.8, 13 mm × 11 mm × 10 mm

Coilcraft

ZA9675-BE

LM25184-Q1 PSR flyback converter, VSON-8, AEC-Q100

Texas Instruments

LM25184QNGURQ1

8.2.3.2 Detailed Design Procedure

Using the LM25184-Q1 quick-start calculator , components are selected based on the flyback converter

specifications.

8.2.3.2.1 Flyback Transformer – T1

Set the turns ratio of the transformer secondary windings using Equation 33, where NS1 and NS2 are the number

of secondary turns for the respective outputs.

NS2

NS1

VOUT2

VOUT1

VD2

VD1

8 V 0.3 V

15 V 0.3 V

0.542

(33)

Choose a primary-secondary turns ratio for a 15-V output based on an approximate 70% max duty cycle at

minimum input voltage using Equation 34. The transformer turns ratio when considering both outputs is thus

specified as 1 : 1.5 : 0.8.

NPS

VIN(min)

DMAX

˜

1 DMAX VOUT VD

0.7

4.5 V

˜

1 0.7 15 V + 0.3 V

0.69

(34)

Select a magnetizing inductance based on the minimum off-time constraint using Equation 35. Choose a value

of 7 µH and a saturation current of 5 A for this application.

LMAG t

26

VOUT

VD ˜ NPS ˜ t OFF-MIN

ISW-PEAK(FFM)

15 V + 0.3 V ˜ 1 1.5 ˜ 425ns

0.82 A

Submit Document Feedback

5.3 +

(35)

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

Find the maximum output current for a given turns ratio, assuming the outputs are symmetrically loaded, using

Equation 36.

IOUT(max)

K

ISW-PEAK

˜

2 § VOUT

¨

© VIN

0.9

4.1A

˜

2 § 23 V

1

¨¨

1 2.3

© VIN

1 ·

¸

NPS ¹

·

¸¸

¹

-°0.45 A at VIN

®

°¯0.57 A at VIN

12 V

24 V

(36)

8.2.3.2.2 Flyback Diodes – DFLY1 and DFLY2

The flyback diode reverse voltages for the positive and negative outputs are given respectively by Equation 37

and Equation 38.

VD1-REV t

VD2-REV t

VIN(max)

NPS1

VIN(max)

NPS2

VOUT1

42 V

1 1.5

15 V

(37)

42 V

1 0.8

VOUT2

79 V

8V

42 V

(38)

Choose 100-V, 1-A and 60-V, 3-A Schottky diodes for the positive and negative outputs, respectively, to allow

some margin for inevitable voltage overshoot and ringing related to leakage inductance and diode capacitance.

Use an RC snubber circuit across each diode, for example, 100 Ω and 22 pF, to mitigate such overshoot and

ringing, particularly if the transformer leakage inductance is high.

8.2.3.2.3 Input Capacitor – CIN

The input capacitor filters the primary-winding current waveform. To prevent large ripple voltage, use a low-ESR

ceramic input capacitor sized according to Equation 25 for the RMS ripple current given by Equation 26. In this

design example, choose a 10-µF, 50-V ceramic capacitor with X7R dielectric and 1210 footprint.

8.2.3.2.4 Output Capacitors – COUT1, COUT2

The output capacitors determine the voltage ripple at the converter outputs, limit the voltage excursion during a

load transient, and set the dominant pole of the small-signal response of the converter.

Mindful of the voltage coefficient of ceramic capacitors, select two 22-µF, 25-V, X7R capacitors in 1210 case size

for the positive output and two 47-µF, 10-V, X7R capacitors in 1210 case size for the negative output.

8.2.3.2.5 Feedback Resistor – RFB

Install a 102-kΩ resistor from SW to FB based on an output voltage setpoint of 15 V (plus a flyback diode voltage

drop) reflected to the primary side by a transformer turns ratio of 1 : 1.5.

RFB

VOUT1

VD1 ˜ NPS1

15 V 0.3 V ˜ 1 1.5

0.1 mA

0.1 mA

102 k:

(39)

8.2.3.2.6 Thermal Compensation Resistor – RTC

Select a resistor value for output voltage thermal compensation based on Equation 40.

RTC ª¬k: º¼

RFB ª¬k: º¼

NPS

˜

3

TCDiode ª¬ mV qC º¼

102 k: ˜ 3

1 1/ 5 ˜ 2

230 k:

(40)

8.2.3.2.7 Output Voltage Clamp Zeners – DOUT1 and DOUT2

Calculate the power delivered to the output at no load based on Equation 41.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

27

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

POUT(min)

LMAG ˜ ISW-PEAK(FFM)

2

2

˜ FSW(min)

7 +˜

$

2

2

˜ 12kHz

28mW

(41)

Select Zener clamp diodes to limit the voltages to a range of 110% to 120% of the nominal output voltage

setpoints during no-load operation. Connect 18-V and 9.1-V Zener diodes with ±5% tolerance and SOD-523

package across the positive and negative outputs, respectively.

28

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

8.2.3.3 Application Curves

95

95

90

90

85

Efficiency (%)

Efficiency (%)

85

80

75

70

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

65

80

75

70

65

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

60

55

60

50

0

100

200

300

400

Load Current (mA)

500

600

1

23.8

23.8

23.6

23.6

23.4

23.4

23.2

23

22.8

D006

23.2

23

22.8

22.6

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

22.4

1000

Figure 8-18. Efficiency (Log Scale)

Output Voltage (V)

Output Voltage (V)

Figure 8-17. Efficiency (Linear Scale)

22.6

10

100

Load Current (mA)

D005

VIN = 6 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

22.4

22.2

22.2

0

200

400

Load Current (mA)

600

800

1

10

100

Load Current (mA)

D007

Total of VOUT1 and VOUT2

1000

D008

Total of VOUT1 and VOUT2

Figure 8-19. Load Regulation (Linear Scale)

Figure 8-20. Load Regulation (Log Scale)

VIN 10 V/div

VOUT1 5 V/div

IOUT1 0.5 A/div

VSW 10 V/div

VOUT2 5 V/div

2 ms/div

20 Ps/div

VIN stepped to 24 V

30-Ω and 16-Ω Loads

Figure 8-21. Start-Up Characteristic

VIN = 24 V

IOUT1 = IOUT2 = 0 A

Figure 8-22. Switch Voltage, No Load

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

29

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

VSW 10 V/div

VSW 10 V/div

1 Ps/div

1 Ps/div

VIN = 24 V

IOUT1 = IOUT2 = 0.3 A

Figure 8-23. Switch Voltage, Medium Load

VIN = 24 V

IOUT1 = IOUT2 = 0.5 A

Figure 8-24. Switch Voltage, Full Load

VOUT1 0.2 V/div

VOUT1 0.2 V/div

VOUT2 0.2 V/div

VOUT2 0.2 V/div

IOUT1 0.2 A/div

IOUT2 0.2 A/div

IOUT2 0.2 A/div

IOUT1 0.2 A/div

200 Ps/div

200 Ps/div

VIN = 24 V

IOUT2 = 0.5 A

Figure 8-25. Positive Output Load Transient, 0.25 A

to 0.5 A

30

VIN = 24 V

IOUT1 = 0.5 A

Figure 8-26. Negative Output Load Transient, 0.25

A to 0.5 A

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

9 Power Supply Recommendations

The LM25184-Q1 flyback converter operates over a wide input voltage range from 4.5 V to 42 V. The

characteristics of the input supply must be compatible with Section 6.1 and Section 6.3. In addition, the input

supply must be capable of delivering the required input current to the fully-loaded regulator. Estimate the

average input current with Equation 42.

IIN

VOUT ˜ IOUT

VIN ˜ K

(42)

where

•

η is the efficiency

If the converter is connected to an input supply through long wires or PCB traces with a large impedance, special

care is required to achieve stable performance. The parasitic inductance and resistance of the input cables can

have an adverse effect on converter operation. The parasitic inductance in combination with the low-ESR

ceramic input capacitors form an underdamped resonant circuit. This circuit can cause overvoltage transients at

VIN each time the input supply is cycled ON and OFF. The parasitic resistance causes the input voltage to dip

during a load transient. If the regulator is operating close to the minimum input voltage, this dip can cause false

UVLO fault triggering and a system reset. The best way to solve such issues is to reduce the distance from the

input supply to the regulator and use an aluminum electrolytic input capacitor in parallel with the ceramics. The

moderate ESR of the electrolytic capacitors helps damp the input resonant circuit and reduce any voltage

overshoots. A capacitance in the range of 22 µF to 100 µF is usually sufficient to provide input damping and

helps to hold the input voltage steady during large load transients. A typical ESR of 200 mΩ provides enough

damping for most input circuit configurations.

An EMI input filter is often used in front of the regulator that, unless carefully designed, can lead to instability as

well as some of the effects mentioned above. The application report Simple Success with Conducted EMI for

DC-DC Converters provides helpful suggestions when designing an input filter for any switching regulator.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

31

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

10 Layout

The performance of any switching converter depends as much upon PCB layout as it does the component

selection. The following guidelines are provided to assist with designing a PCB with the best power conversion

performance, thermal performance, and minimized generation of unwanted EMI. Figure 10-1 and Figure 10-2

provide layout examples for single-output and dual-output designs, respectively.

10.1 Layout Guidelines

PCB layout is critical for good power supply design. There are several paths that conduct high slew-rate currents

or voltages that can interact with transformer leakage inductance or parasitic capacitance to generate noise and

EMI or degrade the performance of the power supply.

1. Bypass VIN to GND with a low-ESR ceramic capacitor, preferably of X7R or X7S dielectric. Place CIN as

close as possible to the LM25184-Q1 VIN and GND pins. Ground return paths for the input capacitor or

capacitors must consist of localized top-side planes that connect to the GND pin and exposed PAD.

2. Minimize the loop area formed by the input capacitor connections and the VIN and GND pins.

3. Locate the transformer close to the SW pin. Minimize the area of the SW trace or plane to prevent excessive

e-field or capacitive coupling.

4. Minimize the loop area formed by the diode-Zener clamp circuit connections and the primary winding

terminals of the transformer.

5. Minimize the loop area formed by the flyback rectifying diode, output capacitor, and the secondary winding

terminals of the transformer.

6. Tie the GND pin directly to the DAP under the device and to a heat-sinking PCB ground plane.

7. Use a ground plane in one of the middle layers as a noise shielding and heat dissipation path.

8. Have a single-point ground connection to the plane. Route the return connections for the reference resistor,

soft start, and enable components directly to the GND pin. This prevents any switched or load currents from

flowing in analog ground traces. If not properly handled, poor grounding results in degraded load regulation or

erratic output voltage ripple behavior.

9. Make VIN+, VOUT+, and ground bus connections short and wide. This reduces any voltage drops on the input

or output paths of the converter and maximizes efficiency.

10.Minimize trace length to the FB pin. Locate the feedback resistor close to the FB pin.

11. Locate components RSET, RTC, and CSS as close as possible to their respective pins. Route with minimal

trace lengths.

12.Place a capacitor between input and output return connections to route common-mode noise currents directly

back to their source.

13.Provide adequate heatsinking for the LM25184-Q1 to keep the junction temperature below 150°C. For

operation at full rated load, the top-side ground plane is an important heat-dissipating area. Use an array of

heat-sinking vias to connect the DAP to the PCB ground plane. If the PCB has multiple copper layers,

connect these thermal vias to inner-layer ground planes. The connection to VOUT+ provides heatsinking for

the flyback diode.

32

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

10.2 Layout Examples

Place the input capacitor close

to the VIN pin and connect to

the GND plane under the IC

Keep the DZ clamp and RC snubber

components close to the primary winding

pins and use heatsinking for the Zener

Locate the RC snubber

components close to

the flyback diode

Use adequate heatsinking

copper connected to the

cathode of the flyback

diode (VOUT)

Locate the converter IC close

to the transformer and connect

to the GND plane as shown

Keep the secondary

winding, flyback diode

and output capacitor

loop as tight as possible

Locate the RSET, TC and FB resistors and

the SS capacitor close to their respective pins

Place the Y-cap close to the transformer so that common-mode

currents from the secondary to the primary side return in a tight loop

Figure 10-1. Single-Output PCB Layout Example

Place the ceramic input

capacitor close to the IC to

minimize the switching loop area

Use heatsinking for the clamp

Zener, especially if the transformer

leakage inductance is high

Locate the converter IC close

to the transformer and connect

to the GND plane as shown

Minimize the area of the

secondary winding,

flyback diode and output

capacitor switching loops

Place the RSET, TC, FB and SS small-signal

components near their respective pins

Maintain the appropriate primaryto-secondary clearance distance

Figure 10-2. Dual-Output PCB Layout Example

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: LM25184-Q1

33

�LM25184-Q1

www.ti.com

SNVSBJ6A – MARCH 2020 – REVISED AUGUST 2020

11 Device and Documentation Support

11.1 Device Support

11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT

CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES