LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

LM3000 Dual Synchronous Emulated Current-Mode Controller

Check for Samples: LM3000

FEATURES

DESCRIPTION

•

•

•

•

•

The LM3000 is a dual output synchronous buck

controller which is designed to convert input voltages

ranging from 3.3V to 18.5V down to output voltages

as low as 0.6V. The two outputs switch at a constant

programmable frequency of 200 kHz to 1.5 MHz, with

the second output 180 degrees out of phase from the

first to minimize the input filter requirements. The

switching frequency can also be phase locked to an

external frequency. A CLKOUT provides an external

clock 90 degrees out of phase with the main clock so

that a second chip can be run out of phase with the

main chip. The emulated current-mode control utilizes

bottom side FET sensing to provide fast transient

response and current limit without the need for

external current sense resistors or RC networks.

Separate Enable, Soft-Start and Track pins allow

each output to be controlled independently to provide

maximum flexibility in designing system power

sequencing.

1

2

•

•

•

•

•

VIN Range FROM 3.3V to 18.5V

Output Voltage From 0.6V to 80% of VIN

Remote Differential Output Voltage Sensing

1% Accuracy at FB Pin

Interleaved Operation Reduces Input

Capacitors

Frequency Sync/Adjust From 200 kHz to 1.5

MHz

Startup With Pre-Bias Load

Independent Power Good, Enable, Soft-Start

and Track

Programmable Current Limit Without External

Sense Resistor

Hiccup Mode Short Circuit Protection

APPLICATIONS

•

•

•

•

•

•

DC Power Distribution Systems

Graphic Cards - GPU and Memory ICs

FPGA, CPLD, and ASICs

Embedded Processor

1.8V and 2.5V I/O Supplies

Networking Equipment (Routers, Hubs)

The LM3000 has a full range of protection features

which include input under-voltage lock-out (UVLO),

power good (PGOOD) signals for each output, overvoltage crowbar and hiccup mode during short circuit

events.

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2009–2013, Texas Instruments Incorporated

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

Simplified Application

VIN

CIN

L1

VOUT1

RFBT1

VIN

Q1

HG1

COUT1

RFBB1

LG1

Q2

LM3000

PGND1

LG2

Q4

VOUT2

COUT2

+

RFBT2

RFBB2

PGND2

GND1

GND2

EA1_GND

EA2_GND

FB2

FB1

PGOOD1

CSS1

CSYNC

SYNC

PGOOD2

EN1

EN2

SS1

SS2

CSS2

TRK2

TRK1

FREQ/SYNC

RFRQ

2

L2

VSW2

VSW1

+

Q3

HG2

CLKOUT

SGND

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

VSW1

PGND1

LG1

VDR

VIN

LG2

PGND2

VSW2

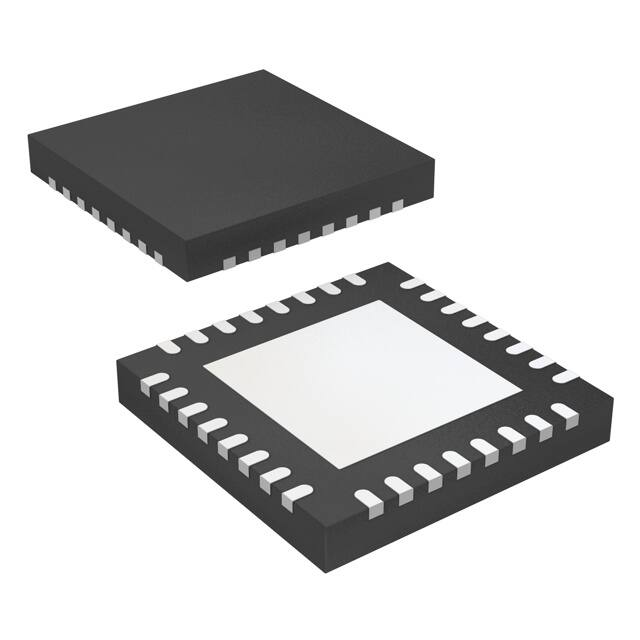

Connection Diagram

8

7

6

5

4

3

2

1

ILIM1

9

32

ILIM2

HG1

10

31

HG2

30

VCB2

DAP (should be tied to SGND on

board)

13

28

CLKOUT

FB1

14

27

EA2_GND

COMP1

15

26

FB2

PGOOD1

16

25

COMP2

17

18

19

20

21

22

23

24

PGOOD2

EA1_GND

EN2

SGND

SS2

29

WQFN-32

5x5x0.8mm body size

0.5mm pitch

TRK2

LM3000

SS1

12

TRK1

VDD

EN1

11

FREQ/SYNC

VCB1

Figure 1. Top View

32-Lead WQFN

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

3

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

PIN DESCRIPTIONS

Pin No.

(1)

4

Name

Description

1

VSW2

Switch node sense for channel 2.

2

PGND2

3

LG2

Channel 2 low-side gate drive for external MOSFET.

4

VIN

Chip supply voltage, input to the VDD and VDR regulators. (3.3V to 18.5V)

5

VDR

Supply for low-side gate drivers.

6

LG1

Channel 1 low-side gate drive for external MOSFET.

7

PGND1

8

VSW1

Switch node sense for channel 1.

9

ILIM1

Current limit setting input for channel 1.

10

HG1

Channel 1 high-side gate drive for external MOSFET.

11

VCB1

Boost voltage for channel 1 high-side driver.

12

VDD

Supply for control circuitry.

13

EA1_GND

14

FB1

15

COMP1

16

PGOOD1

17

FREQ/SYNC

Power ground for channel 2 low-side drivers. (1)

Power ground for channel 1 low-side drivers. (1)

Error amplifier ground sense for channel 1. (1)

Error amplifier input for channel 1.

Error amplifier output for channel 1.

Power good signal for channel 1 under-voltage and over-voltage.

Frequency set / synchronization input for internal PLL.

18

EN1

19

TRK1

Channel 1 enable input. Used to set the emulated current slope for channel 1.

20

SS1

21

TRK2

22

SS2

Channel 2 soft-start.

23

EN2

Channel 2 enable input. Used to set the emulated current slope for channel 2.

24

PGOOD2

25

COMP2

26

FB2

27

EA2_GND

28

CLKOUT

29

SGND

Local signal ground.*

30

VCB2

Boost voltage for channel 2 high-side driver.

31

HG2

Channel 2 high-side gate drive for external MOSFET.

32

ILIM2

Current limit setting input for channel 2.

DAP

Exposed die attach pad. Connect the DAP directly to SGND. (1)

Channel 1 track input.

Channel 1 soft-start.

Channel 2 track input.

Power good signal for channel 2 under-voltage and over-voltage.

Error amplifier output for channel 2.

Error amplifier input for channel 2.

Error amplifier ground sense for channel 2. (1)

Output clock. CLKOUT is shifted 90 degrees from SYNC input.

The LM3000 offers true remote ground sensing to achieve very tight line and load regulation. For best layout practice, the EA1_GND,

and EA2_GND should be tied to the ground end of the output capacitor (or output terminal) for VOUT1 and VOUT2 respectively. Inside the

LM3000, the two power ground nodes PGND1 and PGND2 are physically isolated from each other and also isolated from the internal

signal ground SGND. In order to achieve the best cross-channel noise rejection, it is advised to keep these three grounds isolated from

each other for the most part in the board layout and only tie them together at the ground terminals.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1) (2)

VIN to SGND, PGND

-0.3V to 20V

VSW1, VSW2 to SGND, PGND

-3V to 20V

(3)

-0.3V to 5.5V

VDD, VDR to SGND, PGND

VCB1, VCB2 to SGND ,PGND

24V

VCB1 to VSW1, VCB2 to VSW2

5.5V

FB1, FB2 to SGND, PGND

All other input pins to SGND, PGND

-0.3V to 3.0V

(4)

-0.3V to 5.5V

Junction Temperature (TJ-MAX)

150°C

Storage Temperature Range

-65°C to +150°C

Maximum Lead Temperature

Soldering, 5 seconds

260°C

ESD Rating

HBM (5)

2000V

(1)

(2)

(3)

(4)

(5)

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of

device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or

other conditions beyond those indicated in the Recommended Operating Conditions is not implied. Operating Range conditions indicate

the conditions at which the device is functional and the device should not be operated beyond such conditions. For ensured

specifications and conditions, see the Electrical Characteristics table.

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and

specifications.

VDD and VDR are outputs of the internal linear regulator. Under normal operating conditions where VIN > 5.5V, they must not be tied to

any external voltage source. In an application where VIN is between 3.3V to 5.5V, it is recommended to tie the VDD, VDR and VIN pins

together, especially when VIN may drop below 4.5V. In order to have better noise rejection under these conditions, a 10Ω, 1μF input

filter may be used for the VDD pin.

HG1, HG2, LG1, LG2 and CLKOUT are all output pins and should not be tied to any external power supply. COMP1 and COMP2 are

also outputs and should not be tied to any lower output impedance power source. PGOOD1 and PGOOD2 are open drain outputs, with

a pull-down resistance of about 250Ω. Each of them may be tied to an external voltage source less than 5.5V through an external

resister greater than 3kΩ, although 10kΩ and above are preferred to reduce the necessary signal ground current.

Human Body Model (HBM) is 100 pF capacitor discharged through a 1.5k resistor into each pin. Applicable standard is JESD22-A114C.

Operating Ratings (1)

Input Voltage Range

VDD = VDR = VIN (2)

VIN

−40°C to +125°C

Junction Temperature (TJ) Range

(1)

(2)

3.3V to 5.5V

3.3V to 18.5V

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of

device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or

other conditions beyond those indicated in the Recommended Operating Conditions is not implied. Operating Range conditions indicate

the conditions at which the device is functional and the device should not be operated beyond such conditions. For ensured

specifications and conditions, see the Electrical Characteristics table.

VDD and VDR are outputs of the internal linear regulator. Under normal operating conditions where VIN > 5.5V, they must not be tied to

any external voltage source. In an application where VIN is between 3.3V to 5.5V, it is recommended to tie the VDD, VDR and VIN pins

together, especially when VIN may drop below 4.5V. In order to have better noise rejection under these conditions, a 10Ω, 1μF input

filter may be used for the VDD pin.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

5

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

Electrical Characteristics

Limits in standard type are for TJ = 25°C only; limits in boldface type apply over the junction temperature (TJ) range of -40°C

to +125°C. Minimum and Maximum limits are ensured through test, design, or statistical correlation. Typical values represent

the most likely parametric norm at TJ = 25°C, and are provided for reference purposes only. Unless otherwise noted, VIN =

12.0V, IEN1 = IEN2 = 40 µA.

Symbol

VFB

Parameter

Condition

FB Pin Voltage FB1, FB2 (LM3000A)

-20°C to +85°C

Min

Typ

Max

Units

0.594

0.6

0.606

V

0.591

0.6

0.609

0.591

0.6

0.609

0.6

0.612

VFB

FB Pin Voltage FB1, FB2 (LM3000)

-20°C to +85°C

ΔVFB/VFB

Line Regulation VDD = VIN = VDR

3.3V < VIN < 5.5, COMP = 1.5V

0.15

%

Line Regulation VIN > 6V

6V < VIN < 18.5V, COMP = 1.5V

0.3

%

Load Regulation

VIN = 12.0V, 1.0V < COMP < 1.4V

0.1

%

5

mA

0.588

Iq

VIN Operating Current

ISD

VIN Shutdown Current

IEN1 , IEN2 < 5 µA

50

IEN

EN Input Threshold Current

IEN Rising

15

ILIM

Source Current ILIM1, ILIM2

VILIM1, VILIM2 = 0V

17

ISS

Soft-Start Pull-Up Current

VSS = 0.5V

5.5

COMP Pin Hiccup Thresholds

COMP Threshold High

Hysteresis

VHICCUP

Hiccup Delay

tCOOL

Cool-Down Time Until Restart

VOVP

Over-Voltage Protection Threshold

µA

35

µA

20

23

µA

8.5

11.5

µA

10

Hysteresis

tDELAY

V

2.85

V

50

mV

16

Cycles

4096

As a % of Nominal Output Voltage

110

115

Cycles

120

%

Hysteresis

3

Under-Voltage Protection Threshold

As a % of REF1, REF2 (see Block

Diagram)

85

%

VCB Pin Leakage Current

VCB - VSW = 5.5V

250

nA

RDS1

Top FET Drive Pull-Up On-Resistance

VCB - VSW = 4.5V, VCB - HG = 100

mV

3

Ω

RDS2

Top FET Drive Pull-Down On-Resistance

VCB - VSW = 4.5V, HG - VSW = 100

mV

2

Ω

RDS3

Bottom FET Drive Pull-Up On-Resistance VDR - PGND = 5V, VDR - LG = 100

mV

2

Ω

RDS4

Bottom FET Drive Pull-Down OnResistance

VDR - PGND = 5V, LG - PGND = 100

mV

1

Ω

Switching Frequency

RFRQ = 100 kΩ

VUVP

GATE DRIVE

ICB

OSCILLATOR

fSW

RFRQ = 42.2 kΩ

230

425

RFRQ = 10 kΩ

VSYNC

Threshold for Synchronization at the

FREQ/SYNC Pin

Rising

1550

200

SYNC Pulse Width

100

Maximum Duty cycle

kHz

0.6

SYNC Range

DMAX

kHz

V

Falling

tSYNC

SYNC Rise/Fall Time

kHz

575

2.2

fSYNC

tSYNC-TRS

500

1500

kHz

ns

10

85

ns

%

ERROR AMPLIFIER

IFB

ISOURCE

ISINK

6

FB Pin Bias Current

FB = 0.6V

20

nA

COMP Pin Source Current

FB = 0.5V, COMP = 1.0V

80

µA

COMP Pin Sink Current

FB = 0.7V, COMP = 0.7V

80

µA

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

Electrical Characteristics (continued)

Limits in standard type are for TJ = 25°C only; limits in boldface type apply over the junction temperature (TJ) range of -40°C

to +125°C. Minimum and Maximum limits are ensured through test, design, or statistical correlation. Typical values represent

the most likely parametric norm at TJ = 25°C, and are provided for reference purposes only. Unless otherwise noted, VIN =

12.0V, IEN1 = IEN2 = 40 µA.

Symbol

Parameter

VCOMP-HI

COMP Pin Voltage High Clamp

VCOMP-LO

COMP Pin Voltage Low Clamp

VOS-TRK

Condition

2.80

gm

Transconductance

Unity Gain Bandwidth Frequency

Typ

Max

Units

3.0

3.2

V

9.0

mV

0.48

Offset Using TRK Pin

fBW

Min

TRK = 0.45V

-9.0

0

V

1400

µS

10

MHz

INTERNAL VOLTAGE REGULATOR

VVDD

VVDD-ON

Internal Core Regulator Voltage

No External Load

5.15

V

UVLO Thresholds

VDD Rising

2.12

V

Hysteresis

0.14

1.1

V

VVDD-DO

Internal Core Regulator Dropout Voltage

No External Load

IVDD-ILIM

Internal Core Regulator Current Limit

VDD Short to Ground

80

mA

Regulator for External MOSFET Drivers

IVDR = 100 mA

5.2

V

VVDR-DO

Driver Regulator Dropout Voltage

IVDR = 100 mA

1.0

V

IVDR-ILIM

Driver Regulator Current Limit

VDR Short to Ground

450

mA

PGOOD On-Resistance

FB1 = FB2 = 0.47V

250

Ω

PGOOD High Leakage Current

VPGOOD = 5V

100

nA

WQFN-32 Package (1)

26.4

°C/W

VVDR

PGOOD OUTPUT

RPG-ON

IOH

THERMAL RESISTANCE

θJA

(1)

Junction-to-Ambient Thermal Resistance

Tested on a four layer JEDEC board. Four vias provided under the exposed pad. See JEDEC standards JESD51-5 and JESD51-7.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

7

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

Typical Performance Characteristics

8

3.3V Output Efficiency at 500 kHz

1.2V Output Efficiency at 500 kHz

Figure 2.

Figure 3.

3.3V Output Load and Line Regulation

1.2V Output Load and Line Regulation

Figure 4.

Figure 5.

FB1, FB2 Reference vs Temperature

VDD Voltage vs Temperature

Figure 6.

Figure 7.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

Typical Performance Characteristics (continued)

Soft-Start without Load

Pulse Skipping during Over-Current Condition

IL1 (5A/DIV)

VEN1 and VEN2 (5V/DIV)

VOUT1 (2V/DIV)

SW1 (5V/DIV)

VOUT2 (1V/DIV)

5 Ps/DIV

1 ms/DIV

Figure 8.

Figure 9.

No Load Soft-Start with Pre-Bias

Output Short Circuit Hiccup

VEN1 and VEN2 (5V/DIV)

VOUT1 (1V/DIV)

VOUT1 (1V/DIV)

VOUT2 (0.5V/DIV)

SW1 (10V/DIV)

1 ms/DIV

5 ms/DIV

Figure 10.

Figure 11.

Soft-Start with Load

Switch Node Short Circuit Hiccup

VEN1 and VEN2 (5V/DIV)

VOUT2 (1V/DIV)

VOUT1 (1V/DIV)

IL2 (10A/DIV)

VOUT2 (0.5V/DIV)

SW2 (5V/DIV)

1 ms/DIV

5 ms/DIV

Figure 12.

Figure 13.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

9

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

Typical Performance Characteristics (continued)

External Clock Synchronization

External Tracking

TRK1 (1V/DIV)

External Clock (1V/DIV)

FB1 (1V/DIV)

VOUT1 (2V/DIV)

VOUT1 (2V/DIV)

SW1 (10V/DIV)

5 Ps/DIV

10

20 ms/DIV

Figure 14.

Figure 15.

Error Amplifier Transconductance vs Temperature

Enable Current Threshold vs Temperature

Figure 16.

Figure 17.

Switching Frequency vs Temperature

RFRQ vs Switching Frequency

Figure 18.

Figure 19.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

BLOCK DIAGRAM

4 VIN

LG1

gmn

gm

LG1

IVIN

12 VDD

RDSON

5.2V

REGS

CURRENT

EMULATION

AND

SLOPE

COMPENSATION

ISLOPE2

1 kÖ 1 kÖ

7

VSW2

1

PGND2

2

ILIM1

9

ILIM2

32

SS2

22

TRK2

21

LG2

LG2

RDSON

SENSING

VBG

0.6V

BIAS

ASEN(s)

RAMP1

FREQ/

17 SYNC

PGND1

ASEN(s)

18 EN1

23 EN2

8

SENSING

ISLOPE1

5 VDR

VSW1

RAMP2

IFREQ

CLOCK/

PLL

++

28 CLKOUT

20 éA

+

-

OC1

++

20 éA

OC2

SYSTEM_CLOCK

+

-

SYSTEM_REF

20 SS1

8.5 éA

+

+

+

-

19 TRK1

REF1

EN2

or

FAULT

VSW1

EN1

11 VCB1

10 HG1

VSW1

14 FB1

REF1

VDR

EN2

VDR

PGND1

gm

+

+

FAULT

13 EA1_GND

EN1

VCB2

30

HG2

31

LG2

3

COMP2

25

FB2

26

VSW2

PGND2

gm

REF2

EA2_GND

27

PGOOD2

24

EN2

FB1

16 PGOOD1

FB2

VSW2

PWM LOGIC

DUTY CYCLE

AND

DRIVER

CONTROL

6 LG1

15 COMP1

REF2

EN1

or FAULT

FB1

8.5 éA

+

+

+

-

FB2

VOUT1, VOUT2

MONITOR

REF1

REF2

250Ö

250Ö

SYSTEM_REF

SGND

29

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

11

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

FUNCTIONAL DESCRIPTION

THEORY OF OPERATION

The LM3000 is a dual emulated current-mode PWM synchronous controller. Unlike traditional peak current-mode

controllers which sense the current while the high-side FET is on, the LM3000 senses current while the low-side

FET is on. It then emulates the peak current waveform and uses that information to regulate the output voltage.

The blanking time when the high-side FET first turns on that is normally associated with high-side sensing is not

needed, allowing high-side ON pulses as low as 50 ns. The LM3000 therefore has both excellent line transient

response and the ability to regulate low output voltages from high input voltages.

STARTUP

After the EN1 or EN2 current exceeds the enable ON threshold and the voltage at the VDD pin reaches 2.2V, an

internal 8.5 µA current source charges the soft-start capacitor of the enabled channel. Once soft-start is complete

the converter enters steady state operation. Current limit is enabled during soft-start in case of a short circuit at

the output. The soft-start time is calculated as:

tSS =

CSS x 0.6V

8.5 éA

(1)

To avoid current limit during startup, the soft-start time tSS should be substantially longer than the time required

to charge COUT to VOUT at the maximum output current. To meet this requirement:

tSS >

VOUT x COUT

ILIMIT ± IOUT

(2)

STARTUP INTO OUTPUT PRE-BIAS

If the output capacitor of the LM3000 has been charged up to some pre-bias level before the converter is

enabled, the chip will force the soft-start capacitor to the same voltage as the FB pin. This will cause the output

to ramp up from the existing output voltage without discharging it. During the soft-start ramp, the low-side FET is

disabled whenever the COMP voltage is below the active regulation voltage range.

LOW INPUT VOLTAGE

The LM3000 includes an internal 5.2V linear regulator connected from the VIN pin to the VDD pin. This linear

regulator feeds the logic and FET drive circuitry. For input voltages less than 5.5V, the VIN, VDD and VDR pins

can be tied together externally. This allows the full input voltage to be used for driving the power FETs and also

minimizes conduction loss in the LM3000.

TRACKING

The LM3000 has individual tracking inputs which control each output during soft-start. This allows the output

voltage slew rates to be controlled for loads that require precise sequencing. When the tracking function is not

being used the TRK1 or TRK2 pins should be connected directly to the VDD pin.

During start-up, the error amplifier will follow the lower of the SS or TRK voltages. For design margin, the softstart time tSS should be set to 75% of the minimum expected rise time of the controlling supply. In the event that

the LM3000 is enabled with a pre-biased master supply controlling track, the soft-start capacitor will control the

tracking output voltage rise time. Pulling TRK down after a normal startup will cause the output voltage to follow

the track signal.

12

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

VOUT1

RFBT1

VDD

FB1

RFBB1

TRK1

RT2

LM3000

VOUT2

TRK2

RFBT2

RT1

FB2

RFBB2

Figure 20. Tracking with VOUT1 Controlling VOUT2

Figure 20 shows a tracking example with the highest output voltage at VOUT1 controlling VOUT2. Tracking may be

set so that VOUT1 and VOUT2 both rise together. For this case, the equation governing the values of the tracking

divider resistors RT1 and RT2 is:

RT1

0.75 = VOUT1 x

RT1 + RT2

(3)

A value of 10 kΩ 1% is recommended for RT1 as a good compromise between high precision and low quiescent

current through the divider. Using an example of VOUT1 = 3.3V and VOUT2 = 1.2V, the value of RT2 is 34.4 kΩ 1%.

A timing diagram for VOUT1 controlling VOUT2 is shown in Figure 21. Note that the TRK pin must finish at least 100

mV higher than the 0.6V reference to achieve the full accuracy of the LM3000 regulation. To meet this

requirement the tracking voltage is offset by 150 mV. The tracking output voltage will reach its final value at 80%

of the controlling output voltage.

3.3V

0.8 x 3.3V

VOUT1

1.2V

VOUT2

Figure 21. Tracking with VOUT1 Controlling VOUT2

Alternatively, the tracking feature can be used to create equal slew rates for the output voltages. In order to track

properly, use the highest output voltage to control the slew rate. In this case, the tracking resistors are found

from:

RT1

VOUT2 = VOUT1 x

RT1 + RT2

(4)

Again, a value of 10 kΩ 1% is recommended for RT1. For the example case of VOUT1 = 5V and VOUT2 = 1.8V, RT2

is 17.8 kΩ 1%. A timing diagram for the case of equal slew rates is shown in Figure 22.

Either method ensures that the output voltage of the tracking supply always reaches regulation before the output

voltage of the controlling supply.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

13

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

5V

1.8V

VOUT1

1.8V

VOUT2

Figure 22. Tracking with Equal Slew Rates

The LM3000 can track the output of a master power supply by connecting a resistor divider to the TRK pins as

shown in Figure 23. For equal start times, the tracking resistors are determined by:

RT1

0.75 = VMASTER x

RT1 + RT2

(5)

VMASTER

MASTER

POWER

SUPPLY

VOUT1

RFBT1

FB1

RT2

RFBB1

TRK1

LM3000

VOUT2

TRK2

RFBT2

RT1

FB2

RFBB2

Figure 23. Tracking a Master Supply with Equal Start Time

5V

0.8 x 5V

VMASTER

3.3V

VOUT1

1.2V

VOUT2

Figure 24. Tracking a Master Supply with Equal Start Time

For equal slew rates, the circuit of Figure 25 is used. The relationship for the tracking divider is set by:

14

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

VOUT1 = VMASTER x

VOUT2 = VMASTER x

RT1 + RT2

RT1 + RT2 + RT3

RT1

RT1 + RT2 + RT3

(6)

VMASTER

VOUT1

MASTER

POWER

SUPPLY

RFBT1

FB1

RT3

RFBB1

TRK1

LM3000

RT2

VOUT2

TRK2

RFBT2

RT1

FB2

RFBB2

Figure 25. Tracking a Master Supply with Equal Slew Rates

5V

3.3V

1.2V

VMASTER

3.3V

VOUT1

1.2V

VOUT2

Figure 26. Tracking a Master Supply with Equal Slew Rates

Continuous Conduction Mode

The LM3000 controls the output voltage by adjusting the duty cycle of the power MOSFETs with trailing edge

pulse width modulation. The output inductor and capacitor filter the square wave produced as the power

MOSFETs switch the input voltage, thereby creating a regulated output voltage. The dc level of the output

voltage is determined by feedback resistors using the following equation:

VOUT = 0.6 x

RFBB + RFBT

RFBB

(7)

The output inductor current can flow from the drain to the source of the low-side MOSFET, which keeps the

converter in continuous-conduction-mode (CCM). CCM has the advantage of constant frequency and nearly

constant duty cycle (D = VOUT / VIN) over all load conditions, and also allows the converter to sink current at the

output if needed.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

15

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

FREQUENCY SETTING

The switching frequency of the internal oscillator is set by a resistor, RFRQ, connected from the FREQ/SYNC pin

to SGND. The proper resistor for a desired switching frequency fSW can be selected from the curves in the

Typical Performance Characteristics section labeled “RFRQ vs Switching Frequency” or by using the following

equation:

RFRQ =

2.48 x 1010

- 1000

fSW

fSW x 1+

3.4 x 106

where

•

fSW is the switching frequency in Hz

(8)

FREQUENCY SYNCHRONIZATION

The switching frequency of the LM3000 can be synchronized by an external clock or other fixed frequency signal

in the range of 200 kHz to 1.5 MHz. The external clock should be applied through a 100 pF coupling capacitor as

shown in Figure 27. In order for the oscillator to synchronize properly, the minimum amplitude of the SYNC

signal is 2.2V and the maximum amplitude is VDD. The minimum pulse width both positive and negative is 100

ns. The nominal dc voltage at the FREQ/SYNC pin is 0.6V, which is also the clamp voltage level for the falling

edge of the SYNC pulse. Depending on the pulse width and frequency, CSYNC may be adjusted to provide

sufficient amplitude of the signal at the FREQ/SYNC. It is possible to drive this pin directly from a 0 to 2.2V logic

output, though not recommended for the typical application.

Circuits that use an external clock should still have a resistor RFRQ connected from the FREQ/SYNC pin to

ground. RFRQ is selected using the equation from the FREQUENCY SETTING section to match the external

clock frequency. This allows the controller to continue operating at approximately the same switching frequency if

the external clock fails and the coupling capacitor on the clock side is grounded or pulled to logic high.

In the case of no external clock edges at startup, the internal oscillator will be controlled by the external set

resistor until the first clock edge is detected. After the first edge, the PLL will lock within a few clock cycles, after

which any missing edges will cause the oscillator to be programmed by RFRQ. If RFRQ is chosen to program the

oscillator very close to the external clock frequency, the PLL will lock very quickly and there will be very little

disturbance in the switching frequency.

Care must be taken to prevent errant pulses from triggering the synchronization circuitry. In circuits that will not

synchronize to an external clock, CSYNC should be connected from the FREQ/SYNC pin to SGND as a noise

filter. When a clock pulse is first detected, the LM3000 begins switching at the external clock frequency. Noise or

a short burst of clock pulses may result in variations of the switching frequency due to loss of lock by the PLL.

LM3000

CSYNC

FREQ/SYNC

100 pF

EXTERNAL CLOCK

OR CLKOUT FROM

ANOTHER LM3000

RFRQ

Figure 27. Clock Synchronization Circuit

In the case where two LM3000 controllers are used, the CLKOUT of the first controller can be used as a

synchronization input for the second controller. Note that the CLKOUT is 90 degrees out of phase with the main

controller clock, so that the four phases of the two controllers are separated for minimum input ripple current.

16

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

MOSFET GATE DRIVE

The LM3000 has two sets of gate drivers designed for driving N-channel MOSFETs in a synchronous mode.

Power for the high-side driver is supplied through the VCB pin. For the high-side gate HG to turn on the top FET,

the VCB voltage must be at least one VGS(th) greater than VIN. This voltage is supplied from a local charge pump

which consists of a Schottky diode and bootstrap capacitor, shown in Figure 28. For the Schottky, a rating of at

least 250 mA and 30V is recommended. A dual package may be used to supply both VCB1 and VCB2.

Both the bootstrap and the low-side FET driver are fed from VDR, which is the output of a 5V internal linear

regulator. This regulator has a dropout voltage of approximately 1V. The drive voltage for the top FET driver is

about VDR - 0.5 at light load condition and about VDR at normal to full load condition. This information is needed

to select the type of MOSFETs used, as well as calculate the losses in driving them.

D1

VDR

VCB

CBOOT

VIN

HG

VOUT

LM3000

SW

+

LG

Figure 28. Bootstrap Circuit

UVLO

For the case where VIN is > VDD, the VIN UVLO thresholds are determined by the VDD UVLO comparator and

the VDD dropout voltage. This sets the rising threshold for VIN at approximately 3V, with 30 mV of hysteresis.

For the case where VIN is < 5.5V and tied to VDD and VDR, the UVLO trip point is 2.12V rising. UVLO consists

of turning off the top and bottom FETs and remaining in that condition until VDD rises above 2.12V. The falling

trip point is 140 mV below the rising trip point.

CURRENT LIMIT

The current limit of the LM3000 is realized by sensing the current in the low-side FET while the output current

circulates through it. This voltage (IOUT x RDS(on)_LO) is compared against the voltage of a fixed, internal 20 µA

current source and a user-selected resistor, RLIM, connected between the switch node and the ILIM pin. Once a

current limit event is sensed, the high-side switch is disabled for the following cycle and the low-side FET is kept

on during this time. If sixteen consecutive current limit cycles occur, the part enters hiccup mode.

The value of RLIM for a desired current limit IILIMIT can be selected by the following equation:

ILIMIT x RDS(on)_LO

RLIM =

20 éA

(9)

HICCUP MODE

During hiccup mode the LM3000 disables both the high-side and low-side MOSFETs, and remains in this state

for 4096 switching cycles. After this cool down period the circuit restarts again through the normal soft-start

sequence. If the shorted fault condition persists, hiccup will retrigger once the soft-start has finished. This occurs

when the SS voltage is greater than 0.7V and switching has reached the continuous conduction mode state.

There is a coarse high-side current limit which senses the voltage across the high-side MOSFET. The threshold

is approximately 0.5V, which may provide some level of protection for a catastrophic fault. Hiccup will

immediately trigger after two consecutive high-side current limit fault events.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

17

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

POWER GOOD

Power good pins PGOOD1 and PGOOD2 are available to monitor the output status of the two channels

independently. The PGOOD1 pin connects to the output of an open drain MOSFET, which will remain open while

Channel 1 is within the normal operating range. PGOOD1 goes low (low impedance to ground) under the

following three conditions:

1. Channel 1 is turned off.

2. OVP on Channel 1.

3. UVP on Channel 1.

PGOOD2 functions in a similar manner. UVP tracks REF1, REF2 as shown in the block diagram. OVP sets a

fault which turns off the high gate and turns on the low gate. This discharges the output voltage until it has fallen

3% below the OVP threshold.

PGOOD may be pulled up through a resistor to any voltage which is < 5.5V. When using VDD for the pull-up

voltage, a typical value of 100 kΩ is used to minimize loading on VDD.

ENABLE

A fixed external voltage source and resistors to EN1 and EN2 are used to independently enable each output.

The LM3000 can be put into a low power shutdown mode by pulling the EN1 and EN2 pins to ground, or by

applying 0V to the enable resistors. During shutdown both the high-side and low-side FETs are disabled. The

quiescent current during shutdown is approximately 30 µA.

The enable pins also control the emulated current ramp amplitude by programming the current into EN1 and

EN2. The recommended range for IEN is 40 μA to 160 μA. See the Application Information section under

CONTROL LOOP COMPENSATION for the complete design method.

APPLICATION INFORMATION

The most common circuit controlled by the LM3000 is a non-isolated, synchronous buck regulator. The buck

regulator steps down the input voltage and has a duty ratio D of:

VOUT 1

x

D=

VIN K

where

•

η is the estimated converter efficiency

(10)

The following is a design example selecting components for the Typical Application Schematic of Figure 43. The

circuit is designed for two outputs of 3.3V at 8A and 1.2V at 15A from an input voltage of 6V to 18V. This circuit

is typical of a ‘brick’ module and has a height requirement of 6.5mm or less. Other assumptions used to aid in

circuit design are that the expected load is a small microprocessor or ASIC with fast load transients, and that the

type of MOSFETs used are in SO-8 or its equivalent packages such as PowerPAK ®, PQFN and LFPAK (LFPAKi).

SWITCHING FREQUENCY

The selection of switching frequency is based on the tradeoff between size, cost and efficiency. In general, a

lower frequency means larger, more expensive inductors and capacitors. A higher switching frequency generally

results in a smaller but less efficient solution, because the power MOSFET gate capacitances must be charged

and discharged more often in a given amount of time. For this application a frequency of 500 kHz is selected.

500 kHz is a good compromise between the size of the inductor and MOSFETs, transient response and

efficiency. Following the equation given for RFRQ in the FREQUENCY SETTING section, for 500 kHz operation a

42.2 kΩ 1% resistor is used.

MOSFETS

Selection of the power MOSFETs is governed by a tradeoff between size, cost and efficiency. Buck regulators

that use a controller IC and discrete MOSFETs tend to be most efficient for output currents of 4A to 20A.

18

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

Losses in the high-side FET can be broken down into conduction loss, gate charge loss and switching loss.

Conduction, or I2R loss is approximately:

PCOND_HI = D x (IOUT2 x RDS(on)_HI x 1.3) (High-side FET)

PCOND_LO = D x (IOUT2 x RDS(on)_LO x 1.3) (Low-side FET)

(11)

(12)

In the above equations the factor 1.3 accounts for the increase in MOSFET RDS(on) due to self heating.

Alternatively, the 1.3 can be ignored and the RDS(on) of the MOSFET estimated using the RDS(on) vs. Temperature

curves in the MOSFET datasheets.

The gate charge loss results from the current driving the gate capacitance of the power MOSFETs, and is

approximated as:

PDR = VIN x (QG_HI + QG_LO) x fSW

(13)

Where QG_HI and QG_LO are the total gate charge of the high-side and low-side FETs respectively at the typical

5V driver voltage. Gate charge loss differs from conduction and switching losses in that the majority of dissipation

occurs in the LM3000.

The switching loss occurs during the brief transition period as the FET turns on and off, during which both current

and voltage are present in the channel of the FET. This can be approximated as the following:

PSW_ON = VIN x IL_VL x D x RG_ON

x

QGD

VDR - VPLT2

+ CISS x Ln

VDR - VTH

VDR ± VPLT1

(14)

PSW_OFF = VIN x IL_PK x E x RG_OFF

x

QGD

VPLT2

+ CISS x Ln

VPLT2

VTH

(15)

Where QGD is the high-side FET Miller charge with a VDS swing between 0 to VIN; CISS is the input capacitance of

the high-side MOSFET in its off state with VDS = VIN. α and β are fitting coefficient numbers, which are usually

between 0.5 to 1, depending on the board level parasitic inductances and reverse recovery of the low-side power

MOSFET body diode. Under ideal condition, setting α = β = 0.5 is a good starting point. Other variables are

defined as:

IL_VL = IOUT - 0.5 x ΔIL

IL_PK = IOUT + 0.5 x ΔIL

VPLT1

VPLT2

VTH +

(16)

(17)

IL_VL

gmFET_HI

(18)

IL_PK

VTH + g

mFET_HI

(19)

(20)

(21)

RG_ON = 8.5 + RG_INT + RG_EXT

RG_OFF = 2.8 + RG_INT + RG_EXT

Switching loss is calculated for the high-side FET only. 8.5 and 2.8 represent the LM3000 high-side driver

resistance in the transient region. RG_INT is the gate resistance of the high-side FET, and RG_EXT is the external

gate resistance if applicable. RG_EXT may be used to damp out excessive parasitic ringing at the switch node.

For this example, the maximum drain-to-source voltage applied to either MOSFET is 18V. The maximum drive

voltage at the gate of the high-side MOSFET is 5V, and the maximum drive voltage for the low-side MOSFET is

5V. The selected MOSFET must be able to withstand 18V plus any ringing from drain to source, and be able to

handle at least 5V plus ringing from gate to source. If the duty cycle of the converter is small, then the high-side

MOSFET should be selected with a low gate charge in order to minimize switching loss whereas the bottom

MOSFET should have a low RDSONto minimize conduction loss.

For a typical input voltage of 12V and output currents of 8A and 12A, the MOSFET selections for the design

example are HAT2168 for the high-side MOSFET and RJK0330DPB for the low-side MOSFET.

A 3Ω resistor for RCBT is added in series with the VDR regulator output, as shown in Figure 43. This helps to

control the MOSFET turn-on and ringing at the switch node, without affecting the MOSFET turn-off.

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

19

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

To improve efficiency, 3A, 40V Schottky diodes are placed across the low-side MOSFETs. The external Schottky

diodes have a much lower forward voltage than the MOSFET body diode, and help to minimize the loss due to

the body diode recovery characteristic.

OUTPUT INDUCTORS

The first criterion for selecting an output inductor is the inductance itself. In most buck converters, this value is

based on the desired peak-to-peak ripple current, ΔIL that flows in the inductor along with the load current. As

with switching frequency, the selection of the inductor is a tradeoff between size and cost. Higher inductance

means lower ripple current and hence lower output voltage ripple. Lower inductance results in smaller, less

expensive devices. An inductance that gives a ripple current of 1/6 to 1/3 of the maximum output current is a

good starting point. (ΔIL = (1/6 to 1/3) x IOUT). Minimum inductance is calculated from this value, using the

maximum input voltage as:

LMIN =

VIN(MAX) - VOUT

xD

fSW x 'IL

(22)

By calculating in terms of amperes, volts, and megahertz, the inductance value will come out in micro henries.

The inductor ripple current is found from the minimum inductance equation:

VIN(MAX) - VOUT

xD

'IL =

fSW x LACTUAL

(23)

The second criterion is inductor saturation current rating. The LM3000 has an accurately programmed valley

current limit. During an instantaneous short, the peak inductor current can be very high due to a momentary

increase in duty cycle. Since this is limited by the coarse high-side switch current limit, it is advised to select an

inductor with a larger core saturation margin and preferably a softer roll off of the inductance value over load

current.

For the design example, standard values of 1.2 μH for the 1.2V, 15A output and 2.7 μH for the 3.3V, 8A output

are chosen to fall within the ΔIL = (1/6 to 1/3) x IOUT range.

The dc loss in the inductor is determined by its series resistance RL. The dc power dissipation is found from:

PDC = IOUT2 x RL

(24)

The ac loss can be estimated from the inductor manufacturer’s data, if available. The ac loss is set by the peakto-peak ripple current ΔIL and the switching frequency fSW.

OUTPUT CAPACITORS

The output capacitors filter the inductor ripple current and provide a source of charge for transient load

conditions. A wide range of output capacitors may be used with the LM3000 that provide excellent performance.

The best performance is typically obtained using aluminum electrolytic, tantalum, polymer, solid aluminum,

organic or niobium type chemistries in parallel with a ceramic capacitor. The ceramic capacitor provides

extremely low impedance to reduce the output ripple voltage and noise spikes, while the aluminum or other

capacitors provide a larger bulk capacitance for transient loading and series resistance for stability.

When selecting the value for the output capacitor the two performance characteristics to consider are the output

voltage ripple and transient response. The output voltage ripple can be approximated as:

'VO = 'IL x

2

RC +

1

2

8 x fSW x CO

where

•

•

•

•

•

20

ΔVO (V) is the peak to peak output voltage ripple

ΔIL (A) is the peak to peak inductor ripple current

RC (Ω) is the equivalent series resistance or ESR of the output capacitor

fSW (Hz) is the switching frequency

CO (F) is the output capacitance

Submit Documentation Feedback

(25)

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

The amount of output ripple that can be tolerated is application specific. A general recommendation is to keep

the output ripple less than 1% of the rated output voltage. The output capacitor selection will also affect the

output voltage droop and overshoot during a load transient. The peak transient of the output voltage during a

load current step is dependent on many factors. Given sufficient control loop bandwidth an approximation of the

transient voltage can be obtained from:

2

2

L x 'IO

VP =

2 x C O x VL

+

RC x C O x V L

2xL

where

•

•

VP (V) is the output voltage transient

ΔIO (A) is the load current step change

(26)

CO (F) is the output capacitance, L (H) is the value of the inductor and RC (Ω) is the series resistance of the

output capacitor. VL (V) is the minimum inductor voltage, which is duty cycle dependent.

For D < 0.5, VL = VOUT

For D > 0.5, VL = VIN - VOUT

This shows that as the input voltage approaches VOUT, the transient droop will get worse. The recovery

overshoot remains fairly constant.

The loss associated with the output capacitor series resistance can be estimated as:

PCO = RC x

'IL

2

12

(27)

Output Capacitor Design Procedure

For the design example VIN = 12V, VOUT = 3.3V, D = VOUT / VIN = 0.275, L = 2.7 μH, ΔIL = 1.8A, ΔIO = 8A and VP

= 0.15V.

To meet the transient voltage specification, the maximum RC is:

VP

RC d

'IO

(28)

For the design example, the maximum RC is 18.75 mΩ. Choose RC = 15 mΩ as the design limit.

From the equation for VP, the minimum value of CO is:

2

CO t

L x 'IO

VP x VL

1

x

1+

1-

RC x 'IO

2

VP

(29)

For D < 0.5, VL = VOUT

For D > 0.5, VL = VIN - VOUT

With RC = VP / ΔIO this reduces to:

2

CO t

L x 'IO

VP x VL

(30)

With RC = 0 this reduces to:

2

CO t

L x 'IO

2 x VP x VL

(31)

Since D < 0.5, VL = VOUT. With RC = 15 mΩ, the minimum value for CO is 218 μF.

The minimum control loop bandwidth fC is given by:

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

21

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

fC t

www.ti.com

'IO

2 x S x C O x VP

(32)

For the design example, the minimum value for fC is 39 kHz. A 220 μF, 15 mΩ polymer capacitor in parallel with

a 22 μF, 3 mΩ ceramic will meet the target output voltage ripple and transient specification.

For the 1.2V, 15A output, two 220 μF, 15 mΩ polymer capacitors in parallel with a 22 μF, 3 mΩ ceramic are

chosen to meet the target design specifications.

INPUT CAPACITORS

The input capacitors for a buck regulator are used to smooth the large current pulses drawn by the inductor and

load when the high-side MOSFET is on. Due to this large ac stress, input capacitors are usually selected on the

basis of their ac rms current rating rather than bulk capacitance. Low ESR is beneficial because it reduces the

power dissipation in the capacitors. Although any of the capacitor types mentioned in the OUTPUT

CAPACITORS section can be used, ceramic capacitors are common because of their low series resistance. In

general the input to a buck converter does not require as much bulk capacitance as the output.

The input capacitors should be selected for rms current rating and minimum ripple voltage. The equation for the

rms current and power loss of the input capacitor in a single phase can be estimated as:

ICIN(RMS) | IO x D x (1 ± D)

2

PCIN | IO x D x (1 ± D) x RCIN

where

•

•

IO (A) is the output load current

RCIN (Ω) is the series resistance of the input capacitor

(33)

Since the maximum values occur at D = 0.5, a good estimate of the input capacitor rms current rating in a single

phase is one-half of the maximum output current.

Neglecting the series inductance of the input capacitance, the input voltage ripple for a single phase can be

estimated as:

'IL

IO x D x (1 ± D)

x RCIN

+ IO +

'VIN =

CIN x fSW

2

(34)

By defining the maximum input voltage ripple, the minimum requirement for the input capacitance can be

calculated as:

IO x D x (1 ± D)

CIN t

'VIN ± IO +

'IL

2

x RCIN x fSW

(35)

For the dual output design operating 180° out of phase, the general equation for the input capacitor rms current

is approximated as:

ICIN(RMS) |

(I12 x D1) + (I22 x D2)

+ (2 x I1 x I2 x D3)

± (I1 x D1 + I2 x D2)2

(36)

Where the output currents are I1, I2 and the duty cycles are D1, D2 respectively. D3 represents the overlapping

effective duty cycle, which adds to the RMS current.

D3 = MAX(MIN(D1 ± 0.5 , D2) , 0)

+ MAX(MIN(D2 ± 0.5 , D1) , 0)

(37)

If D > 0.5 for both or D < 0.5 for both, the worst case rms current occurs with one output at full load and the other

at no load. The maximum rms current can be approximated as:

ICIN(RMS)MAX | 0.5 x MAX(I1 , I2)

(38)

22

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

If D > 0.5 for one and D < 0.5 for the other, the worst case rms current becomes:

I12 + I22

ICIN(RMS)MAX | 0.707 x

(39)

In most applications for point-of-load power supplies, the input voltage is the output of another switching

converter. This output often has a lot of bulk capacitance, which may provide adequate damping.

When the converter is connected to a remote input power source through a wiring harness, a resonant circuit is

formed by the line impedance and the input capacitors. If step input voltage transients are expected near the

maximum rating of the LM3000, a careful evaluation of the ringing and possible overshoot at the device VIN pin

should be completed. To minimize overshoot make CIN > 10 x LIN. The characteristic source impedance and

resonant frequency are:

LIN

ZS =

fS =

CIN

1

2 x S x LIN x CIN

(40)

The converter exhibits a negative input impedance which is lowest at the minimum input voltage:

ZIN = ±

VIN

2

POUT

(41)

The damping factor for the input filter is given by:

á=

1

x

2

RLIN + RCIN

ZS

+

ZS

ZIN

where

•

•

RLIN is the input wiring resistance

RCIN is the series resistance of the input capacitors

(42)

The term ZS / ZIN will always be negative due to ZIN.

When δ = 1, the input filter is critically damped. This may be difficult to achieve with practical component values.

With δ < 0.2, the input filter will exhibit significant ringing. If δ is zero or negative, there is not enough resistance

in the circuit and the input filter will sustain an oscillation.

When operating near the minimum input voltage, an aluminum electrolytic capacitor across CIN may be needed

to damp the input for a typical bench test setup. Any parallel capacitor should be evaluated for its rms current

rating. The current will split between the ceramic and aluminum capacitors based on the relative impedance at

the switching frequency. Using a square wave approximation, the rms current in each capacitor is found from:

C1 = CIN1 R1 = RCIN1 C2 = CIN2 R2 = RCIN2

X1 |

1

2.2 x S x fSW x C1

X2 |

1

2.2 x S x fSW x C2

ICIN(RMS) x

ICIN1(RMS) =

2

R2 + X2

2

2

2

(R1 + R2) + (X1 + X2)

ICIN(RMS) x

ICIN2(RMS) =

2

R1 + X1

2

2

2

(R1 + R2) + (X1 + X2)

(43)

Input Capacitor Design Procedure

Ceramic capacitors are sized to support the required rms current. Aluminum electrolytic capacitors are used for

damping. Treating each phase separately, find the minimum value for the ceramic capacitor from:

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

23

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

CIN t

www.ti.com

IO x D x (1 ± D)

'VIN x fSW

(44)

For the design example allowing 0.25V input voltage ripple, the worst case occurs for the 3.3V, 8A output at D =

0.5. The minimum value is CIN = 16 μF. For the 1.2V, 15A output, the worst case D = 1.2V / 6V = 0.2. Then CIN =

4.8 μF. Find the rms current rating for each from:

ICIN(RMS) | IO x D x (1 ± D)

(45)

Using the same criteria, results are 4A rms for the 3.3V phase and 3A rms for the 1.2V phase. Manufacturer data

for 10 μF, 25V, X5R capacitors in a 1206 package allows for 3A rms with a 20°C temperature rise. For the

design example, using two ceramic capacitors for each phase will meet both the input voltage ripple and rms

current target. Since the series resistance is so low at about 5 mΩ per capacitor, a parallel aluminum electrolytic

is used for damping. A good general rule is to make the damping capacitor at least five times the value of the

ceramic. By sizing the aluminum such that it is primarily resistive at the switching frequency, the design is greatly

simplified since the ceramic is primarily reactive. In this case the approximation for the rms current in the

damping capacitor is:

ICIN(RMS)

ICIN2(RMS) |

2.2 x S x fSW x RCIN2 x CIN1

where

•

•

•

CIN2 is the damping capacitance

RCIN2 is its series resistance

CIN1 is the ceramic capacitance

(46)

A 150 μF, 50V, 0.18Ω, 670 mA capacitor in a 10 mm x 10.2 mm package is chosen for each input. Calculated

rms current for the 3.3V phase is 322 mA, with 242 mA calculated for the 1.2V phase.

CURRENT LIMIT

For the design example, the desired current limit set point is chosen to be 150% of the maximum load current.

To account for the tolerance of the internal current source and allowing RDS(on) = 4 mΩ for the low-side MOSFET

at elevated temperature, a target of 23A is used for the 1.2V output, with 13A for the 3.3V output. Following the

equation from the CURRENT LIMIT section the values for RLIM are 4.64 kΩ, 1% for the 1.2V output and 2.67 kΩ,

1% for the 3.3V output.

TRACK

Tracking for the design example is configured such that VOUT1 is controlling VOUT2. The divider values are set so

that both outputs will rise together, with VOUT2 reaching its final value just before VOUT1. Following the method in

the TRACKING section and allowing for a 120 mV offset between FB and TRK, standard 1% values are selected

for RT1 = 10 kΩ and RT2 = 35.7 kΩ.

SOFT START

To prevent over-shoot, the soft start time is set to be longer than the time it would take to charge the output

voltage at current limit. Following the equations in the STARTUP section for VOUT1 and VOUT2:

tSS1(MIN) = (3.3V x 242 μF) / (13A - 8A) = 160 μs

tSS2(MIN) = (1.2V x 462 μF) / (23A - 15A) = 69 μs

(47)

(48)

Choosing a value of CSS1 = 27 nF, the soft start time is:

tSS1 = (27 nF x 0.6V) / 8.5 μA = 1.9 ms

(49)

To ensure that VOUT2 tracks VOUT1, tSS2 is set at two-thirds of tSS1 by making CSS2 = 18 nF.

VDD, VDR and VCB CAPACITORS

VDD is used as the supply for the internal control and logic circuitry. A 1 μF ceramic capacitor provides sufficient

filtering for VDD.

24

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

VDR provides power for both the high-side and low-side MOSGET gate drives, and is sized to meet the total

gate drive current. Allowing for ΔVVDR = 100 mV of ripple, the minimum value for CVDR is found from:

QG_HI + QG_LO

CVDR t

'VVDR

(50)

Using QG_HI = 15 nC and QG_LO = 30 nC with a 5V gate drive, the minimum value for CVDR = 0.45 μF.

VCB provides power for the high-side gate drive, and is sized to meet the required gate drive current. Allowing

for ΔVVCB = 100 mV of ripple, the minimum value for CBOOT is found from:

QG_HI

CBOOT t

'VVCB

(51)

To use the minimum number of different components, CVDR and CBOOT are also selected as 1 μF ceramic for the

design example.

CONTROL LOOP COMPENSATION

The LM3000 uses emulated peak current-mode PWM control to correct changes in output voltage due to line and

load transients. This unique architecture combines the fast line transient response of peak current-mode control

with the ability to regulate at very low duty cycles. In order to facilitate the use of MOSFET RDS(on) sensing, the

control ramp is set by the enable voltage and a resistor to the enable pin. This stabilizes the modulator gain from

variations in MOSFET resistance over temperature, providing a robust design solution.

The control loop is comprised of two parts. The first is the power stage, which consists of the duty cycle

modulator, output filter and load. The second part is the error amplifier, which is a transconductance amplifier

with a typical gm of 1400 μmho (or 1400 μS). Figure 29 shows the power stage and error amplifier components.

L

RL

VOUT

CO1

VIN

+

-

+

CO2

CFF

RFBT

RO

HG

RC1

PWM

LG

DRIVERS

+

Ð

+

RS = RDS(on)

A

+

RFBB

RC2

+

-

-

PGND

VSW

0.75V

gm

+

Clamped to

0.5V min

3V max

FB

RCOMP

+

-

+

-

COMP

VREF

EA_GND

CHF

CCOMP

Figure 29. Power Stage and Error Amplifier

The power stage transfer function (also called the control-to-output transfer function) in a buck converter can be

written as:

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

25

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

vO

1+

= AVP x

vC

1+

www.ti.com

s

öZ

s

s2

+

öP x QP öP2

(52)

Where:

AVP =

Km

KD

KD = 1 +

1

Km =

(D ± 0.5) x Ri x

Km x R i

ö P x QP =

öZ =

RO

T

+ KSL

L

1

CO x RC

KD

öP2 =

L

+ CO x (Km x Ri + RC)

RO

KD

L x CO

(53)

With:

D=

VO

VIN

Ri = A x R S

T=

1

fSW

(54)

For the emulated peak current-mode control, Km is the dc modulator gain and Ri is the current-sense gain. KSL is

the proportional slope compensation, which is set by the enable resistor REN and enable voltage VEN.

Figure 30 shows a more detailed view of the current sense amplifier, which includes a three stage filter for

increased noise immunity. The effective gain and phase are shown in Figure 31 and Figure 32. The equivalent

current sense gain A = 7.

104k

11k

3.2k

-

VSW

20 pF

+

PGND

11k

3.2k

104k

15.5k

CS

AMPLIFIER

2.6 pF

SAMPLE

31k

0.75V

5.6 pF

TO RAMP

GENERATOR

Figure 30. Current Sense Amplifier and Filter

26

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

Figure 31. Current Sense Amplifier Gain

Figure 32. Current Sense Amplifier Phase

A relatively high value of slope compensating ramp is used to stabilize the gain. This minimizes the effect of the

current sense filter on the control loop and swamps out the need for a sampling-gain term. When designing

within the recommended operating range, there is no tendency toward sub-harmonic oscillation. The proportional

slope compensation is defined as:

ISL x KSW

ISL = 8.05 éA

KSL =

IEN

fSW

KSW = 1 +

3400000

IEN =

VEN ± 0.75

REN + 2000

(55)

ISL is the internal current source scale factor, KSW is the switching frequency correction factor and IEN is the

external enable current. The recommended range for IEN is 40 μA to 160 μA. With VEN = 5V, this corresponds to

a range for REN of 25 kΩ to 100 kΩ. For operation below 4.2V input, the maximum enable current is limited, as

shown in Figure 33. At the minimum input of 3.3V, a value of 80 μA maximum corresponds to REN = 50 kΩ with

VEN = 5V. The minimum enable current is set by the enable bias circuit to ensure proper turn-on above the

threshold. A minimum enable voltage of 3V is recommended to keep the temperature coefficient of the 0.75V

internal VBE from becoming a significant error term.

Figure 33. Maximum Enable Current vs. Input Voltage

Typical frequency response of the gain and the phase for the power stage are shown in Figure 34 and Figure 35.

It is designed for VIN = 12V, VOUT = 3.3V, IOUT = 8A, VEN = 5V and a switching frequency of 500 kHz. The power

stage component values are:

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

27

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

L = 2.7 μH, RL = 3.4 mΩ, CO1 = 220 μF, RC1 = 15 mΩ, CO2 = 22 μF, RC2 = 3 mΩ, RO = VOUT / IOUT = 0.41Ω, RS =

RDS(on) = 4 mΩ and REN = 43 kΩ.

Figure 34. Power Stage Gain

Figure 35. Power Stage Phase

The effective total PWM ramp height is controlled by REN. Higher REN creates a higher ramp voltage, providing

more noise immunity and less variation in the modulator gain over temperature. Lower REN requires less RC

(output capacitor ESR) for the desired phase margin and a more ideal current-mode behavior.

Figure 36 shows the transconductance amplifier network, which takes the output impedance of the amplifier and

the internal filter into account. To simplify the analysis, the 12.75 kΩ and 10 pF internal filter is absorbed into the

transconductance amplifier. This produces an equivalent REA = 15 MΩ and CBW = 22 pF for an effective 10 MHz

unity gain bandwidth.

gm

FB

VREF

+

+

-

3 pF

15M

COMPF

COMP

PWM

12.75k

4.2k

+

10 pF

5 pF

EA_GND

COMP

gm

FB

VREF

+

+

-

PWM

REA

CBW

15M

22 pF

+

-

EA_GND

Figure 36. Equivalent Transconductance Amplifier and COMP Filter

28

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

Figure 37. Transconductance Amplifier Open Loop

Gain

Figure 38. Transconductance Amplifier Open Loop

Phase

Assuming a pole at the origin, the simplified equation for the error amplifier transfer function can be written in

terms of the mid-band gain as:

vC

vO

=-

AVM

KHF

öZEA

s

1+ ö

s

FZ

x

x

s

s

1+

1+

öHF

öFP

1+

(56)

Where:

AVM = KFB x gm x RCOMP

CHF + CBW

KHF = 1 +

öFZ =

CCOMP

1

CFF x RFBT

öHF =

KFB =

öZEA =

öFP =

RFBB

RFBB + RFBT

1

CCOMP x RCOMP

1

CFF x KFB x RFBT

CHF + CBW + CCOMP

(CHF + CBW) x CCOMP x RCOMP

(57)

In general, the goal of the compensation circuit is to give high dc gain, a bandwidth that is between one-fifth and

one-tenth of the switching frequency, and at least 45° of phase margin.

Control Loop Design Procedure

Once the power stage design is complete, the power stage components are used to determine the proper

frequency compensation. By equating the power stage transfer function to the error amplifier transfer function

term by term, the control loop design procedure targets an ideal single-pole system response.

The compensation components will scale from the feedback divider ratio and selection of the bottom feedback

divider resistor. A maximum value for the divider current is typically set at 1 mA. Using a divider current of 200

μA will allow for a reasonable range of values. For the bottom feedback resistor RFBB = VREF / 200 μA = 3 kΩ.

Choosing a standard 1% value of 2.94 kΩ, the top feedback resistor is found from:

RFBT = RFBB x

VOUT

VREF

-1

(58)

For VOUT = 3.3V and VREF = 0.6V, RFBT = 13.2 kΩ.

Based on the previously defined power stage values, calculate general terms:

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

29

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

D=

VO

www.ti.com

R i = A x RS

VIN

KSW = 1 +

1

T=

fSW

RFBB

fSW

3400000

KFB =

RFBB + RFBT

(59)

For the design example D = 0.275, Ri = 0.028Ω, T = 2 μs, KSW = 1.147 and KFB = 0.1818.

Choose a target crossover frequency fC greater than the minimum control loop bandwidth from the OUTPUT

INDUCTORS section. This is typically set between 1/10 and 1/5 of the switching frequency.

öC = 2 x S x fC

öSW = 2 x S x fSW

öBW = 2 x S x fBW

(60)

Choosing fC = 100 kHz for the design example ωC = 628 krad/sec. The switching frequency ωSW = 3.14 Mrad/sec

and the error amplifier bandwidth ωBW = 62.8 Mrad/sec.

Calculate the parallel equivalent CO and RC at the target crossover frequency:

C1 = CO1

R1 = RC1

X1 =

C2 = CO2

1

öC x C1

Z=

X2 =

2

R12 + X1 x

R2 = RC2

1

öC x C2

R22 + X2

2

2

2

(R1 + R2) + (X1 + X2)

A = TAN

CO =

-1

X1

-1 X1 + X2

-1 X2

- TAN

+ TAN

R1 + R2

R1

R2

1

öC x Z x SIN(A)

RC = Z x COS(A)

(61)

For the design example X1 = 0.00723, X2 = 0.0723, Z = 0.01478 and A = 0.6304. The parallel equivalent CO =

183 μF and RC = 11.9 mΩ.

Find the optimal value of the enable current:

IEN = ISL x KSW x

L

x

CO

KFB

RC

-

1

1

-1

+ RC x

KFB

RO

Ri x 1 -

RC

RO x KFB

(62)

If IEN is not within the range of 40μA to 160μA use either the minimum or maximum limit. Find REN from:

REN =

VEN ± 0.75

IEN

- 2000

(63)

For the design example IEN = 95.5 μA and REN = 44.7 kΩ. Choosing a standard value of 43 kΩ, IEN = 94.4 μA.

Calculate other general terms:

30

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

KSL =

ISL x KSW

1

Km =

IEN

KD = 1 +

(D ± 0.5) x Ri x T + KSL

L

Km x Ri

RO

(64)

For the design example KSL = 0.0978, Km = 10.7 and KD = 1.73.

If the enable resistor has been adjusted from the nominal value to provide more noise immunity or to meet the

minimum input voltage limit, calculate the optimal value of RC. The minimum value of RC to maintain adequate

phase margin for stability is about half this value.

RC =

KFB x L

Km x Ri x CO

(65)

Checking for the design example RC = 9.1 mΩ.

Calculate the compensation components:

gm

CBW = ö

BW

CHF =

CCOMP =

CFF =

gm x Km x RC

öC x öSW x L

KFB x gm x Km

öC x KD

RCOMP =

C O x RC

KFB x RFBT

- CBW

- (CHF + CBW)

KFB x L

KD x RC x CCOMP

(66)

For the design example, the calculated values are CBW = 22 pF, CFF = 904 pF, CHF = 11 pF, CCOMP = 2505 pF

and RCOMP = 9523Ω.

Using standard values of CFF = 820 pF, CHF = 10 pF, CCOMP = 2200 pF and RCOMP = 10 kΩ, the error amplifier

plots of gain and phase are shown in Figure 39 and Figure 40.

Figure 39. Error Amplifier Gain

Figure 40. Error Amplifier Phase

Submit Documentation Feedback

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

31

�LM3000

SNVS612B – JULY 2009 – REVISED APRIL 2013

www.ti.com

The complete control loop transfer function is equal to the product of the power stage transfer function and error

amplifier transfer function. For the Bode plots, the overall loop gain is the equal to the sum in dB and the overall

phase is equal to the sum in degrees. Results are shown in Figure 41 and Figure 42. The crossover frequency is

100 kHz with a phase margin of 75°.

Figure 41. Control Loop Gain

Figure 42. Control Loop Phase

Compensator design for the 1.2V output is similar. With VREF = 0.6V, the feedback divider resistors are chosen

as RFBB = RFBT = 22.6 kΩ. This results in a divider current of about 25 μA, which is considered to be the

minimum acceptable level. With VEN = 5V, the nearest standard value to meet the optimal enable current is REN

= 62 kΩ. For a target crossover frequency of 100 kHz, standard values are CFF = 220 pF, CHF = 10 pF, CCOMP =

2200 pF and RCOMP = 10 kΩ.

For the small-signal analysis, it is assumed that the control voltage at the COMP pin is dc. In practice, the output

ripple voltage is amplified by the error amplifier gain at the switching frequency, which appears at the COMP pin

adding to the control ramp. This tends to reduce the modulator gain, which may lower the actual control loop

crossover frequency.

Efficiency and Thermal Considerations

The total power dissipated in the power components can be obtained by adding together the loss as mentioned

in the MOSFET, input capacitor, output capacitor and output inductor sections.

The efficiency is defined as:

POUT

K=

POUT + PTOTAL_LOSS

(67)

The highest power dissipating components are the power MOSFETs. The easiest way to determine the power

dissipated in the MOSFETs is to measure the total conversion loss (PIN - POUT), then subtract the power loss in

the capacitors, inductors and LM3000. The resulting power loss is primarily in the switching MOSFETs. Selecting

MOSFETs with exposed pads will aid the power dissipation of these devices. Careful attention to RDS(on) at high

temperature should be observed.

LM3000 OPERATING LOSS

This term accounts for the current drawn at the VIN pin, used for driving the logic circuitry and the power

MOSFETs. For the LM3000, this current is equal to the steady state operating current Iq plus the MOSFET gate

charge current IGC, which is defined as:

IGC = (QG_HI + QG_LO) x fSW

PD = VIN x (Iq + IGC)

(68)

where

•

32

PD represents the total power dissipated in the LM3000

Submit Documentation Feedback

(69)

Copyright © 2009–2013, Texas Instruments Incorporated

Product Folder Links: LM3000

�LM3000

www.ti.com

SNVS612B – JULY 2009 – REVISED APRIL 2013

Iq is about 5 mA from the Electrical Characteristics table. The LM3000 has an exposed thermal pad to aid power

dissipation.

Layout Considerations