LM5143-Q1

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

LM5143-Q1 Automotive 3.5-V to 65-V Dual Synchronous Buck Controller With Low IQ

1 Features

2 Applications

•

•

•

•

•

•

•

•

•

•

•

•

AEC-Q100 qualified for automotive applications:

– Device temperature grade 1: –40°C to +125°C

ambient operating temperature

Functional Safety-Capable

– Documentation available to aid functional safety

system design

Versatile synchronous buck DC/DC controller

– Wide input voltage range of 3.5 V to 65 V

– 1% accurate, fixed 3.3-V, 5-V, or adjustable

outputs from 0.6 V to 55 V

– 150°C maximum junction temperature

– Shutdown mode current: 4 µA typical

– No-load standby current: 15 µA typical

Two interleaved synchronous buck channels

– Dual-channel or single-output multiphase

– 65-ns tON(min) for high VIN/VOUT ratio

– 60-ns tOFF(min) for low dropout

Inherent protection features for robust design

– Hiccup-mode overcurrent protection

– Independent ENABLE and PGOOD functions

– VCC, VDDA, and gate-drive UVLO protection

– Thermal shutdown protection with hysteresis

Optimized for ultra-low EMI requirements

– Slew-rate controlled adaptive gate drivers

– Spread spectrum reduces peak emissions

– Optimized for CISPR 25 Class 5 requirements

Switching frequency from 100 kHz to 2.2 MHz

– SYNC in and SYNC out capability

– Selectable diode emulation or FPWM

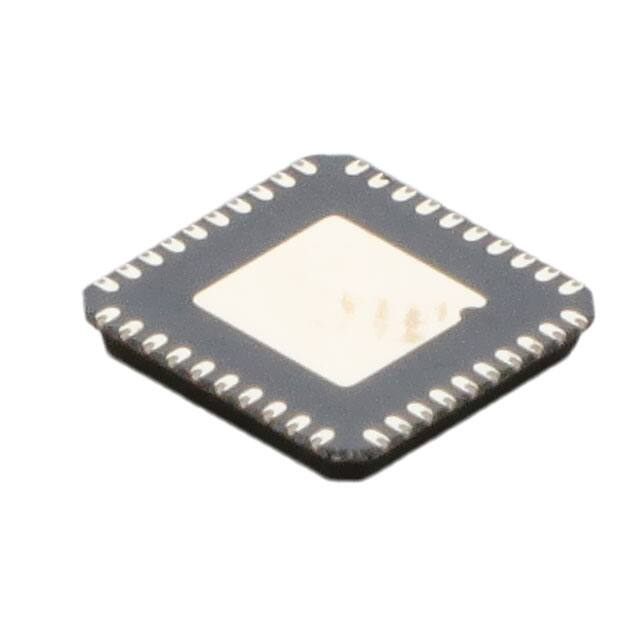

VQFNP-40 pacakge with wettable flank pins

Create a custom design using the LM5143-Q1 with

WEBENCH® Power Designer

Automotive electronic systems

Infotainment systems, instrument clusters

Advanced driver assistance systems (ADAS)

3 Description

The LM5143-Q1 is a 65-V synchronous buck DC/DC

controller for high-current single or dual outputs.

The device uses an interleaved, stackable, peak

current-mode control architecture for easy loop

compensation, fast transient response, excellent load

and line regulation, and accurate current sharing with

paralleled phases for higher output current. A highside switch minimum on-time of 65 ns gives large

step-down ratios, enabling the direct conversion from

12-V, 24-V, or 48-V automotive inputs to low-voltage

rails for reduced system complexity and solution cost.

The LM5143-Q1 continues to operate during input

voltage dips as low as 3.5 V, at nearly 100% duty

cycle if needed.

Current is sensed using the inductor DCR for highest

efficiency or an optional shunt resistor for high

accuracy. The 15-μA no-load quiescent current with

the output voltage in regulation extends operating

run-time in battery-powered systems. Power the

LM5143-Q1 from the output of the switching regulator

or another available source for even lower input

quiescent current and power loss.

Device Information

PACKAGE(1)

PART NUMBER

LM5143-Q1

(1)

VQFNP (40)

BODY SIZE (NOM)

6.00 mm × 6.00 mm

For all available packages, see the orderable addendum at

the end of the data sheet.

VIN = 3.5 V...65 V

VDDA

CIN

HB1

VOUT1 = 3.3 V

IOUT1 = 10 A R

CO1

VCC

VIN FB1 FB2 MODE

HB2

QH1

S1

QH2

LO1

HO1

HO2

HOL1

HOL2

SW1

SW2

LO1

LOL1

LO2

LOL2

QL1

PGND1

VIN

LM5143-Q1

RS2

VOUT2 = 5 V

IOUT2 = 10 A

CO2

QL2

PGND2

EN1

EN2

RT

PG2

PG1

LO2

VIN

SYNCOUT

CS1

VOUT1

DEMB

CS2

VOUT2

COMP1

COMP2

VCCX

AGND SS1 RES SS2 VDDA DITH

* VOUT1 tracks VIN if VIN < 3.7 V

VOUT2 tracks VIN if VIN < 5.4 V

High-Efficiency Dual Step-Down Regulator

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Description (continued).................................................. 3

6 Pin Configuration and Functions...................................4

6.1 Wettable Flanks.......................................................... 6

7 Specifications.................................................................. 7

7.1 Absolute Maximum Ratings ....................................... 7

7.2 ESD Ratings .............................................................. 7

7.3 Recommended Operating Conditions ........................8

7.4 Thermal Information ...................................................8

7.5 Electrical Characteristics ............................................8

7.6 Switching Characteristics .........................................12

7.7 Typical Characteristics.............................................. 13

8 Detailed Description......................................................18

8.1 Overview................................................................... 18

8.2 Functional Block Diagram......................................... 19

8.3 Feature Description...................................................20

8.4 Device Functional Modes..........................................32

9 Application and Implementation.................................. 33

9.1 Application Information............................................. 33

9.2 Typical Applications.................................................. 41

10 Power Supply Recommendations..............................52

11 Layout........................................................................... 53

11.1 Layout Guidelines................................................... 53

11.2 Layout Example...................................................... 56

12 Device and Documentation Support..........................58

12.1 Device Support....................................................... 58

12.2 Documentation Support.......................................... 59

12.3 Receiving Notification of Documentation Updates..59

12.4 Support Resources................................................. 59

12.5 Trademarks............................................................. 60

12.6 Electrostatic Discharge Caution..............................60

12.7 Glossary..................................................................60

13 Mechanical, Packaging, and Orderable

Information.................................................................... 60

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision B (October 2019) to Revision C (June 2021)

Page

• Updated Section 1 to include functional safety bullet......................................................................................... 1

• Removed "DC/DC" from data sheet title.............................................................................................................1

• Updated the numbering format for tables, figures and cross-references throughout the document...................1

• Added the Mode pin to the Absolute Maximum Ratings and Recommended Operating Conditions .................7

• Changed resistor value from 100 k to 220 k for tSYNCOUT1 and tSYNCOUT2 ........................................................ 8

• Added note in Section 9.2.1.2.7 .......................................................................................................................45

• Updated Section 11.2 .......................................................................................................................................56

• Added Table 12-1 in Section 12 .......................................................................................................................58

Changes from Revision A (May 2019) to Revision B (October 2019)

Page

• Changed device status from Advance Information to Production Data ............................................................. 1

2

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

5 Description (continued)

Several features are included to simplify compliance with CISPR 25 and automotive EMI requirements.

Adaptively timed, high-current MOSFET gate drivers with adjustable slew rate control minimize body diode

conduction during switching transitions, reducing switching losses and improving thermal and EMI performance

at high input voltage and high switching frequency. To reduce input capacitor ripple current and EMI filter size,

180° interleaved operation is provided for two outputs. A 90° out-of-phase clock output works well for cascaded,

multi-channel, or multi-phase power stages. Resistor-adjustable switching frequency as high as 2.2 MHz can

be synchronized to an external clock source up to 2.5 MHz to eliminate beat frequencies in noise-sensitive

applications. Optional triangular spread spectrum modulation further improves the EMI signature.

Additional features of the LM5143-Q1 include 150°C maximum junction temperature operation, user-selectable

diode emulation for lower current consumption at light-load conditions, configurable soft-start functions, opendrain Power-Good flags for fault reporting and output monitoring, independent enable inputs, monotonic start-up

into prebiased loads, integrated VCC bias supply regulator, programmable hiccup-mode overload protection, and

thermal shutdown protection with automatic recovery.

The LM5143-Q1 controller comes in a 6-mm × 6-mm thermally-enhanced, 40-pin VQFNP package with wettable

flank pins to facilitate optical inspection during manufacturing.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

3

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

EN2

SYNCOUT

DITH

RT

VDDA

AGND

MODE

DEMB

RES

EN1

40

39

38

37

36

35

34

33

32

31

6 Pin Configuration and Functions

SS2

1

30

SS1

COMP2

2

29

COMP1

FB2

3

28

FB1

CS2

4

27

CS1

VOUT2

5

26

VOUT1

Exposed Pad (EP) on Bottom

Connect to Ground

SW1

HB1

20

21

19

10

LOL1

SW2

18

HO1

LO1

22

17

9

PGND1

HO2

16

HOL1

VCC

23

15

8

VCC

HOL2

14

PG1

PGND2

24

13

7

LO2

PG2

12

VIN

LOL2

25

11

6

HB2

VCCX

Connect Exposed Pad on the bottom to AGND and PGND on the PCB.

Figure 6-1. RWG Package 40-Pin VQFNP with Wettable Flanks (Top View)

4

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

Table 6-1. Pin Functions

PIN

NO.

NAME

I/O (1)

DESCRIPTION

1

SS2

I

Channel 2 soft-start programming pin. An external ceramic capacitor and an internal 20-μA current source

set the ramp rate of the internal error amplifier reference during soft start. Pulling SS2 below 150 mV turns

off the channel 2 gate driver outputs, but all the other functions remain active.

2

COMP2

O

Output of the channel 2 transconductance error amplifier. COMP2 is high impedance in interleave or slave

mode.

3

FB2

I

Feedback input of channel 2. Connect FB2 to VDDA for a 3.3-V output or connect FB2 to AGND for a fixed

5-V output. A resistive divider from VOUT2 to FB2 sets the output voltage level between 0.6 V and 55 V.

The regulation threshold at FB2 is 0.6 V.

4

CS2

I

Channel 2 current sense amplifier input. Connect CS2 to the inductor side of the external current sense

resistor (or to the relevant sense capacitor terminal if inductor DCR current sensing is used) using a

low-current Kelvin connection.

5

VOUT2

I

Output voltage sense and the current sense amplifier input of channel 2. Connect VOUT2 to the output side

of the channel 2 current sense resistor (or to the relevant sense capacitor terminal if inductor DCR current

sensing is used).

6

VCCX

P

Optional input for an external bias supply. If VVCCX > 4.3 V, VCCX is internally connected to VCC and the

internal VCC regulator is disabled. Connect a ceramic capacitor between VCCX and PGND.

7

PG2

O

An open-collector output which goes low if VOUT2 is outside a specified regulation window.

8

HOL2

O

Channel 2 high-side gate driver turnoff output.

9

HO2

O

Channel 2 high-side gate driver turnon output.

10

SW2

P

Switching node of the channel 2 buck regulator. Connect to the bootstrap capacitor, the source terminal of

the high-side MOSFET, and the drain terminal of the low-side MOSFET.

11

HB2

P

Channel 2 high-side driver supply for bootstrap gate drive.

12

LOL2

O

Channel 2 low-side gate driver turnoff output.

13

LO2

O

Channel 2 low-side gate driver turnon output.

14

PGND2

G

Power ground connection pin for low-side NMOS gate driver.

VCC

P

VCC bias supply pin. Pins 15 and 16 must to be connected together on the PCB. Connect ceramic

capacitors between VCC and PGND1 and between VCC and PGND2.

17

PGND1

G

Power ground connection pin for low-side NMOS gate driver.

18

LO1

O

Channel 1 low-side gate driver turnon output.

19

LOL1

O

Channel 1 low-side gate driver turnoff output.

20

HB1

P

Channel 1 high-side driver supply for bootstrap gate drive.

21

SW1

P

Switching node of the channel 1 buck regulator. Connect to the channel 1 bootstrap capacitor, the source

terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET.

22

HO1

O

Channel 1 high-side gate driver turnon output.

23

HOL1

O

Channel 1 high-side gate driver turnoff output.

24

PG1

O

An open-collector output that goes low if VOUT1 is outside a specified regulation window.

25

VIN

P

Supply voltage input source for the VCC regulators.

26

VOUT1

I

Output voltage sense and the current sense amplifier input of channel 1. Connect VOUT1 to the output side

of the channel 1 current sense resistor (or to the relevant sense capacitor terminal if inductor DCR current

sensing is used).

27

CS1

I

Channel 1 current sense amplifier input. Connect CS1 to the inductor side of the external current sense

resistor (or to the relevant sense capacitor terminal if inductor DCR current sensing is used) using a

low-current Kelvin connection.

28

FB1

I

Feedback input of channel 1. Connect the FB1 pin to VDDA for a 3.3-V output or connect FB1 to AGND for

a 5-V output. A resistive divider from VOUT1 to FB1 sets the output voltage level between 0.6 V and 55 V.

The regulation threshold at FB1 is 0.6 V.

29

COMP1

O

Output of the channel 1 transconductance error amplifier (EA).

30

SS1

I

Channel 1 soft-start programming pin. An external capacitor and an internal 20-μA current source set the

ramp rate of the internal error amplifier reference during soft start. Pulling the SS1 voltage below 150 mV

turns off the channel 1 gate driver outputs, but the all the other functions remain active.

15, 16

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

5

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

Table 6-1. Pin Functions (continued)

PIN

NO.

31

NAME

EN1

I/O (1)

DESCRIPTION

I

An active high input (VEN1 > 2 V) enables Output 1. If Outputs 1 and 2 are disabled, the LM5143-Q1 is in

shutdown mode unless a SYNC signal is present at DEMB. EN1 must never be floating.

32

RES

O

Restart timer pin. An external capacitor configures the hiccup-mode current limiting. A capacitor at the RES

pin determines the time the controller remains off before automatically restarting in hiccup mode. The two

regulator channels operate independently. One channel can operate in normal mode while the other is

in hiccup-mode overload protection. The hiccup mode commences when either channel experiences 512

consecutive PWM cycles with cycle-by-cycle current limiting. Connect RES to VDDA during power-up to

disable hiccup-mode protection.

33

DEMB

I

Diode Emulation pin. Connect DEMB to AGND to enable diode emulation mode. Connect DEMB to VDDA

to operate the LM5143-Q1 in forced PWM (FPWM) mode with continuous conduction at light loads. DEMB

can also be used as a synchronization input to synchronize the internal oscillator to an external clock.

34

MODE

I

Connect MODE to AGND or VDDA for dual-output or interleaved single-output operation, respectively. This

also configures the LM5143-Q1 with an EA transconductance of 1200 µS. Connecting a 10-kΩ resistor

between MODE and AGND sets the LM5143-Q1 for dual-output operation with an ultra-low IQ mode and an

EA transconductance of 60 µS.

35

AGND

G

Analog ground connection. Ground return for the internal voltage reference and analog circuits.

36

VDDA

O

Internal analog bias regulator output. Connect a ceramic decoupling capacitor from VDDA to AGND.

37

RT

I

Frequency programming pin. A resistor from RT to AGND sets the oscillator frequency between 100 kHz

and 2.2 MHz.

38

DITH

I

A capacitor connected between the DITH pin and AGND is charged and discharged with a 20-µA current

source. If dithering is enabled, the voltage on the DITH pin ramps up and down modulating the oscillator

frequency between –5% and +5% of the internal oscillator. Connecting DITH to VDDA during power-up

disables the dither feature. DITH is ignored if an external synchronization clock is used.

39

SYNCOUT

O

SYNCOUT is a logic level signal with a rising edge approximately 90° lagging HO2 (or 90° leading HO1).

When the SYNCOUT signal is used to synchronize a second LM5143-Q1 controller, all phases are 90° out

of phase.

40

EN2

I

An active high input (VEN2 > 2 V) enables Output 2. If Outputs 1 and 2 are disabled, the LM5143-Q1 is in

shutdown mode unless a SYNC signal is present on DEMB. EN2 must never be floating.

(1)

P = Power, G = Ground, I = Input, O = Output

6.1 Wettable Flanks

100% automated visual inspection (AVI) post-assembly is typically required to meet requirements for high

reliability and robustness. Standard quad-flat no-lead (QFN) packages do not have solderable or exposed pins

and terminals that are easily viewed. It is therefore difficult to visually determine whether or not the package is

successfully soldered onto the printed-circuit board (PCB). The wettable-flank process was developed to resolve

the issue of side-lead wetting of leadless packaging. The LM5143-Q1 is assembled using a 40-pin VQFNP

package with wettable flanks to provide a visual indicator of solderability, which reduces the inspection time and

manufacturing costs.

6

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

7 Specifications

7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted)(1)

MIN

VIN to PGND

–0.3

70

SW1, SW2 to PGND

–0.3

70

SW1, SW2 to PGND (20-ns transient)

HB1 to SW1, HB2 to SW2

HO1 to SW1, HOL1 to SW1, HO2 to SW2, HOL2 to SW2

HO1 to SW1, HOL1 to SW1, HO2 to SW2, HOL2 to SW2 (20-ns transient)

UNIT

–5

–0.3

HB1 to SW1, HB2 to SW2 (20-ns transient)

Input voltage

MAX

6.5

–5

–0.3

VHB + 0.3

–5

–0.3

LO1, LOL1, LO2, LOL2 to PGND (20-ns transient)

–1.5

VVCC + 0.3

SS1, SS2, COMP1, COMP2, RES, RT, MODE, DITH to AGND

–0.3

VVDDA + 0.3

EN1, EN2 to PGND

–0.3

70

VCC, VCCX, VDDA, PG1, PG2, DEMB, FB1, FB2 to AGND

–0.3

6.5

VOUT1, VOUT2, CS1, CS2

–0.3

60

VOUT1 to CS1, VOUT2 to CS2

–0.3

0.3

PGND to

AGND

–0.3

0.3

V

Operating junction temperature, TJ

–40

150

°C

Storage temperature, Tstg

–40

150

°C

(1)

VVCC + 0.3

V

LO1, LOL1, LO2, LOL2 to PGND

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under

Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

7.2 ESD Ratings

VALUE

UNIT

±2000

V

Corner pins

±750

V

Other pins

±500

V

Human body model (HBM), per AEC-Q100-002 (1)

HBM ESD Classification Level 2

V(ESD)

(1)

Electrostatic discharge

Charge device model (CDM), per AEC-Q100-011,

CDM ESD Classification Level C4B

AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

7

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted).

MIN

Input voltage

range

VIN

TJ

VIN to PGND

–0.3

SW1, SW2 to PGND

–0.3

HB1 to SW1, HB2 to SW2

–0.3

HO1 to SW1, HOL1 to SW1, HO2 to SW2, HOL2 to SW2

–0.3

LO1, LOL1, LO2, LOL2 to PGND

–0.3

FB1, FB2, SS1, SS2, COMP1, COMP2, RES, DEMB, RT,

MODE, DITH to AGND

–0.3

EN1, EN2 to PGND

–0.3

VCC, VCCX, VDDA to PGND

–0.3

VOUT1, VOUT2, CS1, CS2 to PGND

NOM

MAX

UNIT

65

65

5

5.25

VHB + 0.3

5

5.25

V

5.25

65

5

5.25

–0.3

55

PGND to AGND

–0.3

0.3

Operating

junction

temperature

–40

150

°C

7.4 Thermal Information

LM5143-Q1

THERMAL METRIC(1)

RWG (VQFNP)

UNIT

40 PINS

RΘJA

Junction-to-ambient thermal resistance

34.8

°C/W

RΘJC(top)

Junction-to-case (top) thermal resistance

22.8

°C/W

RΘJB

Junction-to-board thermal resistance

9.5

°C/W

RΘJC(bot)

Junction-to-case (bottom) thermal resistance

1.3

°C/W

ΨJB

Junction-to-board characterization parameter

9.4

°C/W

ΨJT

Junction-to-top characterization parameter

0.3

°C/W

(1)

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

7.5 Electrical Characteristics

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted), Typical values

correspond to TJ = 25℃, VVIN = 12 V, VVCCX = 5 V, VVOUT1 = 3.3 V, VVOUT2 = 5 V, VEN1 = VEN2 = 5 V, RRT = 10 kΩ, FSW = 2.2

MHz, no-load on the drive outputs (HO1, HOL1, LO1, LOL1, HO2, HOL2, LO2 and LOL2).

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

INPUT VOLTAGE (VIN)

ISHUTDOWN

Shutdown mode current

VIN = 12 V, VEN1 = VEN2 = 0 V

3.3

7

µA

ISTANDBY1

Standby current, channel 1

VIN = 12 V, VEN1 = 5 V, VEN2 = 0 V, VVOUT1

= 3.3 V, in regulation, no-load, not switching,

DEMB = MODE = GND

24

31

µA

ISTANDBY2

Standby current, channel 2

VIN = 12 V, VEN1 = 0 V, VEN2 = 5 V, VVOUT2 = 5

V, in regulation, no-load, not switching, DEMB

= MODE = AGND

25

43

µA

ISTANDBY3

VIN = 12 V, VEN1 = 5 V, VEN2 = 0 V, VVOUT1

Standby current, channel 1, ultra-low

= 3.3 V, in regulation, no-load, not switching,

IQ mode

DEMB = GND, RMODE = 10 kΩ to GND

15

21

µA

ISTANDBY4

VIN = 12 V, VEN1 = 0 V, VEN2 = 5 V, VVOUT2 = 5

Standby current, channel 2, ultra-low

V, in regulation, no-load, not switching, DEMB

IQ mode

= GND, RMODE = 10 kΩ to AGND

21

33

µA

BIAS REGULATOR (VCC)

8

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted), Typical values

correspond to TJ = 25℃, VVIN = 12 V, VVCCX = 5 V, VVOUT1 = 3.3 V, VVOUT2 = 5 V, VEN1 = VEN2 = 5 V, RRT = 10 kΩ, FSW = 2.2

MHz, no-load on the drive outputs (HO1, HOL1, LO1, LOL1, HO2, HOL2, LO2 and LOL2).

MIN

TYP

MAX

VCC regulation voltage

PARAMETER

VVIN = 12 V, IVCC = 100 mA, VVCCX = 0 V

4.7

5

5.3

VCC-UVLO

VCC UVLO rising threshold

VVCC rising

3.2

3.3

3.4

VVCC-HYST

VCC UVLO hysteresis

IVCC-LIM

VCC sourcing current limit

VVCC-REG

TEST CONDITIONS

UNIT

V

V

175

mV

-250

mA

ANALOG BIAS (VDDA)

VVDDA-REG

VDDA regulation voltage

VVDDA-UVLO

VDDA UVLO rising threshold

VVCC rising, VVCCX = 0 V

4.75

5

5.25

V

3.1

3.2

3.3

V

VVDDA-HYST

VDDA UVLO hysteresis

VVCCX = 0 V

90

mV

RVDDA

VDDA resistance

VVCCX = 0 V

20

Ω

EXTERNAL BIAS (VCCX)

VVCCX-ON

VCCX(ON) rising threshold

RVCCX

VCCX resistance

VVCCX-HYST

VCCX hysteresis voltage

4.1

VVCCX = 5 V

4.3

4.4

V

1.3

Ω

130

mV

CURRENT LIMIT (CS1, CS2)

VCS1

Current limit threshold 1

Measured from CS1 to VOUT1

66

Measured from CS2 to VOUT2

66

VCS2

Current limit threshold 2

TCS-DELAY

CS delay to output

GCS

CS amplifier gain

ICS-BIAS

CS amplifier input bias current

73

80

mV

73

80

mV

40

11.4

12

ns

12.6

V/V

15

nA

POWER GOOD (PG1, PG2)

PG1UV

PG1 UV trip level

Falling with respect to the regulation voltage

90%

92%

PG2UV

PG2 UV trip level

Falling with respect to the regulation voltage

90%

92%

94%

PG1OV

PG1 OV trip level

Rising with respect to the regulation voltage

108%

110%

112%

108%

110%

112%

PG2OV

PG2 OV trip level

Rising with respect to the regulation voltage

PG1UV-HYST

PG1 UV hysteresis

Rising with respect to the regulation voltage

3.4%

PG1OV-HYST

PG1 OV hysteresis

Rising with respect to the regulation voltage

3.4%

PG2UV-HYST

PG2 UV hysteresis

Rising with respect to the regulation voltage

3.4%

PG2OV-HYST

PG2 OV hysteresis

Rising with respect to the regulation voltage

3.4%

VOL-PG1

PG1 voltage

Open collector, IPG1 = 2 mA

94%

0.4

0.4

V

VOL-PG2

PG2 voltage

Open collector, IPG2 = 2 mA

TPG-RISE-DLY

OV filter time

VOUT rising

25

µs

V

TPG-FALL-DLY

UV filter time

VOUT falling

22

µs

HIGH-SIDE GATE DRIVER (HO1, HO2, HOL1, HOL2)

VHO-LOW

HO low-state output voltage

IHO = 100 mA

0.04

V

VHO-HIGH

HO high-state output voltage

IHO = –100 mA, VHO-HIGH = VHB – VHO

0.09

V

tHO-RISE

HO rise time (10% to 90%)

CLOAD = 2.7 nF

24

ns

tHO-FALL

HO fall time (90% to 10%)

CLOAD = 2.7 nF

24

ns

IHO-SRC

HO peak source current

VHO = VSW = 0 V, VHB = 5 V, VVCCX = 5 V

3.25

A

IHO-SINK

HO peak sink current

VVCCX = 5 V

4.25

A

VBT-UV

BOOT UVLO

VVCC falling

2.4

V

VBT-UV-HYS

BOOT UVLO hysteresis

113

mV

IBOOT

BOOT quiescent current

1.2

µA

0.04

V

LOW-SIDE GATE DRIVER (LO1, LO2, LOL1, LOL2)

VLO-LOW

LO low-state output voltage

ILO = 100 mA

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

9

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted), Typical values

correspond to TJ = 25℃, VVIN = 12 V, VVCCX = 5 V, VVOUT1 = 3.3 V, VVOUT2 = 5 V, VEN1 = VEN2 = 5 V, RRT = 10 kΩ, FSW = 2.2

MHz, no-load on the drive outputs (HO1, HOL1, LO1, LOL1, HO2, HOL2, LO2 and LOL2).

PARAMETER

VLO-HIGH

LO high-state output voltage

TEST CONDITIONS

MIN

ILO = –100 mA

TYP

MAX

0.07

UNIT

V

tLO-RISE

LO rise time (10% to 90%)

CLOAD = 2.7 nF

4

ns

tLO-FALL

LO fall time (90% to 10%)

CLOAD = 2.7 nF

3

ns

ILO-SOURCE

LO peak source current

VHO = VSW = 0 V, VHB = 5 V, VVCCX = 5 V

3.25

A

ILO-SINK

LO peak sink current

VVCCX = 5 V

4.25

A

20

µA

RESTART (RES)

IRES-SRC

RES current source

VRES-TH

RES threshold

1.2

V

HICCYCLES

HICCUP mode fault

512

cycles

RRES-PD

RES pull-down resistance

5.5

Ω

OUTPUT VOLTAGE SETPOINT (VOUT1, VOUT2)

VOUT33

3.3 V output voltage setpoint

VFB = 0 V, VIN = 3.5 V to 65 V

3.267

3.3

3.33

V

VOUT50

5 V output voltage setpoint

VFB = 5 V, VIN = 5.5 V to 65 V

4.95

5

5.05

V

FEEDBACK (FB1, FB2)

VFB-3V3-SEL

VOUT select threshold 3.3-V output

4.6

RFB-5V

Resistance FB to AGND for 5-V

output

VMODE = 0 V or RMODE = 10 kΩ

RFB-EXTRES

Thevenin equivelent resistance

VMODE = 0 V or RMODE = 10 kΩ, VFB < 2 V

VFB2-LOW

Master mode select logic level low

MODE = VDDA

VFB2-HIGH

Master mode select logic level high

MODE = VDDA

VFB1-LOW

Diode emulation logic level low

in slave mode

MODE = FB2 = VDDA

VFB1-HIGH

FPWM logic level high in slave mode MODE = FB2 = VDDA

VFB-REG

Regulated feedback voltage

V

500

5

Ω

kΩ

0.8

2

V

V

0.8

V

0.606

V

2

V

TJ = –40°C to 125°C

0.594

0.6

1020

1200

ERROR AMPLIFIER (COMP1, COMP2)

gm1

EA transconductance

FB to COMP, RMODE < 5 kΩ to AGND

gm2

EA transconductance, ultra-low IQ

mode

MODE = GND, RMODE = 10 kΩ

65

IFB

Error amplifier input bias current

VCOMP-CLMP

COMP clamp voltage

VFB = 0 V

3.3

ICOMP-SLAVE

COMP leakage, slave mode

VCOMP = 1 V, MODE = FB2 = VCC

10

nA

ICOMP-INTLV

COMP2 leakage, Imode

VCOMP = 1 V, MODE = VCC, VFB2 = 0 V

10

nA

ICOMP-SRC1

EA source current

VCOMP = 1 V, VFB = 0.4 V, VMODE = 0 V

190

ICOMP-SINK1

EA sink current

VCOMP = 1 V, VFB = 0.8 V, VMODE = 0 V

165

µA

ICOMP-SRC2

VCOMP = 1 V, VFB = 0.4 V,

EA source current, ultra-low IQ mode

RMODE = 10 kΩ to AGND

10

µA

EA sink current, ultra-low IQ mode

VCOMP = 1 V, VFB = 0.8 V,

RMODE = 10 kΩ to AGND

12

µA

EA SS offset with VFB = 0 V

Raise VSS until VCOMP > 300 mV

36

mV

VGS falling, no-load

ICOMP-SINK2

VSS-OFFSET

µS

µS

20

nA

V

µA

ADAPTIVE DEADTIME CONTROL

VGS-DET

VGS detection threshold

2.5

V

tDEAD1

HO off to LO on deadtime

22

ns

tDEAD2

LO off to HO on deadtime

22

ns

DIODE EMULATION (DEMB)

VDEMB-LOW

10

DEMB input low threshold

0.8

Submit Document Feedback

V

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted), Typical values

correspond to TJ = 25℃, VVIN = 12 V, VVCCX = 5 V, VVOUT1 = 3.3 V, VVOUT2 = 5 V, VEN1 = VEN2 = 5 V, RRT = 10 kΩ, FSW = 2.2

MHz, no-load on the drive outputs (HO1, HOL1, LO1, LOL1, HO2, HOL2, LO2 and LOL2).

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

2

UNIT

VDEMB_Rising

DEMB input high threshold

V

VZC-SW

Zero-cross threshold

VDEMB = 0 V

–6

mV

VZC-SS

Zero-cross threshold soft-start

DEMB = VCC,

50 SW cycles after first HO pulse

–5.4

mV

VZC-DIS

Zero-cross threshold disabled

DEMB = VCC,

1000 SW cycles after first HO pulse

200

mV

ENABLE (EN1, EN2)

VEN-LOW

EN1/2 low threshold

VVCCX = 0 V

VEN-HIGH-TH

EN1/2 high threshold

VVCCX = 0 V

IEN-LEAK

EN1/2 leakage currernt

EN1, EN2 logic inputs only

0.8

2

V

V

0.05

µA

0.8

V

SWITCHING FREQUENCY (RT)

VRT

RT regulation voltage

10 kΩ < RRT < 220 kΩ

MODE

RMODE-HIGH

Resistance to AGND for ultra-low IQ

5

kΩ

RMODE-LOW

Resistance to AGND for normal IQ

0.5

kΩ

VMODE-LOW

Non-interleaved mode input low

threshold

0.8

V

VMODE-HIGH

Interleaved mode input high

threshold

2

V

SYNCHRONIZATION INPUT (SYNCIN)

VDEMB-LOW

DEMB input low threshold

VDEMB-HIGH

DEMB input high threshold

0.8

TSYNC-MIN

DEMB minimum pulse width

VMODE = 0 V or RMODE = 10 kΩ

FSYNCIN

External SYNC frequency range

VIN = 8 V to 18 V, % of the nominal frequency

set by RRT

tSYNCIN-HO1

Delay from DEMB rising to HO1

rising edge

tSYNCIN-SLAVE

Delay from DEMB falling edge to

HO2 rising edge

Slave mode, MODE = FB2 = VCC

tDEMB-FILTER

Delay from DEMB low to diode

emulation enable

VMODE = 0 V or RMODE = 10 kΩ

tAWAKE-FILTER

Maximum SYNC period to maintain

standby state

VEN1 = VEN2 = 0 V

2

V

V

20

250

–20%

20%

ns

100

ns

101

ns

15

50

27

µs

µs

SYNCHRONIZATION OUTPUT (SYNCOUT)

VSYNCOUT-LO SYNCOUT low-state voltage

ISYNCOUT = 16 mA

0.8

V

0

Hz

FSYNCOUT

SYNCOUT frequency

MODE = FB2 = VDDA

tSYNCOUT1

Delay from HO2 rising edge to

SYNCOUT rising edge

VDEMB = 0 V, TS = 1/FSW, FSW set by RRT = 220

kΩ

2.5

µs

tSYNCOUT2

Delay from HO2 rising edge to

SYNCOUT falling edge

VDEMB = 0 V, TS = 1/FSW, FSW set by RRT =

220 kΩ

7.5

µs

Dither source/sink current

21

µA

Dither high-level threshold

1.25

V

Dither low-level threshold

1.15

V

DITHER (DITH)

IDITH

VDITH-HIGH

SOFT START (SS1, SS2)

ISS

Soft-start current

VMODE = 0 V

RSS-PD

Soft-start pull-down resistance

VMODE = 0 V

16

21

3

28

µA

Ω

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

11

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted), Typical values

correspond to TJ = 25℃, VVIN = 12 V, VVCCX = 5 V, VVOUT1 = 3.3 V, VVOUT2 = 5 V, VEN1 = VEN2 = 5 V, RRT = 10 kΩ, FSW = 2.2

MHz, no-load on the drive outputs (HO1, HOL1, LO1, LOL1, HO2, HOL2, LO2 and LOL2).

PARAMETER

VSS-FB

SS to FB clamp voltage

TEST CONDITIONS

MIN

VCS – VOUT > 73 mV

TYP

MAX

UNIT

125

mV

ISS-SLAVE

SS leakage, slave mode

VSS = 0.8 V, MODE = FB2 = VDDA

36

nA

ISS-INTLV

SS2 leakage, interleaved mode

VSS = 0.8 V, MODE = VDDA, VFB2 = 0 V

35

nA

175

°C

15

°C

THERMAL SHUTDOWN

TSHD

Thermal shutdown

TSHD-HYS

Thermal shutdown hysteresis

7.6 Switching Characteristics

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted). Typical values

correspond to TJ = 25℃, VVIN = 12 V, VVCCX = 5 V, VVOUT1 = 3.3 V, VVOUT2 = 5 V, VEN1 = VEN2 = 5 V, RRT = 10 kΩ, FSW = 2.2

MHz, no-load on the gate driver outputs (HO1, HOL1, LO1, LOL1, HO2, HOL2, LO2, and LOL2).

PARAMETER

FSW1

Switching frequency 1

TEST CONDITIONS

RRT = 100 kΩ

MIN

TYP

MAX

UNIT

200

220

242

kHz

FSW2

Switching frequency 2

RRT = 10 kΩ

2.2

MHz

FSW3

Switching frequency 3

RRT = 220 kΩ

100

kHz

SLOPE2

Internal slope compensation 2

RRT = 100 kΩ

64

mV/μs

SLOPE1

Internal slope compensation 1

RRT = 10 kΩ

557

tON(min)

Minimum on-time

tOFF(min)

Minimum off-time

PHHO1-HO2

Phase between HO1 and HO2

12

DEMB = MODE = AGND

Submit Document Feedback

mV/μs

35

80

ns

80

100

ns

180

°

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

7.7 Typical Characteristics

100

100

95

95

90

90

Efficiency (%)

Efficiency (%)

VIN = VEN1 = VEN2 = 12 V, TJ = 25°C, unless otherwise stated.

85

80

75

85

80

75

70

70

VIN = 8V

VIN = 12V

VIN = 18V

65

VIN = 8V

VIN = 12V

VIN = 18V

65

60

60

0

1

2

See Figure 9-4

3

4

Load Current (A)

VOUT = 5 V

5

6

FSW = 2.1 MHz

7

0

1

2

See Figure 9-4

Figure 7-1. Efficiency versus Load

3

4

Load Current (A)

VOUT = 3.3 V

5

6

7

FSW = 2.1 MHz

Figure 7-2. Efficiency versus Load

VIN 2V/DIV

VOUT2 1V/DIV

SW1 5V/DIV

VOUT1 1V/DIV

SW2 5V/DIV

IOUT1 5A/DIV

1ms/DIV

80 ns/DIV

See Figure 9-4

See Figure 9-4

Figure 7-4. Start-up Characteristic

Figure 7-3. Switch Node Voltages

Shutdown Quiescent Current (PA)

6

VOUT1 100mV/DIV

IOUT1 2A/DIV

100Ps/DIV

5

4

3

2

1

0

-50

-25

See Figure 9-4

Figure 7-5. Load Transient Response

0

25

50

75

100

Junction Temperature (qC)

125

150

D001

VEN1 = VEN2 = 0 V

Figure 7-6. Shutdown Current versus Temperature

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

13

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

30

Standby Quiescent Current (PA)

Sleep Quiescent Current (PA)

10

8

6

4

2

10

20

30

40

Input Voltage (V)

50

60

26

24

22

20

-50

0

0

28

70

-25

0

25

50

75

100

Junction Temperature (qC)

D002

VEN1 = VEN2 = 0 V

3.33

Fixed 3.3V Output Voltage Setting (V)

ULIQ Mode Standby Quiescent Current (PA)

D003

Figure 7-8. Channel 1 Standby Current versus

Temperature

30

25

20

15

10

5

Channel 1

Channel 2

0

-50

-25

0

25

50

75

100

Junction Temperature (qC)

125

D004

3.32

3.31

3.3

3.29

3.28

3.27

-50

150

Figure 7-9. ULIQ Mode Standby Current versus

Temperature

5.06

0.606

5.04

0.604

5.02

0.602

5

4.98

0

25

50

75

100

Junction Temperature (qC)

125

150

D014

0.6

0.598

0.596

4.96

4.94

-50

-25

Figure 7-10. Fixed 3.3-V Output Voltage (VOUT1)

versus Temperature

FB Voltage (V)

Fixed 5V Output Voltage Setting (V)

150

VEN2 = 0 V

Figure 7-7. Shutdown Current versus Input Voltage

-25

0

25

50

75

100

Junction Temperature (qC)

125

150

D013

Figure 7-11. Fixed 5-V Output Voltage (VOUT1)

versus Temperature

14

125

0.594

-50

-25

0

25

50

75

100

Junction Temperature (qC)

125

150

D015

Figure 7-12. Feedback Voltage versus Temperature

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

100

114

98

112

PG OV Thresholds (%)

PG UV Thresholds (%)

www.ti.com

96

94

92

90

88

86

-50

0

25

50

75

100

Junction Temperature (qC)

125

104

Rising

Falling

-25

0

D016

25

50

75

100

Junction Temperature (qC)

125

150

D016

Figure 7-14. PG OV Thresholds versus

Temperature

3.4

5.3

VCC UVLO Thresholds (V)

5.2

VCC Voltage (V)

106

100

-50

150

Figure 7-13. PG UV Thresholds versus

Temperature

5.1

5

4.9

4.8

3.3

3.2

3.1

3

Rising

Falling

IVCC = 0mA

IVCC = 100mA

4.7

-50

-25

0

25

50

75

100

Junction Temperature (qC)

125

2.9

-50

150

0

25

50

75

100

Junction Temperature (qC)

125

150

D007

Figure 7-16. VCC UVLO Thresholds versus

Temperature

5.3

350

5.2

VDDA Voltage (V)

300

250

200

150

100

-50

-25

D005

Figure 7-15. VCC Regulation Voltage versus

Temperature

VCC Current Limit (mA)

108

102

Rising

Falling

-25

110

5.1

5

4.9

4.8

-25

0

25

50

75

100

Junction Temperature (qC)

125

150

4.7

-50

-25

D010

Figure 7-17. VCC Current Limit versus

Temperature

0

25

50

75

100

Junction Temperature (qC)

125

150

D008

Figure 7-18. VDDA Regulation Voltage versus

Temperature

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

15

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

4.6

3.3

VCCX Thresholds (V)

VDDA UVLO Thresholds (V)

3.4

3.2

3.1

3

4.4

4.2

4

Rising

Falling

2.9

-50

-25

0

25

50

75

100

Junction Temperature (qC)

125

Rising

Falling

2.5

76

CS Threshold Voltage (V)

77

2

1.5

1

0.5

-25

0

25

50

75

100

Junction Temperature (qC)

125

150

D011

74

73

72

-25

0

D012

25

50

75

100

Junction Temperature (qC)

125

150

D019

Figure 7-22. Current Sense (CS1) Threshold versus

Temperature

100

Min On and Off Times (ns)

12.4

CS Amplifier Gain (V/V)

125

75

70

-50

150

12.6

12.2

12

11.8

11.6

80

60

40

20

Min On Time

Min Off Time

-25

0

25

50

75

100

Junction Temperature (qC)

125

150

0

-50

-25

D018

Figure 7-23. Current Sense (CS1) Amplifier Gain

versus Temperature

16

25

50

75

100

Junction Temperature (qC)

71

Figure 7-21. VCCX Switch Resistance versus

Temperature

11.4

-50

0

Figure 7-20. VCCX On/Off Thresholds versus

Temperature

3

0

-50

-25

D009

Figure 7-19. VDDA UVLO Thresholds versus

Temperature

VCCX Switch Rds-on (:)

3.8

-50

150

0

25

50

75

100

Junction Temperature (qC)

125

150

D020

Figure 7-24. Minimum On Time and Off Time (HO1)

versus Temperature

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

2.8

24

2.6

22

SS Current (PA)

BOOT UVLO Thresholds (V)

www.ti.com

2.4

2.2

20

18

Rising

Falling

2

-50

-25

0

25

50

75

100

Junction Temperature (qC)

125

150

16

-50

-25

D021

Figure 7-25. BOOT (HB1) UVLO Thresholds versus

Temperature

0

25

50

75

100

Junction Temperature (qC)

125

150

D022

Figure 7-26. Soft-start (SS1) Current versus

Temperature

250

RT Resistance (k:)

200

150

100

50

0

0

400

800

1200

1600

Switching Frquency (kHz)

2000

D023

Figure 7-27. RT Resistance versus Switching Frequency

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

17

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

8 Detailed Description

8.1 Overview

The LM5143-Q1 is a dual-phase or dual-channel switching controller that features all of the functions necessary

to implement a high-efficiency synchronous buck power supply operating over a wide input voltage range from

3.5 V to 65 V. The LM5143-Q1 is configured to provide a fixed 3.3-V or 5-V output, or an adjustable output

between 0.6 V to 55 V. This easy-to-use controller integrates high-side and low-side MOSFET drivers capable of

sourcing 3.25-A and sinking 4.25-A peak current. Adaptive dead-time control is designed to minimize body diode

conduction during switching transitions.

Current-mode control using a shunt resistor or inductor DCR current sensing provides inherent line feedforward,

cycle-by-cycle peak current limiting, and easy loop compensation. It also supports a wide duty cycle range for

high input voltage and low dropout applications as well as when a high voltage conversion ratio (for example,

10-to-1) is required. The oscillator frequency is user-programmable between 100 kHz to 2.2 MHz, and the

frequency can be synchronized as high as 2.5 MHz by applying an external clock to DEMB.

An external bias supply can be connected to VCCX to maximize efficiency in high input voltage applications.

A user-selectable diode emulation feature enables discontinuous conduction mode (DCM) operation to further

improve efficiency and reduce power dissipation during light-load conditions. Fault protection features include

the following:

•

•

•

•

Current limiting

Thermal shutdown

UVLO

Remote shutdown capability

The LM5143-Q1 incorporates features to simplify the compliance with CISPR 25 automotive EMI requirements.

An optional spread spectrum frequency modulation (SSFM) technique reduces the peak EMI signature, while

the adaptive gate drivers with slew rate control minimize high-frequency emissions. Finally, 180° out-of-phase

interleaved operation of the two controller channels reduces input filtering and capacitor requirements.

The LM5143-Q1 is provided in a 40-pin VQFNP package with wettable flanks and an exposed pad to aid in

thermal dissipation.

18

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

8.2 Functional Block Diagram

VIN

SYNCOUT

COMMON

VCCX

BIAS

VREF 0.6V

DEMB/

SYNCIN

CLK1

VCC

PLL &

OSCILLATORS

CLK2

DEM/FPWM

VDDA

22PA

VOUT1

VDDA

CONTROL

`

DITH

DITHER

22PA

20PA

RT amp

HICCUP FAULT

TIMER

512 CYCLES

RESTART

LOGIC

RES

ILIM1/2

800mV

AGND

+

INTERLEAVE

-

ULIQ

DECODER

MODE

RT

HICCUP1/2

CHANNEL 1/2

EN1/2

ILIM1/2

+

CURRENT

LIMIT

75mV

CS1/2

+

VOUT1/2

-

+

GAIN = 12

-

HB1/2

UVLO

SLOPE COMP

3.3V

HB1

RAMP

5V

FB

DECODER

/MUX

DEM/FPWM

COMP1/2 ENABLE

FB1/2

HO1/2

HOL1/2

HICCUP1/2

INTERLEAVE

ERROR

FB1/2

VREF

0.660V

+

-

R

Q

S

Q

SW1/2

VCC

CLK1/2

LEVEL SHIFT

ADAPTIVE

DEADTIME

ULIQ

-

PG

DELAY

25Ps

PWM1/2

+

+

PGOV

PG1/2

AMPLIFER

+

PGUV

0.552V

LO1/2

LOL1/2

+

COMP1/2

21PA

_

SS1/2

STANDBY

ILIM1/2

PGND1/2

-

+

125mV

+

±

-

GM

150mV

+

SS1/2

+

SS1/2

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

19

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

8.3 Feature Description

8.3.1 Input Voltage Range (VIN)

The LM5143-Q1 operational input voltage range is from 3.5 V to 65 V. The device is intended for step-down

conversions from 12-V, 24-V, and 48-V automotive supply rails. The application circuit in Figure 8-1 shows all

the necessary components to implement an LM5143-Q1 based wide-VIN dual-output step-down regulator using

a single supply. The LM5143-Q1 uses an internal LDO subregulator to provide a 5-V VCC bias rail for the gate

drive and control circuits (assuming the input voltage is higher than 5 V plus the necessary subregulator dropout

specification).

VIN

VDDA

CIN

CVCC2

CVCC1

VCC

VIN

FB1 FB2 MODE

HB1

HB2

HO1

HO2

HOL1

HOL2

SW1

SW2

LO1

LOL1

LO2

LOL2

RHO2

RHO1

RS1

LO1

VOUT1

CO1

EN1

LM5143-Q1

EN2

RT

RRT

SYNC In

optional CC1

RS2

VOUT2

CO2

PGND2

PGND1

VIN

LO2

VIN

PG2

PG1

CS1

VOUT1

DEMB

CS2

VOUT2

VCCX

RC1

COMP1

SYNC Out

SYNCOUT

RC2

CC3

COMP2

AGND SS1 RES SS2 VDDA DITH

CC2

CC4

CSS1 CRES CSS2 CVDD CDITH

Figure 8-1. Dual-Output Regulator Schematic Diagram With Input Voltage Range of 3.5 V to 65 V

In high input voltage applications, make sure the VIN and SW pins do not exceed their absolute maximum

voltage rating of 70 V during line or load transient events. Voltage excursions that exceed the Absolute Maximum

Ratings can damage the IC. Proceed carefully during PCB board layout and use high-quality input bypass

capacitors to minimize voltage overshoot and ringing.

8.3.2 High-Voltage Bias Supply Regulator (VCC, VCCX, VDDA)

The LM5143-Q1 contains an internal high-voltage VCC bias regulator that provides the bias supply for the PWM

controller and the gate drivers for the external MOSFETs. The input voltage pin (VIN) can be connected directly

to an input voltage source up to 65 V. However, when the input voltage is below the VCC setpoint level, the VCC

voltage tracks VIN minus a small voltage drop.

The VCC regulator output current limit is 170 mA (minimum). At power up, the regulator sources current into the

capacitors connected at the VCC pin. When the VCC voltage exceeds 3.3 V, both output channels are enabled

(if EN1 and EN2 are connected to a voltage greater than 2 V) and the soft-start sequence begins. Both channels

remain active unless the VCC voltage falls below the VCC falling UVLO threshold of 3.1 V (typical) or EN1/2

is switched to a low state. The LM5143-Q1 has two VCC pins that must be connected together on the PCB.

TI recommends that two VCC capacitors are connected from VCC to PGND1 and from VCC to PGND2. The

recommended range for each VCC capacitor is from 2.2 µF to 10 µF.

20

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

An internal 5-V linear regulator generates the VDDA bias supply. Bypass VDDA with a 470-nF ceramic capacitor

to achieve a low-noise internal bias rail. Normally VDDA is 5 V, but there are two operating conditions where it

regulates at 3.3 V. The first is in skip cycle mode when VOUT1 is set to 3.3 V and VOUT2 is disabled. The second

is in a cold-crank start-up where VIN is 3.8 V and VOUT1 is 3.3 V.

Internal power dissipation of the VCC regulator can be minimized by connecting VCCX to a 5-V output at VOUT1

or VOUT2 or to an external 5-V supply. If the VCCX voltage is above 4.3 V, VCCX is internally connected to VCC

and the internal VCC regulator is disabled. Tie VCCX to AGND if it is unused. Never connect VCCX to a voltage

greater than 6.5 V or less than –0.3 V. If an external supply is connected to VCCX to power the LM5143-Q1, VIN

must be greater than the external bias voltage during all conditions to avoid damage to the controller.

8.3.3 Enable (EN1, EN2)

The LM5143-Q1 contains two enable inputs. EN1 and EN2 facilitate independent start-up and shutdown control

of VOUT1 and VOUT2. The enable pins can be connected to a voltage as high as 70 V. If an enable input is greater

than 2 V, its respective output is enabled. If an enable pin is pulled below 0.4 V, the output is shutdown. If both

outputs are disabled, the LM5143-Q1 is in a low-IQ shutdown mode with a 4-µA typical current drawn from VIN.

TI does not recommend leaving EN1 or EN2 floating.

8.3.4 Power Good Monitor (PG1, PG2)

The LM5143-Q1 includes output voltage monitoring signals for VOUT1 and VOUT2 to simplify sequencing and

supervision. The power-good function can be used to enable circuits that are supplied by the corresponding

voltage rail or to turn on sequenced supplies. Each power-good output (PG1 and PG2) switches to a high

impedance open-drain state when the corresponding output voltage is in regulation. Each output switches low

when the corresponding output voltage drops below the lower power-good threshold (92% typical) or rises above

the upper power-good threshold (110% typical). A 25-µs deglitch filter prevents false tripping of the power-good

signals during transients. TI recommends pullup resistors of 100 kΩ (typical) from PG1 and PG2 to the relevant

logic rail. PG1 and PG2 are asserted low during soft start and when the corresponding buck regulator is disabled

by EN1 or EN2.

8.3.5 Switching Frequency (RT)

The LM5143-Q1 oscillator is programmed by a resistor between RT and AGND to set an oscillator frequency

between 100 kHz to 2.2 MHz. CLK1 is the clock for channel 1 and CLK2 is for channel 2. CLK1 and CLK2 are

180° out of phase. Use Equation 1 to calculate the RT resistance for a given switching frequency.

RRT ª¬k: º¼

22

FSW ª¬MHz º¼

(1)

Under low VIN conditions when either of the on-time of the high-side MOSFETs exceeds the programmed

oscillator period, the LM5143-Q1 extends the switching period of that channel until the PWM latch is reset by

the current sense ramp exceeding the controller compensation voltage. In such an event, the oscillators (CLK1

and CLK2) operate independently and asynchronously until both channels can maintain output regulation at the

programmed frequency.

The approximate input voltage level where this occurs is given by Equation 2.

VIN(min)

VOUT ˜

t SW

t SW

t OFF(min)

(2)

where

•

•

where tSW is the switching period

tOFF(min) is the minimum off-time of 60 ns

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

21

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

8.3.6 Clock Synchronization (DEMB)

To synchronize the LM5143-Q1 to an external source, apply a logic-level clock signal (greater than 2 V) to

DEMB. The LM5143-Q1 can be synchronized to ±20% of the programmed frequency up to a maximum of

2.5 MHz. If there is an RT resistor and a synchronization signal, the LM5143-Q1 ignores the RT resistor

and synchronizes to the external clock. Under low VIN conditions when the minimum off-time is reached,

the synchronization signal is ignored, allowing the switching frequency to reduce to maintain output voltage

regulation.

8.3.7 Synchronization Out (SYNCOUT)

The SYNCOUT voltage is a logic level signal with a rising edge approximately 90° lagging HO2 (or 90° leading

HO1). When the SYNCOUT signal is used to synchronize a second LM5143-Q1 controller, all four phases are

90° out of phase.

8.3.8 Spread Spectrum Frequency Modulation (DITH)

The LM5143-Q1 provides a frequency dithering option that is enabled by connecting a capacitor from DITH to

AGND. This generates a triangular voltage centered at 1.2 V at DITH. See Figure 8-2. The triangular waveform

modulates the oscillator frequency by ±5% of the nominal frequency set by the RT resistance. Use Equation 3

to calculate the required DITH capacitance to set the modulating frequency, FMOD. For the dithering circuit to

effectively attenuate the peak EMI, the modulation rate must be less than 20 kHz for proper operation of the

clock circuit.

CDITH

22 $

2 ˜ FMOD ˜ 0.1V

(3)

1.26 V (+5% )

1.2 V

1.14 V ±

CDITH

DITH

AGND

Figure 8-2. Switching Frequency Dithering

If DITH is connected to VDDA during power up, the dither feature is disabled and cannot be enabled unless VCC

is recycled below the VCC UVLO threshold. If DITH is connected to AGND on power up, CDITH is prevented from

charging, disabling dither. Also, dither is disabled when the LM5143-Q1 is synchronized to an external clock.

8.3.9 Configurable Soft Start (SS1, SS2)

The soft-start feature allows the regulator to gradually reach the steady-state operating point, thus reducing

start-up stresses and surges.

The LM5143-Q1 features an adjustable soft start that determines the charging time of the output or outputs. Soft

start limits inrush current as a result of high output capacitance to avoid an overcurrent condition. Stress on the

input supply rail is also reduced.

The LM5143-Q1 regulates the FB voltage to the SS voltage or the internal 600-mV reference, whichever is

lower. At the beginning of the soft-start sequence when the SS voltage is 0 V, the internal 21-μA soft-start current

source gradually increases the voltage on an external soft-start capacitor connected to the SS pin, resulting in a

gradual rise of the relevant FB and output voltages. Use Equation 4 to calculate the soft-start capacitance.

CSS (nF)

35 ˜ t SS (ms)

(4)

where

22

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

•

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

tSS is the required soft-start time

SS can be pulled low with an external circuit to stop switching, but this is not recommended. When the controller

is in FPWM mode (set by connecting DEMB to VDDA), pulling SS low results in COMP being pulled down

internally as well. LO remains on and the low-side MOSFET discharges the output capacitor, resulting in large

negative inductor current. In contrast, the LO gate driver is disabled when the LM5143-Q1 internal logic pulls SS

low due to a fault condition.

8.3.10 Output Voltage Setpoint (FB1, FB2)

The LM5143-Q1 outputs can be independently configured for one of the two fixed output voltages with no

external feedback resistors, or adjusted to the desired voltage using an external resistor divider. VOUT1 or VOUT2

can be configured as a 3.3-V output by connecting the corresponding FB pin to VDDA, or a 5-V output by

connecting FB to AGND. The FB1 and FB2 connections (either VDDA or GND) are detected during power up.

The configuration settings are latched and cannot be changed until the LM5143-Q1 is powered down with the

VCC voltage decreasing below its falling UVLO threshold, and then powered up again.

Alternatively, the output voltage can be set using external resistive dividers from the output to the relevant

FB pin. The output voltage adjustment range is between 0.6 V and 55 V. The regulation threshold at FB is

0.6 V (VREF). Use Equation 5 to calculate the upper and lower feedback resistors, designated RFB1 and RFB2,

respectively. See Figure 8-3.

RFB1

§ VOUT

¨

© VREF

·

1¸ ˜ RFB2

¹

(5)

The recommended starting value for RFB2 is between 10 kΩ and 20 kΩ.

VIN

LO

VOUT1

VREF

+

SS

+

FB1

CO

RFB1

±

COMP1

RCOMP

RFB2

gm = 1200 PS

CCOMP

AGND

CHF

Figure 8-3. Control Loop Error Amplifier

The Thevenin equivalent impedance of the resistive divider connected to the FB pin must be greater than 5 kΩ

for the LM5143-Q1 to detect the divider and set the channel to the adjustable output mode.

RTH

RFB1 ˜ RFB2

! 5k:

RFB1 RFB2

(6)

If a low IQ mode is required, take care when selecting the external resistors. The extra current drawn from the

external divider is added to the LM5143-Q1 ISTANDBY current (15 µA typical). The divider current reflected to

VIN is divided down by the ratio of VOUT/VIN. For example, if VOUT is set to 5.55 V with RFB1 equal to 82.5 kΩ

and RFB2 equal to 10 kΩ, use Equation 7 to calculate the input current from a 12-V input required to supply the

current in the feedback resistors.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

23

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

IVIN(DIVIDER)

IVIN

VOUT

V

˜ OUT

RFB1 RFB2 K ˜ VIN

ISTANDBY

IVIN(DIVIDER)

15 $

5.55 V

5.55 V

˜

| 35 $

82.5k: 10k: 80% ˜ 12 V

$

$

(7)

If one output is enabled and the other disabled, the VCC output is in regulation. The HB voltage of the disabled

channel charges to VCC through the bootstrap diode. As a result, the HO driver bias current (approximately 1.5

µA) can increase the output voltage of the disabled channel to approximately 2.2 V. If this is not desired, add a

load resistor (100 kΩ) to the output that is disabled to maintain a low-voltage OFF-state.

8.3.11 Minimum Controllable On-Time

There are two limitations to the minimum output voltage adjustment range: the LM5143-Q1 voltage reference of

0.6 V and the minimum controllable switch-node pulse width, tON(min).

tON(min) effectively limits the voltage step-down conversion ratio of VOUT/VIN at a given switching frequency. For

fixed-frequency PWM operation, the voltage conversion ratio must satisfy Equation 8.

VOUT

! t ON(min) ˜ FSW

VIN

(8)

where

•

•

tON(min) is 65 ns (typical)

FSW is the switching frequency

If the desired voltage conversion ratio does not meet the above condition, the LM5143-Q1 transitions from fixed

switching frequency operation to a pulse-skipping mode to maintain output voltage regulation. For example, if

the desired output voltage is 5 V with an input voltage is 24 V and switching frequency of 2.1 MHz, the voltage

conversion ratio test in Equation 9 is satisfied.

5V

! 65ns ˜ 2.1 MHz

24 V

0.208 ! 0.137

(9)

For wide VIN applications and low output voltages, an alternative is to reduce the LM5143-Q1 switching

frequency to meet the requirement of Equation 8.

8.3.12 Error Amplifier and PWM Comparator (FB1, FB2, COMP1, COMP2)

Each channel of the LM5143-Q1 has an independent high-gain transconductance amplifier that generates an

error current proportional to the difference between the feedback voltage and an internal precision reference

(0.6 V). The output of the transconductance amplifier is connected to the COMP pin, allowing the user to

provide external control loop compensation. A type-II compensation network is generally recommended for peak

current-mode control.

The amplifier has two gain settings, one is for normal operation with a gm of 1200 µS and the other is for

ultra-low IQ with a gm of 60 µS. For normal operation, connect MODE to AGND. For ultra-low operation, IQ

connect MODE to AGND through a 10-kΩ resistor.

8.3.13 Slope Compensation

The LM5143-Q1 provides internal slope compensation for stable operation with peak current-mode control and a

duty cycle greater than 50%. Use Equation 10 to calculate the buck inductance to provide a slope compensation

contribution equal to one times the inductor downslope.

24

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

LO-IDEAL ( +

•

•

VOUT (V) ˜ RS (m:)

24 ˜ FSW (MHz)

(10)

A lower inductance value generally increases the peak-to-peak inductor current, which minimizes size and

cost, and improves transient response at the cost of reduced light-load efficiency due to higher cores losses

and peak currents.

A higher inductance value generally decreases the peak-to-peak inductor current, which increases the fullload efficiency by reducing switch peak and RMS currents at the cost of requiring larger output capacitors to

meet load-transient specifications.

8.3.14 Inductor Current Sense (CS1, VOUT1, CS2, VOUT2)

There are two methods to sense the inductor current of the buck power stage. The first uses a current sense

resistor (also known as a shunt) in series with the inductor, and the second avails of the DC resistance of the

inductor (DCR current sensing).

8.3.14.1 Shunt Current Sensing

Figure 8-4 illustrates inductor current sensing using a shunt resistor. This configuration continuously monitors the

inductor current to provide accurate overcurrent protection across the operating temperature range. For optimal

current sense accuracy and overcurrent protection, use a low inductance ±1% tolerance shunt resistor between

the inductor and the output, with a Kelvin connection to the LM5143-Q1 current sense amplifier.

If the peak differential current signal sensed from CS to VOUT exceeds the current limit threshold of 73 mV, the

current limit comparator immediately terminates the applicable HO output for cycle-by-cycle current limiting. Use

Equation 11 to calculate the shunt resistance.

RS

VCS

IOUT(CL)

'IL

2

(11)

where

•

•

•

VCS is current sense threshold of 73 mV

IOUT(CL) is the overcurrent setpoint that is set higher than the maximum load current to avoid tripping the

overcurrent comparator during load transients

ΔIL is the peak-to-peak inductor ripple current

VIN

LO

RS

VOUT1

CO

Current Sense

Amplifier

VOUT1

CS1

+

CS gain = 12

Figure 8-4. Shunt Current Sensing Implementation

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

25

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

The respective SS voltage is clamped 150 mV above FB during an overcurrent condition for each channel.

Sixteen overcurrent events must occur before the SS clamp is enabled. This makes sure that SS can be pulled

low during brief overcurrent events, preventing output voltage overshoot during recovery.

8.3.14.2 Inductor DCR Current Sensing

For high-power applications that do not require accurate current-limit protection, inductor DCR current sensing

is preferable. This technique provides lossless and continuous monitoring of the inductor current using an RC

sense network in parallel with the inductor. Select an inductor with a low DCR tolerance to achieve a typical

current limit accuracy within the range of 10% to 15% at room temperature. Components RCS and CCS in Figure

8-5 create a low-pass filter across the inductor to enable differential sensing of the voltage drop across the

inductor DCR.

VIN

LO

RDCR

VOUT1

CO

RCS

CCS

Current Sense

Amplifier

VOUT1

CS1

+

CS gain = 12

Figure 8-5. Inductor DCR Current Sensing Implementation

Use Equation 12 to calculate the voltage drop across the sense capacitor in the s-domain. When the RCSCCS

time constant is equal to LO/RDCR, the voltage developed across the sense capacitor, CCS, is a replica of the

inductor DCR voltage and accurate current sensing is achieved. If the RCSCCS time constant is not equal to the

LO/RDCR time constant, there is a sensing error as follows:

•

•

RCSCCS > LO/RDCR → the DC level is correct, but the AC amplitude is attenuated.

RCSCCS < LO/RDCR → the DC level is correct, but the AC amplitude is amplified.

LO

RDCR

§

˜ RDCR ˜ ¨ IOUT(CL)

1 s ˜ RCS ˜ CCS

©

1 s˜

VCS (s)

'IL ·

¸

2 ¹

(12)

Choose the CCS capacitance greater than or equal to 0.1 μF to maintain a low-impedance sensing network, thus

reducing the susceptibility of noise pickup from the switch node. Carefully observe Section 11.1 to make sure

that noise and DC errors do not corrupt the differential current sense signals applied between the CS and VOUT

pins.

8.3.15 Hiccup Mode Current Limiting (RES)

The LM5143-Q1 includes an optional hiccup mode protection function that is enabled when a capacitor is

connected to the RES pin. In normal operation, the RES capacitor is discharged to ground. If 512 cycles of

cycle-by-cycle current limiting occurs, SS is pulled low and the HO and LO outputs are disabled (see Figure 8-6).

A 20-μA current source begins to charge the RES capacitor. When the RES voltage increases to 1.2 V, RES

is pulled low and the SS capacitor begins to charge. The 512-cycle hiccup counter is reset if four consecutive

switching cycles occur without exceeding the current limit threshold. Separate hiccup counters are provided for

each channel, but the RES pin is shared by both channels. One channel can be in hiccup protection while

the other operates normally. In the event that both channels are in an overcurrent condition triggering hiccup

26

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: LM5143-Q1

�LM5143-Q1

www.ti.com

SNVSB29C – OCTOBER 2018 – REVISED JUNE 2021

protection, the last hiccup counter to expire pulls RES low and starts the RES capacitor charging cycle. Both

channels then restart together when V RES = 1.2 V. If RES is connected to VDDA at power up, the hiccup function

is disabled for both channels.

1.2 V RES Threshold

Current Limit

Detected

RES

IRES = 20 PA

0V

SS

ISS = 20 PA

VREF = 0.6 V

VFB + 150 mV

tRES

Current Limit persists

during 512 consecutive

clock cycles

Hiccup delay

± no switching

tSS

Soft-start time

Figure 8-6. Hiccup Mode Timing Diagram

Use Equation 13 to calculate the RES capacitance.

CRES (nF) 17 ˜ tRES (ms)

(13)

where

•

tRES is the specified hiccup delay as shown in Figure 8-6

8.3.16 High-Side and Low-Side Gate Drivers (HO1/2, LO1/2, HOL1/2, LOL1/2)

The LM5143-Q1 contains N-channel MOSFET gate drivers and an associated high-side level shifter to drive the