LMK03806 Evaluation Board

User's Guide

November 2013

SNAU075A

�LMK03806

Ultra-low Jitter Clock Generator with 14 Outputs

Evaluation Board Operating Instructions

2

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�CONTENTS

1. INTRODUCTION ......................................................................................................... 5

2. QUICK START ............................................................................................................ 6

3. DEFAULT CODELOADER MODES FOR EVALUATION BOARDS ......................... 7

4. EXAMPLE: USING CODELOADER TO PROGRAM THE LMK03806B ................... 8

5. PROGRAM/LOAD DEVICE ........................................................................................ 9

6. RESTORING A DEFAULT MODE .............................................................................. 9

7. VISUAL CONFIRMATION OF FREQUENCY LOCK ................................................ 10

8. ENABLE CLOCK OUTPUTS .................................................................................... 10

9. PLL LOOP FILTERS AND LOOP PARAMETERS .................................................. 11

10. EVALUATION BOARD INPUTS AND OUTPUTS .................................................. 12

12. CODELOADER USAGE ......................................................................................... 16

13. TYPICAL PHASE NOISE PERFORMANCE PLOTS ............................................. 23

14. SCHEMATICS ......................................................................................................... 27

15. PCB LAYERS STACKUP ....................................................................................... 35

16. PCB LAYOUT.......................................................................................................... 36

APPENDIX A: EVM SOFTWARE AND COMMUNICATION: INTERFACING UWIRE ... 41

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

3

�LIST OF FIGURES

Figure 1: Quick Start Diagram ...................................................................................................................................... 6

Figure 2: Selecting a Default Mode for the LMK03806B Device .................................................................................. 7

Figure 4: Loading the Device ........................................................................................................................................ 9

Figure 5: Setting the Default mode for LMK03806 ....................................................................................................... 9

Figure 6: Setting Digital Delay, Clock Divider, Analog Delay, and Output Format for CLKout0 ................................. 10

Figure 7: Setting LVCMOS modes ............................................................................................................................. 10

Figure 8: Port Setup Tab............................................................................................................................................. 16

Figure 9: Clock Outputs Tab ....................................................................................................................................... 17

Figure 10: PLL Tab ..................................................................................................................................................... 18

Figure 11: Bits/Pins Tab.............................................................................................................................................. 20

Figure 12: Registers Tab ............................................................................................................................................ 22

Figure 13: LMK03806B PLL VCO div2 LVPECL Phase Noise................................................................................... 23

Figure 14: LMK03806B div8 CLKout LVPECL Phase Noise ...................................................................................... 25

Figure 15: LMK03806B div8 CLKout LVDS Phase Noise .......................................................................................... 25

Figure 16: LMK03806B div8 CLKout LVCMOS Phase Noise .................................................................................... 26

Figure 17 - LMK03806 Power Supply Schematic ....................................................................................................... 27

Figure 18 - LMK03806 Device Schematic .................................................................................................................. 28

Figure 19 - Outputs, (OSCout, CLKout0/1/2/3) Schematics ....................................................................................... 29

Figure 20 - LMK03806 Clock Outputs 4 through 7 Schematics ................................................................................. 30

Figure 21 - LMK03806 Clock Outputs 8 through 11 Schematics ............................................................................... 31

Figure 22: PCB Stackup ............................................................................................................................................. 35

Figure 23: Layer 1 - Top ............................................................................................................................................. 36

Figure 24: Layer 2 – RF Ground Plane ....................................................................................................................... 37

Figure 25: Layer 3 – Vcc Planes ................................................................................................................................. 38

Figure 26: Layer 4 - Bottom ........................................................................................................................................ 39

Figure 27: Top and Bottom (Composite) .................................................................................................................... 40

List of Tables

Table 1: EVM Contents ................................................................................................................................................. 5

Table 2: Default CodeLoader Modes for LMK03806 .................................................................................................... 7

Table 3: PLL Loop Filter Parameters for LMK03806B ................................................................................................ 11

Table 4: Evaluation Board Inputs and Outputs ........................................................................................................... 12

Table 5: Registers Controls and Descriptions in PLL Tab .......................................................................................... 18

Table 6: Datasheet to PCB Silkscreen Updates ......................................................................................................... 20

Table 7: Register Controls and Descriptions on Bits/Pins Tab ................................................................................... 21

Table 8: LMK03806B PLL VCO div2 Phase Noise and RMS Jitter (fs) ..................................................................... 23

Table 9: Typical Phase Noise Performance Plot Setup .............................................................................................. 24

Table 10: LMK03806B Phase Noise and RMS Jitter for Different CLKout Output Formats and Frequencies .......... 24

Table 11: Bill of Materials for LMK03806BEVAL Boards............................................................................................ 32

4

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�1. Introduction

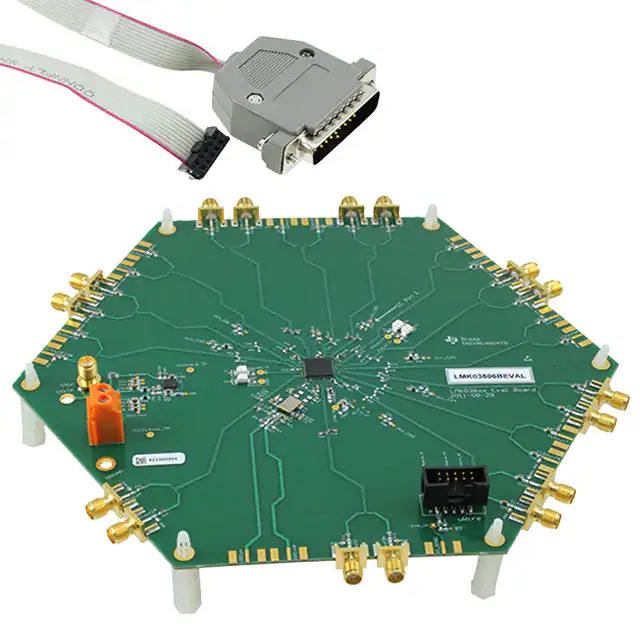

The Texas Instruments LMK03806BEVAL evaluation module (EVM) helps designers evaluate the operation

and performance of the LMK03806B high performance, ultra low-jitter, multirate clock generator.

Texas Instruments CodeLoader software can be used to program the internal registers of the

LMK03806B device through the USB2ANY-uWire interface. The CodeLoader software will run

on a Windows 7 or Windows XP PC and can be downloaded from

http://www.ti.com/tool/codeloader

The EVM contains (See Table 1):

Table 1: EVM Contents

QUANTITY

November 2013

1

DESCRIPTION

LMK03806BEVAL

1

LKM03806 Quick Start Guide

1

Interface cables (LPT or USB)

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

5

�2. Quick Start

1.

Connect a voltage of 5.0 volts to the Vcc SMA connector or terminal block. Device operates at

3.3 V using onboard LP3878-ADJ LDO.

2. Connect the uWire header via LPT or USB2ANY-uWire (See “EVM Software and

Communication” Section for more information).

3. Program the device with CodeLoader. CodeLoader is available for download at:

www.ti.com/tool/codeloader

a. Select correct LMK03806B from “Select Device Clock Conditioners” Menu.

b. Select a default mode from the “Mode” Menu. For the quick start use, “100 MHz

TCXO/XO Reference”

c. Ctrl-L must be pressed at least once to load all registers. Alternatively click menu Keyboard

Controls Load Device.

4. Measurements may be made at an active CLKout port via its SMA connector. Please see also

.

CLKout0

CLKout0*

CLKout2

CLKout2*

CL

CL Kou

Ko t 4

ut 4

*

0*

ut1

K o ut 10

L

C Ko

CL

LMK03806

uWire

header

CL

CL Kou

Ko t 8

ut 8

*

1

Power

5.0 V

(LDO)

OSCout0

OSCout0*

CL

K

CL out 6

Ko

ut 6 *

3

2

Program with CodeLoader

Be sure to press ‘Ctrl - L’

For interfacing

the board

please see

Appendix A

Laptop or PC

Figure 1: Quick Start Diagram

6

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�3. Default CodeLoader Modes for Evaluation Boards

CodeLoader saves the state of the selected LMK03806B device when exiting the software. To ensure a

common starting point, the following modes listed in Table 2: Default CodeLoader Modes for LMK03806

may be restored by clicking “Mode” and selecting the appropriate device configuration, as shown in

Figure 2 in the case of the LMK03806B device. Similar default modes are available for each

LMK03806B device in CodeLoader.

Figure 2: Selecting a Default Mode for the LMK03806B Device

After restoring a default mode, press Ctrl+L to program the device. The default modes also disable

certain outputs, so make sure to enable the output under test to make measurements.

Table 2: Default CodeLoader Modes for LMK03806

Default CodeLoader Mode

LMK03806B, 100 MHz

XO

Frequency

100 MHz

The next section outlines step-by-step procedures for using the evaluation board with the LMK03806B.

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

7

�4. Example: Using CodeLoader to Program the LMK03806B

The purpose of this section is to walk the user through using CodeLoader 4 to make some measurements

with the LMK03806B device as an example. For more information on CodeLoader refer to CodeLoader

Usage or the CodeLoader 4 instructions located at http://www.ti.com/tool/codeloader.

Before proceeding, be sure to follow the Quick Start section to ensure proper connections.

1. Start CodeLoader 4 Application

Click “Start” “Programs” “CodeLoader 4” “CodeLoader 4”

The CodeLoader 4 program is installed by default to the CodeLoader 4 application group.

2. Select Device

Click “Select Device” “Clock Conditioners” “LMK03806B”

Once started CodeLoader 4 will load the last used device. To load a new device click “Select Device”

from the menu bar, then select the subgroup and finally device to load. For this example, the

LMK03806B is chosen. Selecting the device does cause the device to be programmed.

8

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�5. Program/Load Device

Assuming the Port Setup settings are correct, press the “Ctrl+L” shortcut or click “Keyboard Controls”

“Load Device” from the menu to program the device to the current state of the newly loaded LMK03806

file.

Figure 3: Loading the Device

Once the device has been initially loaded, CodeLoader will automatically program changed registers so it

is not necessary to re-load the device upon subsequent changes in the device configuration. It is possible

to disable this functionality by ensuring there is no checkmark by the “Options” “AutoReload with

Changes.”

Because a default mode will be restored in the next step, this step isn’t really needed but included to

emphasize the importance of pressing “Ctrl+L” to load the device at least once after starting CodeLoader,

restoring a mode, or restoring a saved setup using the File menu.

See CodeLoader Usage or the CodeLoader 4 instructions located at http://www.ti.com/tool/codeloader

for more information on Port Setup. Error! Reference source not found. contains information on

troubleshooting communications.

6. Restoring a Default Mode

Click “Mode” “100 MHz XO/TCXO Reference”; then press Ctrl+L.

Figure 4: Setting the Default mode for LMK03806

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

9

�For the purpose of this walkthrough, a default mode will be loaded to ensure a common starting point.

This is important because when CodeLoader is closed, it remembers the last settings used for a particular

device. Again, remember to press Ctrl+L as the first step after loading a default mode.

7. Visual Confirmation of Frequency Lock

After a default mode is restored and loaded, LED D4, should illuminate red when the PLL is locked to the

reference crystal.

8. Enable Clock Outputs

While the LMK03806B offers programmable clock output buffer formats, the evaluation board is shipped

with preconfigured output terminations to match the default buffer type for each output. Refer to the

CLKout port description in the Evaluation Board Inputs and Outputs section.

To measure phase noise at one of the clock outputs, for example, CLKout0:

1. Click on the Clock Outputs tab,

2. Uncheck “Powerdown” in the Divider Powerdown box to enable the channel,

3. Set the following settings as needed:

a. Clock Divider value

b. Clock Output type.

Figure 5: Setting Digital Delay, Clock Divider, Analog Delay, and Output Format for

CLKout0

4. Depending on the configured output type, the clock output SMAs can be interfaced to a test

instrument with a single-ended 50-ohm input as follows.

a. For LVDS:

i. A balun (like ADT2-1T) is recommended for differential-to-single-ended

conversion.

b. For LVPECL:

i. A balun can be used, or

ii. One side of the LVPECL signal can be terminated with a 50-ohm load and the

other side can be run single-ended to the instrument.

c. For LVCMOS:

i. There are two single-ended outputs, CLKoutX and

CLKoutX*, and each output can be set to Normal, Inverted,

or Off. There are nine (9) combinations of LVCMOS

modes in the Clock Output list.

ii. One side of the LVCMOS signal can be terminated with a

50-ohm load and the other side can be run singleFigure 6: Setting LVCMOS

ended to the instrument.

iii. A balun may also be used. Ensure CLKoutX and CLKoutX* states are

complementary, i.e.: Norm/Inv or Inv/Norm.

5. The phase noise may be measured with a spectrum analyzer or signal source analyzer.

10

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�See Typical Phase Noise Performance Plots for phase noise plots of the clock outputs. TI’s Clock Design

Tool can be used to calculate divider values to achieve desired clock output frequencies. See:

http://www.ti.com/tool/codeloader.

9. PLL Loop Filters and Loop Parameters

The default loop filter for the PLL has been configured for a 60 kHz bandwidth. The following table

contains the parameters for the PLL.

TI’s Clock Design Tool can be used to optimize PLL phase noise/jitter for given specifications. See:

http://www.ti.com/tool/codeloader.

PLL Loop Filter

Table 3: PLL Loop Filter Parameters for LMK03806B

Integrated VCO PLL

20 MHz Reference

0.022

C1_LF

18

C2_LF

0.01

C3 (internal)

0.01

C4 (internal)

0.82

R2_A2

0.2

R3 (internal)

0.2

R4 (internal)

Charge

Pump

3.2

Current, K

Phase

20

Detector

Frequency

2500

Frequency

19

Kvco

25

N

5

P

Phase

75

Margin

Loop

63

Bandwidth

100 MHz Reference

.022

18

0.01

0.01

0.82

0.2

0.2

nF

nF

nF

nF

kΩ

kΩ

kΩ

3.2

mA

100

MHz

2400

19

12

2

MHz

MHz/V

70

degrees

60

kHz

Note: PLL Loop Bandwidth is a function of K, Kvco, N as well as loop components. Changing K and

N will change the loop bandwidth.

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

11

�10. Evaluation Board Inputs and Outputs

The following table contains descriptions of the inputs and outputs for the evaluation board. Unless

otherwise noted, the connectors described can be assumed to be populated by default. Additionally,

some applicable CodeLoader programming controls are noted for convenience.

Table 4: Evaluation Board Inputs and Outputs

Connector Name

Signal Type,

Input/Output

Description

Clock outputs with programmable output buffers.

The output terminations by default on the evaluation

board are shown below, and the output type selected

by default in CodeLoader is indicated by an asterisk

(*):

Clock output pair

SMAs Populated:

CLKout0, CLKout0*,

CLKout2, CLKout2*,

CLKout4, CLKout4*,

CLKout6, CLKout6*,

CLKout8, CLKout8*,

CLKout10, CLKout10*

SMAs Not Populated:

CLKout1, CLKout1*,

CLKout3, CLKout3*,

CLKout5, CLKout5*,

CLKout7, CLKout7*,

CLKout9, CLKout9*,

CLKout11, CLKout11*

Analog,

Output

CLKout0

CLKout1

CLKout2

CLKout3

CLKout4

CLKout5

CLKout6

CLKout7

CLKout8

CLKout9

CLKout10

CLKout11

Default Board

Termination

LVPECL*

LVPECL

LVPECL*

LVPECL

LVDS* / LVCMOS

LVDS / LVCMOS

LVDS* / LVCMOS

LVDS / LVCMOS

LVDS* / LVCMOS

LVDS / LVCMOS

LVPECL*

LVPECL

Each CLKout pair has a programmable LVDS,

LVPECL, or LVCMOS buffer. The output buffer

type can be selected in CodeLoader in the Clock

Outputs tab via the CLKoutX_TYPE control.

All clock outputs are AC-coupled to allow safe

testing with RF test equipment.

All LVPECL clock outputs are source-terminated

using 240-ohm resistors.

If an output pair is programmed to LVCMOS, each

output can be independently configured (normal,

inverted, or off/tri-state).

12

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Connector Name

Signal Type,

Input/Output

Description

Buffered outputs of OSCin port.

The output terminations on the evaluation board are

shown below, the output type selected by default in

CodeLoader is indicated by an asterisk (*):

Default Board

OSC output pair

Termination

OSCout0

LVPECL* (fixed)

OSCout1

LVPECL* (fixed)

OSCout0, OSCout0*,

OSCout1, OSCout1*

Analog,

Output

Only OSCout0 has a programmable LVDS,

LVPECL, or LVCMOS output buffer. The OSCout0

buffer type can be selected in CodeLoader on the

Clock Outputs tab via the OSCout0_TYPE control.

OSCout1 has LVPECL buffer only but has

programmable swing amplitude.

Both OSCout pairs are AC-coupled to allow safe

testing with RF test equipment.

The OSCout0 and OSCout1 outputs are sourceterminated using 240-ohm resistors.

If OSCout0 is programmed as LVCMOS, each

output can be independently configured (normal,

inverted, inverted, and off/tri-state).

Main power supply input for the evaluation board.

A 3.9 V DC power source applied to this SMA will,

by default, source the onboard LDO regulators that

power the inner layer planes that supply the

LMK03806B.

Vcc

Power,

Input

The LMK03806B contains internal voltage

regulators for the VCO, PLL and other internal

blocks. The clock outputs do not have an internal

regulator, so a clean power supply with sufficient

output current capability is required for optimal

performance.

On-board LDO regulators and 0 resistor options

provide flexibility to supply and route power to

various devices. See schematics for more details.

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

13

�Connector Name

Signal Type,

Input/Output

J1

Power,

Input

Description

Alternative power supply input for the evaluation

board using two unshielded wires (Vcc and GND).

Apply power to either Vcc SMA or J1, but not both.

By default, these SMAs are not connected to the

traces going to the OSCin/OSCin* pins of the

LMK03806B. Instead, the onboard crystal drives the

OSCin input of the device.

OSCin, OSCin*

Analog,

Input

A single-ended or differential signal may be used to

drive the OSCin/OSCin* pins and must be AC

coupled. If operated in single-ended mode, the

unused input must be connected to GND with 0.1 uF.

Refer to the LMK03806 Datasheet section

“Electrical Characteristics” for PLL Reference Input

(OSCin) specifications.

10-pin header for uWire programming interface and

programmable logic I/O pins for the LMK03806B.

uWire

CMOS,

Input/Output

The uWire interface includes CLKuWire,

DATAuWire, and LEuWire signals.

The programmable logic I/O signals accessible

through this header include: SYNC. SYNC also has

a dedicated SMA and test point.

Programmable status I/O pin. By default, set as an

input pin for synchronize the clock outputs with a

fixed and known phase relationship between each

clock output selected for SYNC.

SYNC

CMOS,

Input/Output

In the default CodeLoader mode, SYNC will asserted

when the SYNC pin is low and the outputs to be

synchronized will be held in a logic low state. When

SYNC is unasserted, the clock outputs to be

synchronized are activated and will be initially phase

aligned with each other except for outputs

programmed with different digital delay values.

A SYNC event can also be programmed by toggling

the SYNC_POL_INV bit in the Bits/Pins tab in

CodeLoader.

Refer to the LMK03806 Datasheet section “Clock

Output Synchronization” for more information.

14

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�11. Recommended Test Equipment

Power Supply

The Power Supply should be a low noise power supply, particularly when the devices on the board are

being directly powered (onboard LDO regulators bypassed).

Phase Noise / Spectrum Analyzer

To measure phase noise and RMS jitter, an Agilent E5052 Signal Source Analyzer is recommended.

An Agilent E4445A PSA Spectrum Analyzer with the Phase Noise option is also usable although the

architecture of the E5052 is superior for phase noise measurements. At frequencies less than 100

MHz the local oscillator noise of the E4445A is too high and measurements will reflect the E4445A’s

internal local oscillator performance, not the device under test.

Oscilloscope

To measure the output clocks for AC performance, such as rise time or fall time, propagation delay, or

skew, it is suggested to use a real-time oscilloscope with at least 1 GHz analog input bandwidth (2.5+

GHz recommended) with 50 ohm inputs and 10+ Gsps sample rate. To evaluate clock

synchronization or phase alignment between multiple clock outputs, it’s recommended to use phasematched, 50-ohm cables to minimize external sources of skew or other errors/distortion that may be

introduced if using oscilloscope probes.

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

15

�12. CodeLoader Usage

Code Loader is used to program the evaluation board with either an LPT or USB2ANY-uWire interface

available from http://www.ti.com.

Port Setup Tab

Figure 7: Port Setup Tab

On the Port Setup tab, the user may select the type of communication port (LPT or USB) that will be used

to program the device on the evaluation board.

The Pin Configuration field is hardware dependent and normally does not need to be changed by the user.

Figure 7: Port Setup Tab shows the default settings.

16

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Clock Outputs Tab

Figure 8: Clock Outputs Tab

The Clock Outputs tab allows the user to control the output channel blocks, including:

Clock Group Source from either Crystal or OSCin

Channel Powerdown (affects clock divider, and buffer blocks)

Clock Divide value

Clock Output format (per output)

Clicking on the cyan-colored PLL block that contains R, PDF and N values will bring the PLL tab into

focus where these values may be modified, if needed.

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

17

�Clicking on the values in the box containing the Internal Loop Filter component (R3, C3, R4, C4) allow

one to step through the possible values. Left click to increase the component value, and right click to

decrease the value. These values can also be changed in the Bits/Pins tab.

The Reference Oscillator value field may be changed in either the Clock Outputs tab or the PLL tab.

The PLL Reference frequency should match the frequency of the onboard Crystal.

PLL Tab

Figure 9: PLL Tab

The PLL tab allows the user to change the following parameters in Table 5.

Table 5: Registers Controls and Descriptions in PLL Tab

Control Name

Reference Oscillator

Frequency (MHz)

Phase Detector Frequency

(MHz)

Register Name

OSCin_FREQ

VCO Frequency (MHz)

n/a

18

SNAU075A

n/s

Description

OSCin frequency from the External OSCin

connector or Crystal.

PLL Phase Detector Frequency (PDF). This

value is calculated as:

PLL PDF = OSCin Frequency

*(2EN_PLL_REF_2X) / (PLL_R).

Internal VCO Frequency should be within

the allowable range of the LMK03806B

device.

This value is calculated as:

VCO Frequency = PLL PDF * (PLL_N *

PLL_P).

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Doubler

EN_PLL_REF_2X

R Counter

N Counter

OSCout Divider

Phase Detector Polarity

PLL_R

PLL_N

PLL_P

PLL_CP_POL

Charge Pump Gain

PLL_CP_GAIN

Charge Pump State

PLL_CP_TRI

PLL Doubler.

0 = Bypass Doubler

1 = Enable Doubler

PLL R Counter value (1 to 4095).

PLL N Counter value (1 to 49140).

PLL N Prescaler value (2 to 8).

PLL Phase Detector Polarity.

Click on the polarity sign to toggle polarity

“+” or “–”.

PLL Charge Pump Gain.

Left-click/right-click to increase/decrease

charge pump gain (100, 400, 1600, 3200

uA).

PLL Charge Pump State.

Click to toggle between Active and Tri-State.

Changes made on this tab will be reflected in the Clock Outputs tab. The VCO Frequency should

conform to the specified internal VCO frequency range for the LMK03806B.

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

19

�Bits/Pins Tab

Figure 10: Bits/Pins Tab

The Bits/Pins tab allows the user to program bits directly, many of which are not available on other tabs.

Brief descriptions for the controls on this tab are provided in Table 7: Register Controls and Descriptions

on Bits/Pins Tab to supplement the datasheet. Refer to the LMK03806 Datasheet for more information.

TIP: Right-clicking any register name in the Bits/Pins tab will display a Help prompt with the register

address, data bit location/length, and a brief register description.

Note: Table 6 shows some differences between the datasheet names and PCB names for -002 PCB’s:

Table 6: Datasheet to PCB Silkscreen Updates

Datasheet Name

Readback (pin 27)

Ftest/LD (pin 33)

GPout0 (pin 62)

GPout1 (pin 63)

20

SNAU075A

PCB Silkscreen Identifier

Status0

Status1

Status2

Status3

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Table 7: Register Controls and Descriptions on Bits/Pins Tab

Mode Control

Group

IO Control – Sync

Output Control

Automatic

Update

Crystal

Register Name

RESET

POWERDOWN

uWire_LOCK

OSCin_FREQ

PLL_N_CAL

EN_PLL_XTAL

READBACK_TYPE

LD_MUX

LD_TYPE

GPO0

GPO1

SYNC_TYPE

SYNC_POL_INV

SYNC_PLL_DLD

NO_SYNC_CLKoutX_Y

PLL_DLD_CNT

PLL

EN_PLL_REF_2X

Program Pins

PLL_R3_LF

PLL_R4_LF

PLL_C3_LF

PLL_C4_LF

SYNC

TRIGGER

November 2013

Description

Resets the device to default register values. RESET

must be cleared for normal operation to prevent an

unintended reset every time R0 is programmed.

Places the device in powerdown mode.

When checked, no other uWire programming will

have effect. Must be unchecked to enable uWire

programming of registers R0 to R30.

Sets the OSCin frequency range.

Sets the PLL_N value.

Enables Crystal Oscillator.

Readback pin type. (Labeled Stats0 on PCB)

Ftest/LD pin selection when output. (Ftest/LD

output labeled Status1 on PCB)

Sets I/O pin type on the LD pin.

Sets logic level on the GPO0 pin. (Labeled Status2

on PCB)

Sets logic level on the GPO1 pin. (Labeled Status3

on PCB)

Sets I/O pin type on the SYNC pin.

Sets polarity on SYNC input to active low when

checked. Toggling this bit will initiate a SYNC

event.

Engage SYNC mode until PLL DLD is true

Synchronization will not affect selected clock

outputs, where X = even-numbered output and Y =

odd-numbered output.

The reference and feedback of PLL must be within

the window of phase error as specified by

PLL_WND_SIZE for this many cycles before PLL

digital lock detect is asserted.

Enables the doubler block to doubles the reference

frequency into the PLL R counter. This can allow

for frequency of 2/3, 2/5, etc. of OSCin to be used

at the phase detector of PLL.

Set the corresponding integrated PLL loop filter

values: R3, R4, C3, and C4.

It is also possible to set these values by clicking on

the loop filter values on the Clock Outputs tab.

Sets these pins on the uWire header to logic high

(checked) or logic low (unchecked).

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

21

�Registers Tab

Figure 11: Registers Tab

The Registers tab shows the value of each register. This is convenient for programming the device to the

desired settings, then exporting to a text file the register values in hexadecimal for use in your own

application.

By clicking in the “bit field” it is possible to manually change the value of registers by typing ‘1’ and ‘0.’

22

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�13. Typical Phase Noise Performance Plots

PLL

Figure 12: LMK03806B PLL VCO div2 LVPECL Phase Noise

Table 8: LMK03806B PLL VCO div2 Phase Noise and RMS Jitter (fs)

Offset

100 Hz

1 kHz

10 kHz

100 kHz

1 MHz

10 MHz

20 MHz

RMS Jitter (fs)

12 kHz to 20 MHz

RMS Jitter (fs)

100 Hz to 20 MHz

November 2013

Phase Noise (dBc/Hz)

-98.3

-107.8

-106.6

-114.2

-136.6

-150.6

-151.3

215

229

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

23

�Clock Outputs (CLKout)

The LMK03806 Family features programmable LVDS, LVPECL, and LVCMOS buffer modes for the

CLKoutX and OSCout0 output pairs. The OSCout1 output pair has a LVPECL buffer. Included below

are various phase noise measurements for each output format.

CLKout Phase Noise (div8 and div16)

For the LMK03806B, the internal VCO frequency is 2400 MHz. The divide-by-8 CLKout frequency is

312.5 MHz, and the divide-by-16 CLKout frequency is 156.25 MHz.

Table 9: Typical Phase Noise Performance Plot Setup

Parameter

LMK03806B Mode

Loop Filter Parameters

CLKout for LVDS/LVCMOS

CLKout for LVPECL

Condition

100 MHz TCXO/XO Reference

As shown under “100 MHz Reference” in Table 3

CLKout8, with CLKout8* terminated in to 50 Ω

CLKout10, with CLKout10* terminated in to 50 Ω

Table 10: LMK03806B Phase Noise and RMS Jitter for Different CLKout Output Formats and

Frequencies

Offset

100 Hz

1 kHz

10 kHz

100 kHz

1 MHz

10 MHz

20 MHz

RMS Jitter (fs)

12 kHz to 20 MHz

RMS Jitter (fs)

100 Hz to 20 MHz

24

SNAU075A

div8

LVPECL

-91.9

-113.8

-122.6

-128.7

-148.1

-157.6

-157.7

div8

LVDS

-92.0

-113.2

-122.7

-128.9

-147.7

-155.0

-155.1

div8

LVCMOS

-93.2

-113.4

-122.5

-128.4

-148.2

-157.2

-157.2

div16

LVPECL

-98.6

-119.8

-128.7

-134.8

-153.7

-160.5

-160.7

div16

LVDS

-98.8

-119.3

-128.4

-134.9

-153.0

-158.0

-158.1

div16

LVCMOS

-97.1

-119.0

-128.4

-134.4

-153.7

-160.4

-160.4

141.1

144.0

143.2

145.3

155.4

149.8

206.1

210.5

210.2

208.8

217.1

224.4

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Figure 13: LMK03806B div8 CLKout LVPECL Phase Noise

Figure 14: LMK03806B div8 CLKout LVDS Phase Noise

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

25

�Figure 15: LMK03806B div8 CLKout LVCMOS Phase Noise

26

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�14. Schematics

Power Supplies

1

2

3

4

5

6

Power Plane for LMK Except Outputs

VccCore_TP

TESTPOINT

VccCore

C41

0.1µF

Vcc Core Supplies Vcc1-VCO, Vcc4-Digital, Vcc5-CLKin, Vcc6-PLL, Vcc7-OSCout0, and Vcc9-PLL2

A

A

R81

120 FB

Direct Power

VccTP

Vcc

Vcc

R82

DNP

1000

1

TESTPOINT

C42

0.1µF

VccCore

C43

10µF

2

3

4

5

142-0701-201

Vcc8_PDCP2

C44

1µF

C45

0.1µF

J1

1

2

1

2

TERMBLOCK_2

Power Planes for LMK CLKout Outputs

TESTPOINT

VccCLKout_TP

B

R83

DNP

1000

VccCLKout

R84

C46

10µF

C47

1µF

0

C48

0.1µF

R86

0

R88

0

Vcc2_CG1_p17

DNPC49

470pF

Vcc3_CG2_p18

DNPC50

0.1µF

Vcc10_CG3_p47

DNPC51

470pF

R85

120 FB

R87

120 FB

R89

120 FB

B

Vcc2_CLKout_CG1

Vcc3_CLKout_CG2

Vcc10_CLKout_CG3

LDO Power Options

C

VccLDOin

C

R90

R92

0

0

LP3878SD-ADJ

V_LM3878-ADJ

U2

4

C53

4.7µF

R94

51k

8

2

7

9

IN

SD

OUT

ADJ

NC

BYP

NC

DAP GND

R93

5

C54

R97

2200pF 2.00k

1

C55

1µF

C56

10µF

R98

C58

0.1µF

LP3878SD-ADJ

R95

VccCLKout

0

120

3

R99

866

R100

0

LP3878-ADJ 3.3 V component values:

C340 = 4.7 uF

R351= 2.00 k

C346 = 0.01 uF

R356= 866

C352 = 10 uF

R350= 51 k

C341 = 2.2 nF

D

Vcc12_CG5_p57

DNPC57

470pF

Vcc13_CG0_p64

DNPC59

0.1µF

2

120 FB

Vcc11_CLKout_CG4

R96

120 FB

R101

120 FB

Vcc12_CLKout_CG5

Vcc13_CLKout_CG0

D

Texas Instruments and/or its licensors do not warrant the accuracy or completeness of this

specification or any information contained therein. Texas Instruments and/or its licensors do not

warrant that this design will meet the specifications, will be suitable for your application or fit for

any particular purpose, or will operate in an implementation. Texas Instruments and/or its

licensors do not warrant that the design is production worthy. You should completely validate

and test your design implementation to confirm the system functionality for your application.

1

R91

VccCore

120

6

Vcc11_CG4_p52

DNPC52

0.1µF

3

4

Mod. Date: 11/28/2011

Designed for: Evaluation Customer

Project: LMK038xx Evaluation Board

Sheet Title: Power Supplies

Sheet: 2 of 9

Size: B

Schematic: 870600688

Rev: 1.1

Assembly Variant: Customer Eval - 2011-11-22

File: Power.SchDoc

Contact: http://www.national.com/support

5

http://www.ti.com

© Texas Instruments CopyrightYear

6

Figure 16 - LMK03806 Power Supply Schematic

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

27

�LMK03806B Device with Loop Filter and Crystal Circuits

1

2

D1

R1

DNP

270

3

4

5

R2

DNP

270

Red

uWire Header and Level Translation

D2

uWire

Red

Status3_TP

Status2_TP

TESTPOINT

A

TESTPOINT

TESTPOINT

Vcc13_CLKout_CG0

6

Vcc12_CLKout_CG5

R3

15k

PLL Loop Filters

Vcc11_CLKout_CG4

10

8

6

4

2

LEuWire_TP

uWire_LE

R4

27k

DNPC1

100pF

9

7

5

3

1

HEADER_2X5

CLKout7_N

CLKout6_P

CLKout6*

CLKout7_P

CLKout6_N

49

50

51

CLKout7

CLKout7*

Vcc11

CLKout8_N

CLKout9_N

CLKout8_P

52

53

CLKout8

54

CLKout8*

55

CLKout9_P

CLKout9

CLKout9*

CLKout10_P

DAP PAD

Vcc7

LDObyp2

OSCin*

CLKout2

OSCin

TESTPOINT

OSCout1*

Vcc5

OSCout1

31

30

OSCout1_P

Status0_TP

Ftest/LD

CLKuWire_TP

IC_SYNC

DNP

DNPC2

100pF

R7

uWire_CLK

R6

27k

SMA

15k

R8

27k

DNPC3

100pF

48

Vcc10_CLKout_CG3

47

TESTPOINT

46

uWire_DATA

45

uWire_CLK

44

43

uWire_LE

15k

uWire_LE

C5

R11

DNP

0

C6

OSCout0_N

39

OSCout0_P

VccCore

C63

18

0.1µF

OSCin_N

36

OSCin_P

DNP

R14

270

R15

270

SMA

Y1

DNP

37

B

OSCin*

R12

R16

DNP

0

22pF

38

R10

27k

DNPC4

100pF

Vcc8_PDCP2

40

35

R9

uWire_CLK

42

41

DATAuWire_TP

uWire_DATA

uWire_DATA

VccCore

DNP

1µF

Y2

DNP

DNP

R17

DNP

100

VccCore

34

Status1_TP

33

R20

270

TESTPOINT

R18

0

C9

DNP

22pF

D3

OSCout1_N 32

NC

29

NC

28

27

22

CLKout5_P

Vcc2

Vcc3

18

17

Vcc2_CLKout_CG1

NC

CLKout3

C

Readback

NC

NC

Vcc6

CLKout3*

CLKout5

CLKout2*

CLKout5*

CLKout3_P 16

OSCout0

0

LDObyp1

21

CLKout3_N 15

Vcc1

CLKout5_N

CLKout2_N 14

OSCout0*

CLKout4*

CLKout2_P 13

C8

0.1µF

Vcc8

NC

CLKout4

12

C7

10µF

CPout

LMK03806

20

11

56

Vcc9

19

0.1µF

Vcc12

CLKout10_N

SYNC*

CLKout4_N

10

DNP

57

LEuWire

CLKout4_P

C62 VccCore

58

CLKout11_N

NC

7

TESTPOINT

NC

R300

DNP

51

8

NC

9

CLKout10

59

CLKout10*

61

60

CLKout11*

62

GPout0

CLKuWire

26

IC_SYNC

CLKout1

Vcc4

5

SYNC_TP

6

DATAuWire

25

B

CLKout1*

TESTPOINT

C2_LF

0.018µF

R2_LF

820

Vcc10

GND

CLKout1_P 4

DNPC2pLF

C1_LF

220pF

220pF

A

R5

15k

IC_SYNC

XTAL-mode Loop Filter

CLKout6

CLKout0*

24

CLKout1_N 3

CLKout0

23

CLKout0_N 2

CLKout11

64

Vcc13

CLKout0_P 1

GPout1

U1

LMK03806

63

CLKout11_P

VTUNE_TP

R19

270

C10

R22

DNP

0

C

OSCin

DNP

18

0.1µF

Green

R21

270

R23

DNP

SMA

Y3

3

Out

GND

2

DNPC64

R24

0.1µF 270

4

Vcc3_CLKout_CG2

VccCore

D4

VccCore

DNPC65

1µF

Red

Vcc Vcont

1

C60

TCXO

0.1µF R104

0

VccCore

R102

1.00k

R103

1.00k

C61

0.1µF

VccCore

D

D

Texas Instruments and/or its licensors do not warrant the accuracy or completeness of this

specification or any information contained therein. Texas Instruments and/or its licensors do not

warrant that this design will meet the specifications, will be suitable for your application or fit for

any particular purpose, or will operate in an implementation. Texas Instruments and/or its

licensors do not warrant that the design is production worthy. You should completely validate

and test your design implementation to confirm the system functionality for your application.

1

2

3

4

Mod. Date: 11/30/2011

Designed for: Evaluation Customer

Project: LMK038xx Evaluation Board

Sheet Title: Main Sheet / IC

Sheet:3 of 9

Size: B

Schematic: 870600688

Rev: 1.1

Assembly Variant: Customer Eval - 2011-11-22

File: LMK03806_PLL.SchDoc

Contact: http://www.national.com/support

5

http://www.ti.com

© Texas Instruments CopyrightYear

6

Figure 17 - LMK03806 Device Schematic

28

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Outputs, (OSCout0/1, CLKout0/1/2/3)

1

2

3

4

5

6

OSCout0 Default: LVDS, AC coupled

OSCout1

Default: LVPECL, AC coupled

R26

DNP

51

A

OSCout0_1_P

OSCout0_P

R27

240

R25

DNP

51

OSCout1

C11

OSCout0

C12

OSCout1_1_P

OSCout1_P

SMA

C13

240

0.1uF

SMA

A

0.1µF

GND

GND

OSCout1*

C14

OSCout0*

C15

OSCout0_1_N

OSCout0_N

R28

240

OSCout1_1_N

OSCout1_N

SMA

C16

240

0.1µF

SMA

0.1µF

R29

DNP

51

R30

DNP

51

GND

GND

CLKout2

CLKout0

Default: LVPECL, AC coupled

B

CLKout1

R31

DNP

51

CLKout0

C17

CLKout0_1_P

CLKout0_P

R34

240

SMA

Default: LVPECL, AC coupled

Default: LVPECL, AC coupled

R33

51

CLKout1_1_N

CLKout1_N

0.1µF

R36

240

GND

DNP

0.1µF

SMA

R35

240

CLKout0_1_N

R37

240

SMA

0.1µF

GND

SMA

0.1µF

GND

C22

CLKout1_P

R39

240

R40

DNP

51

B

CLKout2

CLKout2_1_P

CLKout2_P

GND

CLKout0*

C20

CLKout0_N

R32

DNP

51

C18

CLKout1*

C19

CLKout2*

C21

CLKout1

CLKout1_1_P

SMA

DNP

CLKout2_1_N

CLKout2_N

R38

240

0.1µF

R42

51

SMA

0.1µF

R41

DNP

51

GND

GND

CLKout3

C

C

Default: LVPECL, AC coupled

C23

CLKout3_N

R44

240

0.1µF

R43

51

CLKout3*

CLKout3_1_N

SMA

DNP

GND

C24

CLKout3_P

R45

240

0.1µF

CLKout3

CLKout3_1_P

SMA

DNP

R46

51

GND

D

D

Texas Instruments and/or its licensors do not warrant the accuracy or completeness of this

specification or any information contained therein. Texas Instruments and/or its licensors do not

warrant that this design will meet the specifications, will be suitable for your application or fit for

any particular purpose, or will operate in an implementation. Texas Instruments and/or its

licensors do not warrant that the design is production worthy. You should completely validate

and test your design implementation to confirm the system functionality for your application.

1

2

3

4

Mod. Date: 11/28/2011

Designed for: Evaluation Customer

Project: LMK038xx Evaluation Board

Sheet Title: Clock Outputs 1/3

Sheet:6 of 9

Size: B

Schematic: 870600688

Rev: 1.1

Assembly Variant: Customer Eval - 2011-11-22

File: OutClks0.SchDoc

Contact: http://www.national.com/support

5

Figure 18 - Outputs, (OSCout, CLKout0/1/2/3) Schematics

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

http://www.ti.com

© Texas Instruments CopyrightYear

6

29

�Clock Outputs (CLKout 4/5/6/7)

1

A

2

3

CLKout4

4

R48

51

CLKout4

C25

CLKout4_1_P

CLKout4_P

R49

DNP

240

CLKout4_1_N

R51

DNP

240

0.1µF

CLKout5_1_P

R52

DNP

240

R53

DNP

51

DNP

0.1µF

SMA

R54

51

GND

CLKout6

Default: LVDS or LVCMOS, AC coupled

DNP

51

CLKout6

C29

R57

CLKout6_2_P

R58

DNP

240

CLKout6_1_P

C30

CLKout7_N

SMA

0.1µF

R59

DNP

240

GND

0.1µF

R56

51

CLKout7*

CLKout7_1_N

SMA

DNP

GND

C31

CLKout6_2_N

R60

B

CLKout7

Default: LVDS or LVCMOS, AC coupled

R55

R61

DNP

240

C

CLKout6*

CLKout6_1_N

C32

CLKout7_P

SMA

0.1µF

R62

DNP

240

R63

DNP

51

GND

D

SMA

CLKout5

C28

CLKout5_P

SMA

GND

33

DNP

0.1µF

GND

CLKout4*

C27

CLKout6_N

CLKout5_1_N

R50

DNP

240

GND

C

CLKout5*

C26

CLKout5_N

SMA

0.1µF

CLKout4_N

33

A

Default: LVDS or LVCMOS, AC coupled

R47

DNP

51

CLKout6_P

6

CLKout5

Default: LVDS or LVCMOS, AC coupled

B

5

0.1µF

CLKout7

CLKout7_1_P

SMA

DNP

R64

51

GND

Notes:

D

1. Designators greater than and equal to 300 are placed on bottom of PCB

1

2

Texas Instruments and/or its licensors do not warrant the accuracy or completeness of this

specification or any information contained therein. Texas Instruments and/or its licensors do not

warrant that this design will meet the specifications, will be suitable for your application or fit for

any particular purpose, or will operate in an implementation. Texas Instruments and/or its

licensors do not warrant that the design is production worthy. You should completely validate

and test your design implementation to confirm the system functionality for your application.

3

4

Designed for: Evaluation Customer

Mod. Date: 11/28/2011

Project: LMK038xx Evaluation Board

Sheet Title: Clock Outputs 2/3

Sheet:7 of 9

Size: B

Schematic: 870600688

Rev: 1.1

Assembly Variant: Customer Eval - 2011-11-22

File: OutClks1.SchDoc

Contact: http://www.national.com/support

5

Figure 19 - LMK03806 Clock Outputs 4 through 7 Schematics

30

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

http://www.ti.com

© Texas Instruments CopyrightYear

6

November 2013

�Clock Outputs (CLKout8/9/10/11)

1

A

2

3

CLKout8

6

R66

51

CLKout8

C33

CLKout8_1_P

CLKout8_P

A

Default: LVDS or LVCMOS, AC coupled

R65

DNP

51

C34

CLKout9_N

SMA

0.1µF

R68

DNP

240

GND

0.1µF

CLKout9*

CLKout9_1_N

SMA

DNP

GND

CLKout8*

C35

CLKout8_1_N

CLKout8_N

R69

DNP

240

C36

CLKout9_P

SMA

0.1µF

R70

DNP

240

R71

DNP

51

GND

B

5

CLKout9

Default: LVDS or LVCMOS, AC coupled

R67

DNP

240

4

0.1µF

CLKout9

CLKout9_1_P

SMA

DNP

R72

51

GND

B

CLKout10

CLKout11

Default: LVPECL, AC coupled

Default: LVPECL, AC coupled

R73

DNP

51

CLKout10

C37

CLKout10_1_P

CLKout10_P

R75

240

C38

SMA

CLKout11_N

0.1µF

R76

240

GND

C

CLKout10_1_N

C40

SMA

CLKout11_P

0.1µF

R78

240

R79

DNP

51

GND

D

CLKout11*

CLKout11_1_N

SMA

DNP

GND

CLKout10*

C39

CLKout10_N

R77

240

0.1µF

R74

51

0.1µF

C

CLKout11

CLKout11_1_P

SMA

DNP

R80

51

GND

Notes:

D

1. Designators greater than and equal to 300 are placed on bottom of PCB

Texas Instruments and/or its licensors do not warrant the accuracy or completeness of this

specification or any information contained therein. Texas Instruments and/or its licensors do not

warrant that this design will meet the specifications, will be suitable for your application or fit for

any particular purpose, or will operate in an implementation. Texas Instruments and/or its

licensors do not warrant that the design is production worthy. You should completely validate

and test your design implementation to confirm the system functionality for your application.

1

2

3

4

Designed for: Evaluation Customer

Mod. Date: 11/28/2011

Project: LMK038xx Evaluation Board

Sheet Title: Clock Outputs 3/3

Sheet:8 of 9

Size: B

Schematic: 870600688

Rev: 1.1

Assembly Variant: Customer Eval - 2011-11-22

File: OutClks2.SchDoc

Contact: http://www.national.com/support

5

Figure 20 - LMK03806 Clock Outputs 8 through 11 Schematics

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

http://www.ti.com

© Texas Instruments CopyrightYear

6

31

�Bill of Materials

Table 11: Bill of Materials for LMK03806BEVAL Boards

Item

Description

Qty

1

CAP, CERM, 47pF, 50V, +/5%, C0G/NP0, 0603

CAP, CERM, 3900pF, 50V,

+/-10%, X7R, 0603

CAP, CERM, 0.1uF, 25V,

+/-5%, X7R, 0603

1

C1_LF

Kemet

1

C2_LF

MuRata

33

Kemet

1

C5, C8, C12, C15, C17,

C18, C19, C20, C21,

C22, C23, C24, C25,

C26, C27, C28, C29,

C30, C32, C33, C34,

C35, C36, C37, C38,

C39, C40, C41, C42,

C45, C48, C60, C61

C6

AVX

4

C7, C43, C46, C56

Kemet

C0805C106K8PACTU

10

Vishay-Dale

CRCW06030000Z0EA

Vishay-Dale

CRCW0603240RJNEA

Kemet

C0603C104K3RACTU

2

3

4

5

6

CAP, CERM, 22pF, 50V, +/5%, C0G/NP0, 0603

CAP, CERM, 10uF, 10V, +/10%, X5R, 0805

RES, 0 ohm, 5%, 0.1W,

0603

Designator

Manufacturer

PartNumber

C0603C470J5GACTU

GRM188R71H392KA01D

C0603C104J3RACTU

06035A220JAT2A

7

RES, 240 ohm, 5%, 0.1W,

0603

16

8

CAP, CERM, 0.1uF, 25V,

+/-10%, X7R, 0603

CAP, CERM, 1uF, 10V, +/10%, X5R, 0603

CAP, CERM, 4.7uF, 10V,

+/-10%, X5R, 0603

CAP, CERM, 2200pF, 50V,

+/-10%, X7R, 0603

CAP, CERM, 0.1uF, 16V,

+/-10%, X7R, 0603

Connector, SMT, End

launch SMA 50 Ohm

1

C11, C14, R18, R84,

R86, R88, R90, R95,

R100, R104

C13, C16, R27, R28,

R34, R35, R36, R37,

R38, R39, R44, R45,

R75, R76, R77, R78

C31

3

C44, C47, C55

Kemet

C0603C105K8PACTU

1

C53

Kemet

C0603C475K8PACTU

1

C54

Kemet

C0603C222K5RACTU

1

C58

Kemet

C0603C104K4RACTU

16

Emerson

Network

Power

9

10

11

12

13

14

LED 2.8X3.2MM 565NM

RED CLR SMD

3

CLKout0, CLKout0*,

CLKout2, CLKout2*,

CLKout4, CLKout4*,

CLKout6, CLKout6*,

CLKout8, CLKout8*,

CLKout10, CLKout10*,

OSCout0, OSCout0*,

OSCout1, OSCout1*

D1, D2, D4

15

LED 2.8X3.2MM 565NM

GRN CLR SMD

1

D3

16

CONN TERM BLK PCB

5.08MM 2POS OR

RES, 620 ohm, 5%, 0.1W,

0603

1

J1

Lumex

Opto/Compon

ents Inc.

Lumex

Opto/Compon

ents Inc.

Weidmuller

1

R2_LF

Vishay-Dale

17

32

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

142-0701-851

SML-LX2832IC

SML-LX2832GC

1594540000

CRCW0603620RJNEA

November 2013

�18

19

20

21

22

23

24

RES, 15k ohm, 5%, 0.1W,

0603

RES, 27k ohm, 5%, 0.1W,

0603

RES, 18 ohm, 5%, 0.1W,

0603

RES, 270 ohm, 5%, 0.1W,

0603

RES, 51 ohm, 5%, 0.1W,

0603

RES, 33 ohm, 5%, 0.1W,

0603

FB, 120 ohm, 500 mA, 0603

4

R3, R5, R7, R9

Vishay-Dale

CRCW060315K0JNEA

4

R4, R6, R8, R10

Vishay-Dale

CRCW060327K0JNEA

2

R12, R23

Vishay-Dale

CRCW060318R0JNEA

6

R14, R15, R19, R20,

R21, R24

R33, R42, R43, R46,

R48, R54, R56, R64,

R66, R72, R74, R80

R57, R60

Vishay-Dale

CRCW0603270RJNEA

Vishay-Dale

CRCW060351R0JNEA

Vishay-Dale

CRCW060333R0JNEA

12

2

1

R81, R85, R87, R89,

R91, R93, R96, R98,

R101

R92

Vishay-Dale

CRCW08050000Z0EA

1

R94

Vishay-Dale

CRCW060351K0JNEA

1

R97

Vishay-Dale

CRCW06032K00FKEA

1

R99

Vishay-Dale

CRCW0603866RFKEA

2

R103

Vishay-Dale

CRCW06031K00FKEA

6

1

S1, S2, S3, S4, S5, S6

U1

SPCS-14

LMK03806BISQ

1

U2

1

uWire

FCI

52601-G10-8LF

34

Micropower 800mA Low

Noise 'Ceramic Stable'

Adjustable Voltage

Regulator for 1V to 5V

Applications

Low Profile Vertical Header

2x5 0.100"

Connector, TH, SMA

VOLTREX

Texas

Instruments

Texas

Instruments

1

Vcc

35

100 MHz TCXO

1

Y3

36

CAP, CERM, 100pF, 50V,

+/-5%, C0G/NP0, 0603

CAP, CERM, 220pF, 50V,

+/-5%, C0G/NP0, 0603

CAP, CERM, 22pF, 50V, +/5%, C0G/NP0, 0603

CAP, CERM, 0.1uF, 25V,

+/-5%, X7R, 0603

CAP, CERM, 470pF, 50V,

+/-10%, X7R, 0603

CAP, CERM, 0.1uF, 25V,

+/-10%, X7R, 0603

CAP, CERM, 1uF, 25V, +/10%, X5R, 0805

0

C1, C2, C3, C4

Emerson

Network

Power

Connor

Winfield

Kemet

C0603C101J5GACTU

0

C2pLF

MuRata

GRM1885C1H221JA01D

0

C9

AVX

0

C10, C62, C64

Kemet

C0603C104J3RACTU

0

C49, C51, C57

Kemet

C0603C471K5RACTU

0

C50, C52, C59

Kemet

C0603C104K3RACTU

0

C63, C65

AVX

25

26

27

28

29

30

31

32

33

37

38

39

40

41

42

RES, 0 ohm, 5%, 0.125W,

0805

RES, 51k ohm, 5%, 0.1W,

0603

RES, 2.00k ohm, 1%, 0.1W,

0603

RES, 866 ohm, 1%, 0.1W,

0603

RES, 1.00k ohm, 1%, 0.1W,

0603

0.875" Standoff

LMK03806

November 2013

9

Murata

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

BLM18AG121SN1D

LP3878SD-ADJ

142-0701-201

CWX813-100.00M

06035A220JAT2A

08053D105KAT2A

SNAU075A

33

�43

Connector, SMT, End

launch SMA 50 Ohm

0

44

RES, 270 ohm, 5%, 0.1W,

0603

RES, 0 ohm, 5%, 0.1W,

0603

RES, 100 ohm, 5%, 0.1W,

0603

RES, 51 ohm, 5%, 0.1W,

0603

48

RES, 240 ohm, 5%, 0.1W,

0603

0

49

RES, 1.00k ohm, 1%, 0.1W,

0603

FB, 1000 ohm, 600 mA,

0603

45

46

47

50

51

34

SNAU075A

0

CLKout1, CLKout1*,

CLKout3, CLKout3*,

CLKout5, CLKout5*,

CLKout7, CLKout7*,

CLKout9, CLKout9*,

CLKout11, CLKout11*,

IC_SYNC, OSCin,

OSCin*

R1, R2

Vishay-Dale

CRCW0603270RJNEA

0

R11, R16, R22

Vishay-Dale

CRCW06030000Z0EA

0

R17

Vishay-Dale

CRCW0603100RJNEA

0

Vishay-Dale

CRCW060351R0JNEA

Vishay-Dale

CRCW0603240RJNEA

0

R25, R26, R29, R30,

R31, R32, R40, R41,

R47, R53, R55, R63,

R65, R71, R73, R79,

R300

R49, R50, R51, R52,

R58, R59, R61, R62,

R67, R68, R69, R70

R102

Vishay-Dale

CRCW06031K00FKEA

0

R82, R83

Murata

0

Y1, Y2

ECS

Emerson

Network

Power

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

142-0701-851

BLM18HE102SN1D

DNP_XTAL, ECS-20020-30B-DU

November 2013

�15. PCB Layers Stackup

6-layer PCB Stackup includes:

Top Layer for high-priority high-frequency signals (2 oz.)

FR4 Dielectric, 19 mils

RF Ground plane (1 oz.)

FR4, 14.5 mils

Power plane (1 oz.)

FR4, 19 mils

Bottom Layer copper clad for thermal relief (2 oz.)

Top Layer [LMK03806ENG.GTL]

FR4 (Er = 4.8)

19 mil

RF Ground plane [LMK03806ENG.G1]

Power plane #1 [LMK03806ENG.G2]

61.3 mil thick

FR4 (Er = 4.8)

14.5 mil

FR4

19 mil

Bottom Layer [LMK03806ENG.GBL]

Figure 21: PCB Stackup

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

35

�16. PCB Layout

Figure 22: Layer 1 - Top

36

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Figure 23: Layer 2 – RF Ground Plane

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

37

�Figure 24: Layer 3 – Vcc Planes

38

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Figure 25: Layer 4 - Bottom

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

39

�Figure 26: Top and Bottom (Composite)

40

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�Appendix A:

EVM Software and Communication: Interfacing uWire

Codeloader is the software used to communicate with the EVM (Please download the latest version from TI.com http://www.ti.com/tool/codeloader). This EVM can be controlled through the uWire interface on board. There are two

options in communicating with the uWire interface from the computer.

OPTION 1

Open Codeloader.exe Click “Select Device” Click “Port Setup” tab Click “LPT” (in Communication Mode)

OPTION 2

November 2013

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

SNAU075A

41

�The Adapter Board

This table describes the pins configuration on the adapter board for each EVM board (See examples below table)

Jumper Bank

Code Loader Configuration

EVM

A

B

C

D

E

F

G

H

LMX2581

A4 B1 C2

E5 F1 G1 H1 BUFEN (pin 1), Trigger (pin 7)

LMX2541

A4

C3

E4 F1 G1 H1 CE (pin 1), Trigger (pin 10)

LMK0400x

A0

C3

E5 F1 G1 H1 GOE (pin 7)

LMK01000

A0

C1

E5 F1 G1 H1 GOE (pin 7)

LMK030xx

A0

C1

E5 F1 G1 H1 SYNC (pin 7)

LMK02000

A0

C1

E5 F1 G1 H1 SYNC (pin 7)

LMK0480x

A0 B2 C3

E5 F0 G0 H1 Status_CLKin1 (pin 3)

LMK04816/4906

A0 B2 C3

E5 F0 G0 H1 Status_CLKin1 (pin 3)

LMK01801

A0 B4 C5

E2 F0 G0 H1 Test (pin 3), SYNC0 (pin 10)

LMK0482x (prelease)

A0 B5 C3 D2 E4 F0 G0 H1 CLKin1_SEL (pin 6), Reset (pin 10)

LMX2531

A0

E5 F2 G1 H2 Trigger (pin 1)

LMX2485/7

A0

C1

E5 F2 G1 H0 ENOSC (pin 7), CE (pin 10)

LMK03200

A0

E5 F0 G0 H1 SYNC (pin 7)

LMK03806

A0

C1

E5 F0 G0 H1

LMK04100

A0

C1

E5 F1 G1 H1

Example adapter configuration (LMK01801)

Open Codeloader.exe Click “Select Device” Click “Port Setup” Tab Click “USB” (in Communication Mode)

*Remember to also make modifications in “Pin Configuration” Section according to Table above.

42

SNAU075A

LMK3806 Evaluation Board

Copyright © 2013, Texas Instruments Incorporated

November 2013

�STANDARD TERMS AND CONDITIONS FOR EVALUATION MODULES

1.

Delivery: TI delivers TI evaluation boards, kits, or modules, including any accompanying demonstration software, components, or

documentation (collectively, an “EVM” or “EVMs”) to the User (“User”) in accordance with the terms and conditions set forth herein.

Acceptance of the EVM is expressly subject to the following terms and conditions.

1.1 EVMs are intended solely for product or software developers for use in a research and development setting to facilitate feasibility

evaluation, experimentation, or scientific analysis of TI semiconductors products. EVMs have no direct function and are not

finished products. EVMs shall not be directly or indirectly assembled as a part or subassembly in any finished product. For

clarification, any software or software tools provided with the EVM (“Software”) shall not be subject to the terms and conditions

set forth herein but rather shall be subject to the applicable terms and conditions that accompany such Software

1.2 EVMs are not intended for consumer or household use. EVMs may not be sold, sublicensed, leased, rented, loaned, assigned,

or otherwise distributed for commercial purposes by Users, in whole or in part, or used in any finished product or production

system.

2

Limited Warranty and Related Remedies/Disclaimers:

2.1 These terms and conditions do not apply to Software. The warranty, if any, for Software is covered in the applicable Software

License Agreement.

2.2 TI warrants that the TI EVM will conform to TI's published specifications for ninety (90) days after the date TI delivers such EVM

to User. Notwithstanding the foregoing, TI shall not be liable for any defects that are caused by neglect, misuse or mistreatment

by an entity other than TI, including improper installation or testing, or for any EVMs that have been altered or modified in any

way by an entity other than TI. Moreover, TI shall not be liable for any defects that result from User's design, specifications or

instructions for such EVMs. Testing and other quality control techniques are used to the extent TI deems necessary or as

mandated by government requirements. TI does not test all parameters of each EVM.

2.3 If any EVM fails to conform to the warranty set forth above, TI's sole liability shall be at its option to repair or replace such EVM,

or credit User's account for such EVM. TI's liability under this warranty shall be limited to EVMs that are returned during the

warranty period to the address designated by TI and that are determined by TI not to conform to such warranty. If TI elects to

repair or replace such EVM, TI shall have a reasonable time to repair such EVM or provide replacements. Repaired EVMs shall

be warranted for the remainder of the original warranty period. Replaced EVMs shall be warranted for a new full ninety (90) day

warranty period.

3

Regulatory Notices:

3.1 United States

3.1.1

Notice applicable to EVMs not FCC-Approved:

This kit is designed to allow product developers to evaluate electronic components, circuitry, or software associated with the kit

to determine whether to incorporate such items in a finished product and software developers to write software applications for

use with the end product. This kit is not a finished product and when assembled may not be resold or otherwise marketed unless

all required FCC equipment authorizations are first obtained. Operation is subject to the condition that this product not cause

harmful interference to licensed radio stations and that this product accept harmful interference. Unless the assembled kit is

designed to operate under part 15, part 18 or part 95 of this chapter, the operator of the kit must operate under the authority of

an FCC license holder or must secure an experimental authorization under part 5 of this chapter.

3.1.2

For EVMs annotated as FCC – FEDERAL COMMUNICATIONS COMMISSION Part 15 Compliant:

CAUTION

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not

cause harmful interference, and (2) this device must accept any interference received, including interference that may cause

undesired operation.

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to

operate the equipment.

FCC Interference Statement for Class A EVM devices

NOTE: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of

the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is

operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not

installed and used in accordance with the instruction manual, may cause harmful interference to radio communications.

Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to

correct the interference at his own expense.

SPACER

SPACER

SPACER

SPACER

SPACER

SPACER

SPACER

SPACER

�FCC Interference Statement for Class B EVM devices

NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of

the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential

installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance

with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference

will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which

can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more

of the following measures:

•

•

•

•

Reorient or relocate the receiving antenna.

Increase the separation between the equipment and receiver.

Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

Consult the dealer or an experienced radio/TV technician for help.

3.2 Canada

3.2.1

For EVMs issued with an Industry Canada Certificate of Conformance to RSS-210

Concerning EVMs Including Radio Transmitters:

This device complies with Industry Canada license-exempt RSS standard(s). Operation is subject to the following two conditions:

(1) this device may not cause interference, and (2) this device must accept any interference, including interference that may

cause undesired operation of the device.

Concernant les EVMs avec appareils radio:

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation

est autorisée aux deux conditions suivantes: (1) l'appareil ne doit pas produire de brouillage, et (2) l'utilisateur de l'appareil doit

accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

Concerning EVMs Including Detachable Antennas:

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser)

gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type

and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for

successful communication. This radio transmitter has been approved by Industry Canada to operate with the antenna types

listed in the user guide with the maximum permissible gain and required antenna impedance for each antenna type indicated.

Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited

for use with this device.

Concernant les EVMs avec antennes détachables

Conformément à la réglementation d'Industrie Canada, le présent émetteur radio peut fonctionner avec une antenne d'un type et

d'un gain maximal (ou inférieur) approuvé pour l'émetteur par Industrie Canada. Dans le but de réduire les risques de brouillage

radioélectrique à l'intention des autres utilisateurs, il faut choisir le type d'antenne et son gain de sorte que la puissance isotrope

rayonnée équivalente (p.i.r.e.) ne dépasse pas l'intensité nécessaire à l'établissement d'une communication satisfaisante. Le

présent émetteur radio a été approuvé par Industrie Canada pour fonctionner avec les types d'antenne énumérés dans le

manuel d’usage et ayant un gain admissible maximal et l'impédance requise pour chaque type d'antenne. Les types d'antenne

non inclus dans cette liste, ou dont le gain est supérieur au gain maximal indiqué, sont strictement interdits pour l'exploitation de

l'émetteur

3.3 Japan

3.3.1

Notice for EVMs delivered in Japan: Please see http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_01.page 日本国内に

輸入される評価用キット、ボードについては、次のところをご覧ください。

http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_01.page

3.3.2

Notice for Users of EVMs Considered “Radio Frequency Products” in Japan: EVMs entering Japan may not be certified

by TI as conforming to Technical Regulations of Radio Law of Japan.

If User uses EVMs in Japan, not certified to Technical Regulations of Radio Law of Japan, User is required by Radio Law of

Japan to follow the instructions below with respect to EVMs:

1.

2.

3.

Use EVMs in a shielded room or any other test facility as defined in the notification #173 issued by Ministry of Internal

Affairs and Communications on March 28, 2006, based on Sub-section 1.1 of Article 6 of the Ministry’s Rule for

Enforcement of Radio Law of Japan,

Use EVMs only after User obtains the license of Test Radio Station as provided in Radio Law of Japan with respect to

EVMs, or

Use of EVMs only after User obtains the Technical Regulations Conformity Certification as provided in Radio Law of Japan

with respect to EVMs. Also, do not transfer EVMs, unless User gives the same notice above to the transferee. Please note