Sample &

Buy

Product

Folder

Support &

Community

Tools &

Software

Technical

Documents

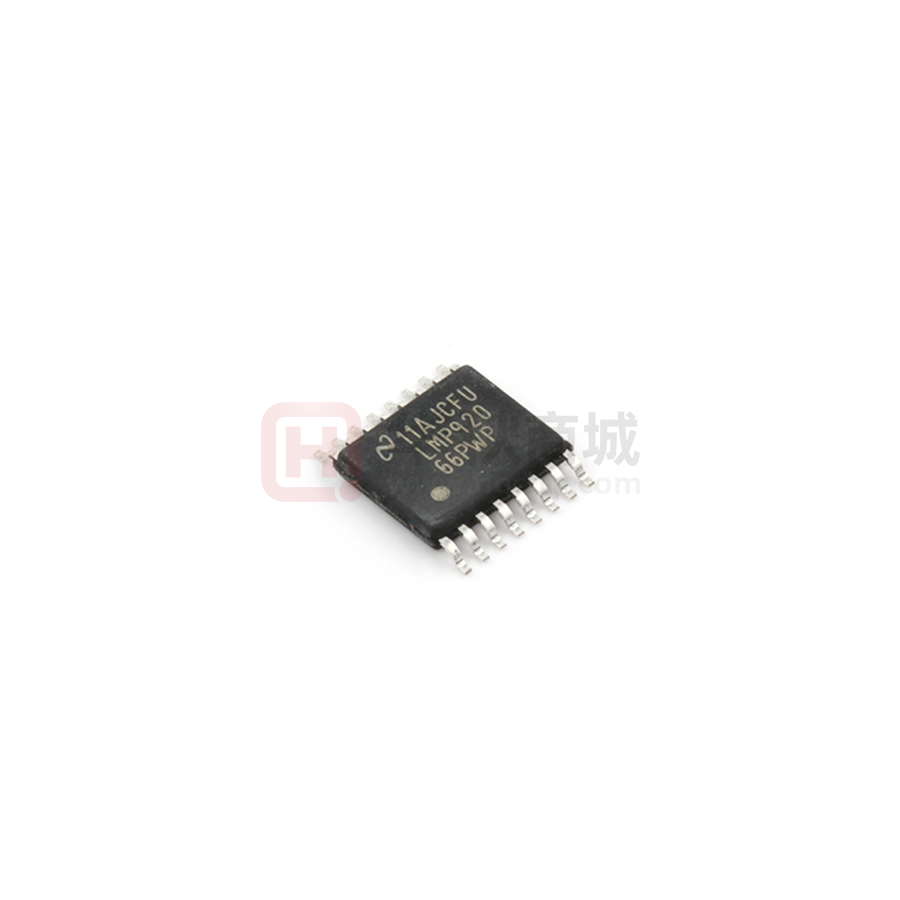

LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

LMP92066 Dual Temperature-Controlled DAC with Integrated EEPROM and Output

ON/OFF Control

1 Features

3 Description

•

The LMP92066 is a highly integrated temperaturecontrolled dual DAC. Both DACs can be programmed

by two independent, user-defined, temperature-tovoltage transfer functions stored in the internal

EEPROM, allowing any temperature effects to be

corrected without additional external circuitry. Once

powered up, the device operates autonomously,

without intervention from the system controller, to

provide a complete solution for setting and

compensating bias voltages and currents in control

applications.

1

•

•

•

•

•

•

•

•

Internal 12-Bit Temperature Sensor

– Accuracy (–40°C to 120°C), ±3.2°C

(maximum)

Two Independent Transfer Functions Stored in

EEPROM

Dual-Analog Output

– Two 12-Bit DACs

– Output Range 0 V to 5 V or 0 V to –5 V

– High-Capacitive Load Tolerant, up to 10 µF

– Post-Calibration Accuracy ±2.4 mV (typical)

Output On/Off Control Switching Time 50 ns

(typical)

– Switching Time 50 ns (typical)

– RDSON 5 Ω (maximum)

I2C Interface: Standard and Fast

– Nine Selectable Slave Addresses

– TIMEOUT Function

VDD Supply Range 4.75 V to 5.25 V

VIO Range 1.65 V to 3.6 V

Specified Temperature Range –25°C to 120°C

Operating Temperature Range –40°C to 125°C

2 Applications

•

•

•

GaN or LDMOS PA Bias Controller

Sensor Temperature Compensation

Timing Circuit Temperature Compensation

The LMP92066 has two analog outputs that support

two output ranges: zero to plus five volts and zero to

minus five volts. Each output can be switched to the

load individually through the use of the dedicated

control pin. The output switching is designed for rapid

response, making the device suitable for the RF

Power Amplifier biasing applications.

The EEPROM is verified for 100 write operations,

enabling repeated field updates. The EEPROM

programming is completed upon the user-issued I2C

command.

The LMP92066’s digital ports interface to a variety of

system controllers, as the dedicated VIO pin sets the

digital I/O levels. The device is available in the

thermally enhanced PowerPAD™ package, enabling

precise PCB temperature measurement.

Device Information

PART NUMBER

LMP92066

PACKAGE

BODY SIZE

HTSSOP (16)

5.00 mm x 4.40 mm

4 Simplified Schematic

3.3V

5V

Residual Error After One Point Calibration

VIO

35

VDD VDDB

FETDRV1

Gate Bias 1

MEAN = 0.72 mV

STDEV = 1.71 mV

PA: LDMOS

30

10µ

SCL

LMP92066

DRVEN1

DRVEN0

FETDRV0

PA: LDMOS

15

10

DAC0

10

8

6

4

2

0

0

5

±2

10µ

±4

GNDD GNDA VSSB

±6

A0

20

±8

A1

Gate Bias 0

25

±10

µC

Occurrences (%)

DAC1

SDA

REAOPC (mV)

C009

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

Table of Contents

1

2

3

4

5

6

7

Features ..................................................................

Applications ...........................................................

Description .............................................................

Simplified Schematic.............................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

7.1

7.2

7.3

7.4

7.5

7.6

7.7

7.8

8

1

1

1

1

2

3

5

Absolute Maximum Ratings ...................................... 5

ESD Ratings.............................................................. 5

Recommended Operating Conditions....................... 5

Thermal Information .................................................. 5

Electrical Characteristics........................................... 6

Timing Requirements ................................................ 8

Output Switching Characteristics .............................. 8

Typical Characteristics ............................................ 10

Detailed Description ............................................ 14

8.1

8.2

8.3

8.4

Overview .................................................................

Functional Block Diagram .......................................

Features Description ...............................................

Device Functional Modes........................................

14

14

15

28

8.5 Programming........................................................... 32

8.6 Register Map........................................................... 39

9

Application and Implementation ........................ 43

9.1

9.2

9.3

9.4

Application Information............................................

Typical Applications ................................................

Do's and Don'ts .......................................................

Initialization Setup ...................................................

43

43

51

52

10 Power Supply Recommendations ..................... 54

10.1 VDD Supply Sourcing ........................................... 54

10.2 IVDD During EEPROM BURN ................................ 54

10.3 IVDD During EEPROM TRANSFER....................... 54

11 Layout................................................................... 55

11.1 Layout Guidelines ................................................. 55

11.2 Layout Example .................................................... 56

12 Device and Documentation Support ................. 57

12.1

12.2

12.3

12.4

Device Support......................................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

57

57

57

57

13 Mechanical, Packaging, and Orderable

Information ........................................................... 57

5 Revision History

Changes from Revision A (April 2015) to Revision B

Page

•

Added new footnote. .............................................................................................................................................................. 7

•

Added VDD Supply Sourcing section. ................................................................................................................................. 54

Changes from Original (March 2014) to Revision A

Page

•

Changed header row of Device Information table; revised "terminal" to "pin" throughout document, changed

Handling Ratings to ESD Ratings table; took out "+" from positive values; italicize section cross references; add

titles for tables 3, 4, 5, and 6 .................................................................................................................................................. 1

•

Added "Ω" after "k" in EC table ............................................................................................................................................. 6

•

Added "Ω" after "k" in Output Switching table ....................................................................................................................... 8

•

Added "NOTE" to beginning of Applications and Implementations ...................................................................................... 43

•

Changed title from Application Performance Plots to Application Curves; deleted reference to Figure 43 in first

sentence of first Application Curves section......................................................................................................................... 47

•

Added change "5 mA" to "50 mA" ........................................................................................................................................ 54

2

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

6 Pin Configuration and Functions

PWP Package

16-Pin HTSSOP

Top View

GNDD

1

16

VDD

DRVEN1

2

15

VDDB

DRVEN0

3

14

DAC1

VIO

4

13

FETDRV1

DAP

SDA

5

12

GNDA

SCL

6

11

FETDRV0

A1

7

10

DAC0

A0

8

9

VSSB

Pin Functions

PIN

NUMBER

NAME

TYPE

(1)

DESCRIPTION

ESD STRUCTURES

VIO

1

GNDD

G

Lower power rail of the digital I/O

2:3

DRVEN[1:0]

I

Asynchronous control of the Changeover Switches

Digital I/O power supply rail

GNDA

4

VIO

I

5

SDA

I/O

6

SCL

I

I2C bi-directional data line

I2C clock input

GNDA

VIO

7:8

A[1:0]

I

I2C slave address selector

GNDA

GNDA

9

VSSB

P

Output drive lower supply rail

10, 14

DAC0

DAC1

O

DAC0 output

11, 13

FETDRV0

FETDRV1

O

Gate drive of the external FET device

VDDB

VSSB

(1)

G = Ground; I = Input; O = Output; P = Power

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

3

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

Pin Functions (continued)

PIN

NUMBER

NAME

TYPE

(1)

DESCRIPTION

ESD STRUCTURES

VDD

12

GNDA

G

Analog block lower rail

Merril

Clamp

GNDA

VDD

15

VDDB

P

Output drive upper supply rail

GNDA

VDD

16

VDD

P

Analog block upper rail

Merril

Clamp

GNDA

---

4

DAP

G

Die Attach Pad. For best thermal, and noise performance

it should be soldered to the local system ground pad.

Submit Documentation Feedback

GNDA

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)

MIN

MAX

–0.3

5.5

–0.3

5.5

–0.3

5.5

VSSB

–5.5

0.3

GNDD

–0.3

0.3

VDDB to VSSB

–0.3

5.5

Any other pins to GNDA

–0.3

5.5

VDD

VDDB

VIO

Supply voltage with respect to GNDA

DAC output current

10

Current at all other pins

5

Storage temperature, Tstg

(1)

–65

UNIT

V

V

mA

150

°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

7.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)

±2500

Charged-device model (CDM), per JEDEC specification JESD22-C101 (2)

±1000

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

MAX

Operational temperature

–40

125

Specification temperature

–25

120

8

12

DAC output load capacitance

VDD

Supply voltage range (VDD)

4.75

5.25

VIO

Digital I/O supply voltage

1.65

3.3

VDDB–VSSB

LDMOS mode VSSB = GNDA

5

GaN mode VSSB = –5 V

5

UNIT

°C

µF

V

7.4 Thermal Information

THERMAL METRIC (1)

PWP (HTSSOP)

16 PINS

RθJA

Junction-to-ambient thermal resistance

38.2

RθJC(top)

Junction-to-case (top) thermal resistance

21.3

RθJB

Junction-to-board thermal resistance

15.1

ψJT

Junction-to-top characterization parameter

0.5

ψJB

Junction-to-board characterization parameter

14.9

RθJC(bot)

Junction-to-case (bottom) thermal resistance

1.4

(1)

UNIT

°C/W

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

5

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

7.5 Electrical Characteristics

Unless otherwise noted: VDD = 5 V ±5%, VIO = 1.8 V to 3.3 V, TA = 25°C. VDDB = 5 V ±5%, VSSB = GNDA, VDACx output

range 0 V to 5 V; or VDDB = GNDA, VSSB = –5 V ±5%, VDACx output range 0 V to –5V. DAC input code range 48 to 4047.

VDACX load CL = 10 µF.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

ANALOG SIGNAL PATH CHARACTERISTICS (DAC, Buffer Amplifier, Internal Reference)

Resolution

12

–25°C < TA < 120°C

Monotonic

12

12

DNL

Differential non-linearity

RL = 100 kΩ, –25°C < TA < 120°C

–0.99

1

INL

Integral non-linearity

RL = 100 kΩ, –25°C < TA < 120°C

−1.93

2.78

–14

14

LDMOS mode, RL = 100 kΩ,

–25°C < TA < 120°C

OE

Offset error

(1)

LDMOS mode, RL = 100 kΩ

±1

GaN mode, RL = 100 kΩ, –25°C < TA <

120°C

OETC

Offset error temperature coefficient (1) (2)

RL = 100 kΩ, –25°C < TA < 120°C

GE

Gain error (1)

RL = 100 kΩ, –25°C < TA < 120°C

GETC

Gain error temperature coefficient

(1) (2)

Residual error after one point

calibration (1) (2) (3) (4)

Zero code output (VDACx – VSSB)

FSO

Full-scale output at code 4095 (VDDB –

VDACx)

IO

Continuous output current per channel

allowed (5)

CL

Load capacitance (5)

mV

16.5

43

μV/°C

–0.72

0.74

%FS

20 ppm/°C

–13.3

BASEx = 1638 (VDACX = 2 V at 24°C)

BASEx = 819 (VDACX = 1 V at 24°C)

–25°C < TA < 120°C

13.3

±2.4

–11.3

BASEx = 819 (VDACX = 1 V at 24°C)

ZCO

mV

11.3

±2.1

LDMOS mode, RL = 100 kΩ

0

LDMOS mode, IOUT = 10 mA

mV

200

LDMOS mode, RL = 100 kΩ

10

LDMOS mode, IOUT = –10 mA

mV

150

TA = 125°C

10

RL = 2 kΩ or ∞, –25°C < TA < 120°C

12

RL = 2 kΩ or ∞

DAC output resistance

DACCODEx = 2048

DAC settling time

CL = 10 µF

LSB

–16.5

RL = 100 kΩ, –25°C < TA < 120°C

BASEx = 1638 (VDACX = 2 V at 24°C)

–25°C < TA < 120°C

REAOPC

Bits

10

mA

µF

3

Ω

250

µs

OUTPUT SWITCH DC CHARACTERISTICS

RDRV

On Resistance of the switch between

DACx and FETDRVx

RG

On Resistance of the switch between

FETDRVx and VSSB

–25°C < TA < 120°C

6

Ω

11

TEMPERATURE SENSOR CHARACTERISTICS

Resolution

TE

Temperature sensor error (2)

0.0625

TA = –40°C to 120°C

Conversion time

(1)

(2)

(3)

(4)

(5)

6

–3.2

°C/lsb

3.2

25

°C

ms

The package mechanical stress-induced parameter shift may cause the parts to manifest behavior beyond the specified limits.

Mechanical stresses may also arise as a result of the PCB manufacturing process.

Device specification is verified by characterization and is not tested in production.

The specification is a calculated worst-case value based on the OE, OETC, GE, and GETC limits.

The outcome of the REAOPC characterization of the PCB mounted devices is shown in Figure 4, Figure 5, and Figure 6 of the Typical

Characteristics. The 97, randomly selected, devices from 3 diffusion lots were installed on the 4-layer RO4003 Laminate using

Convection Reflow. The Look-Up-Table was set for maximum gain; for example, all DELx = 0xFF. While powered up, the devices were

subjected to 3 thermal cycles, from –40°C to 125°C, during which their REAOPC was recorded.

Parameter based on the process data and circuit simulation.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

Electrical Characteristics (continued)

Unless otherwise noted: VDD = 5 V ±5%, VIO = 1.8 V to 3.3 V, TA = 25°C. VDDB = 5 V ±5%, VSSB = GNDA, VDACx output

range 0 V to 5 V; or VDDB = GNDA, VSSB = –5 V ±5%, VDACx output range 0 V to –5V. DAC input code range 48 to 4047.

VDACX load CL = 10 µF.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

EEPROM

Maximum EEPROM write cycles

100

DIGITAL INPUT CHARACTERISTICS (DRVEN0, DRVEN1, SDA, and SCL)

VIH

Input high voltage

–25°C < TA < 120°C

VIL

Input low voltage

–25°C < TA < 120°C

0.7 ×

VIO

0.3 ×

VIO

0.2 ×

VIO

Hysteresis

CiND

V

Input capacitance

5

pF

DIGITAL INPUT CHARACTERISTICS (A0, A1)

0.7 ×

VIO

VIH

Input high voltage

–25°C < TA < 120°C

VIL

Input low voltage

–25°C < TA < 120°C

RUP

Internal pullup resistance

17

RDN

Internal pulldown resistance

17

0.3 ×

VIO

Max external capacitance (5)

V

kΩ

30

pF

DIGITAL OUTPUT CHARACTERISTICS (SDA)

VOL

Output low voltage

ILEAK

Open-drain output leakage current with

output high (5)

COUT

Output capacitance

IOUT = 4 mA, –25°C < TA < 120°C

0.4

IOUT = 4 mA

0.16

Current from the supply rail through the

pullup resistor into the drain of the opendrain output device, –25°C < TA < 120°C

±1

4

V

μA

pF

SUPPLY CURRENT SPECIFICATIONS

Normal operation (6), (7) –25°C < TA < 120°C

IDD

2.6

While executing EEPROM BURN (8)

4

While transferring EEPROM content to

operating memory (9)

9

I2C inactive, –25°C < TA < 120°C

IVIO

mA

3

I2C in fast mode, –25°C < TA < 120°C

3.1

IVDDB

LDMOS mode, RL = ∞, –25°C < TA < 120°C

1.5

IVSSB

GaN mode, RL = ∞, –25°C < TA < 120°C

PWR

(Conv)

(6)

(7)

(8)

(9)

Power consumption, conversion mode

All output pins RL = ∞

–1.4

20

µA

mA

mW

The normal operation current through the VDD excludes the current supplied to the external load, and excludes the current required by

the EPPROM BURNS and TRANSFERS.

The power supply must be capable of sourcing a minimum of 50mA in order to avoid the continuous activation of the LMP92066’s

power-on-reset (POR) circuit.

During the EEPROM BURN command execution the device activates internal systems that are not active during the Normal operation.

This causes a momentary increase in supply current through the VDD pin. The duration of this temporary surge in supply current is

typically 125 ms.

During the data transfer from the EEPROM to the Operating memory there will be a momentary surge in supply current through the VDD

pin. The duration of this surge is typically 200 µs.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

7

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

7.6 Timing Requirements

Unless otherwise noted: VDD = 5 V ±5%, VIO = 1.8 V to 3.3 V. VDDB = 5 V ±5%, VSSB = GNDA; or VDDB = GNDA, VSSB

= –5V ±5%.

PARAMETER

TEST CONDITIONS

MIN

I2C clock frequency

10

tLOW

Clock low time

1.3

tHIGH

Clock high time

MAX

UNIT

400

kHz

0.6

After this period, the first clock pulse is

generated

tHD-STA

Hold time repeated START condition

tSU;STA

Setup time for a repeated START

condition

tHD;DAT

Data hold time (Note x and y)

tSU;DAT

Data setup time

tf

SDA fall time

tSU;STO

Setup time for STOP condition

0.6

tBUF

Bus free time between a STOP and

START condition

1.3

Cb

SDA capacitive load

tSP

Pulse width of spikes that must be

suppressed by the input filter

µs

0.6

0.6

0

900

100

ns

IL ≤ 3 mA and CL ≤ 400 pF

250

SCL and SDA timeout

µs

25

400

pF

50

ns

35

ms

7.7 Output Switching Characteristics

Unless otherwise noted: VDD = 5 V ±5%, VIO = 1.8 V to 3.3 V. VDDB = 5 V ±5%, VSSB = GNDA; or VDDB = GNDA, VSSB

= –5V ±5%.

PARAMETER

TEST CONDITIONS

MIN

TYP

tON

On time

tOFF

Off time

tBBM

Break-before-make time

15

CFETDRV

FETDRV output capacitance

10

MAX

UNIT

50

DACCODEx = 4095, RL = 100 kΩ

50

ns

pF

tVD;DAT, tVD;ACK

SDA

70%

tLOW

tf

tr

SCL

tBUF

tHD;STA

tf

30%

tSP

70%

30%

tSU;STA

tHD;STA

tHD;DAT

START

tHIGH

tSU;STO

tSU;DAT

REPEATED

START

STOP

START

Figure 1. I2C Timing

8

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

VIO

DRVENx

50%

50%

GNDD

VDACx

FETDRVx

90%

HiZ

90%

HiZ

VSSB

tBBM

tON

tBBM

tOFF

Figure 2. Switching

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

9

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

7.8 Typical Characteristics

Unless otherwise stated the plot data was collected under these conditions: VDD = 5 V, VDDB = 5 V, VSSB = GNDA, VIO =

3.3 V, Temperature = 24°C, RL = 100 kΩ.

2.1

35

MEAN = 0.76 mV

STDEV = 1.43 mV

1.8

30

1.5

Occurrences (%)

1.2

0.9

TE (ƒC)

0.6

0.3

0.0

±0.3

25

20

15

10

±0.6

±40

±20

0

20

40

60

80

100

120

Temperature (ƒC)

C008

PCB Mounted

3 Cycles: –40°C to 125°C

Figure 3. Temperature Sensor Error

Figure 4. REAOPC

35

REAOPC (mV)

REAOPC (mV)

C009

BASE = 1638

97 devices

C010

PCB Mounted

3 Cycles: –40°C to 125°C

BASE = 3277

97 devices

Figure 5. REAOPC

PCB Mounted

3 Cycles: –40°C to 125°C

Figure 6. REAOPC

0.5

1.0

0.4

0.8

0.3

0.6

0.2

0.4

0.1

0.2

INL (lsb)

DNL (lsb)

10

8

2

0

10

8

6

4

2

0

±2

0

±4

0

±6

5

±8

5

±2

10

±4

10

15

±6

15

20

±8

20

25

±10

Occurrences (%)

25

±10

MEAN = 0.66 mV

STDEV = 2.42 mV

30

6

MEAN = 0.72 mV

STDEV = 1.71 mV

30

4

35

0.0

±0.1

0.0

±0.2

±0.2

±0.4

±0.3

±0.6

±0.4

±0.8

±0.5

±1.0

0

512

1024

1536

2048

2560

Input Code (dec)

3072

3584

4096

0

C003

Figure 7. DAC DNL

10

10

8

6

4

2

0

REAOPC (mV)

C001

BASE = 819

97 devices

Occurrences (%)

±2

±4

0

±6

±1.5

±10

±1.2

±8

5

Mean Error

1

± 1

±0.9

512

1024

1536

2048

2560

Input Code (dec)

3072

3584

4096

C003

Figure 8. DAC INL

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

Typical Characteristics (continued)

1.0

1.0

0.8

0.8

0.6

0.6

0.4

0.4

0.2

0.2

INL (lsb)

0.0

±0.2

±0.4

0.0

±0.2

±0.4

±0.6

±0.6

MAX

MIN

100 120 140

±60

25

60

Occurrences (%)

70

20

15

10

10

8

6

4

2

0

80

100 120 140

C005

20

0

±2

60

30

0

±4

40

40

10

±6

20

50

5

±8

0

Figure 10. DAC MIN/MAX INL vs Temperature

30

±10

±20

Temperature (ƒC)

Figure 9. DAC MIN/MAX DNL vs Temperature

Occurrences (%)

±40

C004

OE (mV)

GE (%)

C006

C007

TEMP = –40°C to 120°C

TEMP = –40°C to 120°C

Figure 11. DAC Offset Error

Figure 12. DAC Gain Error

VDACx

VDACx

VSCL

VSCL

Time (100 µs/DIV)

Time (100 µs/DIV)

C012

C011

DAC OVERRIDE MODE

CL = 10 µF

1.0

80

0.8

60

0.6

40

0.4

20

Temperature (ƒC)

0.2

0

±0.4

±20

±0.6

±40

±1.0

±0.8

±60

MAX

MIN

±0.8

0.0

±1.0

±0.2

±0.8

±1.0

DNL (lsb)

Unless otherwise stated the plot data was collected under these conditions: VDD = 5 V, VDDB = 5 V, VSSB = GNDA, VIO =

3.3 V, Temperature = 24°C, RL = 100 kΩ.

I2C command triggers DAC step

Step size: 1/4 to 3/4 FS

DAC OVERRIDE MODE

CL = 10 pF

Figure 13. DAC Step Response

I2C command triggers DAC step

Step size: 1/4 to 3/4 FS

Figure 14. DAC Step Response

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

11

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

Typical Characteristics (continued)

Unless otherwise stated the plot data was collected under these conditions: VDD = 5 V, VDDB = 5 V, VSSB = GNDA, VIO =

3.3 V, Temperature = 24°C, RL = 100 kΩ.

VDACx

VDACx

VSCL

VSCL

Time (100 µs/DIV)

Time (100 µs/DIV)

C013

I2C command triggers DAC step

Step size: 3/4 to 1/4 FS

DAC OVERRIDE MODE

CL = 10 µF

C014

Figure 15. DAC Step Response

Figure 16. DAC Step Response

5

5

4

4

3

3

RDRV ( )

RDRV ( )

I2C command triggers DAC step

Step size: 3/4 to 1/4 FS

DAC OVERRIDE MODE

CL = 10 pF

2

2

1

1

Vdacx=

VDACx 1.38 V

VDACx 3.23 V

Vdacx=

VDACx 4.46 V

Vdacx=

0

0

0

1

2

3

4

5

VDACx (V)

±40

±20

0

20

40

60

80

100

120

Temperature (ƒC)

C015

Figure 17. RDRV Resistance vs DAC Output Level

C016

Figure 18. RDRV vs Temperature

90

60

80

50

Occurrences (%)

70

tON (ns)

40

30

20

60

50

40

30

20

10

Temperature (ƒC)

C017

45

0

44

120

43

100

42

80

41

60

40

40

39

20

38

0

37

±20

36

±40

35

10

0

tON (ns)

C018

Figure 19. Output Switch ON Time vs Temperature

12

Submit Documentation Feedback

Figure 20. Output Switch ON Time

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

Typical Characteristics (continued)

Unless otherwise stated the plot data was collected under these conditions: VDD = 5 V, VDDB = 5 V, VSSB = GNDA, VIO =

3.3 V, Temperature = 24°C, RL = 100 kΩ.

70

Occurrences (%)

60

50

40

30

20

13.0

12.5

12.0

11.5

11.0

10.5

10.0

9.5

0

9.0

10

RG ( )

C019

Figure 21. Ground Switch Resistance When Closed

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

13

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

8 Detailed Description

8.1 Overview

The LMP92066 is a dual temperature-dependent bias generator whose temperature-to-voltage transfer functions

are user defined. The device contains a digital temperature sensor that addresses two independently

programmable Look-Up-Tables (LUTs). The outputs of LUTs are sent on to their respective 12-bit DACs to

produce two independent output voltages. For added flexibility the device can be configured to provide bias

potential above or below GNDA.

In applications requiring rapid ON/OFF switching of the bias voltage, the LMP92066 provides asynchronous

control over its outputs. Dedicated digital input pins control analog output switching.

All aspects of the device functionality are controlled through internal registers. These registers, and the LUTs, are

accessible through the I2C-compatible interface.

The LMP92066 can operate autonomously of the system controller, once LUT coefficients have been committed

to its non-volatile memory, EEPROM. Upon power up the EEPROM content is automatically transferred to the

operating memory, and the device begins to produce required bias voltage.

8.2 Functional Block Diagram

VIO

A[1:0]

SCL

SDA

VDD

VDDB

I2C

Interface

&

Controller

DAC1

LUT1

Temp.

Sensor

FETDRV1

DAC1

DRVEN1

EPROM

VSSB

DAC0

LUT0

FETDRV0

DAC0

DRVEN[1:0]

DRVEN0

VSSB

GNDD

14

GNDA

VSSB

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

8.3 Features Description

8.3.1 Temperature Sensor

The onboard digital temperature sensor produces 12-bit, twos complement output, where the LSB represents

+0.0625°C, and MSB represents –128°C. The output of the temperature sensor is stored in the TEMPM and

TEMPL registers. These registers are updated automatically once the temperature sensor completes a new

conversion, approximately every 25 ms. The temperature sensor begins operation immediately after the supply

voltage at VDD has reached its minimum operating level. Initially, right after power up, TEMPM and TEMPL

registers contain 0s. The first measurement result is loaded into TEMPM and TEMPL registers 25 ms after power

up.

Table 1. Temperature Sensor Output

TEMPERATURE SENSOR

OUTPUT

{TEMPM[3:0], TEMPL[7:0]}

TEMPERATURE (°C)

100000000000

–128.0000

111001000000

–28.0000

111111111111

–0.0625

000000000001

0.0625

000110000000

24.0000

011111111111

127.9375

NOTE

The maximum output of the temperature sensor stored in the TEMPM and TEMPL

registers is 127.9375°C.

8.3.2 Look-Up-Table (LUT) and Arithmetic-Logic Unit (ALU)

The LUT is used to create an arbitrary transfer function which maps the temperature to the analog output of the

device. In concept, the temperature readout is used as a pointer to a table of discrete values that are

representative of the samples of the desired temperature-dependent function.

In order to minimize the storage requirements, the LMP92066 LUTs are indexed in 4°C increments. Also, the

stored values are only the increments, or first derivatives (Δs) of the modeled transfer function. The internal ALU

reconstructs the original transfer function by integrating the coefficients stored in the LUTs. The errors due to the

coarseness of the temperature quantization are significantly reduced through the use of linear interpolation,

which is also implemented in the ALU.

Consider the example shown in Figure 22. The target output vs temperature is shown in the top graph. VDACx is a

smooth, monotonic function with, ideally, infinite precision. The LUT stores only the increments, or the rise, within

each 4°C interval.

In order to recreate the original transfer function, the series of increments must be summed together and added

to the constant BASE value. BASE represents the constant offset which is lost due to the differentiation - storage

of the increments only. This process must also be referenced to the common temperature point. This reference

temperature is called BASELINE in this document, and is fixed at 24°C.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

15

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

VDACx

û4

BASE

24°C

Temperature

4°C

4°C

û VDACx

û4

1

2

3

4

LUT Index

BASELINE

Figure 22. Original Transfer Function

The LUT and ALU Organization, LUT Coefficient to Register Mapping, and The LUT Input and Output Ranges

sections below detail the operation of the LUTs and the ALUs.

8.3.2.1 LUT and ALU Organization

In Figure 23 TEMP represents the 12-bit input value to the LUT. This value is produced by the local temperature

sensor, or it can be provided by the user through the use of the OVERRIDE registers. The OVERRIDE modes

are described in the later sections.

TEMP is truncated, and TEMP[11:6] is used to index the LUT. The truncation is equivalent to reducing the TEMP

resolution from 0.0625°C/LSB to 4°C/LSB.

The overall transfer function is stored in the LUT as a set of unsigned 4-bit increments from the BASE value, that

is, LUT location (+1) stores the value of the increment Δ1. This is shown in Figure 23. The BASELINE is 24°C

temperature reference point, and BASE is the numeric representation of the required output at 24°C

TEMP

INDEX

VALUE

K+1

û(K+1)

K

ûK

36°C

+3

û3

32°C

+2

û2

28°C

+1

û1

24°C

BASELINE

BASE

20°C

-1

û-1

-(M-1)

û-(M-1)

-M

û-M

128°C

Temp.

Sensor

-28°C

Figure 23. LUT Organization

When TEMP is above 24°C, the LUT is addressed above the BASELINE address, all increments are added to

the BASE value to produce numeric equivalent of the analog output. When TEMP is below 24°C, LUT is

addressed below the BASELINE, all increments are subtracted from the BASE value to produce DACIN.

16

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

Interpolation function is implemented in the ALU that follows the LUT. The truncated lower bits of the TEMP

value, REM = TEMP[5:0], are used to interpolate between data points stored in the LUT. A portion of increment,

αΔi, is added to form the final numeric output - the input data to the DAC. The factor α is a fraction of 4°C

temperature span, or equivalently it is a fraction of the 64-code temperature span.

D

REM

64

(1)

The process of calculating the DACIN, including the interpolation, is depicted in Figure 24. The DACIN is the final

12-bit value produced by the ALU and the LUT, and forwarded to the DAC for conversion to analog domain.

K

DACIN = BASE + ™ ûi + . û(K+1)

i=1

DACIN

.û(K+1)

ûK+1

ûK

REM

û3

û2

û1

M

™û-i + . û-M

i=1

DACIN = BASE ±

BASE

û-1

REM

û-(M-1)

û-M

)

+K

+(K

+1

+3

+2

+1

-1

SE

(24 o LIN

C) E

LUT INDEX

(TEMP)

Truncated

Full Accuracy

Truncated

Full Accuracy

BA

-(M

-1)

-M

.û-M

Figure 24. DACIN Calculation

Up to this point the algorithm description concerned only the generation of the monotonically increasing transfer

function. The device can also produce monotonically decreasing transfer function by setting the

DACx_BASEM.POL bit.

The effect of polarity reversal (POL = 1) on the overall transfer function is shown in Figure 25. The LUT content

is unchanged from the original example above. Note that now the LUT values stored at locations above

BASELINE address are subtracted from BASE value, and the LUT values stored at locations below BASELINE

address are added to the BASE value.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

17

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

DACIN

û-M

û-(M-1)

û-1

BASE

û1

û2

û3

ûK

+(K

+1

)

+K

+3

+2

SE

(24 o LIN

C) E

LUT INDEX

(TEMP)

BA

+1

-1

-1)

-(M

-M

ûK+1

Figure 25. Monotonically Decreasing Transfer Function

The expressions used in the calculation of the transfer function are summarized below:

LUT index > BASELINE:

DACIN

POL

BASE ( 1)

§

¨

¨

¨

©

¦

§

¨

¨

¨

©

M

K

'i

D'(K

·

¸

1) ¸

i 1

¸

¹

(2)

LUT index < BASELINE:

DACIN

18

POL

BASE ( 1)

¦

'

i

i 1

·

¸

D' M ¸

¸

¹

(3)

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

8.3.2.2 LUT Coefficient to Register Mapping

For the sake of convenience the preceding sections referred to LUT coefficients as ΔK. These are stored in the

operating memory in the registers DELx. This is reflected in the Register Map section of this document. The

example of the ΔK to DELx register mapping is shown in Table 2 section below.

Table 2. ΔK to DELx Register Mapping

TEMPERATURE

FUNCTION INCREMENT

REGISTER ASSIGNMENT

–28°C

Δ–13

DEL0

↓

↓

↓

20°C

Δ–1

DEL12

28°C

Δ+1

DEL13

↓

↓

↓

Δ+26

DEL38

124°C

128°C

8.3.2.3 The LUT Input and Output Ranges

The programmable LUT input range spans temperatures –28°C to 128°C. For the temperatures below –28°C the

LUT output is linearly extrapolated; that is, the increment Δ–13 (register DEL0) stored at the location

corresponding to –28°C is used as the slope down to –40°C.

Computed DAC input data

Extrapolated

LUT output

LUT Range

DEL0

-40° C

-28°C

-24°C

+124°C +128°C

Temperature Sensor Output

Figure 26. Temperature Sensor Output

Although the maximum output of the temperature sensor is 127.9375°C, the LUT index corresponding to 128°C

(DEL38) is required for proper interpolation when the temperature is above 124°C.

The increments stored in the LUT are 4-bit unsigned values. This limits the maximum slope of the transfer

function stored in the LUT to:

=

SLOPEMAX = 16LSB

4 qC

4LSB

qC

(4)

Given this slope limit imposed by the LUT structure, and the fact that the LUT input range is 156°C (from –28°C

to 128°C ), the maximum output range of the LUT due to the temperature sensor input is 624 LSBs, for the given

BASE value.

NOTE

The maximum span of 624 codes can reside anywhere within the 0 to 4095 code space of

the 12-bit DAC input. The total input code to the DAC is the sum of the increments (Δs)

and the 12-bit BASE value.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

19

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

8.3.3 Analog Signal Path

The simplified schematic of one analog channel of the device is shown in Figure 27. The LMP92066 contains 2

such channels. The following sub-sections describe each of the individual blocks within a channel.

DACxM.DAC

DACxL.DAC

DACxM_OVRD.DAC

DACxL_OVRD.DAC

VDD

VDDB

DAC

BUFFER

0

1 S

1

2

DACx

OVRD_CTL.DAC

GNDA

VSSB

FETDRVx

DRVENx

VSSB

Figure 27. One Analog Channel Simplified Schematic

8.3.3.1 DAC

The DAC produces unipolar output voltage proportional to the 12-bit input code. The input code format is offset

binary, where 0x000 represents minimum and the 0xFFF full-scale input. The input code is produced by the

LUT/ALU and stored in the DACxM and DACxL read-only registers. The user can also insert the DAC input code

via the DACxM_OVRD and DACxL_OVRD registers, and by setting the OVRD_CTL.DAC bit. The DAC is

referenced to the internally generated 5 V.

The DAC transfer functions:

DACIN

VDACx 5A

(V)

4096

(5)

Where A is the Buffer Amplifier gain (see Buffer Amplifier) and DACIN is the 12-bit input code stored in either:

{ DACxM[3:0], DACxL[7:0] }

or

{ DACxM_OVRD[3:0], DACxL_OVRD[7:0] }

The LUT Input and Output Ranges describes the maximum output code span of the LUT, for the given base

value. This also implies that when DACxM and DACxL registers are selected as the DAC inputs, the maximum

VDACx output excursion over temperature is:

4LSB

5V

dVDACx SLOPEMAX x TRANGE x VLSB

x156qC x

762mV

qC

4096

(6)

However, this limitation is lifted when using DACxM_OVRD and DACxL_OVRD registers as the DAC inputs. In

this case the DAC input range is full 4096 codes, and the output spans 0 V to 5 V.

8.3.3.2 Buffer Amplifier

The buffer amplifier provides the low impedance drive for the potential generated by the DAC. The output of the

amplifier is always available at the DACx output pin of the device. The buffer is designed to drive large capacitive

loads, as high as 10 µF.

The structure of the Buffer is such that it can produce output voltages above or below GNDA potential. Both

Buffer Amplifiers are biased from dedicated supply rails: VDDB and VSSB. The difference between the VDDB

and VSSB is nominally 5 V, but the span can be above or below GNDA. The gain A of the Buffer Amplifier

depends on the state of supply rails VDDB and VSSB.

20

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

When the span is above GNDA, or VDDB = 5 V and VSSB = 0 V, then the output buffer gain is A = 1. The net

effect on the output of the analog processing chain is shown in Figure 28. The DAC input codes in the range of

0x000 to 0xFFF are mapped to the output voltage in the range of 0 V to 5 V.

VDDB

VDACx

5V

A=1

0V

VSSB

DACx Input Code

0x000

0xFFF

Figure 28. Output of Analog Processing Chain: Net Effect

If the span is below GNDA, or VDDB = 0 V and VSSB = –5 V, then the output buffer gain is A = –1. This

configuration is depicted Figure 29. This results in effective mapping of the DAC input codes in the range of

0x000 to 0xFFF, to the output voltage range of 0 V to –5 V.

0x000

0xFFF

DACx Input Code

VDDB

VDACx

0V

A=-1

-5V

VSSB

Figure 29. Common Mode Voltage Below GNDA,

or VDDB = 0 V and VSSB = –5 V

NOTE

Both Buffer Amplifiers share the VDDB and VSSB rails. Therefore, both Buffers produce

gain of A = 1, or both produce gain of A = –1.

The state of the VDDB and VSSB supplies, whether their span is above or below GNDA is indicated by the state

of the DRV_STATUS.GAN bit, and can be read by the controller via the I2C interface.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

21

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

8.3.3.3 Output On and Off Control

The LMP92066 facilitates rapid turnon and shutdown of the downstream devices. The FETDRVx outputs can be

switched ON or OFF by the DRVENx input, independently of the I2C bus transactions. The FETDRVx pin is

driven by the Buffer amplifier when the corresponding DRVENx input pin is asserted HIGH. Otherwise, the

FETDRVx pin is connected to VSSB.

The control and switch design was optimized for minimum delay between the DRVENx input and the FETDRVx

switching. The design also ensures that during the state transition there exists an instance when both switches at

FETDRVx are open; that is, no possibility for the crow-bar current to flow from the Buffer output to VSSB.

The switches are assured to default to the state where FETDRVx output is connected to VSSB at power up, as

long as logic 0 is present at the DRVENx input.

8.3.4 Memory

The internal memory of the device consists of 2 distinct areas: the user register set or operating memory and the

EEPROM (non-volatile storage).

The operating memory registers provide the control over device functionality, report internal status of the device,

and store the signal path data (LUT, temperature sensor output, etc). A section of operating memory, designated

as a SCRATCH PAD, is available for arbitrary data storage. All operating memory locations are directly

accessible to the user via the I2C bus.

The EEPROM is not directly accessible via the I2C bus. The EEPROM acquires its data via the transfer from the

operating memory, upon user issued command.

Sections READ and WRITE Access, Access Control, LUT, NOTEPAD Storage, and EEPROM, and Figure 30

detail the internal memory functionality.

8.3.4.1 READ and WRITE Access

The operating memory consists of individually addressable bytes whose content can be accessed via a single

I2C transaction. For 8-bit data, as soon as the I2C transfer is complete the transferred value takes effect.

The device also uses values longer that 8 bits — for example, with Temperature Sensor output, Temperature

Sensor Override input, and the DAC input and Override registers are 12-bit values which require storage in 2

adjacent registers. For these values any access should start with the register containing the upper 4 bits,

immediately followed by the access to the lower byte.

NOTE

It is the WRITE of the lower byte that results in the update of the 12-bit value. See

Table 3.

Table 3. Block Writing

2

I C OPERATION

WRITE

22

REGISTER

BLK_CNTL

DATA

DESCRIPTION

0x8F

Enable the BLOCK access and set the block length to 15. This

transfer results in the immediate update of the BLK_CNTL register

and immediate change of behavior of the I2C interface.

WRITE

TEMPM_OVRD

0x08

Write the upper nibble of the Temperature Sensor override value.

This transaction does not result in the update of the

TEMPM_OVRD register. The transferred value is placed on a queue

awaiting the transfer of the lower byte. The output of the device is

not affected.

WRITE

TEMPL_OVRD

0x00

Write the lower byte of the Temperature Sensor override value. This

transaction results in the update of both the TEMPM_OVRD and

TEMPL_OVRD registers. The output of the device changes

accordingly with the new setting.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

8.3.4.2 Access Control

By default, all operating memory locations are open to READ access. The WRITE access is controlled by the

Access Level setting. Increasing the Access Level, broadens the scope of the WRITE access. There are 3

access levels available to the user; see Access Control.

User can change the current Access Level by writing a “password” sequence to the ACC_CNTL register. The

“password” sequences are 2 consecutive I2C byte transfers to the ACC_CNTL register. The data content of each

2 byte transfer is unique for each access level.

For example, to enter access level L2 perform the following 2 transfers:

Table 4. Memory Access Control

2

I C OPERATION

REGISTER

DATA

WRITE

ACC_CNTL

0xCD

First byte of the “password”.

WRITE

ACC_CNTL

0xF0

Second byte of the “password”. After this transfer is

completed the access level is changed to L2.

0x03

Optional:

Reading the ACC_CNTL serves as status report.

The possible returned values are:

0x00 – access level L0

0x01 – access level L1 is activated

0x03 – access level L2 is activated (and due to

nesting, L1 is also indicated)

READ

ACC_CNTL

DESCRIPTION

Table 5. EEPROM Access Levels

ACCESS LEVEL

SCOPE

L0

Default. User has READ access only to all locations in the operating

memory.

L1

User has READ access to all locations, and WRITE access to ADR_LK

and BLK_CNTL registers.

L2

User has READ and WRITE access to all operating memory locations.

NOTE

The access levels are nested. This means that L1 access level also gives all L0 level

functionality. L2 access level provides L1 and L0 functionality.

8.3.4.3 LUT, NOTEPAD Storage, and EEPROM

The LUT (its coefficients, BASE value, ALU control bits) and the NOTEPAD are stored in the operating memory

block spanning addresses 0x40 through 0x7F. This space is directly accessible (READ and WIRITE) via the I2C

bus.

There is an option to store the LUT and the NOTEPAD in the non-volatile memory, EEPROM. The move of data

from the operating memory to the EEPROM (BURN) is initiated by WRITING a command byte to the

EEPROM_CNTL register.

Upon power up the device automatically executes the TRANSFER of the EEPROM data to the operating

memory. The user can also issue a command via the I2C bus to force the TRANSFER of data from the EEPROM

to the operating memory.

Table 6. EEPROM Control

TRANSFER/BURN

2

I C OPERATION

REGISTER

DATA

COMMENT

TRANSFER

WRITE

EEPROM_CNTL

0x4E

Transfer of data from the EEPROM to the

operating memory.

BURN

WRITE

EEPROM_CNTL

0xE4

Transfer of data from the operating memory

to the EEPROM.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

23

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

The READ of the EEPROM_CNTL register returns the status of the BURN or TRANSFER.

Table 7. Status of BURN or TRANSFER

EEPROM_CNTL BIT FIELD

DESCRIPTION

RDYB

0 - The TRANSFER or BURN has completed

1 – The TRANSFER or BURN is in progress

COR

1 – A bit error was detected during the transfer from EEPROM to

the operating memory. The error has been corrected and the data

is valid.

UCOR

1 – A bit error was detected during the transfer from EEPROM to

operating memory. The error was not corrected. LUT data is

compromised.

0x00

0x05

Temp Sensor

and

DAC Data

RESERVED

0x07 Temp Sensor Status,

Override Control,

EEPROM Control

RESET,

Access Level Control

0x11

RESERVED

0x16 Block Access Control

RESERVED

0x18

Address Lock

I 2C

OPERATING MEMORY

RESERVED

0x1E Output Drive Status,

Device Version

0x1F

RESERVED

0x40

Burn Counter,

LUT Coefficients,

LUT Control

BURN

COMMAND

EEPROM

TRANSFER

COMMAND

0x6B

0x6C

Note Pad

0x7F

Figure 30. Memory-to-EEPROM Mapping

24

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

8.3.5 I2C Interface

I2C bus is used for communication between the Master (the digital supervisor; for example, the microcontroller)

and the Slave (LMP92066). This interface provides the user full access to all Data, Status, and Control registers

of the device.

LMP92066 supports Standard-mode and Fast-mode, 100 kbit/s and 400 kbit/s, respectively.

All

•

•

•

•

•

•

•

•

•

transactions follow the format:

Master begins all transactions by generating START condition.

All transfers comprise 8-bit bytes.

First byte following START must contain 7-bit Slave address.

First byte is followed by a READ/WRITE bit.

All subsequent bytes contain 8-bit data.

By default, the device assumes 1-byte data transfers. Block access can be enabled via BLK_CNTL register,

resulting in multi-byte transfers.

Bit order within a byte is always MSB first

ACK/NAK condition follows every byte transfer – this can be generated by either Master or the Slave

depending on direction of data transfer.

STOP condition generated by the MASTER terminates all transactions, and resets the I2C bus. LMP92066

resets its internal address pointer to 0x00.

8.3.5.1 Supported Data Transfer Formats

Table 8 lists all conditions defined by the I2C specification and supported by this device. All following bus

descriptions refer to the symbols listed in Table 8.

Table 8. I2C Symbol Set

CONDITION

SYMBOL

SOURCE

DESCRIPTION

START

S

Master

Begins all bus transactions

STOP

P

Master

Terminates all transations and resets

bus

ACK (Acknowledge)

A

Master/Slave

Handshaking bit (LOW)

NAK (Not

Acknowledge)

A

Master/Slave

Handshaking bit (HIGH)

Master

Active HIGH bit that follows

immediately after the slave address

sequence. Indicates that the master

is initiating the slave-to-master data

transfer.

READ

R

WRITE

W

Master

Active LOW bit that follows

immediately after the slave address

sequence. Indicates that the master

is initiating the master-to-slave data

transfer.

REPEATED START

Sr

Master

Generated by master, same function

as the START condition (highlights

the fact that STOP condition is not

strictly necessary.)

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

25

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

The single data byte transfers are shown in Figure 31 and Figure 32:

S

Slave Address

W

A

RegAddr[7:0]

A

Data[7:0]

A

P

From MASTER to SLAVE

From SLAVE to MASTER

Figure 31. Single-Byte WRITE Access Protocol

S

Slave Address

W

A

RegAddr[7:0]

A

Sr

Slave Address

R

A

Data[7:0]

A

P

From MASTER to SLAVE

From SLAVE to MASTER

Figure 32. Single-Byte READ Access Protocol

Block Access functionality is provided to minimize the transfer overhead of large data sets. By default the

LMP92066 is ready to accept multi-byte transfers. Until the transaction is terminated by the STOP condition, the

device will READ (WRITE) the subsequent memory locations.

The size of the contiguous block can be limited by the user. This functionality can be enabled by setting

BLK_CNTL.EN bit. The 7-bit value of BLK_CNTL.SIZE=N sets the size of the contiguous memory block that can

be accessed via the block transfer.

If the Master generates a block transfer that is larger than (BLK_CNTL.SIZE + 1), the internal register pointer

wraps around to the First Register address and the access continue to subsequent memory locations. The

examples of the block WRITE and READ transactions are shown below in Figure 33 and Figure 34:

Address of the First Register of

the contiguous memory block

S

Slave Address

W

A

RegAddr[7:0]

A

From MASTER to SLAVE

Data[7:0]

A

Data[7:0]

A

Data[7:0]

A

P

Data to First Register

N bytes of data to

contiguous memory

locations following First

Register

From SLAVE to MASTER

Figure 33. Block WRITE Access —

BLK_CNTL.EN = 1, BLK_CNTL.SIZE = N

Address of the First Register of

the contiguous memory block

S

Slave Address

W

A

RegAddr[7:0]

A

Sr

Data[7:0]

Slave Address

A

R

A

Data[7:0]

A

Data[7:0]

A

P

Data to First Register

From MASTER to SLAVE

From SLAVE to MASTER

N bytes of data to

contiguous memory

locations following First

Register

Figure 34. Block READ Access —

BLK_CNTL.EN = 1, BLK_CNTL.SIZE = N

26

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

8.3.5.2 Slave Address Selection

The I2C bus slave address is selected by installing shunts from A0 and A1 pins of the device to the VIO or GNDD

rails. The device discerns between 3 possible options for each pin: shunt to VIO, shunt to GNDD, or left not

connected (floating), for the total of 9 possible slave addresses.

The state of the A0 and A1 pins is tested after every occurrence of START condition on the I2C bus. However,

the user has an option to LOCK the acquired address by setting the ADR_LK.EN bit. Once the address is locked,

the device stores its Slave address internally and does not attempt to decode the address during subsequent I2C

transactions. The address lock can be disabled by resetting ADR_LK.EN bit. The device resets the ADR_LK.EN

upon power up.

Figure 35 and Figure 36 illustrate the operation of the address decoder circuit. The device internally attempts to

pull up, and then pull down, the Ax pin while monitoring the voltage at that pin. If the shunts are installed, the

weak pull-ups or pull-downs does not affect the voltage at the Ax pin; that is. the state is fixed by the shunt. If the

Ax pin floats, then pull-up and pull-down change the voltage at that pin.

VIO

VIO

Device

Terminal

LMP92066

UPx

SHUNT

RUP

Ax

OUTx

RDN

ENx

SHUNT

GNDD

DNx

GNDD

2

Figure 35. I C Address Decoder - Simplified Diagram

The address decoder operates during 2nd through 4th cycles of the SCL. The decoding of the state of Ax pins is

performed serially; that is, A0 is decoded first then A1. The functional diagram of the address decoder is shown

in Figure 36.

SCL

EN0

UP0

DN0

EN1

UP1

DN1

Figure 36. I2C Address Decoder - Functional Diagram

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

27

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

The interpretation of the OUTx values produced from the test phases is summarized in the following table. For

example: if a shunt is present between Ax and VIO (first case in the table), both UPx phase and DNx phase

result in OUTx being decoded as logical 1, unambiguously indicating the presence of the shunt to VIO, or HI

state of Ax.

Table 9. Address Decoder Output

TEST PHASE

DECODED Ax ↓

UPx

DNx

SHUNT to VIO: OUTx →

1

1

SHUNT to GNDD: OUTx →

0

0

LO

NO SHUNT: OUTx →

1

0

N.C.

HI

The mapping from the decoded Ax states to the I2C Slave address is shown in Table 10.

Table 10. Slave Address Space

I2C SLAVE ADDRESS

DEVICE PINS

A1

A0

[A6:A0]

LO

LO

0111111

LO

N.C.

1000000

LO

HI

1000001

N.C.

LO

1000010

N.C.

N.C.

1000011

N.C.

HI

1000100

HI

LO

1000101

HI

N.C.

1000110

HI

HI

1000111

The Slave Address alignment within the first byte following the START condition is shown in Figure 37:

S

A6

A5

A4

A3

A2

A1

A0 R/W

W

A

From MASTER to SLAVE

From SLAVE to MASTER

Figure 37. Slave Address Alignment

8.4 Device Functional Modes

The numeric signal path is shown in Figure 38. The signal flow is generally from left to right: the system input is

the temperature sensor, signal processing is done by the LUT/ALU, and the output is driven by the DACs - DAC

detail is omitted as DACs provide a conversion from numeric domain to voltage domain only, and they do not

affect the signal flow.

There are a number of multiplexers in the signal path which alter the data flow when their respective control bits

are set. The multiplexer states, and thus modes of device operation, are described in further detail below.

28

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

Device Functional Modes (continued)

DAC1_BASEM.POL

DAC1_BASEM.BYP

LUT1

0

ALU

[11:6]

S

DAC1M.DAC

12

DAC1L.DAC

1

0

DAC1

DAC1M_OVRD.DAC

DAC1L_OVRD.DAC

12

1 S

[5:0]

DAC1_BASEM

DAC1_BASEL

12

OVRD_CTL.TEMP

TEMPM.TEMP

Temp.

Sensor

TEMPL.TEMP

12

0 S

12

TEMPM_OVRD.TEMP

OVRD_CTL.DAC

1

TEMPL_OVRD.TEMP

12

DAC0_BASEM.POL

LUT0

DAC0_BASM.BYP

0

ALU

[11:6]

12

S

DAC0M.DAC

DAC0L.DAC

0 S

1

DAC0

DAC0M_OVRD.DAC

DAC0L_OVRD.DAC

12

1

[5:0]

DAC0_BASEM.BASE

DAC0_BASEL.BASE

12

Figure 38. Modes of Operation

8.4.1 Default Operating Mode

This mode of operation is active upon power up. By default the OVRD_CTL.TEMP and OVRD_CTL.DAC are

cleared. The temperature sensor continuously updates readings every 25 ms (registers: TEMPM, TEMPL). Each

temperature sensor update triggers the ALU to re-calculate its output using the user defined coefficients stored in

the LUT. The ALU output is passed on to the DACs (registers: DACxM, DACxL) which ultimately drive the VDACx

outputs. All of the functionality described here occurs automatically, without intervention from the system

controller, as long as the power is applied to the device supply pins: VDD, VIO, and VDDB.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

29

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

Device Functional Modes (continued)

8.4.2 Temperature Sensor Override

The temperature sensor output can be overridden by the externally supplied data. This capability may be used to

verify the validity of the function stored in the LUT. The externally supplied data can act as the temperature

sweep input and the output response due to temperature may be readily observed, without actually altering the

temperature of the test setup.

This functionality is facilitated by the multiplexer that follows the temperature sensor, and user writable data

registers TEMPM_OVRD and TEMPL_OVRD. TEMPM_OVRD[3:0] is the upper nibble of the temperature data.

TEMPL_OVRD[7:0] is the lower byte of the temperature data. The multiplexer control signal is the

OVRD_CTL.TEMP bit.

Table 11 shows an example of the I2C bus transfer sequence which results in externally supplied data indexing

the LUT.

Table 11. I2C Bus Transfer Sequence:

Externally Supplied Data Indexing LUT

I2C OPERATION

REGISTER

DATA

DESCRIPTION

WRITE

ACC_CNTL

0xCD

First byte of the “password”

WRITE

ACC_CNTL

0xF0

Second byte of the “password”. After this transfer is completed

the access level is changed to L2

READ

ACC_CNTL

0x03

Optional:

Reading the ACC_CNTL serves as status report.

0x03 – access level L2 is activated (and due to nesting, L1 is

also indicated)

WRITE

TEMPM_OVRD

0x01

Writes 0x1 as the value of the top nibble of the 12-bit, twos

complement, temperature value. After this transaction the

TEMPM_OVRD register is not updated, yet. The update takes

place only after the TEMPL_OVRD register is written.

WRITE

TEMPL_OVRD

0x01

Writes 0x01 into the lower byte of temperature value. After this

transaction completes both TEMPM_OVRD and

TEMPL_OVRD registers are updated. The 12-bit value in this

example is 0x101 which corresponds to 16.0625°C

WRITE

OVRD_CTL

0x01

Sets the OVRD_CTL.TEMP bit. This causes the temperature

stored in the TEMPM_OVRD and TEMPL_OVRD to index the

LUT.

READ

TEMPM

0x**

Optional:

READ

TEMPL

0x**

Read the actual temperature reported by the temperature

sensor.

The temperature sensor override is cancelled by clearing the OVRD_CTL.TEMP bit.

NOTE

TEMPM_OVRD, TEMPL_OVRD and OVRD_CTL registers are in the volatile section of

memory and are not backed by EEPROM. Upon power up these registers are cleared.

8.4.3 ALU Bypass

It may be desirable that the device produces a predetermined constant output level as soon as it is powered up.

The ALU bypass mode does that. This mode is enabled by setting DACx_BASEM.BYP bit. Since

DACx_BASEM.BYP is stored in the EEPROM, its value is automatically loaded into the operating memory at

power up. If the stored value for DACx_BASEM.BYP is 1, upon power up the corresponding DAC output

immediately produces an analog output equivalent of the BASE.

In this mode of operation the ALU is bypassed, and the BASE value of the LUT is presented at the input of the

DAC. This is the result of DACx_BASEM.BYP, which controls the mux that follows the ALU in the signal path,

being set. Therefore, the output of the device is constant over the operating temperature range of the device.

30

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

�LMP92066

www.ti.com

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

NOTE

Each channel has its own BYP bit, and its own BASE value.

8.4.4 DAC Input Override

The DAC inputs words can be directly written via the I2C interface. In this mode the LMP92066 is a dual 12-bit

DAC. This functionality is facilitated by the multiplexers that precede the DACs, and user writable data registers

DACxM_OVRD and DACxL_OVRD. DACxM_OVRD[3:0] is the upper nibble of the DAC input word.

DACxL_OVRD[7:0] is the lower byte of the DAC input data.

The multiplexer control signal is the OVRD_CTL.DAC bit. This bit is shared by both channels; that is, both

channels are either in the DAC input override mode, or both are in the default mode.

Table 12 shows the example of the I2C bus transfer sequence which results in externally supplied data being the

source of input to the DACs.

Table 12. I2C Bus Transfer Sequence:

Externally Supplied Data Sourcing Input to DACs

I2C OPERATION

REGISTER

DATA

DESCRIPTION

WRITE

ACC_CNTL

0xCD

First byte of the “password”

WRITE

ACC_CNTL

0xF0

Second byte of the “password”. After this transfer is completed

the access level is changed to L2

READ

ACC_CNTL

0x03

Optional:

Reading the ACC_CNTL serves as status report.

0x03 – access level L2 is activated (and due to nesting, L1 is

also indicated)

WRITE

DAC0M_OVRD

0x08

Writes 0x8 as the value of the top nibble of the 12-bit, offset

binary, DAC0 input value. After this transaction the

DAC0M_OVRD register is not updated, yet. The update takes

place only after the DAC0L_OVRD register is written.

WRITE

DAC0L_OVRD

0x00

Writes 0x00 into the lower byte of the DAC0 input value. After

this transaction completes both DAC0M_OVRD and

DAC0L_OVRD registers are updated. The 12-bit value in this

example is 0x800.

WRITE

DAC1M_OVRD

0x04

Writes 0x4 as the value of the top nibble of the 12-bit, offset

binary, DAC1 input value. After this transaction the

DAC1M_OVRD register is not updated, yet. The update takes

place only after the DAC1L_OVRD register is written.

WRITE

DAC1L_OVRD

0x00

Writes 0x00 into the lower byte of the DAC1 input value. After

this transaction completes both DAC1M_OVRD and

DAC1L_OVRD registers are updated. The 12-bit value in this

example is 0x400.

WRITE

OVRD_CTL

0x02

Sets the OVRD_CTL.TEMP bit. This causes both multiplexers

that precede the DACs to start routing the DACx_OVRD

values to the inputs of their respective DACs. As a result the

outputs of the device are: VDAC0 = 2.5 V, and VDAC1 = 1.25

V

READ

DAC0M

0x**

Optional:

READ

DAC0L

0x**

Read the values computed by the ALU.

NOTE

The DAC Input Override and Temperature Sensor Override modes are mutually exclusive.

The allowed values for OVRD_CTRL register are 0x00, 0x01 or 0x02.

NOTE

DACxM_OVRD, DACxL_OVRD and OVRD_CTL registers are in the volatile section of

memory and are not backed by EEPROM. Upon power up these registers are cleared.

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

Product Folder Links: LMP92066

31

�LMP92066

SNAS634B – MARCH 2014 – REVISED JANUARY 2016

www.ti.com

8.4.5 LDMOS and GaN Drives

The LDMOS mode and the GaN mode result from 2 possible biasing methods of the DAC output buffers – these

were described in earlier sections of this data sheet.

The LDMOS mode is in effect when the VDDB and VSSB common mode is above GNDA. This mode is suitable

for biasing of the LDMOS Power Amplifiers, since the output produced by the LMP92066 is in the 0 V to 5 V

range. The GaN mode is in effect when the VDDB and VSSB common mode is below GNDA. This mode is

suitable for biasing of the GaN type Power Amplifiers, as the output produced by the LMP92066 is in the 0V to

–5V range.

8.5 Programming

8.5.1 Temperature Sensor Output Data Access Registers

The temperature sensor produces a 12-bit output value, TEMP[11:0], which is stored in 2 adjacent registers:

TEMPM and TEMPL.

The temperature sensor updates its output every 25 ms, nominally, but the exact instance of the update is

unknown to the user. It is possible that the temperature sensor produces a new value between READ operations

of TEMPM and TEMPL. Therefore, a synchronization mechanism was implemented, to assure that TEMPM and

TEMPL values correspond to the same temperature sample. The coherence of the temperature sensor data is

maintained if the READ sequence is: read TEMPM first, then TEMPL.

ADDRESS

0x00

NAME

TEMPM

ACCESS

TYPE

R

ACCESS

LEVEL

BIT

FUNCTION

7

RES

6:5

*

4

RES

3:0

TEMP[11:8]

L0

ADDRESS

NAME

ACCESS

TYPE

ACCESS

LEVEL

BIT

FUNCTION

0x01

TEMPL

R

L0

7:0

TEMP[7:0]

DESCRIPTION

Reserved bit.

The value may be reported as 0 or 1

Reserved bit.

Always reported as 0.

Reserved bit.

The value may be reported as 0 or 1.

4-bit MSB nibble of the 12-bit Temperature Sensor

output word.

DESCRIPTION

8-bit LSB byte of the 12-bit Temperature Sensor

output word.

8.5.2 DAC Input Data Registers