Product

Folder

Sample &

Buy

Support &

Community

Tools &

Software

Technical

Documents

LP38852-ADJ

SNVS482F – JANUARY 2007 – REVISED DECEMBER 2015

LP38852-ADJ 1.5-A Fast-Response High-Accuracy Adjustable LDO Linear Regulator With

Enable and Soft-Start

1 Features

3 Description

•

•

•

•

The LP38852-ADJ is a high-current, fast-response

regulator which can maintain output voltage

regulation with extremely low input-to-output voltage

drop. Fabricated on a CMOS process, the device

operates from two input voltages: VBIAS provides

voltage to drive the gate of the N-MOS power

transistor, while VIN is the input voltage which

supplies power to the load. The use of an external

bias rail allows the part to operate from ultralow VIN

voltages. Unlike bipolar regulators, the CMOS

architecture consumes extremely low quiescent

current at any output load current. The use of an NMOS power transistor results in wide bandwidth, yet

minimum external capacitance is required to maintain

loop stability.

1

•

•

•

•

•

Input VIN Range 0.93 V to 5.5 V

Adjustable VOUT Range 0.8 V to 1.8 V

Wide VBIAS Supply Operating Range 3 V to 5.5 V

Dropout Voltage of 130 mV (Typical) at 1.5-A

Load Current

Precision Output Voltage Across All Line and

Load Conditions:

– ±1.5% VADJ for TJ = 25°C

– ±2% VADJ for 0°C ≤ TJ ≤ +125°C

– ±3% VADJ for –40°C ≤ TJ ≤ +125°C

Overtemperature and Overcurrent Protection

Stable with 10-µF Ceramic Capacitors

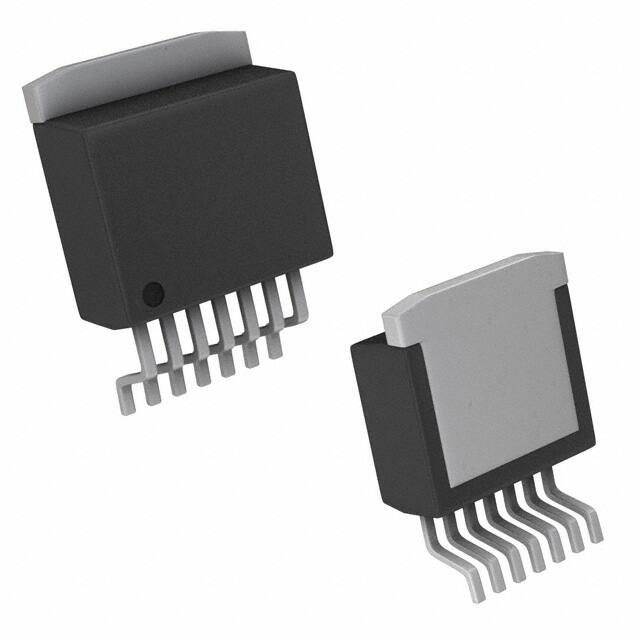

Available in 7-pin TO-220, 7-Pin DDPAK/TO-263,

and 8-Pin SO PowerPAD™ Packages

−40°C to +125°C Operating Junction Temperature

Range

The fast transient response of this device makes it

suitable for use in powering DSP, microcontroller core

voltages, and switch-mode power supply postregulators.

Dropout Voltage: 130 mV (typical) at 1.5-A load

current.

2 Applications

•

•

•

•

ASIC Power Supplies In:

– Desktops, Notebooks, and Graphics Cards,

Servers

– Gaming Set Top Boxes, Printers and Copiers

Server Core and I/O Supplies

DSP and FPGA Power Supplies

SMPS Post-Regulator

Low Ground Pin Current: 10 mA (typical) at 1.5-A

load current.

Soft Start: Programmable soft-start time.

Device Information(1)

PART

NUMBER

LP38852-ADJ

PACKAGE

BODY SIZE (NOM)

DDPAK/TO-263 (7)

10.10 mm × 8.89 mm

TO-220 (7)

14.986 × 10.16 mm

SO PowerPAD (8)

4.89 mm × 3.90 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Typical Application Circuit

LP38852-ADJ

VIN

IN

VBIAS

VOUT

OUT

CIN

CFF

10 PF Ceramic

BIAS

R1

CBIAS

VEN

1 PF

SS

COUT

10 PF

Ceramic

ADJ

EN

R2

GND

CSS

GND

GND

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�LP38852-ADJ

SNVS482F – JANUARY 2007 – REVISED DECEMBER 2015

www.ti.com

Table of Contents

1

2

3

4

5

6

7

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

1

1

1

2

3

4

6.1

6.2

6.3

6.4

6.5

6.6

6.7

4

4

4

5

5

6

7

Absolute Maximum Ratings ......................................

ESD Ratings..............................................................

Recommended Operating Conditions.......................

Thermal Information ..................................................

Electrical Characteristics...........................................

Timing Requirements ................................................

Typical Characteristics ..............................................

Detailed Description ............................................ 11

7.1 Overview ................................................................. 11

7.2 Functional Block Diagram ....................................... 11

7.3 Feature Description................................................. 11

7.4 Device Functional Modes........................................ 14

8

Application and Implementation ........................ 15

8.1 Application Information............................................ 15

8.2 Typical Application ................................................. 15

9 Power Supply Recommendations...................... 19

10 Layout................................................................... 19

10.1 Layout Guidelines ................................................. 19

10.2 Layout Examples................................................... 20

11 Device and Documentation Support ................. 21

11.1

11.2

11.3

11.4

11.5

Documentation Support ........................................

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

21

21

21

21

21

12 Mechanical, Packaging, and Orderable

Information ........................................................... 21

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision E (April 2013) to Revision F

Page

•

Added Device Information and Pin Configuration and Functions sections, ESD Ratings and Thermal Information

tables, Feature Description, Device Functional Modes, Application and Implementation, Power Supply

Recommendations, Layout, Device and Documentation Support, and Mechanical, Packaging, and Orderable

Information sections................................................................................................................................................................ 1

•

Deleted Lead temperature from Abs Max table; it is in POA ................................................................................................ 4

•

Updated thermal information ................................................................................................................................................. 5

•

Deleted out-of-date heatsinking subsections ....................................................................................................................... 17

Changes from Revision D (April 2013) to Revision E

•

2

Page

Changed layout of National Data Sheet to TI format ........................................................................................................... 19

Submit Documentation Feedback

Copyright © 2007–2015, Texas Instruments Incorporated

Product Folder Links: LP38852-ADJ

�LP38852-ADJ

www.ti.com

SNVS482F – JANUARY 2007 – REVISED DECEMBER 2015

5 Pin Configuration and Functions

KTW Package

7-Pin DDPAK/TO-263

Top View

TAB

IS

GND

SS

EN

IN

GND

ADJ

OUT

BIAS

1

2

3

4

5

6

7

LP38852T-ADJ

1

2

3

4

5

6

7

LP38852S-ADJ

SS

EN

IN

GND

ADJ

OUT

BIAS

NDZ Package

7-Pin TO-220

Top View

TAB

IS

GND

DDA Package

8-Pin SO PowerPAD

Top View

ADJ 1

8 N/C

OUT 2

7 IN

BIAS 3

6 EN

GND 4

5 SS

DAP

Connect to GND

Pin Functions

PIN

NAME

TYPE

DESCRIPTION

DDPAK/TO-263

TO-220

SO PowerPAD

ADJ

5

5

1

O

The feedback connection to set the output voltage

BIAS

7

7

3

I

The supply for the internal control and reference circuitry.

EN

2

2

6

I

Device enable, High = On, Low = Off.

GND

4

4

4

GND

IN

3

3

7

I

N/C

-

-

8

—

No internal connection

OUT

6

6

2

O

The regulated output voltage

SS

1

1

5

O

Soft-start capacitor connection. Used to control the rise time

of VOUT at turnon.

TAB

TAB

TAB

—

—

The KTW and NDZ TAB is a thermal and electrical

connection that is physically attached to the backside of the

die, and used as a thermal heat-sink connection.

DAP

—

—

DAP

—

The SO PowerPAD DAP is a thermal connection only that is

physically attached to the backside of the die, and used as a

thermal heat-sink connection.

Ground

The unregulated voltage input

Submit Documentation Feedback

Copyright © 2007–2015, Texas Instruments Incorporated

Product Folder Links: LP38852-ADJ

3

�LP38852-ADJ

SNVS482F – JANUARY 2007 – REVISED DECEMBER 2015

www.ti.com

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

MIN

MAX

UNIT

VIN supply voltage (survival)

−0.3

6

V

VBIAS supply voltage (survival)

−0.3

6

V

VSS soft-start voltage (survival)

−0.3

6

V

VOUT voltage (survival)

−0.3

6

V

IOUT current (survival)

Internally Limited

−40

Junction temperature

Power dissipation (3)

−65

Storage temperature, Tstg

(1)

(2)

(3)

150

°C

Internally Limited

150

°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

If Military/Aerospace specified devices are required, contact the TI Sales Office/ Distributors for availability and specifications.

Device power dissipation must be de-rated based on device power dissipation (PD), ambient temperature (TA), and package junction to

ambient thermal resistance (RθJA). Additional heat-sinking may be required to ensure that the device junction temperature (TJ) does not

exceed the maximum operating rating. See the Application and Implementation section for details.

6.2 ESD Ratings

V(ESD)

(1)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

VALUE

UNIT

±2000

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

VIN supply voltage (survival)

NOM

MAX

UNIT

(VOUT + VDO) to VBIAS

V

0.8 V ≤ VOUT ≤ 1.2 V

3

5.5

V

1.2 V < VOUT ≤ 1.8 V

4.5

5.5

V

VEN voltage

0

VBIAS

IOUT

0

3

mA

−40

125

°C

VBIAS supply voltage (survival) (1)

Junction temperature (2)

(1)

(2)

4

V

VIN cannot exceed either VBIAS or 4.5 V, whichever value is lower.

Device power dissipation must be de-rated based on device power dissipation (PD), ambient temperature (TA), and package junction-toambient thermal resistance (RθJA). Additional heat sinking may be required to ensure that the device junction temperature (TJ) does not

exceed the maximum operating rating. See the Application and Implementation section for details.

Submit Documentation Feedback

Copyright © 2007–2015, Texas Instruments Incorporated

Product Folder Links: LP38852-ADJ

�LP38852-ADJ

www.ti.com

SNVS482F – JANUARY 2007 – REVISED DECEMBER 2015

6.4 Thermal Information

LP38852-ADJ

THERMAL METRIC (1)

KTW (DDPAK/TO-263)

NDZ (TO-220)

DDA (SO PowerPAD)

7 PINS

7 PINS

8 PINS

UNIT

RθJA

Junction-to-ambient thermal resistance

34.3

34.0

48.4

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

37.6

36.4

54.6

°C/W

RθJB

Junction-to-board thermal resistance

25.3

25.0

29.1

°C/W

ψJT

Junction-to-top characterization parameter

6.6

6.3

9.6

°C/W

ψJB

Junction-to-board characterization parameter

24.0

23.6

29.0

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

n/a

n/a

4.3

°C/W

(1)

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

6.5 Electrical Characteristics

Unless otherwise specified: VOUT = 0.8 V, VIN = VOUT(NOM) + 1 V, VBIAS = 3 V, VEN = VBIAS, IOUT = 10 mA, CIN = COUT = 10 µF,

CBIAS = 1 µF, CSS = open; typical (TYP) limits are for TJ = 25°C only, and minimum (MIN) and maximum (MAX) limits apply

over the junction temperature (TJ) range of –40°C to +125°C. Minimum and maximum limits are specified through test,

design, or statistical correlation. Typical values represent the most likely parametric norm at TJ = 25°C, and are provided for

reference purposes only.

PARAMETER

VADJ

VADJ accuracy

MIN

TYP

MAX

VOUT(NOM)+1 V ≤ VIN ≤ VBIAS ≤ 4.5 V (1)

3 V ≤ VBIAS ≤ 5.5 V, 10 mA ≤ IOUT ≤ 1.5 A

TJ = 25°C

TEST CONDITIONS

492.5

500.

507.5

VOUT(NOM)+1 V ≤ VIN ≤ VBIAS ≤ 4.5 V (1)

3 V ≤ VBIAS ≤ 5.5 V, 10 mA ≤ IOUT ≤ 1.5 A

485

VOUT(NOM)+1 V ≤ VIN ≤ VBIAS ≤ 4.5 V (1)

3 V ≤ VBIAS ≤ 5.5 V,

10 mA ≤ IOUT ≤ 1.5 A,

0°C ≤ TJ ≤ +125°C

490

3 V ≤ VBIAS ≤ 5.5 V

0.8

1.2

4.5 V ≤ VBIAS ≤ 5.5 V

0.8

1.8

515

500.

UNIT

mV

510

VOUT

VOUT range

ΔVOUT/ΔVIN

Line regulation, VIN (2)

VOUT(NOM)+1 V ≤ VIN ≤ VBIAS

0.04

%/V

ΔVOUT/ΔVBIAS

Line regulation, VBIAS (2)

3 V ≤ VBIAS ≤ 5.5 V

0.1

%/V

ΔVOUT/ΔIOUT

Output voltage load

regulation (3)

10 mA ≤ IOUT ≤ 1.5 A

0.2

%/A

VDO

Dropout voltage (4)

IOUT = 1.5 A, TJ = 25°C

130

IOUT = 1.5 A

VOUT = 0.8 V, VBIAS = 3 V

10 mA ≤ IOUT ≤ 1.5 A

TJ = 25°C

IGND(IN)

Quiescent current drawn from

VIN supply

180

7

IGND(BIAS)

Quiescent current drawn from

VBIAS supply

1

VEN ≤ 0.5 V

(1)

(2)

(3)

(4)

100

300

3

10 mA ≤ IOUT ≤ 1.5 A

VEN ≤ 0.5 V, TJ = 25°C

8.5

9

VEN ≤ 0.5 V

10 mA ≤ IOUT ≤ 1.5 A, TJ = 25°C

mV

mA

VOUT = 0.8 V, VBIAS = 3 V

10 mA ≤ IOUT ≤ 1.5 A

VEN ≤ 0.5 V, TJ = 25°C

165

V

3.8

4.5

100

170

200

μA

mA

μA

VIN cannot exceed either VBIAS or 4.5 V, whichever value is lower.

Output voltage line regulation is defined as the change in output voltage from nominal value resulting from a change in input voltage.

Output voltage load regulation is defined as the change in output voltage from nominal value as the load current increases from no load

to full load.

Dropout voltage is defined as the input to output voltage differential (VIN – VOUT) where the input voltage is low enough to cause the

output voltage to drop 2% from the nominal value.

Submit Documentation Feedback

Copyright © 2007–2015, Texas Instruments Incorporated

Product Folder Links: LP38852-ADJ

5

�LP38852-ADJ

SNVS482F – JANUARY 2007 – REVISED DECEMBER 2015

www.ti.com

Electrical Characteristics (continued)

Unless otherwise specified: VOUT = 0.8 V, VIN = VOUT(NOM) + 1 V, VBIAS = 3 V, VEN = VBIAS, IOUT = 10 mA, CIN = COUT = 10 µF,

CBIAS = 1 µF, CSS = open; typical (TYP) limits are for TJ = 25°C only, and minimum (MIN) and maximum (MAX) limits apply

over the junction temperature (TJ) range of –40°C to +125°C. Minimum and maximum limits are specified through test,

design, or statistical correlation. Typical values represent the most likely parametric norm at TJ = 25°C, and are provided for

reference purposes only.

PARAMETER

UVLO

Undervoltage lockout threshold

TEST CONDITIONS

MIN

TYP

MAX

VBIAS rising until device is functional

TJ = 25°C

2.2

2.45

2.7

VBIAS rising until device is functional

2

VBIAS falling from UVLO threshold until

device is non-functional

Undervoltage lockout hysteresis TJ = 25°C

VBIAS falling from UVLO threshold until

device is non-functional

UVLO(HYS)

ISC

Output short-circuit current

60

UNIT

V

2.9

150

300

mV

50

VIN = VOUT(NOM) + 1 V, VBIAS = 3 V,

VOUT = 0 V

350

4.5

A

SOFT-START

rSS

Soft-start internal resistance

tSS

Soft-start time

tSS = CSS × rSS × 5

11

CSS = 10 nF

13.5

16

kΩ

μs

675

ENABLE

VEN = VBIAS

IEN

ENABLE pin current

VEN(ON)

Enable voltage threshold

VEN(HYS)

Enable voltage hysteresis

0.01

VEN = 0 V, VBIAS = 5.5 V, TJ = 25°C

–19

VEN = 0 V, VBIAS = 5.5 V

–13

VEN rising until output = ON, TJ = 25°C

1

VEN rising until output = ON

0.9

VEN falling from VEN(ON) until Output = OFF

TJ = 25°C

50

VEN falling from VEN(ON) until Output = OFF

30

–30

–40

μA

–51

1.25

1.5

1.55

100

150

V

mV

200

AC PARAMETERS

PSRR (VIN)

PSRR (VBIAS)

Ripple rejection for VIN input

voltage

Ripple rejection for VBIAS

voltage

Output noise density

en

Output noise voltage

VIN = VOUT(NOM) + 1 V,

ƒ = 120 Hz

80

VIN = VOUT(NOM) + 1 V,

ƒ = 1 kHz

65

VBIAS = VOUT(NOM) + 3 V,

ƒ= 120 Hz

58

VBIAS = VOUT(NOM) + 3 V,

ƒ = 1 kHz

58

dB

dB

ƒ = 120 Hz

1

BW = 10 Hz − 100 kHz

150

BW = 300 Hz − 300 kHz

90

µV/√Hz

µVRMS

THERMAL PARAMETERS

TSD

Thermal shutdown junction

temperature

TSD(HYS)

Thermal shutdown hysteresis

160

°C

10

°C

6.6 Timing Requirements

MIN

NOM

MAX

UNIT

tOFF

Turnoff delay time, RLOAD x COUT