LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

LP3950 Color LED Driver with Audio Synchronizer

Check for Samples: LP3950

FEATURES

DESCRIPTION

•

The LP3950 is a color LED driver with a built-in audio

synchronization feature for any analog audio input

such as polyphonic ring tones and MP3 music. LEDs

can be synchronized to an audio signal with two

methods - amplitude and frequency. Also several fine

tuning options are available for differentiation

purposes. The chip also has an unique AGC

(Automatic Gain Control) feature which tracks the

input signal level and automatically adjusts the gain

to an optimal value.

1

2

•

•

•

•

•

•

•

Audio Synchronization for Color LEDs with

Two Modes: Amplitude and Frequency

Programmable Frequency and Amplitude

Response with Tracking Speed Control

Automatic Gain Control or Selectable Gain for

Input Signal Optimization

RGB Pattern Generator Similar to

LP3933/LP3936

Magnetic DC-DC Boost Converter with

Programmable Boost Output Voltage

Selectable SPI or I2C Compatible Interface

One Pin Default Enable for Non-Serial Interface

Users. One Pin Selector for Synchronization

Mode

Space Efficient 32-Pin TLGA Package

The LP3950 has a high efficiency magnetic DC/DC

converter with programmable output voltage and

switching frequency. The converter has high output

current capability so it is also able to drive flash LEDs

in camera phone applications.

The LP3950 is similar

the color LEDs (or

programmed

to

(programmable color,

and blinking cycle).

APPLICATIONS

•

•

•

Cellular Phones

MP3/CD/Minidisc Players

Toys

to LP3933 and LP3936 in that

RGB LEDs) can also be

generate

light

patterns

intensity, on/off timing, slope

All functions are software controllable through a SPI

or I2C compatible interface but the device also

supports one pin control for enabling predefined

(default) audio synchronization mode.

Typical Application

VIN

2.8V

CVDD1

100 nF

VDD1

C1

SINGLE-ENDED

AUDIO SIGNAL

CVDD2

100 nF

VDD2

L1

CIN

4.7 PH

10 PF

D1

VDDA

SW

ASE

10 nF

COUT

10 PF

FB

RR1

C2

R1

AD1

DIFFERENTIAL

AUDIO SIGNAL

CVDDA

100 nF

RG1

10 nF

G1

C3

RB1

B1

AD2

10 nF

4

LP3950

SERIAL

INTERFACE

RG2

G2

RB2

NRST

MICROCONTROLLER

RR2

R2

B2

PWM_LED

RT

RT

82k

IF_SEL

VREF

VDD_IO

CVDD_IO

100 nF

DME

AMODE

GNDs

CVREF

100 nF

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2004–2013, Texas Instruments Incorporated

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

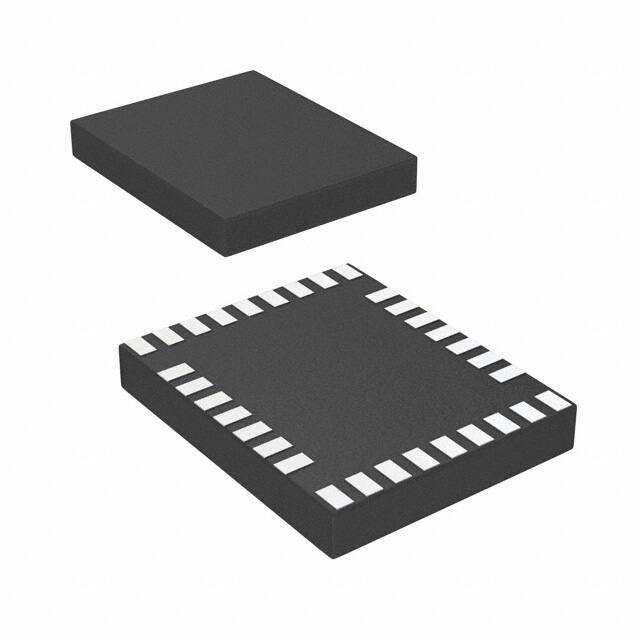

Connection Diagrams

Top View

Bottom View

Figure 1. 32-Lead TLGA Package

4.5 x 5.5 x 0.8 mm, 0.5 mm Pitch, See Package Number NPC0032A

2

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

PIN DESCRIPTIONS

Pin #

Name

Type

Description

1

FB

Input

2

GND_BOOST

Ground

Boost converter feedback.

Power switch ground.

3

SW

Output

Open drain, boost converter power switch.

4

VDD2

Power

Supply voltage for internal digital circuits.

5

GND2

Ground

Ground return for VDD2 (internal digital).

6

DME

Logic Input

Default mode enable (internal pull down 1 MΩ).

7

AMODE

Logic Input

Audio mode selection (internal pull down 1 MΩ).

8

VDDA

Power

Supply voltage for audio circuits.

9

ASE

Input

Analog audio input, single-ended.

10

AD1

Input

Analog audio input, differential.

11

AD2

Input

Analog audio input, differential.

12

GNDA

Ground

Ground for analog audio inputs.

13

RT

Input

Oscillator resistor.

14

VDD1

Power

Supply voltage for internal analog circuits.

15

GND1

Ground

Ground.

16

VREF

Output

Internal reference bypass capacitor.

17

GND3

Ground

Ground.

18

NRST

Logic Input

19

SS/SDA

Logic I/O

20

SO

Logic Output

21

SI

Logic Input

SPI serial data input.

22

SCK/SCL

Logic Input

SPI/ I2C clock.

23

PWM_LED

Logic Input

Direct PWM control for LEDs.

Low active reset input.

SPI slave select/ I2C data line.

SPI serial data output.

24

VDDIO

Power

25

IF_SEL

Logic Input

Supply voltage for logic IO signals.

26

B2

Output

Open drain output, blue LED2.

27

G2

Output

Open drain output, green LED2.

SPI/I2C select (IF_SEL = 1 in SPI mode).

28

R2

Output

Open drain output, red LED2.

29

GND_RGB

Ground

RGB driver ground.

30

R1

Output

Open drain output, red LED1.

31

G1

Output

Open drain output, green LED1.

32

B1

Output

Open drain output, blue LED1.

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

3

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1) (2) (3)

(4) (5)

V (SW, FB, R1–2, G1–2, B1–2)

−0.3V to +7.2V

−0.3V to +6.0V

VDD1, VDD2, VDDIO, VDDA

−0.3V to VDD1 +0.3V with 6.0V max

Voltage on ASE, AD1, AD2

−0.3V to VDD_IO+0.3V with 6.0V max

Voltage on Logic Pins

(6)

I (R1, G1, B1, R2, G2, B2)

150 mA

I (VREF)

10 µA

Continuous Power Dissipation

(7)

Internally Limited

Junction Temperature (TJ-MAX)

125°C

Storage Temperature Range

−65°C to +150°C

Maximum Lead Temperature

260°C

(Reflow soldering, 3 times)

ESD Rating

(8)

(9)

Human Body Model:

2 kV

Machine Model:

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

200V

All voltages are with respect to the potential at the GND pins (GND1–3, GND_BOOST, GND_RGB, GNDA).

Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under

which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed

performance limits and associated test conditions, see the Electrical Characteristics tables.

If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

Battery/Charger voltage should be above 6.0V no more than 10% of the operational lifetime.

Voltage tolerance of LP3950 above 6.0V relies on fact that VDD1, VDD2 and VDDA (2.8V) are available (ON) at all conditions. If VDD1,

VDD2 and VDDA are not available (ON) at all conditions, Texas Instruments does not guarantee any parameters or reliability for this

device. Also, VDD1, VDD2 and VDDA must be at the same electric potential.

The total load current of the boost converter should be limited to 300 mA.

Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at TJ = 160°C (typ.) and

disengages at TJ = 140°C (typ.).

For detailed package and soldering specifications and information, please refer to Texas Instruments Application Note 1125 (SNAA002):

Laminate CSP/FBGA.

The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF

capacitor discharged directly into each pin. MIL-STD-883 3015.7

Operating Ratings (1) (2)

V (SW, FB, R1–2, G1–2, B1–2)

0V to 6.0V

VDD1, VDD2, VDDA (3)

2.7V to 2.9V

VDDIO

1.65V to VDD1,2 V

Voltage on ASE, AD1, AD2

0.1V to VDD1 - 0.1V

Recommended Load Current

0 mA to 300 mA

−40°C to +125°C

Junction Temperature (TJ) Range

Ambient Temperature (TA) Range

(1)

(2)

(3)

(4)

4

(4)

−40°C to +85°C

Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under

which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed

performance limits and associated test conditions, see the Electrical Characteristics tables.

All voltages are with respect to the potential at the GND pins (GND1–3, GND_BOOST, GND_RGB, GNDA).

Voltage tolerance of LP3950 above 6.0V relies on fact that VDD1, VDD2 and VDDA (2.8V) are available (ON) at all conditions. If VDD1,

VDD2 and VDDA are not available (ON) at all conditions, Texas Instruments does not guarantee any parameters or reliability for this

device. Also, VDD1, VDD2 and VDDA must be at the same electric potential.

In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may

have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP =

125°C), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the

part/package in the application (θJA), as given by the following equation: TA-MAX = TJ-MAX-OP − (θJA x PD-MAX).

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

Thermal Properties

Junction-to-Ambient Thermal Resistance

(θJA), NPC0032A Package

(1)

72°C/W

(1)

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power

dissipation exists, special care must be paid to thermal dissipation issues in board design.

Electrical Characteristics

(1) (2)

Limits in standard typeface are for TJ = +25°C. Limits in boldface type apply over the operating ambient temperature range

(−40°C ≤ TA ≤ +85°C). Unless otherwise noted, specifications apply to Figure 2 with: VDD1 = VDD2 = VDDA = 2.8V, CVDD1 =

CVDD2 = CVDDA = CVDDIO = 100 nF, COUT = CIN = 10 µF, CVREF = 100 nF, L1 = 4.7 µH and fBOOST = 2.0 MHz (3).

Symbol

IVDD

Parameter

Condition

Min

Typ

Max

Units

Standby Supply Current

(VDD1 + VDD2 + VDDA current)

NSTBY = L (register)

SCK, SS, SI, NRST = H

1

5

µA

No-Load Supply Current

(VDD1 + VDD2 + VDDA current, boost off)

NSTBY = H (reg.)

EN_BOOST = L (reg.)

SCK, SS, SI, NRST = H

300

400

µA

Full Load Supply Current

(VDD1 + VDD2 + VDDA current, boost on) (4)

NSTBY = H (reg.)

EN_BOOST = H (reg.)

SCK, SS, SI, NRST = H

All Outputs Active

850

µA

IVDDIO

VDDIO Supply Current

1.0 MHz SCK Frequency

CL = 50 pF at SO Pin

20

µA

IVDDA

Audio Circuitry Supply Current (5)

INPUT_SEL = [10] (register)

550

µA

VREF

Reference Voltage (6)

IREF ≤ 1.0 nA Only for Test Purpose

1.230

V

(1)

(2)

(3)

(4)

(5)

(6)

All voltages are with respect to the potential at the GND pins (GND1–3, GND_BOOST, GND_RGB, GNDA).

Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the

most likely norm.

Low-ESR Surface-Mount Ceramic Capacitors are used in setting electrical characteristics.

Audio block inactive.

In single-ended and in differential mode one audio buffer only is active and IVDDA will be reduced by 90 µA (typ).

VREF pin (Bandgap reference output) is for internal use only. A capacitor should always be placed between VREF and GND1.

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

5

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

Block Diagram

CVDD2

100 nF

CVDDA

CIN

10 PF

-

CVDD1

100 nF

100 nF

VDD1

D1

SW

CVREF

OSC

COUT

10 PF

FB

THSD

100 nF

GND_BOOST

LP3950

RT

EN

VREF

BOOST

RT

82k

ASE

R1

FREQ

10 nF

L1

4.7 PH

VDDA

VDD2

VREF

SINGLE ENDED

AUDIO SIGNAL

10 nF

IMAX = 300 mA

VOUT = 4.1V TO 5.3V

+

BATTERY

LDO

2.8V

ADC

AD1

AGC

PWM

G1

AMPL

AD2

10 nF

B1

GNDA

SPI

RGB PATTERN

GENERATOR

CTRL

2

DRIVERS

DIFFERENTIAL

AUDIO SIGNAL

I C

RR1

RG1

RB1

RR2

R2

G2

B2

RG2

RB2

LEVEL SHIFTER

MICROCONTROLLER

GND3

GND1

GND2

VDDIO

DME

AMODE

NRST

PWM_LED

SI

SO

SS/SDA

IF_SEL

SCK/SCL

GND_RGB

CVDDIO

100 nF

Figure 2. LP3950 Block Diagram

Modes of Operation

RESET: In the RESET mode all the internal registers are reset to the default values. RESET is entered always if

input NRST is LOW or internal Power On Reset is active.

STANDBY: The STANDBY mode is entered if the register bit NSTBY is LOW and RESET is not active. This is

the low power consumption mode, when all the circuit functions are disabled. Registers can be written in

this mode and the control bits are effective immediately after start up.

STARTUP: INTERNAL STARTUP SEQUENCE powers up all the needed internal blocks (VREF, oscillator, etc.).

To ensure the correct oscillator initialization, a 10 ms delay is generated by the internal state-machine.

Thermal shutdown (THSD) disables the chip operation and Startup mode is entered until no thermal

shutdown event is present.

BOOST STARTUP: Soft start for boost output is generated in the BOOST STARTUP mode. In this mode the

boost output is raised in PFM mode during the 10 ms delay generated by the state-machine. All RGB

outputs are off during the 10 ms delay to ensure smooth startup. The Boost startup is entered from

Internal Startup Sequence if EN_BOOST is HIGH or from Normal mode when EN_BOOST is written

HIGH.

NORMAL: During the NORMAL mode the user controls the chip using the control registers. Registers can be

written in any sequence and any number of bits can be altered in a register within one write cycle . If the

default mode is selected, default control register values are used.

6

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

RESET

NRST = L

or

POR = H

NSTBY= L and

DME = L and

NRST = H

STANDBY

(NSTBY = H or DME = H)

and

NRST = H

(NSTBY = H or DME = H)

and

NRST = H

NSTBY = L

and

DME = L

and

NRST = H

INTERNAL

STARTUP

SEQUENCE

V REF = 95% OK 1

THSD = H

~10 ms DELAY

DME = H or

EN_BOOST = H1

DME = L and

EN_BOOST = L1

BOOST STARTUP

EN_BOOST

RISING EDGE1

~10 ms DELAY

NORMAL MODE

1) THSD = L

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

7

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

Logic Interface Characteristics (1)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

0.5

V

LOGIC INPUTS SS, SI, SCK/SCL, PWM_LED, IF_SEL

VIL

Input Low Level

VIH

Input High Level

II

Logic Input Current

fSCL

Clock Frequency

VDDIO − 0.5

V

−1.0

1.0

µA

I2C Mode

400

kHz

SPI Mode

8

MHz

0.5

V

LOGIC OUTPUT SO

VOL

Output Low Level

ISO = 3.0 mA

VOH

Output High Level

ISO = −3.0 mA

IL

Output Leakage Current

VSO = 2.8V

0.3

VDDIO − 0.5

VDDIO − 0.3

V

1.0

µA

0.5

V

0.5

V

6.0

µA

LOGIC I/O SDA

VOL

Output Low Level

ISDA = 3.0 mA

0.3

LOGIC INPUTS DME, AMODE (Internal pull down 1 MΩ)

VIL

Input Low Level

VIH

Input High Level

II

Logic Input Current

VDDIO − 0.5

V

−1.0

(1.80V ≤ VDDIO ≤ VDD1,2V). Limits in standard typeface are for TJ = +25°C. Limits in boldface type apply over the operating ambient

temperature range (−40°C ≤ TA ≤ +85°C).

(1)

Logic Interface Characteristics, Low I/O Voltage (1)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

0.35

V

1.0

µA

200

kHz

0.5

V

0.35

V

6.0

µA

Max

Units

0.5

V

1.0

µA

LOGIC INPUTS SCL, PWM_LED, IF_SEL

VIL

Input Low Level

VIH

Input High Level

II

Logic Input Current

fSCL

Clock Frequency

VDDIO − 0.35

V

−1.0

I2C Mode

LOGIC I/O SDA

VOL

Output Low Level

ISDA = 3.0 mA

0.3

LOGIC INPUTS DME, AMODE (Internal pull down 1 MΩ)

VIL

Input Low Level

VIH

Input High Level

II

Logic Input Current

VDDIO − 0.35

V

−1.0

(1.65V ≤ VDDIO < 1.80V) . I2C compatible interface only.

(1)

Logic Input NRST Characteristics (1)

Symbol

Parameter

Conditions

Min

VIL

Input Low Level

VIH

Input High Level

1.3

II

Logic Input Current

−1.0

tNRST

Reset Pulse Width

(1)

8

Note: Guaranteed by

design

10

Typ

V

µs

(1.65V ≤ VDDIO ≤ VDD1,2V).

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

Control Interface

The LP3950 supports three different interface modes:

1. SPI interface (4 wire, serial)

2. I2C compatible interface (2 wire, serial)

3. Direct enable (2 wire, enable lines)

User can define the serial interface by the IF_SEL pin. The following table shows the pin configuration for both

interface modes. Note that the pin configurations will be based on the status of the IF_SEL pin.

IF_SEL

Interface

Pin Configuration

Comment

HIGH

SPI

SCK

SI

SO

SS

(clock)

(data in)

(data out)

(chip select)

LOW

I2C Compatible

SCL

SDA

SI

SO

(clock)

(data in/out)

(I2 address)

(NC)

Use pull up resistor for SCL.

Use pull up resistor for SDA.

SI HIGH → address is 51'h;

SI LOW → address is 50'h;

Unused pin SO can be left unconnected.

SPI Interface

The transmission consists of 16-bit write and read cycles. One cycle consists of seven address bits, one

read/write (R/W) bit and eight data bits. R/W bit high state defines a write cycle and low defines a read cycle. SO

output is normally in high-impedance state and it is active only during when data is sent out during a read cycle.

A pull-up or pull-down resistor may be needed for SO line if a floating logic signal can cause unintended current

consumption in the circuitry.

The address and data are transmitted Most Significant Byte (MSB) first. The Slave Select signal (SS) must be

low during the cycle transmission. SS resets the interface when high and it has to be taken high between

successive cycles. Data is clocked in on the rising edge of the SCK clock signal, while data is clocked out on the

falling edge of SCK.

SS

SCK

SI

A6

A5

A4

A3

A2

A1

A0

1

R/W

D7

D6

D5

D4

D3

D2

D1

D0

D2

D1

D0

SO

Figure 3. SPI Write Cycle

SS

SCK

SI

A6

A5

A4

A3

A2

A1

A0

R/W

0

Don't Care

SO

D7

D6

D5

D4

D3

Figure 4. SPI Read Cycle

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

9

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

SS

2

5

1

SCK

3

4

12

7

6

SI

MSB IN

BIT 14

BIT 9

BIT 8

BIT 1

BIT 7

8

Address

9

11

10

MSB OUT

SO

LSB IN

BIT 1

LSB OUT

Data

R/W

Figure 5. SPI Timing Diagram

Table 1. SPI Timing Parameters (1)

Symbol

(1)

Limit

Parameter

Min

Max

Units

1

Cycle Time

80

ns

2

Enable Lead Time

40

ns

3

Enable Lag Time

40

ns

4

Clock Low Time

40

ns

5

Clock High Time

40

ns

6

Data Setup Time

0

ns

7

Data Hold Time

20

8

Data Access Time

27

ns

9

Output Disable Time

27

ns

10

Output Data Valid

37

ns

11

Output Data Hold Time

0

ns

12

SS Inactive Time

15

ns

ns

Data guaranteed by design.

I2C Compatible Interface

I2C SIGNALS

In I2C compatible mode, the LP3950 pin SCL is used for the I2C clock and the SDA pin is used for the I2C data.

Both these signals need a pull-up resistor according to I2C specification. The values of the pull-up resistors are

determined by the capacitance of the bus (typ. 1.8k). Signal timing specifications are shown in Table 2. Unused

pin SO can be left unconnected and pin SI must be connected to VDDIO or GND (address selector). Maximum bit

rate is 400 kbit/s (VDDIO 1.80V to VDD1,2V). I2C compatible interface can be used down to 1.65 VDDIO with

maximum bit rate of 200 kbit/s.

I2C DATA VALIDITY

The data on the SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state

of the data line can only be changed when CLK is LOW.

SCL

SDA

data

change

allowed

data

valid

data

change

allowed

data

valid

data

change

allowed

Figure 6. I2C Signals: Data Validity

10

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

I2C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of the I2C session. START condition is defined as SDA

signal transition from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transition

from LOW to HIGH while SCL is HIGH. The I2C master always generates START and STOP bits. The I2C bus is

considered to be busy after START condition and free after STOP condition. During data transmission, the I2C

master can generate repeated START conditions. First START and repeated START conditions are equivalent,

function-wise.

SDA

SCL

S

P

STOP condition

S TART condition

Figure 7. Start and Stop Conditions

TRANSFERRING DATA

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first.

Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated

by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver

must pull down the SDA line during the 9th clock pulse, signifying an acknowledge. A receiver which has been

addressed must generate an acknowledge after each byte has been received.

After the START condition, the I2C master sends a chip address. This address is seven bits long followed by an

eighth bit which is a data direction bit (R/W). The LP3950 address is 50'h or 51'h. The selection of the address is

done by connecting SI pin to VDDIO (51 hex) or GND (50 hex). For the eighth bit, a “0” indicates a WRITE and a

“1” indicates a READ. The second byte selects the register to which the data will be written. The third byte

contains data to write to the selected register.

MSB

LSB

ADR6

bit7

ADR5

bit6

ADR4

bit5

ADR3

bit4

ADR2

bit3

ADR1

bit2

ADR0

bit1

0

1

1

0

1

1

0

R/W

bit0

I2C SLAVE address (chip address)

Figure 8. I2C Chip Address

ack from slave

ack from slave

start

msb Chip Address lsb

w

ack

msb Register Add lsb

ack

start

Id = 36h

w

ack

addr = 02h

ack

ack from slave

msb

DATA

lsb

ack

stop

ack

stop

SCL

SDA

DGGUHVV K¶02 data

w = write (SDA = “0”)

r = read (SDA = “1”)

ack = acknowledge (SDA pulled down by either master or slave)

rs = repeated start

id = chip address, 50'h or 51'h for LP3950.

Figure 9. I2C Write Cycle

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

11

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in

Figure 10 .

ack from slave

ack from slave

start

msb Chip Address lsb

start

Id = 36h

w

msb Register Add lsb

ack from slave data from slave ack from master

repeated start

rs

msb Chip Address lsb

rs

Id = 36h

r

msb

DATA

lsb

r ack

$GGUHVV K¶00 data

stop

SCL

SDA

addr = K¶00

w ack

ack

ack stop

Figure 10. I2C Read Cycle

SDA

10

8

7

6

1

8

2

7

SCL

5

1

3

4

9

Figure 11. I2C Timing Diagram

Table 2. I2C Timing Parameters (1)

Symbol

Parameter

Limit

Min

(1)

12

Units

Max

1

Hold Time (repeated) START Condition

0.6

µs

2

Clock Low Time (1.65V ≤ VDDIO < 1.80V)

3.2

µs

2

Clock Low Time (1.80V ≤ VDDIO ≤ VDD1,2V)

1.3

µs

3

Clock High Time (1.65V ≤ VDDIO < 1.80V)

1200

ns

3

Clock High Time (1.80V ≤ VDDIO ≤ VDD1,2V)

600

ns

4

Setup Time for a Repeated START Condition

600

ns

5

Data Hold Time (data output, delay generated by LP3950)

300

900

ns

5

Data Hold Time (data input)

0

900

ns

6

Data Setup Time

7

Rise Time of SDA and SCL

20+0.1Cb

300

ns

8

Fall Time of SDA and SCL

15+0.1Cb

300

ns

9

Set-up Time for STOP condition

600

ns

10

Bus Free Time between a STOP and a START Condition

1.3

µs

Cb

Capacitive Load Parameter for Each Bus Line.

Load of One Picofarad Corresponds to One Nanosecond.

10

100

ns

200

ns

Data guaranteed by design

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

Magnetic Boost DC/DC Converter

The boost DC/DC converter generates a 4.1V–5.3V output voltage to drive LEDs from a single Li-Ion battery

(3.0V to 4.5V). The output voltage is controlled with an eight-bit register in nine steps. The converter is a

magnetic switching PWM mode DC/DC converter with a current limit. The converter has three options for

switching frequency, 1.0 MHz, 1.67 MHz and 2.0 MHz (default), when the timing resistor RT is 82 kΩ.

The LP3950 boost converter uses an unique pulse-skipping elimination method to stabilize the noise spectrum.

Even with light load or no load a minimum length current pulse is fed to the inductor. An internal active load is

used to remove the excess charge from the output capacitor when needed (see NOTE below). The boost

converter should be disabled when there is no load to avoid idle current consumption.

The topology of the magnetic boost converter is called CPM control, current programmed mode, where the

inductor current is measured and controlled with the feedback. The output voltage control changes the resistor

divider in the feedback loop.

Figure 12 shows the boost topology with the protection circuitry. Four different protection schemes are

implemented:

1. Over voltage protection, limits the maximum output voltage

– Keeps the output below breakdown voltage

– Prevents boost operation if the battery voltage is much higher than desired output

2. Over current protection, limits the maximum inductor current

– Voltage over switching NMOS is monitored; too high voltages turn the switch off

3. Feedback (FB) protection for no connection

4. Duty cycle limit function, done with digital control

NOTE

When the battery voltage is close to the output voltage, the output voltage may rise slightly

over programmed value if the load on output is small and pulse-skipping elimination is

active.

2 MHz clock

VIN

Duty control

VOUT

SW

FBNCCOMP

FB

+

-

R

S

R

OVPCOMP

SWITCH

+

-

R

RESETCOMP

+

ERRORAMP

SLOPER

+

-

+

-

R

+

-

R

OLPCOMP

ACTIVE

LOAD

LOOPC

Figure 12. Boost Converter Functional Block Diagram

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

13

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

Magnetic Boost DC/DC Converter Electrical Characteristics (1) (2)

Symbol

Parameter

Conditions

ILOAD

Load Current

3.0V ≤ VIN ≤ 4.5V

VOUT = 5.0V

VOUT

Output Voltage Accuracy

(FB Pin)

1.0 mA ≤ ILOAD ≤ 300 mA

3.0V ≤ VIN ≤ 4.5V

VOUT = 5.0V (target value), autoload OFF

Output Voltage

(FB Pin)

1.0 mA ≤ ILOAD ≤ 300 mA

3.0V < VIN < 5.0V + V(SCHOTTKY),

autoload OFF

Min

Typ

Max

Units

0

300

mA

−5

+5

%

5.0

V

1.0 mA ≤ ILOAD ≤ 300 mA

VIN > 5V + V(SCHOTTKY)

VIN–V(SCHOTTKY)

V

RDSON

Switch ON Resistance

VDD1,2 = 2.8V, ISW = 0.5A

0.4

fPWF

PWM Mode Switching

Frequency

RT = 82 kΩ

freq_sel[2:0] = 1XX

2.0

Frequency Accuracy

2.7 ≤ VDD1,2 ≤ 2.9

−6

RT = 82 kΩ

−9

tPULSE

Switch Pulse Minimum

Width

tSTARTUP

Startup Time

ICL_OUT

SW Pin Current Limit

±3

No Load

(2)

+6

25

800

%

ns

15

700

Ω

MHz

+9

500

(1)

0.7

ms

900

1000

mA

Limits in standard typeface are for TJ = +25°C. Limits in boldface type apply over the operating ambient temperature range (−40°C ≤ TA

≤ +85°C). Unless otherwise noted, specifications apply to Figure 2 with: VDD1 = VDD2 = VDDA = 2.8V, CVDD1 = CVDD2 = CVDDA = CVDDIO =

100 nF, COUT = CIN = 10 µF, CVREF = 100 nF, L1 = 4.7 µH and fBOOST = 2.0 MHz.

Low-ESR Surface-Mount Ceramic Capacitors are used in setting electrical characteristics.

Boost Standby Mode

User can set the boost converter to STANDBY mode by writing the register bit EN_BOOST low when there is no

load to avoid idle current consumption. When EN_BOOST is written high, the converter starts in PFM (Pulse

Frequency Modulation) mode for 10 ms and then goes to PWM (Pulse Width Modulation ) mode. All RGB

outputs are off during the 10 ms delay.

Boost Output Voltage Control

User can control the boost output voltage by eight-bit boost output voltage register according to the following

table.

BOOST[7:0]

Register 0D'h

14

BOOST Output Voltage

(typical)

Binary

Hex

0000 0000

00

4.10

0000 0001

01

4.25

0000 0011

03

4.40

0000 0111

07

4.55

0000 1111

0F

4.70

0001 1111

1F

4.85

0011 1111

3F

5.00 Default

0111 1111

7F

5.15

1111 1111

FF

5.30

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

Boost Frequency Control

The register ‘boost frequency’ has address 0C’h. The default value after reset is 07’h. ‘x’ means don’t care.

FREQ_SEL[2:0]

Frequency

1xx

2.00 MHz

01x

1.67 MHz

001

1.00 MHz

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

15

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

Boost Converter Typical Performance Characteristics

VIN = 3.6V, VOUT = 5.0V if not otherwise stated.

16

Boost Converter Efficiency

Boost Frequency

vs

RT Resistor

Figure 13.

Figure 14.

Battery Current

vs

Voltage

Battery Current

vs

Voltage

Figure 15.

Figure 16.

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

Boost Converter Typical Performance Characteristics (continued)

VIN = 3.6V, VOUT = 5.0V if not otherwise stated.

Boost Startup with No Load

(5V/DIV)

VSWITCH

ICOIL

100 mA

AVERAGE

(100 mA/DIV)

VOUT = 5.0V

(10 mV/DIV)

Boost Typical Waveforms at 100 mA Load

TIME (200 ns/DIV)

Figure 17.

Figure 18.

Boost Line Regulation

Boost Load Transient Response, 50 mA to 100 mA

Figure 19.

Figure 20.

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

17

�LP3950

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

www.ti.com

RGB LED Pattern Generator

The LP3950 RGB outputs can be controlled either with audio synchronization or with RGB pattern generator.

The pattern generator of LP3950 drives three independently controlled LED outputs (for example, R1, G1 and

B1). The functionality is similar compared to RGB functionality of LP3936 and LP3933.

The output of RGB pattern generator can be selected to drive RGB1 (R1-G1-B1), RGB2 (R2-G2-B2) or RGB1

and RGB2 (R1&R2 – G1&G2 – B1&B2) outputs.

Programmable Pattern Mode

User has control over the following parameters separately for each LED:

ON and OFF (start and stop time in blinking cycle)

DUTY (PWM brightness control)

SLOPE (dimming slope)

ENABLE (output enable control)

The main blinking cycle is controlled with three-bit CYCLE control (0.25 / 0.5 / 1.0 / 2.0 / 4.0s).

LED

brightness

ON[3:0]

OFF[3:0]

SLOPE[3:0]

Duty increases

DUTY[3:0]

Duty constant

SLOPE[3:0]

Duty decreases

PWM

current

pulses

Blinking period

Figure 21. RGB PWM Operating Principle

RGB_START is the master control for the whole RGB function. The internal PWM and blinking control can be

disabled by setting the RGB_PWM control LOW. In this case the individual enable controls can be used to switch

outputs on and off. PWM_EN input can be used for external hardware PWM control.

In the normal PWM mode the R, G and B switches are controlled in 3 phases (one phase per driver). During

each phase the peak current set by an external ballast resistor is driven through the LED for the time defined by

DUTY setting (0 µs to 50 µs). As a time averaged current this means 0% to 33% of the peak current. The PWM

period is 150 µs and the pulse frequency is 6.67 kHz in normal mode.

R1

1111

G1

0110

B1

1100

3

1

2

3

150 Ps /6.7 kHz

1

2

Combined PWM cycle

Figure 22. Normal Mode PWM Waveforms at Different Duty Settings

In the FLASH mode all the outputs are controlled in one phase and the PWM period is 50 µs. The time averaged

FLASH mode current is three times the normal mode current at the same DUTY value.

18

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

Product Folder Links: LP3950

�LP3950

www.ti.com

SNVS331C – NOVEMBER 2004 – REVISED APRIL 2013

ON