LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

Advanced Lighting Management Unit

Check for Samples: LP3954

FEATURES

DESCRIPTION

•

•

LP3954 is an advanced lighting management unit for

handheld devices. It drives any phone lights including

display backlights, RGB, keypad and camera flash

LEDs. The boost DC-DC converter drives high

current loads with high efficiency. White LED

backlight drivers are high efficiency low voltage

structures with excellent matching and automatic fade

in/ fade out function. The new stand-alone command

based RGB controller is feature rich and easy to

configure. Built-in audio synchronization feature

allows user to synchronize the color LEDs to audio

input. Integrated high current driver can drive camera

flash LED or motor/vibra. Internal ADC can be used

for ambient light or temperature sensing. The flexible

SPI/I2C interface allows easy control of LP3954.

Small DSBGA package together with minimum

number of external components is a best fit for

handheld devices.

1

2

•

•

•

•

•

•

•

•

Audio Synchronization for Color/RGB LEDs

Command Based PWM Controlled RGB LED

Drivers

High Current Driver for Flash LED With Built-in

Timing

4+2 or 6 Low Voltage Constant Current White

LED Drivers With Orogrammable 8-Bit

Adjustment (0…25mA/LED)

High Efficiency Boost DC-DC Converter

SPI / I2C Compatible Interface

Possibility for External PWM Dimming Control

Possibility for Clock Synchronization for RGB

Timing

Ambient Light and Temperature Sensing

Possibility

Small Package – DSBGA, 3.0 x 3.0 x 0.6mm

APPLICATIONS

•

•

Cellular Phones

PDAs, MP3 players

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2005–2013, Texas Instruments Incorporated

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

Typical Application

+

CIN

CVDD

-

10 PF

100 nF

CVDDA

1 éF

BATTERY

CREF

D1

L1 4.7 PH

SW

FB

COUT

IMAX = 300...400 mA

10 PF

VOUT = 4...5.3V

VDD1

VDD2

VDDA

WLED1

MAIN

BACKLIGHT

0...25 mA/LED

WLED2

VREF

100 nF

WLED3

RRGB

IRGB

WLED4

RRT

IRT

SO

SUB

BACKLIGHT

0...25 mA/LED

WLED5

SI

WLED6

SCK/SCL

MCU

SS/SDA

SYNC/PWM

LP3954

R1

VDDIO

CVDDIO

RGB1

Up to 40 mA/LED

G1

IF_SEL

100 nF

B1

EN_FLASH

CAMERA

R2

TEMP SENSOR

RGB2

Up to 40 mA/LED

G2

or

B2

ASE

LIGHT

SENSOR

FLASH

Up to 300 mA

FLASH

or

AUDIO INPUT

GNDs

2

IFLASH

RFLASH

or

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

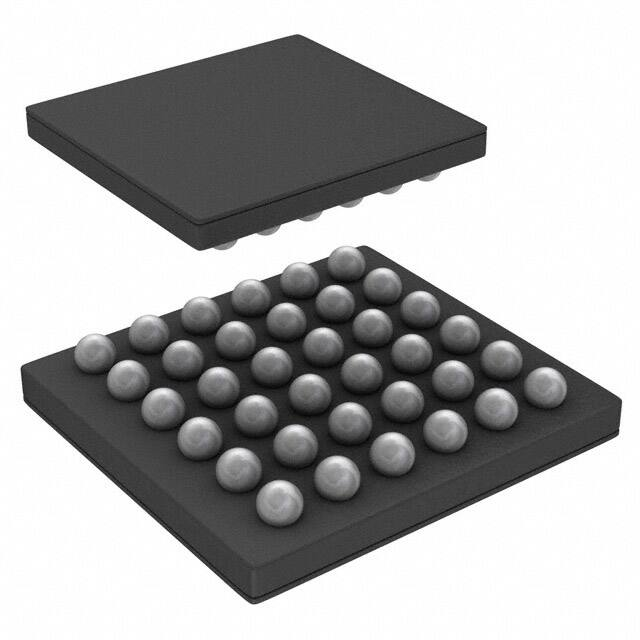

Connection Diagrams

DSBGA Package, 3.0 x 3.0 x 0.6mm, 0.5mm pitch Package Number YZR0036AAA or

DSBGA Package, 3.0 x 3.0 x 0.65mm, 0.5mm pitch Package Number YPG0036AAA

6

6

B1

G1

R1

FLASH

FB

SW

SW

FB

FLASH

R1

G1

B1

5

GND_

RGB

IRGB

SS/SDA

VDDIO

GND

GND_

SW

GND_

SW

GND

VDDIO

SS/

SDA

IRGB

GND_

RGB

5

4

R2

SO

SI

SYNC_

PWM

IFLASH

GND_

WLED

GND_

WLED

IFLASH

SYNC_

PWM

SI

SO

R2

4

3

G2

SCK/

SCL

FLASH

_EN

VDD1

WLED

6

WLED

5

WLED

5

WLED

6

VDD1

FLASH

_EN

SCK/

SCL

G2

3

2

B2

IF_SEL

IRT

ASE

WLED

4

WLED

3

WLED

3

WLED

4

ASE

IRT

IF_SEL

B2

2

1

VDD2

VDDA

VREF

GNDA

WLED

2

WLED

1

WLED

1

WLED

2

GNDA

VREF

VDDA

VDD2

1

B

C

D

E

F

E

D

C

A

F

TOP VIEW

B

A

BOTTOM VIEW

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

3

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

Table 1. Pin Descriptions

4

Pin No.

Name

Type

6F

SW

Output

Description

Boost Converter Power Switch

6E

FB

Input

Boost Converter Feedback

6D

FLASH

Output

High Current Flash Output

6C

R1

Output

Red LED 1 Output

6B

G1

Output

Green LED 1 Output

6A

B1

Output

Blue LED 1 Output

5F

GND_SW

Ground

Power Switch Ground

5E

GND

Ground

Ground

Supply Voltage for Input/output Buffers and Drivers

5D

VDDIO

Power

5C

SS/SDA

Logic Input/Output

Slave Select (SPI), Serial Data In/Out (I2C)

5B

IRGB

Input

Bias Current Set Resistor for RGB Drivers

5A

GND_RGB

Ground

Ground for RGB Currents

4F

GND_WLED

Ground

Ground for WLED Currents

4E

IFLASH

Input

4D

SYNC_PWM

Logic Input

External PWM Control for LEDs or External Clock for RGB Sync

4C

SI

Logic Input

Serial Input (SPI), Address Select (I2C)

4B

SO

Logic Output

4A

R2

Output

Red LED 2 output

High Current Flash Current Set Resistor

Serial Data Out (SPI)

3F

WLED5

Output

White LED 5 output

3E

WLED6

Output

White LED 6 output

3D

VDD1

Power

Supply voltage

3C

EN_FLASH

Logic Input

Enable for High Current Flash

3B

SCK/SCL

Logic Input

Clock (SPI/I2C)

3A

G2

Output

Green LED 2 Output

2F

WLED3

Output

White LED 3 output

White LED 4 output

2E

WLED4

Output

2D

ASE

Input

Audio Synchronization Input

2C

IRT

Input

Oscillator Frequency Resistor

2B

IF_SEL

Logic Input

2A

B2

Output

Blue LED 2 Output

1F

WLED1

Output

White LED 1 Output

Interface (SPI or I2C compatible) Selection (IF_SEL = 1 for SPI)

1E

WLED2

Output

White LED 2 Output

1D

GNDA

Ground

Ground for Analog Circuitry

1C

VREF

Output

Reference Voltage

1B

VDDA

Power

Internal LDO Output

1A

VDD2

Power

Supply Voltage

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1)

(2) (3)

V (SW, FB, R1-2, G1-2, B1-2, FLASH, WLED1-6) (4)

(5)

-0.3V to +7.2V

VDD1, VDD2, VDD_IO, VDDA

-0.3V to +6.0V

Voltage on ASE, IRT, IFLASH, IRGB, VREF

-0.3V to VDD1+0.3V with 6.0V max

Voltage on Logic Pins

-0.3V to VDD_IO +0.3V with 6.0V max

V(all other pins): Voltage to GND

-0.3V to 6.0V

I (VREF)

10µA

I(R1, G1, B1, R2, G2, B2)

100mA

I(FLASH) (6)

400mA

Continuous Power Dissipation (7)

Internally Limited

Junction Temperature (TJ-MAX)

150°C

Storage Temperature Range

-65°C to +150°C

Maximum Lead Temperature (Soldering)

(8)

260ºC

ESD Rating, Human Body Model (9)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

2kV

Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under

which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits

and associated test conditions, see the Electrical Characteristics tables.

All voltages are with respect to the potential at the GND pins.

If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

Battery/Charger voltage should be above 6V no more than 10% of the operational lifetime.

Voltage tolerance of LP3954 above 6.0V relies on fact that VDD1 and VDD2 (2.8V) are available (ON) at all conditions. If VDD1 and VDD2

are not available (ON) at all conditions, TI does not ensure any parameters or reliability for this device.

The total load current of the boost converter in worst-case conditions should be limited to 300mA (min. input and max. output voltage).

Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at TJ=160°C (typ.) and

disengages at TJ=140°C (typ.).

For detailed soldering specifications and information, please refer to Application Note AN1112 : Micro SMD Wafer Level Chip Scale

Package SNVA009 or Application Note AN1412 : Micro SMDxt Wafer Level Chip Scale Package SNVA131.

The Human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. The machine model is a 200pF

capacitor discharged directly into each pin. MIL-STD-883 3015.7

Operating Ratings (1)

(2)

V (SW, FB, WLED1-6, R1-2, G1-2, B1-2, FLASH)

0 to 6.0V

VDD1,2 with external LDO

2.7 to 5.5V

VDD1,2 with internal LDO

3.0 to 5.5V

VDDA

2.7 to 2.9V

VDD_IO

1.65V to VDD1

Voltage on ASE

0.1V to VDDA –0.1V

Recommended Load Current

0mA to 300mA

Junction Temperature (TJ) Range

-30°C to +125°C

Ambient Temperature (TA) Range (3)

(1)

(2)

(3)

-30°C to +85°C

Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under

which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits

and associated test conditions, see the Electrical Characteristics tables.

All voltages are with respect to the potential at the GND pins.

In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may

have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP =

125°C), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the

part/package in the application (θJA), as given by the following equation: TA-MAX = TJ-MAX-OP – (θJA × PD-MAX).

Thermal Properties

Junction-to-Ambient Thermal Resistance(θJA), YZR0036AAA or YPG0036AAA Package (1)

(1)

60°C/W

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power

dissipation exists, special care must be paid to thermal dissipation issues in board design.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

5

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

Electrical Characteristics (1)

www.ti.com

(2)

Limits in standard typeface are for TJ = 25° C. Limits in boldface type apply over the operating ambient temperature range (30°C < TA < +85°C). Unless otherwise noted, specifications apply to the LP3954 Block Diagram with: VDD1 = VDD2 = 3.6V,

VDDIO = 2.8V, CVDD = CVDDIO = 100nF, COUT = CIN = 10µF, CVDDA = 1µF, CREF = 100nF, L1 = 4.7µH, RFLASH =1.2k, RRGB =5.6k

and RRT =82k (3).

Parameter

IVDD

IVDDIO

IEXT_LDO

VDDA

(1)

(2)

(3)

(4)

6

Test Conditions

Min

Typ

Max

Unit

1

8

µA

Standby supply current

(VDD1, VDD2)

NSTBY = L

SCK, SS, SI

No-boost supply current

(VDD1, VDD2)

NSTBY = H,

EN_BOOST = L

SCK, SS, SI

Audio sync and LEDs OFF

400

µA

No-load supply current

(VDD1, VDD2)

NSTBY = H,

EN_BOOST = H

SCK, SS, SI

Audio sync and LEDs OFF

Autoload OFF

1

mA

RGB drivers

(VDD1, VDD2)

CC mode at R1, G1, B1 and R2, G2,

B2 set to 15mA

150

SW mode

150

WLED drivers

(VDD1, VDD2)

4+2 banks IOUT/LED 25mA

500

µA

Audio synchronization

(VDD1, VDD2)

Audio sync ON

VDD1,2 = 2.8V

390

µA

VDD1,2 = 3.6V

700

Flash

(VDD1, VDD2)

I(RFLASH)=1mA

Peak current during flash

VDDIO Standby Supply current

NSTBY = L

SCK, SS, SI = H

VDDIO supply current

1MHz SCK frequency in SPI mode,

CL = 50pF at SO pin

External LDO output current

(VDD1, VDD2, VDDA)

7V tolerant application only

IBOOST = 300mA

Output voltage of internal LDO

for analog parts

(4)

µA

2

mA

1

20

µA

6.5

2.72

-3

2.80

µA

mA

2.88

V

+3

%

All voltages are with respect to the potential at the GND pins.

Min and Max limits are ensured by design, test, or statistical analysis. Typical numbers are not ensured, but do represent the most likely

norm.

Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

VDDA output is not recommended for external use.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

DETAILED DESCRIPTION

Block Diagram

L1

4.7 µH

IMAX = 300...400 mA

VOUT = 4...5.3 V

D1

SW

+

-

CVDD

CIN

10 µF 100 nF

COUT

10 µF

FB

VDD1

VDD2

Logic supply

BG

PWM

Li-Ion

Battery

Or

Charger

VDDA

LDO

POR

GND_SW

VREF

BOOST

REF

CVDDA

1 µF

THSD

WLED1

CREF

100 nF

8-Bit

IDAC

WLED2

IRGB

BIAS

OSC

D

IRT

WLED3

A

MAIN

BACKLIGHT

0...25 mA/LED

WLED4

GND_WLED

RRGB

RRT

8-Bit

IDAC

SO

SS/SDA

IF_SEL

SYNC/PWM

VDDIO

INTERFACE

MCU

WLED6

D

CONTROL

SI

SCK/SCL

WLED5

A

SPI

I2C

R1

RGB1

Up to

40 mA/LED

G1

OUTPUT SELECTOR

CVDDIO

100 nF

SINGLE ENDED

ANALOG

AUDIO

SUB

BACKLIGHT

0...25 mA/LED

COMMAND

BASED

PATTERN

GENERATOR

B1

R2

RGB2

Up to

40 mA/LED

G2

ASE

B2

AUDIO SYNC

GND_RGB

FLASH

CAMERA

EN_FLASH

FLASH

Up to 300 mA

FLASH

CT

CTRL

RL

FLASH

LOGIC

IFLASH

GNDA

GND

RFLASH

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

7

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

Modes of Operation

RESET: In the RESET mode all the internal registers are reset to the default values and the chip goes to

STANDBY mode after reset. NSTBY control bit is low after reset by default. Reset is entered always if

Reset Register is written or internal Power On Reset is active. There is no dedicated Reset pin available.

LP3954 can be reset by writing any data to Reset Register in address 60H. Power On Reset (POR) will

activate during the chip startup or when the supply voltage VDD2 falls below 1.5V. Once VDD2 rises

above 1.5V, POR will inactivate and the chip will continue to the STANDBY mode.

STANDBY: The STANDBY mode is entered if the register bit NSTBY is LOW. This is the low power

consumption mode, when all circuit functions are disabled. Registers can be written in this mode and the

control bits are effective immediately after power up.

STARTUP: When NSTBY bit is written high, the INTERNAL STARTUP SEQUENCE powers up all the needed

internal blocks (Vref, Bias, Oscillator etc..). To ensure the correct oscillator initialization, a 10ms delay is

generated by the internal state-machine. If the chip temperature rises too high, the Thermal Shutdown

(THSD) disables the chip operation and STARTUP mode is entered until no thermal shutdown event is

present.

BOOST STARTUP: Soft start for boost output is generated in the BOOST STARTUP mode. The boost output is

raised in PFM mode during the 10ms delay generated by the state-machine. The Boost startup is entered

from Internal Startup Sequence if EN_BOOST is HIGH or from Normal mode when EN_BOOST is written

HIGH. During the 10ms Boost Startup time all LED outputs are switched off to ensure smooth start-up.

NORMAL: During NORMAL mode the user controls the chip using the Control Registers. The registers can be

written in any sequence and any number of bits can be altered in a register in one write

RESET

Reset Register write

POR = L

or POR = H

STANDBY

NSTBY = H

NSTBY = L

INTERNAL

STARTUP

SEQUENCE

VREF = 95% OK*

THSD = H

~10 ms Delay

EN_BOOST = H*

EN_BOOST = L*

BOOST STARTUP

EN_BOOST

rising edge*

~10 ms Delay

NORMAL MODE

* THSD = L

Figure 1. Modes of Operation

8

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

Magnetic Boost DC/DC Converter

The LP3954 Boost DC/DC Converter generates a 4.0 – 5.3V voltage for the LEDs from single Li-Ion battery

(3V…4.5V). The output voltage is controlled with an 8-bit register in 9 steps. The converter is a magnetic

switching PWM mode DC/DC converter with a current limit. The converter has three options for switching

frequency, 1MHz, 1.67MHz and 2MHz (default), when timing resistor RT is 82kohm. Timing resistor defines the

internal oscillator frequency and thus directly affects boost frequency and all circuit's internally generated timing

(RGB, Flash, WLED fading).

The LP3954 Boost Converter uses pulse-skipping elimination to stabilize the noise spectrum. Even with light load

or no load a minimum length current pulse is fed to the inductor. An active load is used to remove the excess

charge from the output capacitor at very light loads. At very light load and when input and output voltages are

very close to each other, the pulse skipping is not completely eliminated. Output voltage should be at least 0.5V

higher than input voltage to avoid pulse skipping. Reducing the switching frequency will also reduce the required

voltage difference.

Active load can be disabled with the en_autoload bit. Disabling will increase the efficiency at light loads, but the

downside is that pulse skipping will occur. The Boost Converter should be stopped when there is no load to

minimise the current consumption.

The topology of the magnetic boost converter is called CPM control, current programmed mode, where the

inductor current is measured and controlled with the feedback. The user can program the output voltage of the

boost converter. The output voltage control changes the resistor divider in the feedback loop.

The following figure shows the boost topology with the protection circuitry. Four different protection schemes are

implemented:

1. Over voltage protection, limits the maximum output voltage

– Keeps the output below breakdown voltage.

– Prevents boost operation if battery voltage is much higher than desired output.

2. Over current protection, limits the maximum inductor current

– Voltage over switching NMOS is monitored; too high voltages turn the switch off.

3. Feedback break protection. Prevents uncontrolled operation if FB pin gets disconnected.

4. Duty cycle limiting, done with digital control.

2 MHz clock

VIN

Duty control

VOUT

SW

FBNCCOMP

FB

+

-

R

S

R

OVPCOMP

SWITCH

+

-

R

RESETCOMP

+

ERRORAMP

SLOPER

+

-

+

-

R

+

-

R

OLPCOMP

ACTIVE

LOAD

LOOPC

Figure 2. Boost Converter Topology

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

9

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

MAGNETIC BOOST DC/DC CONVERTER ELECTRICAL CHARACTERISTICS

Parameter

Test Conditions

Min

Typ

Max

3.0V ≤ VIN

VOUT = 5V

0

300

3.0V ≤ VIN

VOUT = 4V

0

400

Output Voltage Accuracy

(FB Pin)

3.0V ≤ VIN ≤ VOUT - 0.5

VOUT = 5.0V

−5

+5

Output Voltage

(FB Pin)

1 mA ≤ ILOAD ≤ 300 mA

VIN > 5V + V(SCHOTTKY)

RDSON

Switch ON Resistance

VDD1,2 = 2.8V, ISW = 0.5A

fPWF

PWM Mode Switching Frequency

RT = 82 kΩ

freq_sel[2:0] = 1XX

Frequency Accuracy

2.7 ≤ VDDA ≤ 2.9

−6

RT = 82 kΩ

−9

ILOAD

Load Current

VOUT

Unit

mA

tPULSE

Switch Pulse Minimum Width

no load

tSTARTUP

Startup Time

Boost startup from STANDBY

ISW_MAX

SW Pin Current Limit

VIN–V(SCHOTT

%

V

KY)

0.4

0.8

2

±3

MHz

+6

+9

25

550

800

%

ns

10

700

Ω

ms

900

950

mA

BOOST STANDBY MODE

User can stop the Boost Converter operation by writing the Enables register bit EN_BOOST low. When

EN_BOOST is written high, the converter starts for 10ms in PFM mode and then goes to PWM mode.

BOOST OUTPUT VOLTAGE CONTROL

User can control the boost output voltage by boost output 8-bit register.

Boost Output [7:0]

Register 0DH

10

Boost Output

Voltage (typical)

Bin

Hex

0000 0000

00

4.00

0000 0001

01

4.25

0000 0011

03

4.40

0000 0111

07

4.55

0000 1111

0F

4.70

0001 1111

1F

4.85

0011 1111

3F

5.00 Default

0111 1111

7F

5.15

1111 1111

FF

5.30

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

Figure 3. Boost Output Voltage Control

BOOST FREQUENCY CONTROL

(1)

freq_sel[2:0] (1)

frequency

1XX

2.00 MHz

01X

1.67 MHz

001

1.00 MHz

Register ‘boost freq’ (address 0EH). Register default value after

reset is 07H.

Boost Converter Typical Performance Characteristics

Vin = 3.6V, Vout = 5.0V if not otherwise stated

Boost Typical Waveforms at 100mA Load

(5V/DIV)

VSWITCH

ICOIL

100 mA

AVERAGE

(100 mA/DIV)

VOUT = 5.0V

(10 mV/DIV)

Boost Converter Efficiency

TIME (200 ns/DIV)

Figure 4.

Figure 5.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

11

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

Vin = 3.6V, Vout = 5.0V if not otherwise stated

Battery Current vs Voltage

Battery Current vs Voltage

Figure 6.

Figure 7.

Boost Line Regulation

Boost Startup with No Load

Figure 8.

Figure 9.

Boost Load Transient, 50 mA–100 mA

Figure 10.

12

Boost Switching Frequency

Figure 11.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

Vin = 3.6V, Vout = 5.0V if not otherwise stated

Efficiency At Low Load vs Autoload

5.2

90

5.0

80

4.8

70

EFFICIENCY (%)

OUTPUT VOLTAGE (V)

Output Voltage vs Load Current

4.6

VIN = 3V

4.4

f = 2 MHz

L - TDK VLF0410 4.7 PH

CIN = COUT = 10 PF

4.2

60

50

40

Autoload ON

Autoload OFF

4.0

30

3.8

20

3.6

0

100

200

300

400

0

500

5

10

15

20

25

30

LOAD CURRENT (mA)

OUTPUT CURRENT (mA)

Figure 12.

Figure 13.

Functionality of Color LED Outputs (R1, G1, B1; R2, G2, B2)

LP3954 has 2 sets of RGB/color LED outputs. Both sets have 3 outputs and the sets can be controlled in 4

different ways:

1. Command based pattern generator control (internal PWM)

2. Audio synchronization control

3. Direct ON/OFF control

4. External PWM control

By using command based pattern generator user can program any kind of color effect patterns. LED intensity,

blinking cycles and slopes are independently controlled with 8 16-bit commands. Also real time commands are

possible as well as loops and step by step control. If analog audio is available on system, the user can use

audio synchronization for synchronizing LED blinking to the music. The different modes together with the

various sub modes generate very colorful and interesting lighting effects. Direct ON/OFF control is mainly for

switching on and off LEDs. External PWM control is for applications where external PWM signal is available

and required to control the color LEDs. PWM signal can be connected to any color LED separately as shown

later.

COLOR LED CONTROL MODE SELECTION

The RGB_SEL[1:0] bits in the Enables register (08H) control the output modes for RGB1 (R1, G1, B1) and RGB2

(R2, G2, B2) outputs. The following table shows the RGB_SEL functionality.

Audio Sync Connected To

Command Based Pattern Generator

Connected To

00

none

RGB1 & RGB2

01

RGB1

RGB2

10

RGB2

RGB1

11

RGB1 & RGB2

none

RGB_SEL[1:0]

RGB Control register (00H) has control bits for direct on/off control of all color LEDs. Note that the LEDs have

to be turned on in order to control them with audio synchronization or pattern generator.

The external PWM signal controls any LED depending on the control register setup. The controls are in the Ext.

PWM Control register (address 07H) except the FLASH control in HC_Flash (10H) register as follows:

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

13

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

Ext. PWM Control (1)

wled1-4_pwm

bit 7

PWM controls WLED 1-4

wled5-6_pwm

bit 6

PWM controls WLED 5-6

r1_pwm

bit 5

PWM controls R1 output

g1_pwm

bit 4

PWM controls G1 output

b1_pwm

bit 3

PWM controls B1 output

r2_pwm

bit 2

PWM controls R2 output

g2_pwm

bit 1

PWM controls G2 output

b2_pwm

bit 0

PWM controls B2 output

hc_pwm

bit 5

HC_Flash

(1)

PWM controls high current flash

Note: If DISPL=1, wled1-4pwm controls WLED1-6

Note: Maximum external PWM frequency is 1kHz. If during the

external PWM control the internal PWM is on the result will be

product of both functions.

CURRENT CONTROL OF COLOR LED OUTPUTS (R1, R2, G1, G2, B1, B2)

Both RGB output sets can be separately controlled as constant current sinks or as switches. This is done using

cc_rgb1/2 bits in the RGB control register. In constant current mode one or both RGB output sets are controlled

with constant current sinks (no external ballast resistors required). The maximum output current for both drivers

is set by one external resistor RRGB. User can decrease the maximum current for an individual LED driver by

programming as shown later.

The maximum current for all RGB drivers is set with RRGB. The equation for calculating the maximum current is

IMAX = 100 ×1.23V / (RRGB + 50Ω)

(1)

where

IMAX - maximum RGB current in any RGB output in constant current mode

1.23V - reference voltage

100 - internal current mirror multiplier

RRGB- resistor value in Ohms

50Ω - internal resistor in the IRGB input

For example if 22mA is required for maximum RGB current RRGB equals to

RRGB = 100 × 1.23V / IMAX –50Ω = 123V / 0.022A –50Ω = 5.54kΩ

(2)

Each individual RGB output has a separate maximum current programming. The control bits are in registers

RGB1 max current and RGB2 max current (12H and 13H) and programming is shown in table below. The

default value after reset is 00.

IR1[1:0], IG1[1:0],

IB1[1:0], IR2[1:0],

IG2[1:0], IB2[1:0]

Maximum

Current/Output

00

0.25 × IMAX

01

0.50 × IMAX

10

0.75 × IMAX

11

1.00 × IMAX

SWITCH MODE

The switch mode is used if there is a need to connect parallel LEDs to output or if the RGB output current needs

to be increased.

Please note that the switch mode requires an external ballast resistors at each output to limit the LED current.

The switch/current mode and on/off controls for RGB are in the RGB_ctrl register (00H) as follows:

14

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

Table 2. RGB_ctrl Register (00H)

CC_RGB1

bit7

CC_RGB2

bit6

r1sw

bit5

g1sw

bit4

b1sw

bit3

r2sw

bit2

g2sw

bit1

b2sw

bit0

1

R1, G1 and B1 are switches → limit current with ballast resistor

0

R1, G1 and B1 are constant current sinks, current limited internally

1

R2, G2 and B2 are switches → limit current with ballast resistor

0

R2, G2 and B2 are constant current sinks, current limited internally

1

R1 is on

0

R1 is off

1

G1 is on

0

G1 is off

1

B1 is on

0

B1 is off

1

R2 is on

0

R2 is off

1

G2 is on

0

G2 is off

1

B2 is on

0

B2 is off

VOUT

R1

R1

RR2

R1

control

G1

VOUT

RR1

R1

control

RG1

G1

RG2

G1

control

G1

control

B1

RB1

B1

RB2

B1

control

B1

control

RGB1 output as switch (SW)

RGB1 output as a constant

current sink (CC)

Command Based Pattern Generator for Color LEDs

The LP3954 has a unique stand-alone command based pattern generator with 8 user controllable 16-bit wide

commands. Since write registers are 8-bit long one command requires 2 write cycles. Each command has

intensity level for each LED, command execution time (CET) and transition time (TT). The command structure is

shown in following two figures.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

15

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

16 bits

RED[2:0]

GREEN[2:0]

CET [3:0]

TT[2:0]

BLUE[2:0]

16 bits

ADDESS[7:0]

RED[2:0]

GREEN[2:0]

CET[3:2]

16 bits

CET[1:0]

NEXT ADDESS[7:0]

BLUE[2:0]

TT[2:0]

COMMAND REGISTER WITH 8 COMMANDS

COMMAND 1

COMMAND 2

COMMAND 3

COMMAND 4

COMMAND 5

ADDRESS 50H

R2

R1

R0

ADDRESS 51H

CET1

CET0

B2

ADDRESS 52H

R2

R1

R0

ADDRESS 53H

CET1

CET0

B2

G2

G1

G0

CET3

CET2

B1

B0

TT2

TT1

TT0

G2

G1

G0

CET3

CET2

B1

B0

TT2

TT1

TT0

CET2

ADDRESS 54H

R2

R1

R0

G2

G1

G0

CET3

ADDRESS 55H

CET1

CET0

B2

B1

B0

TT2

TT1

TT0

ADDRESS 56H

R2

R1

R0

G2

G1

G0

CET3

CET2

ADDRESS 57H

CET1

CET0

B2

B1

B0

TT2

TT1

TT0

CET2

ADDRESS 58H

R2

R1

R0

G2

G1

G0

CET3

ADDRESS 59H

CET1

CET0

B2

B1

B0

TT2

TT1

TT0

COMMAND 6

ADDRESS 5AH

R2

R1

R0

G2

G1

G0

CET3

CET2

ADDRESS 5BH

CET1

CET0

B2

B1

B0

TT2

TT1

TT0

COMMAND 7

ADDRESS 5CH

R2

R1

R0

G2

G1

G0

CET3

CET2

ADDRESS 5DH

CET1

CET0

B2

B1

B0

TT2

TT1

TT0

COMMAND 8

ADDRESS 5EH

R2

R1

R0

G2

G1

G0

CET3

CET2

ADDRESS 5FH

CET1

CET0

B2

B1

B0

TT2

TT1

TT0

COLOR INTENSITY CONTROL

Each color, Red, Green and Blue, has 3-bit intensity levels. The level control is logarithmic. 2 logarithmic curves

are available. The LOG bit in Pattern_gen_ctrl register (11H) defines the curve used. The values for both

logarithmic curves are shown in following table.

R[2:0], G[2:0],

B[2:0]

16

CURRENT

[% × IMAX(COLOR)]

LOG=0

LOG=1

000

0

0

001

7

1

010

14

2

011

21

4

100

32

10

101

46

21

110

71

46

111

100

100

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

100

LOG=0

% IMAX

80

LOG=1

60

40

20

0

000

001

010

011

100

101

111

110

R[2:0], G[2:0], B[2:0]

COMMAND EXECUTION TIME (CET) AND TRANSITION TIME (TT)

The command execution CET time is the duration of one single command. Command execution times CET are

defined as follows, when RT=82k:

CET [3:0]

CET duration, ms

0000

197

0001

393

0010

590

0011

786

0100

983

0101

1180

0110

1376

0111

1573

1000

1769

1001

1966

1010

2163

1011

2359

1100

2556

1101

2753

1110

2949

1111

3146

Transition time TT is duration of transition from the previous RGB value to programmed new value. Transition

times TT are defined as follows:

TT [2:0]

Transition time, ms

000

0

001

55

010

110

011

221

100

442

101

885

110

1770

111

3539

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

17

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

The figure below shows an example of RGB CET and TT times.

CET2

COMMAND EXECUTION TIME = CET1

CET3

TT2

TRANSITION TIME = TT1

TT3

BLUE

GREEN

RED

TT < CET

The command execution time also may be less than the transition time – the figure below illuminates this case.

TRANSITION TIME = TT1

COMMAND EXECUTION TIME = CET1

CET3

CET2

TT2

TT3

Target values

BLUE

GREEN

RED

TT1 > CET1

TT2 < CET2

TT3 < CET3

LOOP CONTROL

Pattern generator commands can be looped using the LOOP bit (D1) in Pattern gen ctrl register (11H). If

LOOP=1 the program will be looped from the command 8 register or if there is 0000 0000 and 0000 0000 in one

command register. The loop will start from command 1 and continue until stopped by writing rgb_start=0 or

loop=0. The example of loop is shown in following figure:

IF 0000 0000 and 0000 0000 then Æ LOOP

LOOP=1

ADDRESS 50H

COMMAND 1

ADDRESS 51H

ADDRESS 52H

COMMAND 2

ADDRESS 53H

ADDRESS 54H

0

0

0

0

0

0

0

0

ADDRESS 55H

0

0

0

0

0

0

0

0

COMMAND 3

18

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

SINGLE PROGRAM

If control bit LOOP=0 the program will start from Command 1 and run to either last command or to empty “0000

0000 / 0000 0000” command.

IF 0000 0000 and 0000 0000 then Æ STOP

LOOP=0

ADDRESS 50H

start

COMMAND 1

ADDRESS 51H

ADDRESS 52H

COMMAND 2

ADDRESS 53H

stop

ADDRESS 54H

0

0

0

0

0

0

0

0

ADDRESS 55H

0

0

0

0

0

0

0

0

COMMAND 3

The LEDs maintain the brightness of the last command when the single program stops. Changes in command

register will not be effective in this phase. The RGB_START bit has to be toggled off and on to make changes

effective.

START BIT

Pattern_gen_ctrl register’s RGB_START bit will enable command execution starting from Command 1.

Pattern gen ctrl register (11H)

rgb_start

Bit 2

0 – Pattern generator disabled

1 – execution pattern starting from command 1

loop

Bit 1

0 – pattern generator loop disabled (single pattern)

1 – pattern generator loop enabled (execute until stopped)

log

Bit 0

0 – color intensity mode 0

1 – color intensity mode 1

HARDWARE ON/OFF CONTROL AND DIMMING

PWM_LED input can be used as direct ON/OFF control or PWM dimming control for selected RGB outputs or

the WLED groups. PWM_LED control can be enabled with the control bits in the Ext. PWM Control register.

Audio Synchronization

The color LEDs connected to RGB outputs can be synchronized to incoming audio with Audio Synchronization

feature. Audio Sync has 2 modes. Amplitude mode synchronizes color LEDs based on input signal’s peak

amplitude. In the amplitude mode the user can select between 3 different amplitude mapping modes and 4

different speed configurations. The frequency mode synchronizes the color LEDs based on bass, middle and

treble amplitudes (= low pass, band pass and high pass filters). User can select between 2 different frequency

responses and 4 different speed configurations for best audio-visual user experience. Programmable gain and

AGC function are also available for adjustment of input signal amplitude to light response. The Audio Sync

functionality is described more closely below.

USING A DIGITAL PWM AUDIO SIGNAL AS AN AUDIO SYNCHRONIZATION SOURCE

If the input signal is a PWM signal, use a first or second order low pass filter to convert the digital PWM audio

signal into an analog waveform. There are two parameters that need to be known to get the filter to work

successfully: frequency of the PWM signal and the voltage level of the PWM signal. Suggested cut-off frequency

(-3dB) should be around 2 kHz to 4 kHz and the stop-band attenuation at sampling frequency should be around 48dB or better. Use a resistor divider to reduce the digital signal amplitude to meet the specification of the analog

audio input. Because a low-order low-pass filter attenuates the high-frequency components from audio signal,

MODE_CONTROL=[01] selection is recommended when frequency synchronization mode is enabled.

Application example 5 shows an example of a second order RC-filter for 29 kHz PWM signal with 3.3V

amplitude. Active filters, such as a Sallen-Key filter, may also be applied. An active filter gives better stop-band

attenuation and cut-off frequency can be higher than for a RC-filter.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

19

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

To make sure that the filter rolls off sufficiently quickly, connect your filter circuit to the audio input(s), turn on the

audio synchronization feature, set manual gain to maximum, apply the PWM signal to the filter input and keep an

eye on LEDs. If they are blinking without an audio signal (modulation), a sharper roll-off after the cut-off

frequency, more stop-band attenuation, or smaller amplitude of the PWM signal is required.

AUDIO SYNCHRONIZATION SIGNAL PATH

LP3954 audio synchronization is mainly done digitally and it consists of the following signal path blocks:

• Input Buffers

• AD Converter

• DC Remover

• Automatic Gain Control (AGC)

• Programmable Gain

• 3 Band Digital Filter

• Peak Detector

• Look-up Tables (LUT)

• Mode Selector

• Integrators

• PWM Generator

• Output Drivers

EN

SPEED

3 FILTERS

ASE

BUFFER

ADC

DC

REMOVER

MODE

HIGH / LOW

GAIN

LUT

INT

AGC

PEAK

DETECTOR

PW

M

LED

DRIVER

R

G

B

LUT

The digitized input signal has DC component that is removed by digital DC REMOVER (-3dB at 400Hz). Since

the light response of input audio signal is very much amplitude dependent the AGC adjusts the input signal to

suitable range automatically. User can disable AGC and the gain can be set manually with PROGRAMMABLE

GAIN. LP3954 has 2 audio synchronization modes: amplitude and frequency. For amplitude based

synchronization the PEAK DETECTION method is used. For frequency based synchronization 3 BAND FILTER

separates high pass, low pass and band bass signals. For both modes the predefined LUT is used to optimize

the audio visual effect. MODE SELECTOR selects the synchronization mode. Different response times to music

beat can be selected using INTEGRATOR speed variables. Finally PWM GENERATOR sets the driver FET duty

cycles.

INPUT SIGNAL TYPE AND BUFFERING

LP3954 supports single ended audio input as shown in the figure below. The electric parameters of the buffer are

described in the Audio Synch table. The buffer is rail-to-rail input operational amplifier connected as a voltage

follower. DC level of the input signal is set by a simple resistor divider

VDDA

1 M:

10 nF

ASE

1 M:

AGND

20

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

AUDIO SYNC ELECTRICAL PARAMETERS

Symbol

Parameter

Test Conditions

ZIN

Input Impedance of ASE

AIN

Audio Input Level Range (peak-to-peak)

Gain = 21dB

Min

Typ

250

500

Unit

kOhm

0.1

V

Gain = 0 dB

f3dB

Max

VDDA - 0.1

Crossover Frequencies (-3 dB)

Narrow Frequency Response

Wide Frequency Response

Low Pass

0.5

Band Pass

1.0 and

1.5

High Pass

2.0

Low Pass

1.0

Band Pass

2.0 and

3.0

High Pass

4.0

kHz

CONTROL OF AUDIO SYNCHRONIZATION

The following table describes the controls required for audio synchronization.

Audio_sync_CTRL1 (2AH)

Input signal gain control. Range 0...21 dB, step 3 dB:

GAIN_SEL[2:0]

Bits 7-5

[000] = 0 dB (default)

[011] = 9 dB

[110] = 18 dB

[001] = 3 dB

[100] = 12 dB

[111] = 21 dB

[010] = 6 dB

[101] = 15 dB

SYNC_MODE

Bit 4

Synchronization mode selector.

SYNCMODE = 0 → Amplitude Mode (default)

SYNCMODE = 1 → Frequency Mode

EN_AGC

Bit 3

Automatic Gain Control enable

1 = enabled

0 = disabled (Gain Select enabled) (default)

EN_SYNC

Bit 2

Audio synchronization enable

1 = Enabled

Note : If AGC is enabled, AGC gain starts from current GAIN_SEL gain value.

0 = Disabled (default)

INPUT_SEL[1:0]

Bits 1-0

[00] = Single ended input signal, ASE.

[01] = Temperature measurement

[10] = Ambient light measurement

[11] = No input (default)

EN_AVG

Bit 4

0 – average disabled (not applicable in audio synchronization mode)

1 – average enabled (not applicable in audio synchronization mode)

MODE_CTRL[1:0]

Bits 3-2

See below: Mode control

Bits 1-0

Sets the LEDs light response time to audio input.

[00] = FASTEST (default)

[01] = FAST

[10] = MEDIUM

[11] = SLOW

(For SLOW setting in amplitude mode fMAX=3.8Hz,

Frequency mode fMAX=7.6Hz)

Audio_sync_CTRL2 (2BH)

SPEED_CTRL[1:0]

MODE CONTROL IN FREQUENCY MODE

Mode control has two setups based on audio synchronization mode select: the frequency mode and the

amplitude mode. During the frequency mode user can select two filter options by MODE_CTRL as shown

below. User can select the filters based on the music type and light effect requirements. In the first mode the

frequency range extends to 8 kHz in the secont to 4 kHz.

The lowpass filter is used for the red, the bandpass filter for the blue and the hipass filter for the green LED.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

21

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

0

0

-10

-20

BANDPASS

LOWPASS

HIPASS

-20

-30

-30

-40

-40

dB

dB

-10

BANDPASS

LOWPASS

HIPASS

-50

-50

-60

-60

-70

-70

-80

-80

-90

-90

-100

-100

1.0

0

2.0

3.0

4.0

5.0

6.0

7.0

8.0

0.5

0

1.0

kHz

1.5

2.0

2.5

3.0

3.5

4.0

kHz

Figure 14. Higher frequency mode

MODE_CTRL = 00 and SYNC_MODE = 1

Figure 15. Lower frequency mode

MODE_CTRL = 01 and SYNC_MODE = 1

MODE CONTROL IN AMPLITUDE MODE

During the amplitude synchronization mode user can select between three different amplitude mappings by

using MODE_CTRL select. These three mapping option gives different light response. The modes are shown in

the tables below.

100

100

90

90

BLUE

RED

70

60

50

40

30

GREEN

RED

70

60

50

40

30

20

20

10

10

0

0

0

10 20 30 40 50 60 70 80 90 100

0

INPUT AMPLITUDE (%)

10 20 30 40 50 60 70 80 90 100

INPUT AMPLITUDE (%)

Figure 16. Non-overlapping mode

MODE_CTRL[1:0] = [01]

22

BLUE

80

INTENSITY (%)

INTENSITY (%)

80

GREEN

Figure 17. Partly overlapping mode

MODE_CTRL[1:0] = [00]

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

5.00

100

90

GREEN

PEAK INPUT SIGNAL VPP (V)

BLUE

INTENSITY (%)

80

70

60

50

40

30

20

RED

10

3.00

2.50

2.00

1.50

1.00

0.50

0.30

0.25

0.20

0.15

0.10

0.05

0

0

0

10 20 30 40 50 60 70 80 90 100

3

6

9

12

15

18

21

GAIN (dB)

INPUT AMPLITUDE (%)

Figure 18. Overlapping mode MODE_CTRL[1:0] =

[10]

Figure 19. Peak Input Signal Level

Range vs Gain Setting

RGB OUTPUT SYNCHRONIZATION TO EXTERNAL CLOCK

The RGB pattern generator and high current flash driver timing can be synchronized to external clock with

following configuration.

1. Set PWM_SYNC bit in Enables register to 1

2. Feed PWM_SYNC pin with 5 MHz clock

By this the internal 5 MHz clock is disabled from pattern generator and flash timing circuitry.

The external clock signal frequency will fully determine the timings related to RGB and Flash.

Note: The boost converter will use internal 5 MHz clock even if the external clock is available.

RGB Driver Typical Performance Characteristics

RGB DRIVER ELECTRICAL CHARACTERISTICS (R1, G1, B1, R2, G2, B2 OUTPUTS)

Parameter

Test Conditions

Min

Typ

Max

Unit

0.1

1

µA

ILEAKAGE

R1, G1, B1, R2, G2, B2 pin

leakage current

IMAX(RGB)

Maximum recommended sink

current (1)

CC mode

40

mA

SW mode

50

mA

Accuracy at 37mA

RRGB=3.3 kΩ ±1%, CC mode

Current mirror ratio

CC mode

RGB1 and RGB2 current

mismatch

IRGB=37mA, CC mode

RSW

Switch resistance

SW mode

ƒRGB

RGB switching frequency

Accuracy proportional to internal

clock freq.

If external SYNC 5MHz is in use

(1)

±5

%

1:100

±5

18.2

%

2.5

4

Ω

20

21.8

kHz

20

kHz

Note: RGB current should be limited as follows:

constant current mode – limit by external RRGB resistor;

switch mode – limit by external ballast resistors

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

23

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

Figure 20. Output Current vs Pin Voltage (Current

Sink Mode)

Figure 21. Pin Voltage vs Output Current (Switch

Mode)

Figure 22. Output Current vs RRGB (Current Sink Mode)

Single High Current Driver

LP3954 has internal constant current driver that is capable for driving high current mainly targeted for FLASH

LED in camera phone applications.

MAXIMUM CURRENT SETUP FOR FLASH

The user sets the maximum current of FLASH with RFLASH resistor based on following equation:

IMAX = 300 × 1.23V / (RFLASH + 50Ω),

(3)

where

Imax = maximum flash current in Amps (ie. 0.3A)

1.23V = reference voltage

300 = internal current mirror multiplier

RFLASH = Resistor value in Ohms

50Ω = Internal resistor in the IFLASH input

For example if 300mA is required for maximum flash current RFLASH equals to

RFLASH = 300 × 1.23V / IMAX – 50Ω = 369V / 0.3A – 50Ω = 1.18kΩ

24

Submit Documentation Feedback

(4)

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

CURRENT CONTROL FOR FLASH

To minimize the internal current consumption, the flash function has an enable bit EN_HCFLASH in the

HC_Flash register.

EN_HCFLASH

0

FLASH disabled, no extra current consumption through RFLASH

1

FLASH enabled, IFLASH set by HC_SW[1:0] (see below)

HC[1:0] bits in the HC_Flash register control the FLASH current as show in following table.

HC[1:0]

I(FLASH)

00

0.25 × IMAX(FLASH)

01

0.50 × IMAX(FLASH)

10

0.75 × IMAX(FLASH)

11

1.00 × IMAX(FLASH)

Figure 23 shows the internal structure for the FLASH driver.

LOUT

LED

1 mA

1 mA

1.23V

+

-

FLASH

up to 300 mA

RFLASH

IFLASH

(1.23V)

1 mA

Figure 23. Internal Structure of Flash Driver

FLASH TIMING

Flash output is turned on in lower current View finder mode when the EN_HCFLASH bit is written high. The

actual Flash at maximum current starts when the EN_FLASH i/o-pin goes high. The Flash length can be selected

from 3 pre-defined values or EN_FLASH pin pulse length can determine the length. The pulse length is

controlled by the FT_T[1:0] bits as show in the table below.

FL_T[1:0]

Flash Duration Typ

Current During View

Finder/Focusing

Current During FLASH

00

200ms

Set by HC[1:0]

HC[11] = IMAX(FLASH)

01

400ms

Set by HC[1:0]

HC[11] = IMAX(FLASH)

10

600ms

Set by HC[1:0]

HC[11] = IMAX(FLASH)

11

EN_FLASH on duration

Set by HC[1:0]

HC[11] = IMAX(FLASH)

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

25

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

Figure 24 shows the functionality of the built-in flash.

Current

VIEW FINDER / FOCUS

HIGH CURRENT

FLASH

HC[1:0] = 11

FL_T[1:0]

HC[1:0] = 10

HC[1:0] = 01

HC[11] = IMAX

HC[1:0] = 00

HC[1:0]

For mode Time

FL_T[1:0]=11

FLASH_EN input

EN_HCFLASH bit

Figure 24. Built-In Flash

HIGH CURRENT DRIVER ELECTRICAL CHARACTERISTICS

Parameter

Test Conditions

ILEAKAGE

FLASH pin leakage current

IMAX(FLASH)

Maximum Sink Current

Accuracy at 300 mA

Min

Typ

0.1

RFLASH=1.18 kΩ ±1%

±5

Current mirror ratio

Max

Unit

2

µA

400

mA

±10

%

1:300

Backlight Drivers

LP3954 has 2 independent backlight drivers. Both drivers are regulated constant current sinks. LED current for

both LED banks (WLED1…4 and WLED5…6) are controlled by 8-bit current mode DACs with 0.1 mA step.

WLED1…4 and WLED5…6 can be also controlled with one DAC for better matching allowing the use of larger

displays having up to 6 white LEDs in parallel.

Display configuration is controlled with DISPL bit as shown below.

DISPL

0

1

Configuration

Matching

Main display up to 4 LEDs

Good btw WLED1…4

Sub display up to 2 LEDs

Good btw WLED5…6

Large display up to 6 LEDs

Good btw WLED 1…6

Display backlight enables

EN_W1-4

EN_W5-6

26

1

WLED1-4 enabled

0

WLED1-4 disabled

1

WLED5-6 enabled

0

WLED5-6 disabled

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

WLED4

&

WLED3

External PWM

WLED1-4_pwm

WLED2

SNVS340D – JUNE 2005 – REVISED MARCH 2013

WLED1

www.ti.com

8-Bit IDAC

WLED1-4

WLED1-4[7:0]

EN_W1-4

WLED5-6[7:0]

&

WLED6

External PWM

WLED5-6_pwm

WLED5

Figure 25. Main Display up to 4 LEDs (WLED1…4)

8-Bit IDAC

WLED5-6

EN_W5-6

WLED1-4[7:0]

WLED6

WLED5

WLED4

WLED3

&

WLED2

External PWM

WLED1-4_pwm

WLED1

Figure 26. Sub Display Driver up to 2 LEDs (WLED5…6)

8-Bit IDAC

WLED1-4

EN_W1-4

Figure 27. Main Display up to 6 LEDs (WLED1…6) (DISPL=1)

BACKLIGHT DRIVER ELECTRICAL CHARACTERISTICS

Parameter

Test Conditions

Min

Typical

Max

Unit

21.3

25.5

29.4

mA

0.03

1

µA

12.8

14.78

mA

+16

%

IMAX

Maximum Sink Current

ILeakage

Leakage Current

VFB =5V

IWLED1

WLED1 Current tolerance

IWLED1 set to 12.8mA (80H)

IMatch1-4

Sink Current Matching

ISINK=13mA, Between WLED1…4

0.2

%

IMatch5-6

Sink Current Matching

ISINK=13mA, Between WLED5…6

0.2

%

IMatch1-6

Sink Current Matching

ISINK=13mA, Between WLED1…6

0.3

%

10.52

-18

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

27

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

ADJUSTMENT

WLED1-4[7:0]

WLED5-6[7:0]

Driver Current,

mA (typical)

0000 0000

0

0000 0001

0.1

0000 0010

0.2

0000 0011

0.3

…

…

…

…

1111 1101

25.3

1111 1110

25.4

1111 1111

25.5

30

25oC

WLED CURRENT (mA)

25

85oC

20

-40oC

15

10

5

0

0

0.05

0.10

0.15

0.20

0.25

0.30

WLED OUTPUT VOLTAGE (V)

Figure 28. WLED Output Current vs. Voltage

FADE IN / FADE OUT

LP3954 has an automatic fade in and out for main and sub backlight. The fade function is enabled with

EN_FADE bit. The slope of the fade curve is set by the SLOPE bit. Fade control for main and sub display is set

by FADE_SEL bit.

EN_FADE

SLOPE

FADE_SEL

0

Automatic fade disabled

1

Automatic fade enabled

0

Fade execution time 1.3s

1

Fade execution time 0.65s

0

Fade controls WLED1-4

1

Fade controls WLED5-6

Recommended fading sequence:

1. ASSUMPTION: Current WLED value in register

2. Set SLOPE

3. Set FADE_SEL

4. Set EN_FADE = 1

5. Set target WLED value

6. Fading will be done either within 0.5s or 1s based on Slope selection

28

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

100

100

FADE OUT

FADE OUT

80

80

FADE IN

CURRENT (%)

CURRENT (%)

FADE IN

60

40

20

60

40

20

0

0

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0

0.2

0.4

TIME (s)

0.6

0.8

0.1

1.2

1.4

TIME (s)

Figure 29. WLED Dimming, SLOPE=0

Figure 30. WLED Dimming, SLOPE=1

Ambient Light and Temperature Measurement with LP3954

The Analog-to-Digital converter (ADC) in the Audio Syncronization block can be also used for ambient light

measurement or temperature measurement.

The selection between these modes is controlled with input selector bits INPUT_SEL[1:0] as follows

INPUT_SEL[1:0]

Mode

00

Audio synchronization

01

Temperature measurement

(voltage input)

10

Ambient light measurement

(current input)

11

No input

AMBIENT LIGHT MEASUREMENT

The ambient light measurement requires only one external component: Ambient light sensor (photo transistor or

diode). The ADC reads the current level at ASE pin and converts the result in digital word. User can read the

ADC output from the ADC output register. The known ambient light condition allows user to set the backlight

current to optimal level thus saving power especially in low light and bright sunlight condition.

VDDA

AMBIENT

LIGHT

SENSOR

IBIAS

1 PA

R

S2

ADC

AIN

-

S1

S3

+

VDDA

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

29

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

FF

E0

ADC CODE

C0

A0

80

60

40

20

00

0

1

2

3

4

5

6

7

INPUT CURRENT (PA)

Figure 31. ADC Code vs Input Current in Light Measurement Mode

TEMPERATURE MEASUREMENT

The temperature measurement requires two external components: resistor and thermistor (resistor that has

known temperature vs resistance curve). The ADC reads the voltage level at ASE pin and converts the result in

digital word. User can read the ADC output from register. The known temperature allows for example to monitor

the temperature inside the display module and decrease the current level of the LEDs if temperature raises too

high. This function may increase lifetime of LEDs in some applications.

R

ADC

+

VDDA

TEMPERATURE

SENSOR

VDDA

AIN

S1

S2

Figure 32. Temperature Sensor Connection Example

30

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

FF

RESISTANCE VALUE R(T) / R(25)

100

E0

ADC CODE

C0

A0

80

60

40

20

0.2

0.4

0.6

0.8

1

0.1

0.01

-40

00

0

10

1

-20

0

20

40

60

80

100 120

TEMPERATURE (°C)

INPUT VOLTAGE × VDDA

Figure 33. ADC Code vs Input Voltage in

Temperature Measurement Mode

Figure 34. Example Curve for Thermistor

EXAMPLE TEMP SENSOR READING AT DIFFERENT TEMPERATURES (R(25°C)=1MΩ)

T°C

R(MΩ)

Rt(MΩ)

V(ASE)

-40

1

60

2.7540984

2.24

0

1

4

25

1

1

1.4

60

1

0.2

0.4666667

100

1

0.04

0.1076923

7V Shielding

To shield LP3954 from high input voltages 6…7.2V the use of external 2.8V LDO is required. This 2.8V voltage

protects internally the device against high voltage condition. The recommended connection is as shown in the

picture below. Internally both logic and analog circuitry works at 2.8V supply voltage. Both supply voltage pins

should have separate filtering capacitors.

4.7 PH

BATTERY

+

-

CIN

10 PF

Digital

supply

voltage

VDD1

VDD2

2.8V

LDO

2.8V

CVDD CVDDA

1 PF

100 nF

VDDA

SW

LDO

Analog

supply

voltage

LP3954

In cases where high voltage is not an issue the connection is as shown below.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

31

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

4.7 H

BATTERY

+

-

CIN

10 F

CVDD

100 nF

Digital

supply

voltage

VDD1

VDD2

2.8V

VDDA

CVDDA

1 PF

SW

LDO

Analog

supply

voltage

LP3954

Logic Interface Characteristics

(1.65V ≤ VDDIO ≤ VDD1,2V) (Unless otherwise noted)

Parameter

Test Conditions

Min

Typ

Max

Unit

0.2 ×

VDDIO

V

LOGIC INPUTS SS, SI, SCK/SCL, SYNC/PWM, IF_SEL, EN_FLASH

VIL

Input Low Level

VIH

Input High Level

II

Logic Input Current

0.8 ×

VDDIO

V

−1.0

1.0

µA

I C Mode

400

kHz

SPI Mode,

VDDIO > 1.8V

13

MHz

SPI Mode,

1.65V ≤ VDDIO < 1.8V

5

MHz

2

fSCL

Clock Frequency

LOGIC OUTPUT SO

VOL

Output Low Level

VOH

Output High Level

IL

Output Leakage Current

ISO = 3 mA

VDDIO > 1.8V

0.3

0.5

ISO = 2 mA

1.65V ≤ VDDIO < 1.8V

0.3

0.5

V

ISO = −3 mA

VDDIO > 1.8V

VDDIO −

0.5

VDDIO −

0.3

ISO = -2 mA

1.65V ≤ VDDIO < 1.8V

VDDIO −

0.5

VDDIO −

0.3

VSO = 2.8V

V

1.0

µA

0.5

V

LOGIC OUTPUT SDA

VOL

Output Low Level

ISDA = 3 mA

0.3

Control Interface

The LP3954 supports two different interface modes:

• SPI interface (4 wire, serial)

• I2C compatible interface (2 wire, serial)

User can define the serial interface by IF_SEL pin. IF_SEL=0 selects the I2C mode.

32

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

SPI INTERFACE

LP3954 is compatible with SPI serial bus specification and it operates as a slave. The transmission consists of

16-bit Write and Read Cycles. One cycle consists of 7 Address bits, 1 Read/Write (RW) bit and 8 Data bits. RW

bit high state defines a Write Cycle and low defines a Read Cycle. SO output is normally in high-impedance state

and it is active only when Data is sent out during a Read Cycle. A pull-up resistor may be needed in SO line if a

floating logic signal can cause unintended current consumption in the input circuits where SO is connected.The

Address and Data are transmitted MSB first. The Slave Select signal SS must be low during the Cycle

transmission. SS resets the interface when high and it has to be taken high between successive Cycles. Data is

clocked in on the rising edge of the SCK clock signal, while data is clocked out on the falling edge of SCK.

SS

SCK

SI

A6

A5

A4

A3

A2

A1

A0

1

R/W

D7

D6

D5

D4

D3

D2

D1

D0

D2

D1

D0

SO

Figure 35. SPI Write Cycle

SS

SCK

SI

A6

A5

A4

A3

A2

A1

A0

R/W

0

Don't Care

D7

SO

D6

D5

D4

D3

Figure 36. SPI Read Cycle

SS

2

5

1

SCK

3

4

12

7

6

MSB IN

SI

BIT 14

BIT 9

BIT 8

BIT 1

BIT 7

8

11

10

MSB OUT

SO

Address

LSB IN

R/W

BIT 1

9

LSB OUT

Data

Figure 37. SPI Timing Diagram

SPI Timing Parameters

VDD = VDD_IO = 2.775V

Symbol

(1)

Parameter

Limit (1)

Min

Max

Unit

1

Cycle Time

70

ns

2

Enable Lead Time

35

ns

Note: Data ensured by design.

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

33

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

Symbol

www.ti.com

Limit (1)

Parameter

Min

Max

Unit

3

Enable Lag Time

35

ns

4

Clock Low Time

35

ns

5

Clock High Time

35

ns

6

Data Setup Time

20

ns

7

Data Hold Time

0

8

Data Access Time

20

ns

9

Disable Time

10

ns

10

Data Valid

20

ns

11

Data Hold Time

0

ns

ns

I2C COMPATIBLE INTERFACE

I2C Signals

In I2C mode the LP3954 pin SCK is used for the I2C clock SCL and the pin SS is used for the I2C data signal

SDA. Both these signals need a pull-up resistor according to I2C specification. SI pin is the address select pin.

I2C address for LP3954 is 54h when SI = 0 and 55h when SI = 1. Unused pin SO can be left unconnected.

I2C Data Validity

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of

the data line can only be changed when CLK is LOW.

SCL

SDA

data

change

allowed

data

valid

data

change

allowed

data

valid

data

change

allowed

Figure 38. I2C Signals: Data Validity

I2C Start and Stop Conditions

START and STOP bits classify the beginning and the end of the I2C session. START condition is defined as SDA

signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA

transitioning from LOW to HIGH while SCL is HIGH. The I2C master always generates START and STOP bits.

The I2C bus is considered to be busy after START condition and free after STOP condition. During data

transmission, I2C master can generate repeated START conditions. First START and repeated START

conditions are equivalent, function-wise.

SDA

SCL

34

S

P

START condition

STOP condition

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

�LP3954

www.ti.com

SNVS340D – JUNE 2005 – REVISED MARCH 2013

Transferring Data

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first.

Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated

by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver

must pull down the SDA line during the 9th clock pulse, signifying an acknowledge. A receiver which has been

addressed must generate an acknowledge after each byte has been received.

After the START condition, the I2C master sends a chip address. This address is seven bits long followed by an

eighth bit which is a data direction bit (R/W). The LP3954 address is 54h or 55H as selected with SI pin. For the

eighth bit, a “0” indicates a WRITE and a “1” indicates a READ. The second byte selects the register to which the

data will be written. The third byte contains data to write to the selected register.

MSB

ADR6

Bit7

LSB

ADR5

bit6

ADR4

bit5

ADR3

bit4

ADR2

bit3

ADR1

bit2

ADR0

bit1

R/W

bit0

2

I C SLAVE address (chip address)

Figure 39. I2C Chip Address

Register changes take an effect at the SCL rising edge during the last ACK from slave.

ack from slave

ack from slave

msb Chip Address lsb

start

w

ack

msb Register Add lsb

ack

w

ack

addr = 02h

ack

ack from slave

msb

DATA

lsb

ack

stop

address 02h data

ack

stop

SCL

SDA

start

Id = 54h

w = write (SDA = “0”)

r = read (SDA = “1”)

ack = acknowledge (SDA pulled down by either master or slave)

rs = repeated start

id = 7-bit chip address, 54h (SI=0) or 55h (SI=1) for LP3954.

Figure 40. I2C Write Cycle

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in

the Read Cycle waveform.

ack from slave

msb Chip Address lsb

start

w

ack from slave repeated start

msb Register Add lsb

ack from slave data from slave ack from master

rs

msb Chip Address lsb

rs

Id = 54h

r

msb

DATA

lsb

stop

SCL

SDA

start

Id = 54h

w ack

addr = h00

ack

r ack

Address 00h data

ack stop

Figure 41. I2C Read Cycle

Submit Documentation Feedback

Copyright © 2005–2013, Texas Instruments Incorporated

Product Folder Links: LP3954

35

�LP3954

SNVS340D – JUNE 2005 – REVISED MARCH 2013

www.ti.com

SDA

10

8

7

6

1

8

2

7

SCL

5

1

3

4

9

Figure 42. I2C Timing Diagram

I2C Timing Parameters (VDD1,2 = 3.0 to 4.5V, VDD_IO = 1.65V to VDD1,2)

Symbol

(1)

Parameter

Limit (1)

Min

Max

Unit

1

Hold Time (repeated) START Condition

0.6

µs

2

Clock Low Time

1.3

µs

3

Clock High Time

600

ns

4

Setup Time for a Repeated START Condition

600

5

Data Hold Time (Output direction, delay generated by LP3954)

300

900

ns

5

Data Hold Time (Input direction, delay generated by the Master)

0

900

ns

6

Data Setup Time

7

Rise Time of SDA and SCL

20+0.1Cb

300

ns

8

Fall Time of SDA and SCL

15+0.1Cb

300

ns

ns

100

9

Set-up Time for STOP condition

600

10

Bus Free Time between a STOP and a START Condition

1.3

Cb

Capacitive Load for Each Bus Line

10

ns

ns

µs

200

pF

NOTE: Data ensured by design

Autoincrement mode is available, with this possible read or write few byte with autoincreasing addresses, but

LP3954 has holes in address register map, and is recommended to use autoincrement mode only for the pattern

command registers.

Recommended External Components

OUTPUT CAPACITOR, COUT

The output capacitor COUT directly affects the magnitude of the output ripple voltage. In general, the higher the

value of COUT, the lower the output ripple magnitude. Multilayer ceramic capacitors with low ESR are the best