Product

Folder

Sample &

Buy

Support &

Community

Tools &

Software

Technical

Documents

LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

LP5520 RGB Backlight LED Driver

1 Features

3 Description

•

The LP5520 is an RGB backlight LED driver for small

format color LCDs. RGB backlights enable better

colors on the display and power savings compared

with white LED backlights. The device offers a small

and simple driver solution without need for optical

feedback. Calibration in display module production

can be done in one temperature. The LP5520

produces true white light over a wide temperature

range. Three independent LED drivers have accurate

programmable current sinks and PWM modulation

control. Using internal calibration memory and

external temperature sensor, the RGB LED currents

are adjusted for perfect white balance independent of

the brightness setting or temperature. The user

programmable calibration memory has intensity vs

temperature data for each color. This white balance

calibration data can be programmed to the memory

on the production line of a backlight module.

1

•

•

•

•

•

•

•

•

•

•

•

•

•

Temperature Compensated LED Intensity and

Color

Individual Calibration Coefficients for Each Color

Color Accuracy ΔX and ΔY ≤ 0.003

12-Bit ADC for Measurement of 2 Sensors

Adjustable Current Outputs for Red, Green, and

Blue (RGB) LED

0.2% Typical LED Output Current Matching

PWM Control Inputs for Each Color

SPI™ and I2C-Compatible Interface

Stand-Alone Mode With One-Wire Control

Sequential Mode for One Color at a Time

Magnetic High Efficiency Boost Converter

Programmable Output Voltage from 5 V to 20 V

Adaptive Output Voltage Control Option

< 2-µA Typical Shutdown Current

The device has a magnetic boost converter that

creates a supply voltage of up to 20 V LED from the

battery voltage. The output can be set at 1-V steps

from 5 V to 20 V. In adaptive mode the circuit

automatically adjusts the output voltage to minimum

sufficient level for lowest power consumption.

Temperature is measured using an external

temperature sensor placed close to the LEDs. The

second ADC input can be used, for example, for

ambient light measurement.

2 Applications

•

•

Color LCD Display Backlighting

LED Lighting Applications

Device Information(1)

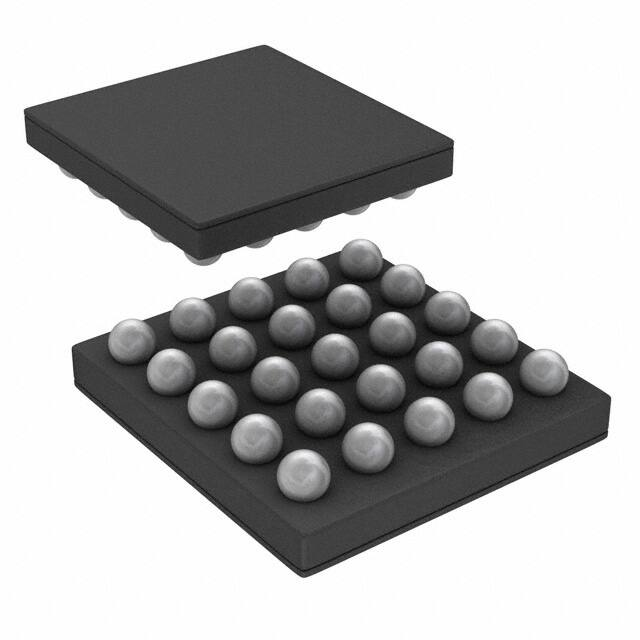

PART NUMBER

LP5520

PACKAGE

DSBGA (25)

BODY SIZE (MAX)

2.787 mm × 2.621 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Typical Application

D1

L1

2.9 ± 5.5V

+

CVDDA

CVDDD

CIN

100 nF

100 nF

4.7 PF

4.7 PH

1 PF

CVLDO

VDDA

VDDD

5 ± 20V

COUT

2x

4.7 PF

SW

VLDO

S1_IN

S2_IN

ADC

CALIBRATION

MEMORY

FB

BOOST

VLDO

LM 20

MCU

WITH

I2C

OR

SPI

CVDDIO

100 nF

NRST

SS/SDA

SCK/SCL SPI/I2C

SI/A0

INTERFACE

SO

IFSEL

VDDIO

PWMR

PWMG

PWMB

BRC

LP5520

LP55XX

COLOR AND

BRIGHTNESS

PWM LOGIC

LED

DRIVERS ROUT

GOUT

BOUT

GND

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

Table of Contents

1

2

3

4

5

6

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Function ...........................

Specifications.........................................................

1

1

1

2

3

4

6.1

6.2

6.3

6.4

6.5

6.6

Absolute Maximum Ratings ...................................... 4

ESD Ratings.............................................................. 4

Recommended Operating Conditions....................... 4

Thermal Information .................................................. 4

Electrical Characteristics........................................... 5

RGB Driver Electrical Characteristics (ROUT, GOUT,

BOUT Outputs) .......................................................... 5

6.7 Logic Interface Characteristics.................................. 6

6.8 Magnetic Boost DC-DC Converter Electrical

Characteristics ........................................................... 6

6.9 I2C Timing Parameters ............................................. 7

6.10 SPI Timing Requirements ....................................... 7

6.11 Typical Characteristics ............................................ 8

7

Detailed Description .............................................. 9

7.1 Overview ................................................................... 9

7.2

7.3

7.4

7.5

7.6

8

Functional Block Diagram ......................................... 9

Feature Description................................................... 9

Device Functional Modes........................................ 18

Programming........................................................... 22

Register Maps ......................................................... 28

Application and Implementation ........................ 33

8.1 Application Information............................................ 33

8.2 Typical Applications ............................................... 33

9 Power Supply Recommendations...................... 37

10 Layout................................................................... 37

10.1 Layout Guidelines ................................................. 37

10.2 Layout Example .................................................... 38

11 Device and Documentation Support ................. 39

11.1

11.2

11.3

11.4

11.5

11.6

Device Support......................................................

Documentation Support ........................................

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

39

39

39

39

39

39

12 Mechanical, Packaging, and Orderable

Information ........................................................... 40

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision A (May 2013) to Revision B

Page

•

Changed "R, G and B" to "Red, Green, and Blue"................................................................................................................. 1

•

Deleted "Non-Linear Temperature Compensation" and "Ambient Light Compensation" from Applications ......................... 1

•

Added Device Information and Pin Configuration and Functions sections, ESD Ratings and Thermal Information

tables, Feature Description, Device Functional Modes, Application and Implementation, Power Supply

Recommendations, Layout, Device and Documentation Support, and Mechanical, Packaging, and Orderable

Information sections................................................................................................................................................................ 1

•

Changed "MAIN, SUB" to " ROUT, GOUT, BOUT"................................................................................................................ 4

•

Changed "come" to "are loaded" .......................................................................................................................................... 12

•

Changed ", and also the variable" to ". The variable parameter" ......................................................................................... 18

•

Changed "makes possible" to "allows" ................................................................................................................................. 19

•

Changed "read" to "loaded" .................................................................................................................................................. 19

•

Changed "The stand-alone mode must be inhibited in automatic and manual modes by writing the control bit

high and by keeping BRC input low." to new text .............................................................................................. 19

Changes from Original (April 2013) to Revision A

•

2

Page

Changed layout of National Data Sheet to TI format ........................................................................................................... 32

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

5 Pin Configuration and Function

YZR Packge

25-Pin DSBGA

Top View

YZR Packge

25-Pin DSBGA

Bottom View

5

SO

SI/

A0

VDDD

FB

SW

SW

FB

VDDD

SI/

A0

SO

5

4

SS/

SDA

SCK/

SCL

IFSEL

PWMR

GND

_SW

GND

_SW

PWMR

IFSEL

SCK/

SCL

SS/

SDA

4

3

VDDIO

NRST

PWMG

GNDA

GND

_LED

GND

_LED

GNDA

PWMG

NRST

VDDIO

3

2

VLDO

BRC

S2_IN

PWMB

ROUT

ROUT

PWMB

S2_IN

BRC

VLDO

2

1

VDDA

GNDT

S1_IN

BOUT

GOUT

GOUT

BOUT

S1_IN

GNDT

VDDA

1

A

B

D

E

E

D

C

B

A

C

Pin Functions

PIN

NUMBER

NAME

TYPE

DESCRIPTION

1A

VDDA

Power

Supply voltage for analog circuitry

1B

GNDT

Ground

Ground/Test

1C

S1_IN

Input

1D

BOUT

Output

Blue LED output

1E

GOUT

Output

Green LED output

2A

VLDO

Power

Internal LDO output

2B

BRC

Logic Input

2C

S2_IN

Input

2D

PWMB

Logic Input

2E

ROUT

Output

Red LED output

3A

VDDIO

Power

Supply voltage for input/output buffers and drivers

3B

NRST

Logic Input

Master reset, active low

3C

PWMG

Logic Input

PWM control for output G

3D

GNDA

Ground

Ground for analog circuitry

3E

GND_LED

Ground

Ground for LED currents

4A

SS/SDA

Logic Input/Output

4B

SCK/SCL

Logic Input

Clock (SPI/I2C)

4C

IFSEL

Logic Input

Interface selection (SPI or I2C-compatible, IF_SEL = 1 for SPI)

4D

PWMR

Logic Input

PWM control for output R

4E

GND_SW

Ground

Power switch ground

5A

SO

Logic Output

Serial data out (SPI)

5B

SI/A0

Logic Input

5C

VDDD

Power

5D

FB

Input

5E

SW

Output

ADC input 1, input for temperature sensor

Brightness control for all LED outputs

ADC input 2, input for optional second sensor

PWM control for output B

Slave select (SPI), serial data in/out (I2C)

Serial input (SPI), address select (I2C)

Supply voltage for digital circuitry

Boost converter feedback

Boost converter power switch

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

3

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2) (3)

MIN

MAX

UNIT

V (SW, FB, ROUT, GOUT, BOUT)

–0.3

22

V

VDDA, VDDD, VDDIO, VLDO

–0.3

6

V

–0.3 V to VDDIO

0.3 V with 6 V

maximum

V

Voltage on logic pins

Continuous power dissipation (4)

Internally limited

Junction temperature, TJ-MAX

Storage temperature, Tstg

(1)

(2)

(3)

(4)

–65

125

°C

150

°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltages are with respect to the potential at the GND pins.

If Military/Aerospace specified devices are required, contact the TI Sales Office/Distributors for availability and specifications.

Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at TJ = 160°C (typical) and

disengages at TJ = 140°C (typical).

6.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)

±2000

Charged-device model (CDM), per JEDEC specification JESD22-C101 (2)

±200

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) (1)

V (SW, FB, ROUT, GOUT, BOUT)

VDDA,DDD

VDDIO

Recommended load current (ROUT, GOUT, BOUT) per driver

MIN

MAX

0

21

UNIT

V

2.9

5.5

V

1.65

VDDA

V

0

60

mA

Junction temperature, TJ

–30

125

°C

Ambient temperature, TA (2)

–30

85

°C

(1)

(2)

All voltages are with respect to the potential at the GND pins.

In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may

have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP =

125°C), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the

part/package in the application (RθJA), as given by the following equation: TA-MAX = TJ-MAX-OP – (RθJA × PD-MAX).

6.4 Thermal Information

LP5520

THERMAL METRIC (1)

YZR (DSBGA)

UNIT

25 PINS

RθJA

Junction-to-ambient thermal resistance

58.2

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

0.3

°C/W

RθJB

Junction-to-board thermal resistance

7.9

°C/W

ψJT

Junction-to-top characterization parameter

0.5

°C/W

ψJB

Junction-to-board characterization parameter

7.9

°C/W

(1)

4

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

6.5 Electrical Characteristics

Unless otherwise noted typical limits are for TJ = 25°C, minimum and maximum limits apply over the operating ambient

temperature range (–30°C < TJ < +85°C), and specifications apply to the LP5520 Functional Block Diagram with: CVDDA/D =

100 nF, COUT = 2 × 4.7 µF, 25 V, CIN= 10 µF, 6.3 V, L1 = 4.7 µH. (1) (2) (3)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

1.7

7

Standby supply current

(VDDA + VDDD)

NSTBY = L, VDDIO ≥ 1.65 V

No-boost supply current

(VDDA + VDDD)

NSTBY = H,

EN_BOOST = L

0.9

No-load supply current

(VDDA + VDDD)

NSTBY = H, EN_BOOST = H

AUTOLOAD = L

1.4

IVDDIO

VDDIO standby supply current

NSTBY = L

VLDO

Internal LDO output voltage

VIN ≥ 2.9 V, TJ = 25°C

ILDO

Internal LDO output current

Current to external load

IVDD

(1)

(2)

(3)

NSTBY = L , VDDIO = 0 V

UNIT

µA

1

mA

1

2.77

2.80

µA

2.84

V

1

mA

All voltages are with respect to the potential at the GND pins.

Minimum and maximum limits are specified by design, test or statistical analysis. Typical numbers represent the most likely norm.

Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

6.6 RGB Driver Electrical Characteristics (ROUT, GOUT, BOUT Outputs)

Typical limits are for TJ = 25°C, minimum and maximum limits apply over the operating ambient temperature range

(–30°C < TJ < +85°C); over operating free-air temperature range (unless otherwise noted).

PARAMETER

ILEAKAGE

ROUT, GOUT, BOUT pin

leakage current

IMAX

Maximum sink current

TEST CONDITIONS

TYP

MAX

0.1

1

Outputs ROUT, GOUT, BOUT control = 255

(FFH)

Output current set to 20 mA

Current accuracy of ROUT,

GOUT, and BOUT

IR

MIN

Output current set to 60 mA

UNIT

µA

mA

60

19

20

–5%

54

21

mA

5%

60

–10%

66

mA

10%

IMATCH

Matching (1)

Between ROUT, GOUT, BOUT at 20 mA current

tPWM

PWM cycle time

Accuracy proportional to internal clock frequency

820

µs

= 0

1.22

kHz

= 1

19.52

ƒRGB

RGB switching frequency

VSAT

Saturation voltage (2)

I(LED) = 60 mA

ƒMAX

External PWM maximum

frequency

I(LED) = 60 mA, TJ = 25°C

(1)

(2)

±0.2%

±2%

550

mV

1

MHz

Matching is the maximum difference from the average when all outputs are set to same current.

Saturation voltage is defined as the voltage when the LED current has dropped 10% from the value measured at 2 V.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

5

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

6.7 Logic Interface Characteristics

Typical limits are for TJ = 25°C, minimum and maximum limits apply over the operating ambient temperature range

(–30°C < TJ < +85°C); over operating free-air temperature range (unless otherwise noted).

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

LOGIC INPUTS SS, SI/A0, SCK/SCL, IFSEL, NRST, PWMR, PWMG, PWMB and BRC

VIL

Input low level

VIH

Input high level

II

Logic input current

ƒSCK/SLC

Clock frequency

0.2 × VDDIO

V

1

µA

0.8 × VDDIO

V

−1

I2C mode

0.4

SPI mode, VDDIO > 1.8 V

13

SPI mode, 1.65 V < VDDIO <

1.8 V

MHz

5

LOGIC INPUT NRST

VIL

Input low level

VIH

Input high level

1.2

05

II

Logic input current

–1

tNRST

Reset pulse width

10

V

V

1

µA

µs

LOGIC OUTPUT SO

VOL

Output low level

VOH

Output high level

IL

Output leakage current

ISO = 3 mA

VDDIO > 1.8 V

0.3

0.5

V

ISO = 2 mA

1.65 V < VDDIO < 1.8 V

0.3

0.5

V

ISO = –3 mA

VDDIO > 1.8 V

VDDIO − 0.5

VDDIO − 0.3

V

ISO = –2 mA

1.65 V < VDDIO < 1.8 V

VDDIO − 0.5

VDDIO − 0.3

V

VSO = 2.8 V

1

µA

0.5

V

LOGIC OUTPUT SDA

VOL

Output low level

ISDA = 3 mA

0.3

6.8 Magnetic Boost DC-DC Converter Electrical Characteristics

Typical limits are for TJ = 25°C, minimum and maximum limits apply over the operating ambient temperature range

(–30°C < TJ < +85°C); over operating free-air temperature range (unless otherwise noted).

PARAMETER

TEST CONDITIONS

ILOAD

Maximum continuous load

current

VOUT

2.9 ≤ VIN ≤ 5.5 V, VOUT = 20 V

Output voltage accuracy (FB pin) TJ = 25°C

2.9 ≤ VIN ≤ 5.5 V, VOUT = 20 V

RDSON

Switch ON resistance

ƒPWM

Frequency accuracy

tPULSE

Switch pulse minimum width

tSTARTUP

Start-up time

IMAX

SW pin current limit

6

2.9V = VIN, VOUT = 20 V

TJ = 25°C

MIN

–1.7%

1.7%

–5%

5%

Submit Documentation Feedback

Ω

0.3

−6%

UNIT

mA

±3%

–9%

no load

MAX

70

ISW = 0.5 A

TJ = 25°C

TYP

6%

9%

50

ns

20

ms

1100

mA

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

6.9 I2C Timing Parameters

VDD1,2 = 3 V to 4.5 V, VDDIO = 1.8 V To VDD1,2; see Figure 1.

MIN

MAX

UNIT

1

Hold time (repeated) START condition

0.6

µs

2

Clock low time

1.3

µs

3

Clock high time

600

ns

4

Setup time for a repeated START condition

600

ns

5

Data hold time (output direction, delay generated by LP5520)

300

900

ns

5

Data hold time (input direction, delay generated by Master)

0

900

ns

6

Data setup time

7

Rise time of SDA and SCL

20 + 0.1Cb

300

ns

8

Fall time of SDA and SCL

15 + 0.1Cb

300

ns

9

Setup time for STOP condition

600

10

Bus free time between a STOP and a START condition

1.3

Cb

Capacitive load for each bus line

10

200

pF

MIN

MAX

UNIT

100

ns

ns

µs

6.10 SPI Timing Requirements

See Figure 2.

1

Cycle time

70

ns

2

Enable lead time

35

ns

3

Enable lag time

35

ns

4

Clock low time

35

ns

5

Clock high time

35

ns

6

Data setup time

0

ns

7

Data hold time

25

ns

8

Data access time

30

ns

9

Disable time

20

ns

10

Data valid

40

ns

11

Data hold time

0

ns

SDA

10

8

7

6

1

8

2

7

SCL

5

1

4

3

9

Figure 1. I2C Timing Diagram

SS

2

5

1

SCK

3

4

12

7

6

SI

MSB IN

BIT 14

BIT 9

BIT 8

BIT 1

BIT 7

8

11

10

MSB OUT

SO

Address

R/W

LSB IN

BIT 1

9

LSB OUT

Data

Figure 2. SPI Timing Diagram

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

7

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

6.11 Typical Characteristics

60.0

60.0

50.0

50.0

OUTPUT CURRENT (mA)

OUTPUT CURRENT (mA)

6.11.1 RGB Driver Typical Characteristics

40.0

30.0

20.0

10.0

40.0

30.0

20.0

10.0

0.0

0.0

0.2

0.4

0.6

0.8

0.0

0.0

1.0

0.2

0.4

0.6

0.8

OUTPUT VOLTAGE (V)

OUTPUT VOLTAGE (V)

Figure 3. VSAT vs ILED

Figure 4. VSAT vs ILED

1.0

6.11.2 Boost Converter Typical Characteristics

VIN = 3.6 V, VOUT = 15 V, if not otherwise stated.

20.0

600

18.0

600

BATTERY CURRENT (mA)

OUTPUT VOLTAGE (V)

INDUCTOR TDK VLF3010 - 4.7 PH

16.0

VIN = 3.6V

14.0

12.0

10.0

VIN = 2.9V

8.0

6.0

4.0

0

VOUT = 20V

450

400

350

VOUT =1 5V

300

250

VOUT = 10V

200

INDUCTOR TDK VLF3010 - 4.7 mH

60

120

180

240

300

150

2.9

360

3.1

3.3

3.5

3.7

3.9

4.1

OUTPUT CURRENT (mA)

BATTERY VOLTAGE (V)

Figure 5. Boost Maximum Output Voltage vs Current

Figure 6. Battery Current vs Voltage

8.0

8.0

6.0

AUTOLOAD ON

VOLTAGE (V)

INPUT CURRENT (mA)

7.0

5.0

4.0

AUTOLOAD OFF

3.0

1.0

5.0

VBOOST

7.0

8.0

6.0

7.0

6.0

5.0

5.0

VLOAD

4.0

4.0

3.0

3.0

2.0

1.0

2.0

0.0

2.0

VDRIVER

1.0

8.0

11.0

14.0

17.0

0.0

20.0

0.0

OUTPUT VOLTAGE (V)

Figure 7. Auto-Load Effect on Input Current, No Load

8

ILOAD = 60 mA

500

0.5

1.0

1.5 2.0 2.5

TIME (s)

3.0

3.5

4.0

Figure 8. Adaptive Output Voltage Operation

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

7 Detailed Description

7.1 Overview

The LP5520 is an RGB backlight LED driver for small format color LCDs. The LP5520 offers a small and simple

driver solution without need for optical feedback. Calibration in display module production can be done in one

temperature. The LP5520 produces true white light over a wide temperature range.

Three independent LED drivers have accurate programmable current sinks with up to 60 mA current capability

and PWM modulation control. Using internal calibration memory and external temperature sensor, the RGB LED

currents are adjusted for perfect white balance independent of the brightness setting or temperature. The user

programmable calibration memory has intensity vs temperature data for each color. This white balance

calibration data can be programmed to the memory on the production line of a backlight module.

The LP5520 has a magnetic boost converter that creates supply voltage up to 20-V LED from the battery

voltage. The output can be set at 1-V step from 5 V to 20 V. In adaptive mode the circuit automatically adjusts

the output voltage to minimum sufficient level for lowest power consumption.

Temperature is measured using an external temperature sensor placed close to the LEDs. The second ADC

input can be used, for example, for ambient light measurement.

7.2 Functional Block Diagram

Optional EMI

filter

close to SW pin

CSW

Optional HF

capacitor

RSW

68 pF

330 pF 3.9 :

D1

2.9 V± 5.5V

CVDDD

100 nF

+

CVLDO 1 PF

VLDO

CVDDA

CIN

100 nF

4.7 PF

VDDD

VDDA

SW

LSW

Optional

Ferrite

Bead

FB

S2_IN

ADC

BOOST

ANALOG

SUPPORT

COUT

2x

4.7 PF

CURRENT

DACS

RST

SS/SDA

SCK/SCL

SI/A0

MCU or

TESTER

with SPI

interface

L1

4.7 PH

5 V ± 20V

LP5520

S1_IN

TEMP

SENSOR

LM20

CHF

SO

SPI/I2C

INTERFACE

AND

CONTROL

CALIBRATION

EEPROM

IFSEL

ROUT 0 ± 60 mA

VDDIO

COLOR

PWM

LOGIC

PWMR

PWMG

PWMB

BRC

LED

DRIVERS

GOUT 0 ± 60 mA

BOUT 0 ± 60 mA

CVDDIO

100 nF

GND_T

GND_A

GND_LED

GND_SW

7.3 Feature Description

7.3.1 Start-Up Powering

VDDD and VDDA must be tied together and turned on first. VDDIO must be turned on at the same time as VDDD or

later. In the power-off sequence VDDIO must be turned off before VDDD or at the same time.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

9

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

Feature Description (continued)

Power ON

Power OFF

VDDD and VDDA

VDDIO

Figure 9. Power-On Signal Timing

7.3.2 RGB Driver Functionality

7.3.2.1 White Balance Control

The LP5520 is designed to provide spectrally rich white light using a three-color RGB LED. White light is

obtained when the red, green, and blue LED intensities are in proper balance. The LED intensities change

independently with temperature. For maintaining the purity of the white color and the targeted total intensity,

precise temperature dependent intensity control for each LED is required. The color coordinates in this document

refer to the CIE 1931 color graph (x,y system).

0.9

Y 520

0.8

540

Green

0.7

Target for white

light

560

0.6

500

580

0.5

0.4

600

0.3

620

490

Red

700

0.2

480

0.1

470

460

0

0

0.1

Blue

380

0.2

X

0.3

0.4

0.5

0.6

0.7

0.8

Figure 10. CIE 1931 Color Graph

Figure 11 shows a typical RGB LED intensity behavior on a 12-bit scale (0 to 4095) at constant 20-mA LED

currents. Figure 12 shows the typical color coordinate change for an uncompensated RGB LED. Figure 13 shows

the corresponding PWM values for achieving constant intensity white light across the temperature range. The

PWM values have been saturated at 104°C to avoid overheating the LED and to better utilize the PWM range.

The white balance is not maintained above 104°C in this case.

INTENSITY

4000

3500

4000

3000

3500

3000

2500

2500

2000

2000

1500

1500

1000

500

10000

Red

Blue

Green

500

0

-40

-20

0

20

40

TEMPERATURE

60

80

Figure 11. LED Intensity vs Temperature

10

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

Feature Description (continued)

0.34

COLOR COORDINATE

0.34

Y

0.32

0.32

0.31

0.29

0.29

X

0.28

0.28

0.26

0.26

-40

-14

12

38

TEMPERATURE,°C

64

90

Figure 12. Typical Color Coordinates vs Temperature for Uncompensated RGB LED

The compensation values for the measured temperatures can be easily calculated when the intensity vs

temperature information is available. For the best accuracy the iterative calibration approach must be used.

PWM VALUE

4000

Red

3500

4000

3000

3500

3000

2500

2500

2000

2000

1500

1500

1000

500

1000

0

Green

Blue

500

0

-40 -20

0

20 40 60 80

TEMPERATURE

100 120

Figure 13. Compensation PWM Values

The compensation values must be converted to 16°C intervals when they are programmed to the calibration

EEPROM. The evaluation software has import function, which can be used to convert the measured

compensation data to the 16°C interval format. The measured data can have any temperature points, and the

software fits a curve through the measured points and calculate new PWM values in fixed temperatures using the

curves.

Typical color coordinate and intensity stability over temperature are shown in Figure 14 and Figure 15.

0.310

COLOR COORDINATES

0.310

0.305

0.305

X

0.300

0.300

0.295

Y

0.295

0.290

0.290

-40

-20

0

20

40

60

TEMPERATURE, °C

80

Figure 14. Compensated Color Coordinates vs Temperature

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

11

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

Feature Description (continued)

1500

1500

INTENSITY BLUE

1450

1450

1400

1400

1350

1350

1300

1300

-40

-20

0

20

40

60

TEMPERATURE, °C

80

Figure 15. Compensated Blue LED Intensity vs Temperature

7.3.2.2 LED Brightness Control

The LED brightness is defined by two factors, the current through the LED and the PWM duty cycle. The

constant current outputs ROUT, GOUT, and BOUT can be independently set to sink between 0 and 60 mA. The

8-bit current control has 255 levels, and the step size is 235 µA. In manual mode the current is defined with the

current control (R/G/B) registers (01H, 02H, and 03H). In automatic mode the current settings are loaded from

the EEPROM.

The PWM control has 12-bit resolution, which means 4095 steps. The minimum pulse width is 200 ns, and the

frequency can be set to either 1.2 kHz or 19.2 kHz. The duty cycle range is from 0 to 100% (0 to 4095). The

output PWM value is obtained by multiplication of three factors. The first factor is the temperature-based value

from the EEPROM. The second factor is the correction register setting, which is independent for each color. The

third factor is the brightness register setting, which is common to all colors.

The temperature-based PWM values are stored in the EEPROM at 16°C intervals starting from –40°C and

ending to 120°C. PWM values for the temperatures between the stored points are interpolated.

LED brightness has 3-bit logarithmic control. The control bits are in the pwm_brightness (04H) register. The 3-bit

value defines a multiplier for the 12-bit PWM value obtained from the memory according to Table 1.

12

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

Feature Description (continued)

Table 1. PWM Value Multipliers

CONTROL BYTE

(1)

(1)

MULTIPLIER

INTENSITY ( %)

0

0.008

0.8

1

0.016

1.6

2

0.031

3.1

3

0.063

6.3

4

0.125

12.5

5

0.250

25

6

0.500

50

7

1.000

100

PWM Brightness register control

The brightness correction can be used for aging compensation or other fine-tuning. There is an 8-bit correction

register for each output. The PWM value obtained from the memory is multiplied by the correction value. The

default correction value is 1. Correction range is from 0 to 2 and the LSB is 0.78% (1/128).

TEMP

SENSOR

ROUT

BRIGHTNESS

0.8 ± 100%

8 STEP LOG

SELF

HEATING

COMPENS.

S1_IN

ADC

+

LOGIC

CORRECTION R

0 ± 200%

(AGEING COMP)

8

R

12

EEPROM G

+

LOGIC B

12

12

12

5 MHz

12

8

PWM

GEN

CURRENT R

0 ± 60mA

PWM_R

Shown complete only for red channel

Figure 16. LED Control Principle

7.3.2.3 LED PWM Control

The PWM frequency can be selected of two alternatives, slow and fast, with the control bit . The

slow frequency is 1.2 kHz. In the fast mode the PWM frequency is multiplied by 16, and the frequency is 19.2

kHz. Fast mode is the default mode after reset. The single pulse in normal PWM is split in 16 narrow pulses in

fast PWM. Higher frequency helps eliminate possible noise from the ceramic capacitors and it also reduces the

ripple in the boost voltage. Minimum pulse length is 200 ns in both modes.

The PWM pulses of each output do not start simultaneously in order to avoid high current spike. Red starts in the

beginning of the PWM cycle, Green is symmetric with the cycle center and Blue ends in the end of the cycle. For

PWM values less than 33% for each output, the output currents are completely non-overlapping. With higher

PWM values the overlapping increases.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

13

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

0%

100%

50%

ROUT

GOUT

BOUT

819 Ps/1.22 kHz in normal PWM

52 Ps/19.2 kHz in fast PWM

Figure 17. Pulse Positions in the PWM Cycle

7.3.2.4 Sequential Mode

Completely non-overlapping timing can be obtained by using the sequential mode as shown in Figure 18. The

timing is defined with external PWM control inputs. The minimum trigger pulse width in the PWM inputs is 1 µs.

There is no limitation on the maximum width of the pulse as long as it is shorter than the whole sequence.

Dead time

Internal PWM cycle

PWMR

ROUT

1

2

3

4

PWMG

1

GOUT

3.333 ms

2

3

4

3.333 ms

3.333 ms

PWMB

1

BOUT

2

3

4

10 ms/100 Hz

Figure 18. Non-Overlapping External Synchronized Sequential Mode

In sequential mode the PWM cycle is synchronized to trigger pulses and the amount of PWM pulses per trigger

can be defined to 2, 3 or 4 using the and control bits. This makes possible to use

sequence lengths of about 5 ms, 7.5 ms or 10 ms. Fast PWM can be used in sequential mode, but the frame

timing is as with normal PWM.

The PWM timing and synchronization timing originate from different clock sources. Some margin must be

allowed for clock tolerances. This margin shows as a dead time in the waveform graph. Some dead time must be

allowed so that no PWM pulse is clipped. Clipping would distort the intensity balance between the LEDs. The

dead time causes some intensity reduction, but assures the current balance.

PWM mode is defined by and control bits of rgb_control (00H) register:

14

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

Table 2. PWM Mode

(BIT 7)

(BIT 6)

0

0

Normal mode

0

1

Sequential mode with 2 PWM pulses per trigger

1

0

Sequential mode with 3 PWM pulses per trigger

1

1

Sequential mode with 4 PWM pulses per trigger

MODE

7.3.2.5 Current Control of the LEDs

The LP5520 has a separate 8-bit current control for each LED output. In manual mode the current for red LED is

controlled with the current_control_r (01H) register, the green LED is controlled with the current_control_g

(02H), and the blue LED with current_control_b (03H). Output current can be calculated with formula: current

(mA) = code × 0.235; for example, a 20-mA current is obtained with code 85 (55H).

In automatic and stand-alone modes the LED current values programmed in EEPROM are used, and the current

control registers have no effect. There are two ways to change the default current if needed. The defaults can be

changed permanently by programming new values to the EEPROM. The other option is to make a temporary

change by writing new current values in SRAM.

7.3.2.6 Output Enables

ROUT, GOUT, and BOUT output activity is controlled with 3 enable bits of the rgb_control (00H) register:

Table 3. Output Enable Bits

(bit 2)

(bit 1)

(bit 0)

0

Blue LED output BOUT disabled

1

Blue LED output BOUT enabled

0

Green LED output GOUT disabled

1

Green LED output GOUT enabled

0

Red LED output ROUT disabled

1

Red LED output ROUT enabled

PWM control inputs PWMR, PWMG and PWMB can be used as external output enables in normal and automatic

mode. In the sequential mode these inputs are the trigger inputs for respective outputs.

7.3.2.7 Fade In and Fade Out

The LP5520 has an automatic fade in and out for the LED outputs. Fading makes the transitions smooth in on

and off switching or when brightness is changed. It is not applied for the changes caused by the compensation

algorithm. The fade can be turned on and off using the bit in the rgb_control (00H) register. The

fade time is constant 520 ms, and it does not depend on how big the brightness change is. The white balance is

maintained during fading. Fading is off in the stand-alone mode.

Table 4. Fade In and Fade Out With Bit

(bit 5)

0

Automatic fade disabled

1

Automatic fade enabled

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

15

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

Fading only works in automatic mode. The LED current registers must be written to 0 for proper fade operation.

When the LEDs are turned on with fading, it is best to set the brightness first and then enable the outputs and

automatic mode. The LEDs can be turned off then by turning off the automatic mode (write rgb_auto to 0).

7.3.2.8 Temperature and Light Measurement

The LP5520 has a 12-bit analog-to-digital converter (ADC) for the measurements. The ADC has two inputs.

S1_IN input is intended for the LM20 temperature sensor and S2_IN input for light measurement or any DC

voltage measurement. The conversion results are filtered with average filter for 134 ms. The bit in the

Control register selects, which conversion result can be read out from the registers ADC_hi_byte and

ADC_low_byte. The ADC_hi_byte must be read first. The bit selects, which input is used for

compensation. The ADC uses the LDO voltage 2.8 V as the reference voltage. The input signal range is 0 V to

2.8 V, and the inputs are buffered on the chip.

If S2_IN is used for light measurement using TDK optical sensor BCS2015G1 as shown in the Functional Block

Diagram, the measurement range is from 10 to 20 000 lux when using a 100-kΩ resistor.

Table 5. ADC Configuration

adc_ch(bit5)

comp_sel(bit4)

0

S1 input can be read

1

S2 input can be read

0

S1 input is used for compensation

1

S2 input is used for compensation

S1_IN

S1_RESULT

2:1

MUX

12 BIT ADC

AVERAGE

1:2

MUX

S2_IN

S2_RESULT

Figure 19. ADC Operation Block Diagram

7.3.3 Magnetic High-Voltage Boost DC-DC Converter

The LP5520 boost DC-DC converter generates a 5-V to 20-V supply voltage for the LEDs from single Li-Ion

battery (2.9 V to 4.5V). The output voltage is controlled with four bits in 18 steps. In adaptive mode the output

voltage is automatically adjusted so that the LED drivers have enough voltage for proper operation. The

converter is a magnetic switching PWM mode DC-DC converter with a current limit. Switching frequency is 1

MHz. Boost converter options are controlled with few bits of Control (06H) register.

Table 6. Boost DC-DC Converter Control

(bit 3)

(bit 2)

(bit 1)

(bit 0)

0

Internal boost converter loader off

1

Internal boost converter loader on

0

Manual boost output adjustment

1

Adaptive boost output adjustment

0

Boost converter standby mode

1

Boost converter active mode

0

LP5520 standby mode

1

LP5520 active mode

The LP5520 boost converter uses pulse-skipping elimination to stabilize the noise spectrum. Even with light load

or no load a minimum length current pulse is fed to the inductor. An active load is used to remove the excess

charge from the output capacitor at very light loads. Active load can be disabled with the bit.

Disabling active load increases slightly the efficiency at light loads, but the downside is that pulse skipping

occurs. The boost converter must be stopped when there is no load to minimize the current consumption.

The topology of the magnetic boost converter is called current programmed mode (CPM) control, where the

inductor current is measured and controlled with the feedback. The user can program the output voltage of the

boost converter. The output voltage control changes the resistor divider in the feedback loop.

16

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

Figure 20 shows the boost topology with the protection circuitry. Four different protection schemes are

implemented:

1. Overvoltage protection: limits the maximum output voltage and:

– Keeps the output below breakdown voltage.

– Prevents boost operation if battery voltage is much higher than desired output.

2. Overcurrent protection: limits the maximum inductor current and:

– Voltage over switching NMOS is monitored; voltages too high turn off the switch.

3. Feedback break protection: prevents uncontrolled operation if FB pin is disconnected.

4. Duty cycle limiting done with digital control.

1 MHz clock

VIN

Duty control

VOUT

SW

FB

UVCOMP

2V

R

+

S

OVPCOMP

R

+

-

RESETCOMP

+

-

+

ERRORAMP

R

+

SLOPER

SWITCH

R

+ OLPCOMP

-

ACTIVE

LOAD

R

R

LOOPC

+

-

OCPCOMP

IMAX

Figure 20. Boost Converter Topology

7.3.3.1 Boost Control

User can set the boost converter to standby mode by writing the register bit low. When

is written high, the converter starts for 50 ms in low current PWM mode and then goes to normal PWM mode.

User can control the boost output voltage by boost output boost_output (05H) register.

Table 7. Boost Output Voltage Control

BOOST OUTPUT [7:0]

REGISTER 0DH

BOOST OUTPUT

VOLTAGE (TYPICAL)

Bin

Dec

00101

5

5V

00110

6

6V

00111

7

7V

...

...

...

01100

12

12 V

01101

13

13 V

01110

14

14 V

...

...

...

10010

18

18 V

10011

19

19 V

10100

20

20 V

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

17

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

If register value is lower than 5, then value of 5 is used internally. If register value is higher than 20, then value of

20 is used internally.

7.3.3.2 Adaptive Output Voltage Control

When automatic boost voltage control is selected using the bit in the Control (06H) register, the

user-defined boost output voltage is ignored. The boost output voltage is adjusted for sufficient operating

headroom by monitoring all enabled LED driver outputs. The boosted voltage is adjusted so that the lowest driver

voltage is from 0.85 V to 1.35 V when the LED output currents are below 30 mA and from 1 V to 1.5V when any

LED current is above 30 mA. The output voltage range is from 5 V to 20 V in adaptive mode.

The adaptive voltage control helps saving energy by always setting the boost voltage to minimum sufficient

value. It eliminates the need for extra voltage margins due to LED forward voltage variation or temperature

variation. With very small brightness settings, when the PWM pulses in LED outputs are very narrow, the

adaptive voltage setting gives higher than necessary boost voltage. This does not harm the overall efficiency,

because this happens only at low power levels.

After reset the adaptive control is on by default. In stand-alone mode the adaptive output voltage is always used.

7.4 Device Functional Modes

The LP5520 has three different operating modes: manual mode, automatic mode, and stand-alone mode.

Automatic mode has two sub modes: normal mode and sequential mode. In manual and automatic modes the

device is controlled through the serial interface. In stand-alone mode only BRC input must be controlled, and all

registers have the default values. The modes are controlled according Table 8.

Table 8. Device Operating Modes Control

(RBG control bit 3)

(RBG control bits 6 and 7)

0

00

Manual mode

1

00

Automatic mode, normal operation (overlapping)

1

01, 10, or 11

DEVICE OPERATING MODE

Automatic mode, sequential operation with 2, 3, or 4 pulses per sequence

7.4.1 Manual Mode

In the manual mode the automatic LED intensity adjustment is not in use. The internal PWM control is disabled,

and the LEDs are driven with DC current. The user can set the LED currents through the serial port using three

current control registers, current_control_R/G/B, and use the external PWM control inputs to adjust LED

intensities if needed. There is an independent PWM control pin for each output. If PWM control is not used, the

PWMR, PWMG, and PWMR inputs must be tied to the VDDIO. All the functions implemented with the internal

PWM control are unavailable in manual mode (logarithmic brightness control from PWM Control register,

temperature compensation, fading, sequential mode).

7.4.2 Automatic Mode

In the automatic mode the LED intensities are controlled with the 12-bit PWM values obtained from the EEPROM

memory according to the temperature information. PWM values are stored at 16°C intervals for the

–40°C to +120°C temperature range, and the PWM values for the intermediate temperatures are linearly

interpolated.

When creating white light from a RGB LED, the intention is to program PWM values, which keep the individual

LED intensities constant in all temperatures. For possible other applications, other kind of PWM behavior can be

programmed. The variable parameter can be other than temperature if the sensor is changed to, for example, a

light sensor.

12-bit ADC is used for the measurements. The ADC has two inputs: S1_IN and S2_IN. The temperature

measurement result from the S1_IN input is converted to EEPROM address using the sensor calibration data

from EEPROM. This EEPROM address is then used to get the PWM values for each output. The second input

S2_IN can be used for example for ambient light measurement. The ADC data from selected input can be read

through the serial interface. Control bit can be used to select which input is used for compensation.

18

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

Current setting for each LED comes from EEPROM in the automatic mode. The same current values must be

programmed as were used in the calibration. Current control range is from 0 to 60 mA with 8-bit resolution and

the step size is 235 µA.

Common brightness control for all LEDs can be done using the pwm_brightness (05H) register. The

pwm_brightness register makes 8 level logarithmic brightness control with 3 bits. An automatic fade function

allows smooth turnon, turnoff, and brightness changes of the LEDs. White balance is maintained during fading.

A brightness correction value can be given for each LED. The PWM value obtained from the EEPROM memory

is multiplied by this correction value. This feature can be used for example for LED aging compensation or for

color adjustment by user. These values are kept in R_correction (0AH), G_correction (0BH) and B_correction

(0CH) registers. The correction multiplier can be between 0 and 2.

Due to LED self-heating, the temperature sensor and the LED temperatures will differ. The difference depends

on the thermal structure of the display module and the distance between the sensor and the LEDs. This

temperature difference can be compensated by storing the temperature difference value at highest power (100%

red LED PWM) in the EEPROM memory. The system then corrects the measured temperature based on the

actual PWM value used. The correction assumes that the red LED PWM value is representing the whole RGB

LED power consumption.

Sequential (non-overlapping) drive is possible using external PWM control inputs to trigger a new sequence in

each LED output. 60 mA maximum current setting makes possible 20 mA maximum averaged current for each

output in the non-overlapping mode.

7.4.3 Stand-Alone Mode

In stand-alone mode the operation is controlled through a single PWM brightness input, BRC. After power-up or

reset the LP5520 is ready for stand-alone operation without any setup through the serial interface. The standalone mode is entered with a rising edge in the BRC input. The boost converter operates in adaptive mode. The

LED current settings are loaded from EEPROM. The LED brightness is controlled with a PWM signal in the BRC

input. The BRC PWM frequency must be from 2 to 10 kHz. The PWM signal in the BRC input is not used as

such for the LED outputs, but it is converted to 3-bit value and a logarithmic brightness control is based on this 3bit value, as shown in Table 9. There is hysteresis in the conversion to avoid blinking when the BRC duty cycle is

close to a threshold. When the PWM pulses end in the BRC input and the input stays low, the circuit goes to the

standby mode.

Figure 21 shows the waveforms in BRC input and ROUT output in the stand-alone mode. The circuit is in

standby mode until the first rising edge in BRC input is detected. The circuit starts up, and the outputs activate

after 30 ms from the first rising edge in BRC. The BRC frequency is assumed to 2 kHz in this example giving 0.5

ms BRC period. When the duty cycle changes in BRC, it takes two BRC periods before the change is reflected in

the output. When BRC goes permanently low, the circuit enters standby mode after 15 ms from the last BRC

pulse.

All controls through the serial interface can be used in the stand-alone mode. In Automatic and Manual mode the

control bit must be written high and BRC input kept low to prevent the LP5520 device from entering

stand-alone mode.

Table 9. Stand-Alone Mode Brightness Control

BRC DUTY CYCLE THRESHOLD VALUES (%)

INCREASING

INTENSITY

(% of maximum)

DECREASING

RECOMMENDED BRC PWM CONTROL VALUES

INCREASING

0

off

DECREASING

0

1

15

0.8

10

10

20

28

1.6

28

22

35

42

3.1

40

32

48

52

6.3

53

47

58

62

12.5

63

58

68

75

25

75

70

82

90

50

88

85

100

99

97

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

19

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

BRC

period

200 Ps

2 periods

BRC

ROUT

50 Ps

30 ms

Turn on delay

15 ms

Turn off

delay

Change

delay

PWM

cycle

Figure 21. LP5520 Control and Output Waveforms in Stand-Alone Mode

L1

2.9 ± 5.5V

+

CVDDA

CVDDD

-

100 nF

100 nF

CVLDO

VDDD

VLDO

1 PF

CIN

4.7 PF

4.7 PH

VDDA

ADAPTIVE

5 ± 20V

SW

LP5520

S1_IN

TEMP

SENSOR

LM20

S2_IN

ADC

ANALOG

SUPPORT

CVDDIO

SCK/SCL

100 nF

SI/A0

SO

IFSEL

NRST

COUT

10 PF

CURRENT

DACS

VDDIO

SS/SDA

FB

BOOST

SPI / I2C

INTERFACE

AND

CONTROL

CALIBRATION

EEPROM

COLOR

PWM

LOGIC

PWMR

PWMG

PWMB

BRC

LED

DRIVERS

ROUT

20 mA

GOUT

20 mA

BOUT

20 mA

PWM INPUT

ON/OFF/

BRIGHTNESS

GND_T

GND_A

GND_LED

GND_SW

Figure 22. LP5520 Connections in Stand-Alone Mode

20

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

7.4.4 Start-Up Sequence

RESET:

In the RESET mode all the internal registers are reset to the default values, and the chip goes to

STANDBY mode after reset. control bit is low after reset by default. Reset is entered

always if NRST input is low or internal power on reset (POR) is active. POR activates during the

chip start-up or when the supply voltage VDD falls below 1.5 V. Once VDD rises above 1.5 V, POR

inactivates, and the device continues to the STANDBY mode.

STANDBY: The STANDBY mode is entered if the register bit is LOW. This is the low-power

consumption mode, when all circuit functions are disabled. Registers can be written in this mode,

and the control bits are effective immediately after power up.

STARTUP: When bit is written high or there is a rising edge in the BRC input, the INTERNAL

STARTUP SEQUENCE powers up all the needed internal blocks (Vref, Bias, Oscillator, etc.). To

ensure the correct initialization, a 10-ms delay is generated by the internal state-machine after the

trim EEPROM values are read. If the chip temperature rises too high, the thermal shutdown (TSD)

disables the chip operation, and STARTUP mode is entered until no TSD event is present.

BOOST STARTUP: Soft start for boost output is generated in the BOOST STARTUP mode. The boost output is

raised in PWM mode during the 20-ms delay generated by the state machine. All LED outputs are

off during the 20-ms delay to ensure smooth start-up. The boost start-up is entered from internal

start-up sequence if is HIGH or from Normal mode when is written

HIGH.

NORMAL:

During NORMAL mode the user controls the chip using the control registers or the BRC input in

stand-alone mode. The registers can be written in any sequence and any number of bits can be

altered in a register in one write.

RESET

NSTBY = L and NRST = H

NRST = L

or

POR = H

STANDBY

NRST = H

and

NSTBY = H or BRC = H

NSTBY = L or BRC = L

and

NRST = H

INTERNAL

STARTUP SEQUENCE

TSD = H

VREF = 95% OK

1

EEPROM AND EEPROM

READING (~1 ms)

~10 ms DELAY

1

EN_BOOST = H

EN_BOOST = L

1

BOOST STARTUP

EN_BOOST

1

RISING EDGE

~20 ms DELAY

NORMAL MODE

1) TSD = L

Figure 23. Device Functional Modes

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

21

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

7.5 Programming

7.5.1 Control Interface

The LP5520 supports two different interface modes:

• SPI interface (4-wire, serial), and

• I2C-compatible interface (2-wire, serial)

User can define the serial interface by IF_SEL pin. IF_SEL = 0 selects the I2C mode.

7.5.1.1 I2C Compatible Interface

7.5.1.1.1 I2C Signals

The serial interface is in I2C mode when IF_SEL = 0. The SCL pin is used for the I2C clock and the SDA pin is

used for bidirectional data transfer. Both these signals need a pullup resistor according to I2C specification. The

values of the pullup resistors are determined by the capacitance of the bus (typical resistance is 1.8 kΩ). Signal

timing specifications are shown in I2C Timing Parameters .

7.5.1.1.2 I2C Data Validity

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of

the data line can only be changed when CLK is LOW.

SCL

SDA

data

change

allowed

data

valid

data

change

allowed

data

valid

data

change

allowed

Figure 24. I2C Signals: Data Validity

7.5.1.1.3 I2C Start and Stop Conditions

START and STOP bits classify the beginning and the end of the I2C session. START condition is defined as SDA

signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA

transitioning from LOW to HIGH while SCL is HIGH. The I2C master always generates START and STOP bits.

The I2C bus is considered to be busy after START condition and free after STOP condition. During data

transmission, I2C master can generate repeated START conditions. First START and repeated START

conditions are equivalent, function-wise.

SDA

SCL

S

P

START condition

STOP condition

Figure 25. I2C Start and Stop Conditions

7.5.1.1.4 Transferring Data

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first.

Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated

by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver

must pull down the SDA line during the 9th clock pulse, signifying an acknowledge. A receiver which has been

addressed must generate an acknowledge after each byte has been received.

22

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

Programming (continued)

After the START condition, the I2C master sends a chip address. This address is seven bits long followed by an

eighth bit which is a data direction bit (R/W). The LP5520 address is 20h when SI=0 and 21h when SI=1. For the

eighth bit, a 0 indicates a WRITE and a 1 indicates a READ. The second byte selects the register to which the

data is written. The third byte contains data to write to the selected register.

MSB

LSB

ADR6

Bit7

ADR5

bit6

ADR4

bit5

ADR3

bit4

ADR2

bit3

ADR1

bit2

ADR0

bit1

R/W

bit0

2

I C SLAVE address (chip address)

Figure 26. I2C Chip Address

ack from slave

ack from slave

start

msb Chip Address lsb

w

ack

msb Register Add lsb

ack

w

ack

addr = 00h

ack

msb

ack from slave

DATA

lsb

ack

stop

ack

stop

SCL

SDA

start

Id = 20h or 21H

address 00h ± data 41h

w = write (SDA = 0)

r = read (SDA = 1)

ack = acknowledge (SDA pulled down by either master or slave)

rs = repeated start

id = 7-bit chip address, 20h when SI=0 and 21h when SI=1 for LP5520.

Figure 27. I2C Write Cycle

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in

the I2C Read Cycle waveform.

ack from slave

msb Chip Address lsb

start

w

ack from slave repeated start

msb Register Add lsb

ack from slave

rs

msb Chip Address lsb

rs

Id = 20h or 21h

r

data from slave noack from master

msb

DATA

lsb

stop

SCL

SDA

start

Id = 20h or 21h

w ack

addr = 05h

ack

no

r ack Address 05h - data 08h ack stop

Figure 28. I2C Read Cycle

7.5.1.2 SPI Interface

The LP5520 is compatible with SPI serial-bus specification, and it operates as a slave. The transmission consists

of 16-bit write and read cycles. One cycle consists of 7 address bits, 1 read/write (RW) bit, and 8 data bits. RWbit high state defines a write cycle and low defines a read cycle. SO output is normally in high-impedance state,

and it is active only when data is sent out during a read cycle. The address and data are transmitted MSB first.

The slave select signal (SS) must be low during the cycle transmission. SS resets the interface when high, and it

must be taken high between successive cycles. Data is clocked in on the rising edge of the SCK clock signal,

while data is clocked out on the falling edge of SCK.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

23

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

Programming (continued)

SS

SCK

A6

SI

A5

A4

A3

A2

A1

A0

1

R/W

D7

D6

D5

D4

D3

D2

D1

D0

D2

D1

D0

SO

Figure 29. SPI Write Cycle

SS

SCK

SI

A6

A5

A4

A3

A2

A1

A0

R/W

0

Don't Care

D7

SO

D6

D5

D4

D3

Figure 30. SPI Read Cycle

7.5.1.2.1 SPI Incremental Addressing

The LP5520 supports incremental addressing for memory read and write.

7.5.2 EEPROM Memory

The 1-kbit calibration EEPROM memory is organized as 128 × 8 bits. It stores the 12-bit calibration PWM values

for each output at 16°C intervals. Ten temperature points are used to cover the range from –40 to +120°C. The

temperature or light sensor calibration data, self-heating factor, and LED currents are also stored in the memory.

The memory contents and detailed memory map are shown in Table 10 and Table 11.

Table 10. EEPROM Contents

DATA

24

LENGTH

TOTAL BITS

10 PWM values for red

12

120

10 coefficients for red between the points

8

80

10 PWM values for green

12

120

10 coefficients for green between the points

8

80

10 PWM values for blue

12

120

10 coefficients for blue between the points

8

80

0°C reading for temperature sensor

12

12

Coefficient for temperature sensor

12

12

Maximum self-heating (100% red PWM)

8

8

Default current for ROUT

8

8

Default current for GOUT

8

8

Default current for BOUT

8

8

Free memory for user data

8

368

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

Table 11. EEPROM Memory Map

ADDRESS

BITS [7:4]

BITS [3:0]

DEFINITION

00

RB0[7:0]

Base PWM value for red

(8 LSB bits)

–40...–25

01

RB1[7:0]

02

RB2[7:0]

03

RB3[7:0]

8...23

04

RB4[7:0]

24..39

05

RB5[7:0]

40...55

06

RB6[7:0]

56...71

07

RB7[7:0]

72...87

08

RB8[7:0]

88...103

09

RB9[7:0]

from 104

0a

GB0[7:0]

0b

GB1[7:0]

0c

GB2[7:0]

0d

GB3[7:0]

8...23

0e

GB4[7:0]

24..39

–24...–9

–8...+7

Base PWM value for green

(8 LSB bits)

–40...–25

–24...–9

–8...+7

0f

GB5[7:0]

40...55

10

GB6[7:0]

56...71

11

GB7[7:0]

72...87

12

GB8[7:0]

88...103

13

GB9[7:0]

from 104

14

BB0[7:0]

15

BB1[7:0]

16

BB2[7:0]

17

BB3[7:0]

8...23

18

BB4[7:0]

24..39

19

BB5[7:0]

40...55

1a

BB6[7:0]

56...71

1b

BB7[7:0]

72...87

Base PWM value for blue

(8 LSB bits)

–40...–25

–24...–9

–8...+7

1c

BB8[7:0]

88...103

1d

BB9[7:0]

from 104

1e

LM20K[7:0]

1f

LM20B[7:0]

Scaling values for LM20 sensor

K

B

20

Not used

...

3f

40

RC0[7:0]

41

RC1[7:0]

Coefficient PWM value for red

–40...–25

–24...–9

42

RC2[7:0]

–8...+7

43

RC3[7:0]

8...23

44

RC4[7:0]

24..39

45

RC5[7:0]

40...55

46

RC6[7:0]

56...71

47

RC7[7:0]

72...87

48

RC8[7:0]

88...103

49

RC9[7:0]

From 104

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

25

�LP5520

SNVS440B – MAY 2007 – REVISED MARCH 2016

www.ti.com

Table 11. EEPROM Memory Map (continued)

ADDRESS

BITS [7:4]

BITS [3:0]

DEFINITION

4a

GC0[7:0]

4b

GC1[7:0]

–24...–9

4c

GC2[7:0]

–8...+7

4d

GC3[7:0]

8...23

4e

GC4[7:0]

24..39

4f

GC5[7:0]

40...55

50

GC6[7:0]

56...71

51

GC7[7:0]

72...87

52

GC8[7:0]

88...103

53

GC9[7:0]

54

BC0[7:0]

55

BC1[7:0]

–24...–9

56

BC2[7:0]

–8...+7

57

BC3[7:0]

8...23

58

BC4[7:0]

24..39

59

BC5[7:0]

40...55

5a

BC6[7:0]

56...71

5b

BC7[7:0]

72...87

5c

BC8[7:0]

88...103

5d

BC9[7:0]

5e

SHF[7:0]

Coefficient PWM value for green

–40...–25

From 104

Coefficient PWM value for blue

–40...–25

From 104

Self-heating factor

5f

RED_CUR

Red LED current

60

GREEN_CUR

Green LED current

61

BLUE_CUR

Blue LED current

62

Not used

...

6f

70

LM20B[11:8]

LM20K[11:8]

Scaling values for LM20 sensor

71

BB9[11:8]

BB8[11:8]

Base PWM value for blue (high bits)

72

BB7[11:8]

BB6[11:8]

73

BB5[11:8]

BB4[11:8]

74

BB3[11:8]

BB2[11:8]

75

BB1[11:8]

BB0[11:8]

76

GB9[11:8]

GB8[11:8]

77

GB7[11:8]

GB6[11:8]

78

GB5[11:8]

GB4[11:8]

79

GB3[11:8]

GB2[11:8]

7a

GB1[11:8]

GB0[11:8]

7b

RB9[11:8]

RB8[11:8]

7c

RB7[11:8]

RB6[11:8]

7d

RB5[11:8]

RB4[11:8]

7e

RB3[11:8]

RB2[11:8]

7f

RB1[11:8]

RB0[11:8]

Base PWM value for green (high bits)

Base PWM value for red (high bits)

The EEPROM data can be read, written, and erased through the serial interface. The boost converter is used to

generate the write and erase voltage for the memory. All operations are done in page mode. The page address

has to be written in the EEPROM_control register before access to the EEPROM. Incremental access can be

used both in I2C and SPI modes to speed up access. During EEPROM access the control bit in rgb

control register must be low.

26

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

Product Folder Links: LP5520

�LP5520

www.ti.com

SNVS440B – MAY 2007 – REVISED MARCH 2016

The EEPROM has 4 pages; only one page at time can be mirrored at the register map. For getting access to

page, the number of page must be set by bits in the EEPROM_control register(0DH). The page

register address range is from 40H to 5FH.

Table 12. EEPROM Pages

(bits1-0)

00

page0 (00H-1FH)

01

page1 (20H-3FH)

10

page2 (40H-5FH)

11

page3 (60H-7FH)

The EEPROM consists of two types of memory, 128 × 8 EEPROM (non volatile memory) and 128 × 8

synchronous random access memory (SRAM). The EEPROM is used to store calibrated RGB control values

when the system is powered off. SRAM is used as working memory during operation.

EEPROM map

SRAM map

00H

ee_page[1:0]

00H

page0

page0

00

1FH

1FH

20H

20H

Register map

40H

page1

page1

01

3FH

40H

5FH

3FH

40H

page2

page2

10

5FH

60H

5FH

60H

page3

page3

11

7FH

7FH

Figure 31. EEPROM Memory

EEPROM content is copied into SRAM always when the chip is taken from stand-by mode to active mode.

Copying to SRAM can also be made during operation by writing the bit high and low in the EEPROM

control (0DH) register. For reading the data from the SRAM, the page number must be set with

bits and the page read from addresses 40H – 5FH.

The EEPROM must be erased before programming. The erase command erases one page at time, which must

be selected with bits. This operation starts after setting and resetting and takes

about 100 ms after rising bit. During erasing bit of the EEPROM_CONTROL register is

low. Corresponding SRAM area is erased with this operation also. and can be set only

one command at a time (erase or program).

During programming the content of SRAM is copied to EEPROM, EEPROM programming cycle has two steps.

At first, write the whole content of the SRAM, all 4 pages. The whole page can be written during one SPI/I2C

cycle in the auto-increment mode. Second step is programming the EEPROM. This operation starts after writing

high and back low and takes about 100 ms after rising bit. During programming

bit of the EEPROM_CONTROL register is low. For EEPROM erasing and programming the chip has