LP5990

www.ti.com

SNVS438B – APRIL 2007 – REVISED DECEMBER 2007

LP5990 Micropower 200mA CMOS Low Dropout Voltage Regulator

Check for Samples: LP5990

FEATURES

DESCRIPTION

•

•

•

The LP5990 regulator is designed to meet the

requirements of portable, battery-powered systems

providing an accurate output voltage, low noise and

low quiescent current.

1

2

•

•

•

•

•

•

•

•

•

•

Operation from 2.2V to 5.5V Input

±1% Accuracy Over Temp Range

Output Voltage from 0.8V to 3.6V in 50mV

Increments

30 μA Quiescent Current (Enabled)

10nA Quiescent Current (Disabled)

160mV Dropout at 200mA Load

60 μVRMSOutput Voltage Noise

60 μs Start-Up Time

500μs Shut-Down Time

PSRR 55 dB at 10 kHz

Stable with 0402 1.0µF Ceramic Capacitors

Logic Controlled Enable

Thermal–Overload and Short–Circuit

Protection

The LP5990 will provide a 1.8V output from a low

input voltage of 2.2V and can provide 200mA to an

external load.

When switched into shutdown mode via a logic signal

at the enable pin, the power consumption is reduced

to virtually

zero.

Fast shut-down is achieved by the push pull

architecture.

The LP5990 is designed to be stable with space

saving 0402 ceramic capacitors as small as 1µF, this

gives an overall solution size of < 2.5mm 2.

Performance is specified for a -40°C to 125°C

junction temperature range.

APPLICATIONS

•

•

Cellular Phones

Hand–Held Information Appliances

The device is available in DSBGA Package (0.4mm

pitch)

and

is

available

with

1.2V,1.3V,1.8V,2.8V,3.0V,3.3V and 3.6V outputs.

Lower voltage options down to 0.8V are available on

request. For all other output voltage options please

contact your local TI sales office.

PACKAGE

•

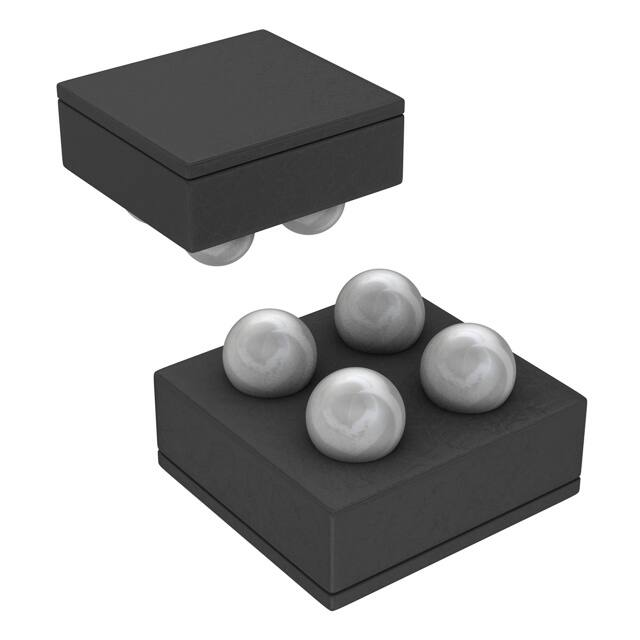

4-Bump DSBGA, 0.4 mm Pitch 866 µm x 917

µm (Lead Free)

TYPICAL APPLICATION CIRCUIT

VIN

VIN

1.0 µF

CIN

VOUT

VOUT

LP5990

1.0 µF

COUT

VEN

VEN

Capacitor Case

Size = 0402

GND

GND

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2007, Texas Instruments Incorporated

�LP5990

SNVS438B – APRIL 2007 – REVISED DECEMBER 2007

www.ti.com

CONNECTION DIAGRAMS

Figure 1. 4-Bump Thin DSBGA Package, 0.4mm pitch

Package Number YFQ0004CEA

VIN

VEN

VEN

VIN

B2

A2

A2

B2

B1

A1

GND

A1

GND

VOUT

VOUT

Bottom View

B1

Top View

The actual physical placement of the package marking will vary from part to part.

PIN DESCRIPTIONS

Pin No.

Symbol

Name and Function

DSBGA

VEN

Enable input; disables the regulator when ≤ 0.35V. Enables the regulator when ≥ 1.0V.

A1

GND

Common ground.

B1

VOUT

Output voltage. A 1.0 μF Low ESR capacitor should be connected to this Pin. Connect

this output to the load circuit.

B2

VIN

A2

Input voltage supply. A 1.0 µF capacitor should be connected at this input.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

ABSOLUTE MAXIMUM RATINGS

(1) (2) (3)

VIN Pin: Input Voltage

-0.3 to 6.0V

VOUT Pin: Output Voltage

-0.3 to (VIN + 0.3V) to 6.0V (max)

VEN Pin: Enable Input Voltage

Continuous Power Dissipation

-0.3 to 6.0V (max)

(4)

Internally Limited

Junction Temperature (TJMAX)

150°C

Storage Temperature Range

-65 to 150°C

Maximum Lead Temperature (Soldering, 10 sec.)

ESD Rating

(5)

260°C

Human Body Model

Machine Model

(1)

(2)

(3)

(4)

(5)

2

2 kV

200V

Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under

which operation of the device is specified. Operating Ratings do not imply specified performance limits. For specified performance limits

and associated test conditions, see the Electrical Characteristics tables.

All voltages are with respect to the potential at the GND pin.

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and

specifications.

Internal thermal shutdown circuitry protects the device from permanent damage.

The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF

capacitor discharged directly into each pin. MIL-STD-883 3015.7

Submit Documentation Feedback

Copyright © 2007, Texas Instruments Incorporated

Product Folder Links: LP5990

�LP5990

www.ti.com

SNVS438B – APRIL 2007 – REVISED DECEMBER 2007

OPERATING RATINGS

(1) (2)

,

VIN: Input Voltage Range

2.2V to 5.5V

VEN: Enable Voltage Range

Recommended Load Current

0 to 5.5V (max)

(3)

0 to 200 mA

Junction Temperature Range (TJ)

Ambient Temperature Range (TA)

(1)

-40°C to +125°C

(3)

-40°C to +85°C

Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under

which operation of the device is specified. Operating Ratings do not imply specified performance limits. For specified performance limits

and associated test conditions, see the Electrical Characteristics tables.

All voltages are with respect to the potential at the GND pin.

In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may

have to be derated. Maximum ambient temperature (TA-MAX) is dependent on the maximum operating junction temperature (TJ-MAX-OP =

125°C), the maximum power dissipation of the device in the application (PD-MAX), and the junction-to ambient thermal resistance of the

part/package in the application (θJA), as given by the following equation: TA-MAX = TJ-MAX-OP – (θJA × PD-MAX). See applications section.

(2)

(3)

THERMAL PROPERTIES

Junction to Ambient Thermal Resistance θJA (1)

JEDEC Board (DSBGA)

(2)

100.6°C/W

4L Cellphone Board (DSBGA)

(1)

174.8°C/W

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power

dissipation exists, special care must be paid to thermal dissipation issues in board design.

Detailed description of the board can be found in JESD51-7

(2)

ELECTRICAL CHARACTERISTICS

Limits in standard typeface are for TA = 25°C. Limits in boldface type apply over the full operating junction temperature range

(-40°C ≤ TJ ≤ +125°C). Unless otherwise noted, specifications apply to the LP5990 Typical Application Circuit (pg. 1) with: VIN

= VOUT (NOM) + 1.0V, or 2.2V, whichever is higher. VEN = 1.0V, CIN = COUT = 1.0 μF, IOUT = 1.0 mA. (1), (2)

Symbol

Parameter

Conditions

Min

Typ

VIN

Input Voltage

ΔVOUT

Output Voltage Tolerance

VIN = (VOUT(NOM) + 1.0V) to 5.5V

Line Regulation

VIN = (VOUT(NOM) + 1.0V) to 5.5V, IOUT = 1

mA

1

Load Regulation

IOUT = 1 mA to 200 mA

5

ILOAD

Load Current

See

(3)

Quiescent Current

V

−1

1

%

VEN = 1.0V, IOUT = 0 mA

0.01

Dropout Voltage (5)

IOUT = 200 mA

160

ISC

Short Circuit Current Limit

See (6)

600

Output Noise Voltage

TSHUTDOWN

(7)

Thermal Shutdown

mV

(7)

75

35

VEN =

很抱歉,暂时无法提供与“LP5990TM-1.8/NOPB”相匹配的价格&库存,您可以联系我们找货

免费人工找货