���������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

D Low Supply Voltage Range 1.8 V to 3.6 V

D Ultralow-Power Consumption:

D Family Members Include:

D

D

D

D

D

D

− Active Mode: 200 µA at 1 MHz, 2.2 V

− Standby Mode: 0.8 µA

− Off Mode (RAM Retention): 0.1 µA

Wake-Up From Standby Mode in less

than 6 µs

16-Bit RISC Architecture, 125 ns

Instruction Cycle Time

Basic Clock Module Configurations:

− Various Internal Resistors

− Single External Resistor

− 32 kHz Crystal

− High Frequency Crystal

− Resonator

− External Clock Source

16-Bit Timer_A With Three

Capture/Compare Registers

Serial Onboard Programming,

No External Programming Voltage

Needed

MSP430F110:

D

1KB + 128B Flash Memory

128B RAM

MSP430F112: 4KB + 256B Flash Memory

256B RAM

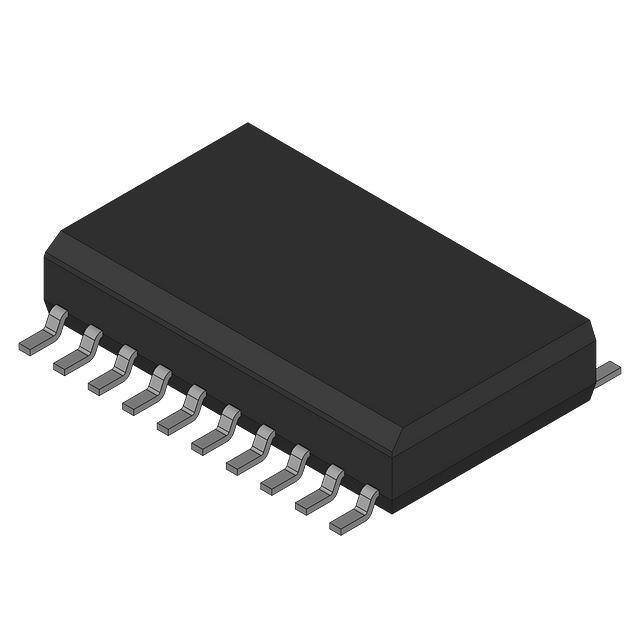

Available in a 20-Pin Plastic Small-Outline

Wide Body (SOWB) Package and 20-Pin

Plastic Thin Shrink Small-Outline Package

(TSSOP)

For Complete Module Descriptions, Refer

to the MSP430x1xx Family User’s Guide,

Literature Number SLAU049

DW OR PW PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

TEST

VCC

P2.5/Rosc

VSS

XOUT/TCLK

XIN

RST/NMI

P2.0/ACLK

P2.1/INCLK

P2.2/TA0

20

19

18

17

16

15

14

13

12

11

P1.7/TA2/TDO/TDI

P1.6/TA1/TDI

P1.5/TA0/TMS

P1.4/SMCLK/TCK

P1.3/TA2

P1.2/TA1

P1.1/TA0

P1.0/TACLK

P2.4/TA2

P2.3/TA1

description

The Texas Instruments MSP430 family of ultralow power microcontrollers consist of several devices featuring

different sets of peripherals targeted for various applications. The architecture, combined with five low power

modes is optimized to achieve extended battery life in portable measurement applications. The device features

a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that attribute to maximum code efficiency.

The digitally controlled oscillator (DCO) allows wake-up from low-power modes to active mode in less than 6µs.

The MSP430F11x series is an ultralow-power mixed signal microcontroller with a built in 16-bit timer and

fourteen I/O pins.

Typical applications include sensor systems that capture analog signals, convert them to digital values, and then

process the data and display them or transmit them to a host system. Stand alone RF sensor front-end is another

area of application.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright 1999 − 2004, Texas Instruments Incorporated

���

���

��

��� ����������� �� !"��#�� �� �� $"%&�!����� '��#(

���'"!�� !������ �� �$#!���!������ $#� �)# �#��� �� �# ��

����"�#���

����'��' *������+( ���'"!���� $��!#����, '�#� ��� �#!#�����&+ ��!&"'#

�#����, �� �&& $����#�#��(

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

1

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

AVAILABLE OPTIONS

PACKAGED DEVICES

TA

−40°C to 85°C

PLASTIC

20-PIN SOWB

(DW)

PLASTIC

20-PIN TSSOP

(PW)

MSP430F110IDW

MSP430F112IDW

MSP430F110IPW

MSP430F112IPW

functional block diagram

XIN

XOUT

VCC

VSS

P1

RST/NMI

JTAG

ROSC

Oscillator

System

Clock

ACLK

4KB Flash

256B RAM

SMCLK

1KB Flash

128B RAM

P2

8

I/O Port 1

8 I/Os, with

Interrupt

Capability

6

I/O Port 2

6 I/Os, with

Interrupt

Capability

MCLK

Test

MAB,

4 Bit

MAB,MAB,

16 Bit16-Bit

JTAG

CPU

MCB

Emulation

Module

Incl. 16 Reg.

Bus

Conv

MDB,

16-Bit

MDB,

16 Bit

MDB, 8 Bit

TEST

†

Watchdog

Timer

Timer_A3

POR

3 CC Reg

15/16-Bit

† A pulldown resistor of 30 kΩ is needed on F11x devices.

2

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

Terminal Functions

TERMINAL

NAME

NO.

I/O

DESCRIPTION

P1.0/TACLK

13

I/O

General-purpose digital I/O pin/Timer_A, clock signal TACLK input

P1.1/TA0

14

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI0A input, compare: Out0 output/BSL transmit

P1.2/TA1

15

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI1A input, compare: Out1 output

P1.3/TA2

16

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI2A input, compare: Out2 output

P1.4/SMCLK/TCK

17

I/O

General-purpose digital I/O pin/SMCLK signal output/test clock, input terminal for device programming

and test

P1.5/TA0/TMS

18

I/O

General-purpose digital I/O pin/Timer_A, compare: Out0 output/test mode select, input terminal for

device programming and test

P1.6/TA1/TDI

19

I/O

General-purpose digital I/O pin/Timer_A, compare: Out1 output/test data input terminal

P1.7/TA2/TDO/TDI†

20

I/O

General-purpose digital I/O pin/Timer_A, compare: Out2 output/test data output terminal or data input

during programming

P2.0/ACLK

8

I/O

General-purpose digital I/O pin/ACLK output

P2.1/INCLK

9

I/O

General-purpose digital I/O pin/Timer_A, clock signal at INCLK

P2.2/TA0

10

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI0B input, compare: Out0 output/BSL receive

P2.3/TA1

11

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI1B input, compare: Out1 output

P2.4/TA2

12

I/O

General-purpose digital I/O pin/Timer_A, compare: Out2 output

P2.5/ROSC

RST/NMI

3

I/O

General-purpose digital I/O pin/Input for external resistor that defines the DCO nominal frequency

7

I

Reset or nonmaskable interrupt input

TEST

1

I

Selects test mode for JTAG pins on Port1. Must be tied low with less than 30 kΩ.

VCC

VSS

2

XIN

6

Supply voltage

4

Ground reference

I

Input terminal of crystal oscillator

XOUT/TCLK

5

I/O Output terminal of crystal oscillator or test clock input

† TDO or TDI is selected via JTAG instruction.

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

3

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

short-form description

CPU

The MSP430 CPU has a 16-bit RISC architecture

that is highly transparent to the application. All

operations, other than program-flow instructions,

are performed as register operations in

conjunction with seven addressing modes for

source operand and four addressing modes for

destination operand.

Program Counter

PC/R0

Stack Pointer

SP/R1

SR/CG1/R2

Status Register

Constant Generator

The CPU is integrated with 16 registers that

provide reduced instruction execution time. The

register-to-register operation execution time is

one cycle of the CPU clock.

Four of the registers, R0 to R3, are dedicated as

program counter, stack pointer, status register,

and constant generator respectively. The

remaining registers are general-purpose

registers.

Peripherals are connected to the CPU using data,

address, and control buses, and can be handled

with all instructions.

instruction set

The instruction set consists of 51 instructions with

three formats and seven address modes. Each

instruction can operate on word and byte data.

Table 1 shows examples of the three types of

instruction formats; the address modes are listed

in Table 2.

CG2/R3

General-Purpose Register

R4

General-Purpose Register

R5

General-Purpose Register

R6

General-Purpose Register

R7

General-Purpose Register

R8

General-Purpose Register

R9

General-Purpose Register

R10

General-Purpose Register

R11

General-Purpose Register

R12

General-Purpose Register

R13

General-Purpose Register

R14

General-Purpose Register

R15

Table 1. Instruction Word Formats

Dual operands, source-destination

e.g. ADD R4,R5

R4 + R5 −−−> R5

Single operands, destination only

e.g. CALL

PC −−>(TOS), R8−−> PC

Relative jump, un/conditional

e.g. JNE

R8

Jump-on-equal bit = 0

Table 2. Address Mode Descriptions

ADDRESS MODE

Indirect

D

D

D

D

D

Indirect

autoincrement

Register

Indexed

Symbolic (PC relative)

Absolute

Immediate

NOTE: S = source

4

S D

D

D

D

D

SYNTAX

EXAMPLE

MOV Rs,Rd

MOV R10,R11

MOV X(Rn),Y(Rm)

MOV 2(R5),6(R6)

OPERATION

R10

−−> R11

M(2+R5)−−> M(6+R6)

MOV EDE,TONI

M(EDE) −−> M(TONI)

MOV &MEM,&TCDAT

M(MEM) −−> M(TCDAT)

MOV @Rn,Y(Rm)

MOV @R10,Tab(R6)

M(R10) −−> M(Tab+R6)

D

MOV @Rn+,Rm

MOV @R10+,R11

M(R10) −−> R11

R10 + 2−−> R10

D

MOV #X,TONI

MOV #45,TONI

D = destination

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

#45

−−> M(TONI)

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

operating modes

The MSP430 has one active mode and five software selectable low-power modes of operation. An interrupt

event can wake up the device from any of the five low-power modes, service the request and restore back to

the low-power mode on return from the interrupt program.

The following six operating modes can be configured by software:

D Active mode AM;

−

All clocks are active

D Low-power mode 0 (LPM0);

−

CPU is disabled

ACLK and SMCLK remain active. MCLK is disabled

D Low-power mode 1 (LPM1);

−

CPU is disabled

ACLK and SMCLK remain active. MCLK is disabled

DCO’s dc-generator is disabled if DCO not used in active mode

D Low-power mode 2 (LPM2);

−

CPU is disabled

MCLK and SMCLK are disabled

DCO’s dc-generator remains enabled

ACLK remains active

D Low-power mode 3 (LPM3);

−

CPU is disabled

MCLK and SMCLK are disabled

DCO’s dc-generator is disabled

ACLK remains active

D Low-power mode 4 (LPM4);

−

CPU is disabled

ACLK is disabled

MCLK and SMCLK are disabled

DCO’s dc-generator is disabled

Crystal oscillator is stopped

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

5

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

interrupt vector addresses

The interrupt vectors and the power-up starting address are located in the memory with an address range of

0FFFFh-0FFE0h. The vector contains the 16-bit address of the appropriate interrupt handler instruction

sequence.

INTERRUPT SOURCE

INTERRUPT FLAG

SYSTEM INTERRUPT

WORD ADDRESS

PRIORITY

Power-up

External reset

Watchdog

WDTIFG (Note1)

KEYV (Note 1)

Reset

0FFFEh

15, highest

NMI

Oscillator fault

Flash memory access violation

NMIIFG (Notes 1 and 5)

OFIFG (Notes 1 and 5)

ACCVIFG (Notes 1 and 5)

(non)-maskable,

(non)-maskable,

(non)-maskable

0FFFCh

14

0FFFAh

13

0FFF8h

12

0FFF6h

11

Watchdog timer

WDTIFG

maskable

0FFF4h

10

Timer_A3

TACCR0 CCIFG

(Note 2)

maskable

0FFF2h

9

Timer_A3

TACCR1 and TACCR2

CCIFGs, TAIFG

(Notes 1 and 2)

maskable

0FFF0h

8

0FFEEh

7

0FFECh

6

0FFEAh

5

0FFE8h

4

I/O Port P2

(eight flags − see Note 3)

P2IFG.0 to P2IFG.7

(Notes 1 and 2)

maskable

0FFE6h

3

I/O Port P1

(eight flags)

P1IFG.0 to P1IFG.7

(Notes 1 and 2)

maskable

0FFE4h

2

0FFE2h

1

0FFE0h

0, lowest

NOTES: 1.

2.

3.

4.

5.

6

Multiple source flags

Interrupt flags are located in the module

There are eight Port P2 interrupt flags, but only six Port P2 I/O pins (P2.0−5) are implemented on the ’11x devices.

Nonmaskable: neither the individual nor the general interrupt enable bit will disable an interrupt event.

(non)-maskable: the individual interrupt enable bit can disable an interrupt event, but the general interrupt enable cannot.

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

special function registers

Most interrupt and module enable bits are collected into the lowest address space. Special function register bits

that are not allocated to a functional purpose are not physically present in the device. Simple software access

is provided with this arrangement.

interrupt enable 1 and 2

Address

7

6

0h

5

4

ACCVIE

NMIIE

rw-0

WDTIE:

OFIE:

NMIIE:

ACCVIE:

Address

3

2

1

OFIE

rw-0

0

WDTIE

rw-0

rw-0

Watchdog Timer interrupt enable. Inactive if watchdog mode is selected. Active if Watchdog Timer

is configured in interval timer mode.

Oscillator fault enable

Nonmaskable interrupt enable

Flash access violation interrupt enable

7

6

5

6

5

4

3

2

4

3

2

1

0

01h

interrupt flag register 1 and 2

Address

7

02h

NMIIFG

rw-0

WDTIFG:

OFIFG:

NMIIFG:

Address

1

OFIFG

rw-1

0

WDTIFG

rw-(0)

Set on Watchdog Timer overflow (in watchdog mode) or security key violation.

Reset on VCC power-up or a reset condition at RST/NMI pin in reset mode.

Flag set on oscillator fault

Set via RST/NMI-pin

7

6

5

4

3

2

1

0

03h

Legend

rw:

rw-0,1:

rw-(0,1):

Bit can be read and written.

Bit can be read and written. It is Reset or Set by PUC.

Bit can be read and written. It is Reset or Set by POR.

SFR bit is not present in device.

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

7

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

memory organization

MSP430F110

FFFFh

FFE0h

FFDFh

Int. Vector

1 KB Flash

FC00h Segment0,1

MSP430F112

FFFFh

FFE0h

Int. Vector

FFDFh

4 KB

Main

Flash

Segment0−7 Memory

F000h

10FFh

1080h

0FFFh

0C00h

128B Flash

SegmentA

1 KB

Boot ROM

10FFh

2 × 128B

Information

Flash

Memory

1000h SegmentA,B

0FFFh

1 KB

Boot ROM

0C00h

02FFh

027Fh

0200h

01FFh

0100h

00FFh

0010h

000Fh

0000h

256B RAM

128B RAM

16b Per.

8b Per.

SFR

0200h

01FFh

16b Per.

0100h

00FFh

0010h

000Fh

0000h

8b Per.

SFR

bootstrap loader (BSL)

The MSP430 bootstrap loader (BSL) enables users to program the flash memory or RAM using a UART serial

interface. Access to the MSP430 memory via the BSL is protected by user-defined password. For complete

description of the features of the BSL and its implementation, see the Application report Features of the MSP430

Bootstrap Loader, Literature Number SLAA089.

BSL Function

DW & PW Package Pins

Data Transmit

14 - P1.1

Data Receive

10 - P2.2

flash memory

The flash memory can be programmed via the JTAG port, the bootstrap loader, or in-system by the CPU. The

CPU can perform single-byte and single-word writes to the flash memory. Features of the flash memory include:

D Flash memory has n segments of main memory and two segments of information memory (A and B) of 128

bytes each. Each segment in main memory is 512 bytes in size.

D Segments 0 to n may be erased in one step, or each segment may be individually erased.

D Segments A and B can be erased individually, or as a group with segments 0−n.

Segments A and B are also called information memory.

D New devices may have some bytes programmed in the information memory (needed for test during

manufacturing). The user should perform an erase of the information memory prior to the first use.

8

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

Segment0 w/

Interrupt Vectors

0FDFFh

0FC00h

Segment1

0FBFFh

0FA00h

Segment2

0F9FFh

0F800h

Segment3

0F7FFh

0F600h

Segment4

0F5FFh

0F400h

Segment5

0F3FFh

0F200h

Segment6

0F1FFh

0F000h

Segment7

010FFh

01080h

SegmentA

0107Fh

01000h

SegmentB

Information

Memory

0FFFFh

0FE00h

Flash Main Memory

flash memory (continued)

NOTE: All segments not implemented on all devices.

peripherals

Peripherals are connected to the CPU through data, address, and control busses and can be handled using

all instructions. For complete module descriptions, refer to the MSP430x1xx Family User’s Guide, literature

number SLAU049.

oscillator and system clock

The clock system is supported by the basic clock module that includes support for a 32768-Hz watch crystal

oscillator, an internal digitally-controlled oscillator (DCO) and a high frequency crystal oscillator. The basic clock

module is designed to meet the requirements of both low system cost and low-power consumption. The internal

DCO provides a fast turn-on clock source and stabilizes in less than 6 µs. The basic clock module provides the

following clock signals:

D Auxiliary clock (ACLK), sourced from a 32768-Hz watch crystal or a high frequency crystal.

D Main clock (MCLK), the system clock used by the CPU.

D Sub-Main clock (SMCLK), the sub-system clock used by the peripheral modules.

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

9

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

digital I/O

There are two 8-bit I/O ports implemented—ports P1 and P2 (only six P2 I/O signals are available on external

pins):

D

D

D

D

All individual I/O bits are independently programmable.

Any combination of input, output, and interrupt conditions is possible.

Edge-selectable interrupt input capability for all the eight bits of port P1 and six bits of port P2.

Read/write access to port-control registers is supported by all instructions.

NOTE:

Six bits of port P2, P2.0 to P2.5, are available on external pins − but all control and data bits for port

P2 are implemented.

watchdog timer

The primary function of the watchdog timer (WDT) module is to perform a controlled system restart after a

software problem occurs. If the selected time interval expires, a system reset is generated. If the watchdog

function is not needed in an application, the module can be configured as an interval timer and can generate

interrupts at selected time intervals.

timer_A3

Timer_A3 is a 16-bit timer/counter with three capture/compare registers. Timer_A3 can support multiple

capture/compares, PWM outputs, and interval timing. Timer_A3 also has extensive interrupt capabilities.

Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare

registers.

Timer_A3 Signal Connections

Input Pin Number

Device Input Signal

Module Input Name

13 - P1.0

TACLK

TACLK

ACLK

ACLK

SMCLK

SMCLK

9 - P2.1

INCLK

INCLK

14 - P1.1

TA0

CCI0A

TA0

CCI0B

DVSS

DVCC

GND

10 - P2.2

15 - P1.2

TA1

VCC

CCI1A

11 - P2.3

TA1

CCI1B

16 - P1.3

10

DVSS

DVCC

TA2

GND

VCC

CCI2A

ACLK (internal)

CCI2B

DVSS

DVCC

GND

Module Block

Module Output Signal

Timer

NA

14 - P1.1

18 - P1.5

CCR0

TA0

10 - P2.2

15 - P1.2

19 - P1.6

CCR1

TA1

11 - P2.3

16 - P1.3

20 - P1.7

CCR2

VCC

POST OFFICE BOX 655303

Output Pin Number

• DALLAS, TEXAS 75265

TA2

12 - P2.4

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

peripheral file map

PERIPHERALS WITH WORD ACCESS

Timer_A

Reserved

Reserved

Reserved

Reserved

Capture/compare register

Capture/compare register

Capture/compare register

Timer_A register

Reserved

Reserved

Reserved

Reserved

Capture/compare control

Capture/compare control

Capture/compare control

Timer_A control

Timer_A interrupt vector

TACCTL2

TACCTL1

TACCTL0

TACTL

TAIV

017Eh

017Ch

017Ah

0178h

0176h

0174h

0172h

0170h

016Eh

016Ch

016Ah

0168h

0166h

0164h

0162h

0160h

012Eh

TACCR2

TACCR1

TACCR0

TAR

Flash Memory

Flash control 3

Flash control 2

Flash control 1

FCTL3

FCTL2

FCTL1

012Ch

012Ah

0128h

Watchdog

Watchdog/timer control

WDTCTL

0120h

PERIPHERALS WITH BYTE ACCESS

Basic Clock

Basic clock sys. control2

Basic clock sys. control1

DCO clock freq. control

BCSCTL2

BCSCTL1

DCOCTL

058h

057h

056h

Port P2

Port P2 selection

Port P2 interrupt enable

Port P2 interrupt edge select

Port P2 interrupt flag

Port P2 direction

Port P2 output

Port P2 input

P2SEL

P2IE

P2IES

P2IFG

P2DIR

P2OUT

P2IN

02Eh

02Dh

02Ch

02Bh

02Ah

029h

028h

Port P1

Port P1 selection

Port P1 interrupt enable

Port P1 interrupt edge select

Port P1 interrupt flag

Port P1 direction

Port P1 output

Port P1 input

P1SEL

P1IE

P1IES

P1IFG

P1DIR

P1OUT

P1IN

026h

025h

024h

023h

022h

021h

020h

Special Function

SFR interrupt flag2

SFR interrupt flag1

SFR interrupt enable2

SFR interrupt enable1

IFG2

IFG1

IE2

IE1

003h

002h

001h

000h

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

11

����������

�

��

�

���� �

�������������

SLAS256D − NOVEMBER 1999 − REVISED SEPTEMBER 2004

absolute maximum ratings†

Voltage applied at VCC to VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.3 V to 4.1 V

Voltage applied to any pin (referenced to VSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.3 V to VCC+0.3 V

Diode current at any device terminal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±2 mA

Storage temperature, Tstg (unprogrammed device) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −55°C to 150°C

Storage temperature, Tstg (programmed device) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −40°C to 85°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE: All voltages referenced to VSS.

recommended operating conditions

MIN

Supply voltage during program execution, VCC (see Note 1)

1.8

Supply voltage during program/erase flash memory, VCC

2.7

Supply voltage, VSS

MAX

−40

LF mode selected, XTS=0

Watch crystal

V

3.6

V

85

°C

XT1 mode selected, XTS=1

Hz

450

8000

1000

8000

VCC = 1.8 V

dc

2

MHz

VCC = 2.2 V

dc

5

MHz

Crystal

Processor frequency f(system) (MCLK signal)

V

32 768

Ceramic resonator

UNITS

3.6

0

Operating free-air temperature range, TA

LFXT1 crystal frequency,

f(LFXT1) (see Note 2)

NOM

kHz

VCC = 3.6 V

dc

8

MHz

NOTES: 1. The LFXT1 oscillator in LF-mode requires a resistor of 5.1 MΩ from XOUT to VSS when VCC