ADS9817, ADS9815

SBASA81 – JANUARY 2023

ADS981x 18-Bit, 8-MSPS, Dual, Simultaneous-Sampling ADC With

Integrated Analog Front-End

1 Features

2 Applications

•

•

•

•

•

•

•

•

•

•

AVDD_5V

AVDD_1V8

REFOUT_2V5

1M

AIN1P

OVP

OVP

Prog. LPF

PGA

ADC

Driver

1M

4.096 V

VREF

VB0

REFIO

REFM

1M

OVP

AIN2P

Prog. LPF

PGA

OVP

AIN2M

ADC REF

ADC

Driver

18-Bit, 8-MSPS

SAR ADC

ADC A

1M

VB1

1M

AIN3P

OVP

AIN3M

OVP

Prog. LPF

PGA

3 Description

The ADS981x is an eight-channel data acquisition

(DAQ) system based on a dual, simultaneoussampling, 18-bit successive approximation register

(SAR) analog-to-digital converter (ADC). The

ADS981x features a complete analog front-end

for each channel with an input clamp, 1-MΩ

input impedance, independently programmable gain

amplifier (PGA), programmable low-pass filter, and an

ADC input driver. The device also features a low-drift,

precision reference with a buffer to drive the ADCs. A

high-speed digital interface supporting 1.2-V to 1.8-V

operation enables the ADS981x to be used with a

variety of host controllers.

DVDD_1V8

2.5 V

AIN1M

Semiconductor test

Battery test

Data acquisition (DAQ)

IOVDD

ADC

Driver

The ADS981x can be configured to accept ±12-V,

±10-V, ±7-V, ±5-V, ±3.5-V, and ±2.5-V bipolar inputs.

The high input impedance allows direct connection

with sensors and transformers, thus eliminating the

need for external driver circuits. The high performance

and accuracy, along with zero-latency conversions

offered by this device make the ADS981x a great

choice for multiple industrial applications.

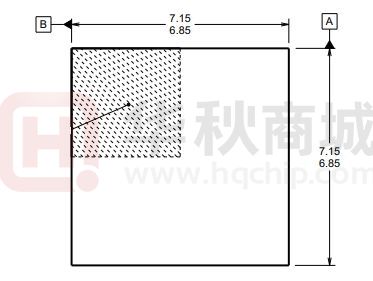

Package Information

1M

VB2

RESET

Prog. LPF

PGA

AIN4M

OVP

ADC

Driver

SMPL_SYNC

1M

ADC REF

VB3

Digital logic

and

Data Interface

1M

Prog. LPF

PGA

OVP

AIN5M

ADC

Driver

FCLKOUT

D1

ADS981x

(1)

D3

1M

OVP

Prog. LPF

PGA

OVP

PART NUMBER

ADC

Driver

1M

VB5

18-Bit, 8-MSPS

SAR ADC

ADC B

1M

OVP

AIN7P

Prog. LPF

PGA

OVP

AIN7M

7.00 mm × 7.00 mm

Device Information

VB4

AIN6M

RSH (VQFN, 56)

For all available packages, see the orderable addendum at

the end of the data sheet.

D2

1M

AIN6P

BODY SIZE (NOM)

DCLKOUT

D0

OVP

AIN5P

PACKAGE(1)

SMPL_CLK

OVP

AIN4P

PART NUMBER

PWDN

1M

SPEED

TOTAL POWER

ADS9817

2 MSPS/channel

232 mW

ADS9815

1 MSPS/channel

160 mW

ADC

Driver

1M

VB6

SPI_EN

CS / EXTREF

1M

AIN8P

OVP

Prog. LPF

PGA

AIN8M

OVP

ADC

Driver

1M

Con�gura�on

Registers

SCLK

SDI

SDO

VB7

GND

Device Block Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. ADVANCE INFORMATION for preproduction products; subject to change

without notice.

ADVANCE INFORMATION

•

8-channel, 18-bit ADC with analog front-end:

– Dual, simultaneous sampling: 4 × 1 channels

– Constant 1-MΩ input impedance front-end

Programmable low-pass filter bandwidth:

– 21 kHz and 400 kHz

Programmable input ranges:

– ±12 V, ±10 V, ±7 V, ±5 V, ±3.5 V, and ±2.5 V

– Single-ended and differential inputs

Input overvoltage protection: Up to ±18 V

Integrated low-drift 4.096-V precision reference

Excellent performance:

– DNL: ±0.3 LSB, INL: ±1.5 LSB

– SNR: 92.2 dB, THD: –112 dB

Power supply:

– Analog and digital: 5 V and 1.8 V

– Digital interface: 1.2 V to 1.8 V

Temperature range: –40°C to +125°C

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

Table of Contents

ADVANCE INFORMATION

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Pin Configuration and Functions...................................3

6 Specifications.................................................................. 5

6.1 Absolute Maximum Ratings........................................ 5

6.2 ESD Ratings............................................................... 5

6.3 Recommended Operating Conditions.........................6

6.4 Thermal Information....................................................6

6.5 Electrical Characteristics.............................................7

6.6 Timing Requirements.................................................. 9

6.7 Switching Characteristics..........................................10

6.8 Timing Diagrams....................................................... 10

6.9 Typical Characteristics.............................................. 13

7 Detailed Description......................................................14

7.1 Overview................................................................... 14

7.2 Functional Block Diagram......................................... 14

7.3 Feature Description...................................................15

7.4 Programming............................................................ 22

7.5 Register Map.............................................................26

8 Application and Implementation.................................. 46

8.1 Application Information............................................. 46

8.2 Typical Application.................................................... 46

8.3 Power Supply Recommendations.............................47

8.4 Layout....................................................................... 48

9 Device and Documentation Support............................50

9.1 Receiving Notification of Documentation Updates....50

9.2 Support Resources................................................... 50

9.3 Trademarks............................................................... 50

9.4 Electrostatic Discharge Caution................................50

9.5 Glossary....................................................................50

10 Mechanical, Packaging, and Orderable

Information.................................................................... 50

10.1 Mechanical Data..................................................... 51

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

DATE

January 2023

2

REVISION

*

NOTES

Initial Release

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

SMPL_CLKP

SMPL_CLKM

44

43

AIN2P

1

42

IOGND

AIN2M

2

41

IOVDD

AIN3P

3

40

FCLKOUT

AIN3M

4

39

NC

AIN4P

5

38

NC

AIN4M

6

37

D3

GND

7

36

D2

REFM

8

AIN5P

Thermal

35

D1

9

34

D0

AIN5M

10

33

DCLKOUT

AIN6P

11

32

PWDN

AIN6M

12

31

RESET

AIN7P

13

30

IOVDD

AIN7M

14

29

IOGND

15

16

17

18

19

20

21

22

23

24

25

26

27

28

AVDD_5V

AIN8P

AIN8M

REFM

REFOUT_2V5

NC

AVDD_1V8

DVDD_1V8

GND

SPI_EN

CS

SCLK

SDI / EXTREF

SDO

Pad

ADVANCE INFORMATION

GND

DVDD_1V8

SMPL_SYNC

DVDD_1V8

47

45

AVDD_1V8

49

48

46

NC

NC

51

50

REFM

REFIO

52

AIN1P

54

53

AVDD_5V

AIN1M

56

55

5 Pin Configuration and Functions

Not to scale

Figure 5-1. RSH Package, 56-Pin VQFN (Top View)

Table 5-1. Pin Functions

PIN

NAME

NO.

I/O(1)

DESCRIPTION

AIN1M

55

AI

Analog input channel 1, negative input.

AIN1P

54

AI

Analog input channel 1, positive input.

AIN2M

2

AI

Analog input channel 2, negative input.

AIN2P

1

AI

Analog input channel 2, positive input.

AIN3M

4

AI

Analog input channel 3, negative input.

AIN3P

3

AI

Analog input channel 3, positive input.

AIN4M

6

AI

Analog input channel 4, negative input.

AIN4P

5

AI

Analog input channel 4, positive input.

AIN5M

10

AI

Analog input channel 5, negative input.

AIN5P

9

AI

Analog input channel 5, positive input.

AIN6M

12

AI

Analog input channel 6, negative input.

AIN6P

11

AI

Analog input channel 6, positive input.

AIN7M

14

AI

Analog input channel 7, negative input.

AIN7P

13

AI

Analog input channel 7, positive input.

AIN8M

17

AI

Analog input channel 8, negative input.

AIN8P

16

AI

Analog input channel 8, positive input.

AVDD_1V8

21, 49

P

1.8-V analog supply. Connect 1-µF and 0.1-µF decoupling capacitors to AGND.

AVDD_5V

15, 56

P

5-V analog supply. Connect 1-µF and 0.1-µF decoupling capacitor to AGND.

25

DI

Chip-select input for configuration of SPI interface; active low. This pin has an internal

100-kΩ pullup resistor to the digital interface supply.

D0

34

DO

Serial output data lane 0.

D1

35

DO

Serial data output lane 1.

CS

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

3

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

Table 5-1. Pin Functions (continued)

PIN

NAME

NO.

I/O(1)

D2

36

DO

Serial data output lane 2.

D3

37

DO

Serial data output lane 3.

DCLKOUT

33

DO

Clock output for the data interface.

DVDD_1V8

22, 47, 48

P

FCLKOUT

GND

IOGND

IOVDD

ADVANCE INFORMATION

NC

PWDN

REFM

REFOUT_2V5

RESET

SCLK

40

DO

P

Ground.

29, 42

P

Digital interface ground. Connect to GND.

30, 41

P

Digital I/O supply for the data interface. Connect 1-µF and 0.1-µF decoupling capacitors to

IOGND.

20, 38, 39, 50,

51

—

32

DI

Power-down control; active low. This pin has an internal 100-kΩ pullup resistor to the digital

interface supply.

52

AI/AO

This pin acts as an internal reference output when the internal reference is enabled. This

pin functions as an input pin for the external reference when internal reference is disabled.

Connect a 10-µF decoupling capacitor to the REFM pins.

8, 18, 53

AI

Reference ground potential. Connect to GND.

19

AO

2.5-V reference output. Connect a decoupling 10-µF capacitor to the REFM pins.

31

DI

Reset input for the device; active low. This pin has an internal 100-kΩ pullup resistor to the

digital interface supply.

26

DI

Serial clock input for the configuration interface. This pin has an internal 100-kΩ pulldown

resistor to the digital interface ground.

27

DI

This pin is a multifunction logic input; pin function is determined by the SPI_EN pin. This pin

has an internal 100-kΩ pulldown resistor to IOGND.

SPI_EN = 0b: This pin is the logic input to select between the internal or external reference.

Connect this pin to IOGND for the external reference. Connect this pin to IOVDD for the

internal reference.

SPI_EN = 1b: Serial data input for the configuration interface.

28

DO

Serial data output for the configuration interface.

44

DI

Single-ended ADC sampling clock input. This pin is the positive input for the differential ADC

sampling clock.

43

DI

Connect this pin to GND for a single-ended ADC sampling clock input. This pin is the

negative input for the differential ADC sampling clock.

45

DI

Logic input to select analog input channel 1 for ADC A and analog input channel 8 for ADC

B.

24

DI

Logic input to enable the configuration SPI interface (CS, SCLK, SDI, and SDO). This pin

has internal 100-kΩ pullup resistor to the digital interface supply.

—

P

Exposed thermal pad; connect to AGND.

SDI

SDO

SMPL_CLKP

SMPL_CLKM

SMPL_SYNC

SPI_EN

Thermal pad

(1)

Digital supply pin. Connect 1-µF and 0.1-µF decoupling capacitors to DGND.

7, 23, 46

REFIO

4

DESCRIPTION

Frame synchronization output for data interface.

Not connected. No external connection.

I = input, O = output, I/O = input or output, G = ground, and P = power.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

6 Specifications

6.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

MAX

UNIT

AVDD_5V to GND

–0.3

6

V

AVDD_1V8 to GND

–0.3

2.1

V

DVDD_1V8 to GND

–0.3

2.1

V

IOVDD to GND

–0.3

2.1

V

AINxP and AINxM to GND

–18

18

V

REFM – 0.3

AVDD_5V + 0.3

V

REFM to GND

GND – 0.3

GND + 0.3

V

IOGND to GND

GND – 0.3

GND + 0.3

V

REFIO to REFM

Digital inputs to IOGND

IOGND – 0.3

2.1

V

Input current to any pin except supply pins(2)

–10

10

mA

Junction temperature, TJ

–40

150

°C

Storage temperature, Tstg

–60

150

°C

(1)

(2)

ADVANCE INFORMATION

MIN

Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress

ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated

under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

Pin current must be limited to 10 mA or less.

6.2 ESD Ratings

VALUE

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all

V(ESD)

(1)

(2)

Electrostatic discharge

pins(1)

Charged device model (CDM), per JEDEC specification JESD22-C101, all

pins(2)

UNIT

±2000

±500

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

5

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

POWER SUPPLY

AVDD_5V

Analog power supply

AVDD_5V to GND, 5 V

4.75

5

5.25

V

AVDD_1V8

Analog power supply

AVDD_1V8 to GND, 1.8 V

1.75

1.8

1.85

V

DVDD_1V8

Digital power supply

DVDD_1V8 to GND, 1.8 V

1.75

1.8

1.85

V

IOVDD

Digital interface power supply

IOVDD to IOGND

1.15

1.8

1.85

V

External reference

4.092

4.096

4.100

V

REFERENCE VOLTAGE

VREF

Reference voltage to the ADC

ANALOG INPUTS

ADVANCE INFORMATION

VFSR

Full-scale input range

–2.5

2.5

–3.5

3.5

–5

5

–7

7

–10

10

V

–12

12

AINxP

Operating input voltage,

positive input

–14

14

V

AINxM

Operating input voltage,

negative input

–14

14

V

125

°C

TEMPERATURE RANGE

TA

Ambient temperature

–40

25

6.4 Thermal Information

ADS9817

THERMAL METRIC(1)

RSH (VQFN)

UNIT

56 PINS

RθJA

Junction-to-ambient thermal resistance

23.2

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

10.5

°C/W

RθJB

Junction-to-board thermal resistance

6.1

°C/W

ΨJT

Junction-to-top characterization parameter

0.1

°C/W

ΨJB

Junction-to-board characterization parameter

6.0

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

0.9

°C/W

(1)

6

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

6.5 Electrical Characteristics

at AVDD_5V = 4.75 V to 5.25 V, AVDD_1V8 = 1.75 V to 1.85 V, DVDD_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V,

VREF = 4.096 V (internal or external), and maximum throughput (unless otherwise noted); minimum and maximum values at

TA = -40°C to +125°C; typical values at TA = 25°C.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

0.85

1

1.15

MΩ

ANALOG INPUTS

RIN

Input impedance

Input range = ±5 V

Input impedance thermal drift

All input ranges

10

Input capacitance

25 ppm/°C

10

pF

ANALOG INPUT FILTER

BW(-3 dB)

Analog input LPF bandwidth

–3 dB

21

Wide-bandwidth filter, input range = ±2.5 V

182

Wide-bandwidth filter, input range = ±3.5 V

240

Wide-bandwidth filter, input range = ±5 V

320

Wide-bandwidth filter, input range = ±7 V

400

Wide-bandwidth filter, input range = ±10 V

385

Wide-bandwidth filter, input range = ±12 V

375

ADVANCE INFORMATION

Low-noise filter, all input ranges

kHz

DC PERFORMANCE

Resolution

DNL

Differential nonlinearity

INL

Integral nonlinearity

No missing codes

TA = 0°C to 70°C

18

–0.5

TA = –40°C to 125°C

TA = 0°C to 70°C

Bits

±0.3

0.5

±0.3

–2.5

TA = –40°C to 125°C

±1.5

2.5

±1.5

LSB

LSB

Offset error

±0.5

mV

Offset error matching

±0.4

mV

Offset error thermal drift

Gain error

Gain error thermal drift

±0.5

ppm/°C

External reference, TA = 0°C to 70°C

–50

±32

50

External reference, TA = –40°C to 125°C

–80

±32

80

External reference

1

LSB

ppm/°C

AC PERFORMANCE

SNR

SINAD

Signal-to-noise ratio

Signal-to-noise + distortion ratio

THD

Total harmonic distortion

SFDR

Spurious-free dynamic range

Low-noise filter, fIN = 2 kHz, range = ±2.5 V

89.3

Low-noise filter, fIN = 2 kHz, range = ±3.5 V

90.6

Low-noise filter, fIN = 2 kHz, range = ±5 V

91.5

Low-noise filter, fIN = 2 kHz, range = ±7 V

91.5

Low-noise filter, fIN = 2 kHz, range = ±10 V

91.9

Low-noise filter, fIN = 2 kHz, range = ±12 V

92.2

Wide-bandwidth filter, fIN = 2 kHz, all ranges

82.8

Low-noise filter, fIN = 2 kHz, range = ±2.5 V

89.3

Low-noise filter, fIN = 2 kHz, range = ±3.5 V

90.6

Low-noise filter, fIN = 2 kHz, range = ±5 V

91.5

Low-noise filter, fIN = 2 kHz, range = ±7 V

91.5

Low-noise filter, fIN = 2 kHz, range = ±10 V

91.9

Low-noise filter, fIN = 2 kHz, range = ±12 V

92.2

Wide-bandwidth filter, fIN = 2 kHz, all ranges

82.8

Low-noise filter, fIN = 2 kHz, all ranges

–112

Wide-bandwidth filter, fIN = 2 kHz, all ranges

–111

fIN = 2 kHz

111

dB

dB

dB

dB

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

7

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

6.5 Electrical Characteristics (continued)

at AVDD_5V = 4.75 V to 5.25 V, AVDD_1V8 = 1.75 V to 1.85 V, DVDD_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V,

VREF = 4.096 V (internal or external), and maximum throughput (unless otherwise noted); minimum and maximum values at

TA = -40°C to +125°C; typical values at TA = 25°C.

PARAMETER

Isolation crosstalk

TEST CONDITIONS

MIN

fIN = 10 kHz on unselected channel

TYP

MAX

–92

UNIT

dB

INTERNAL REFERENCE

VREF (1)

Voltage on REFIO pin

(configured as output)

1-µF capacitor on REFIO pin, TA = 25°C

4.092

Reference temperature drift

4.096

7

4.1

V

20 ppm/°C

DIGITAL INPUTS

ADVANCE INFORMATION

VIL

Input low logic level

VIH

Input high logic level

Input current

–0.3

0.3 IOVDD

V

0.7 IOVDD

IOVDD

V

1

µA

–1

Input capacitance

0.1

6

pF

DIGITAL OUTPUTS

VOL

Output low logic level

IOL = 500 µA sink

VOH

Output high logic level

IOH = 500 µA source

0

0.2 IOVDD

V

0.8 IOVDD

IOVDD

V

POWER SUPPLY

Total power dissipation

IAVDD_5V

Maximum throughput

Supply current from AVDD_5V

IAVDD_1V8 Supply current from AVDD_1V8

mW

26

mA

44

mA

IDVDD

Supply current from DVDD_1V8

6

mA

IIOVDD

Supply current from IOVDD

7

mA

(1)

8

232

Does not include the variation in voltage resulting from solder shift effects.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

6.6 Timing Requirements

at AVDD_5V = 4.75 V to 5.25 V, AVDD_1V8 = 1.75 V to 1.85 V, DVDD_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V,

and maximum throughput (unless otherwise noted); minimum and maximum values at TA = -40°C to +125°C; typical values

at TA = 25°C.

MIN

MAX

UNIT

TBD

8

MSPS

CONVERSION CYCLE

fSMPL_CLK

Sampling frequency

tSMPL_CLK

Sampling time interval

1 / fSMPL_CLK

tPL_SMPL_CLK

SMPL_CLK low time

0.4 tSMPL_CLK

0.6 tSMPL_CLK

ns

tPH_SMPL_CLK

SMPL_CLK high time

0.4 tSMPL_CLK

0.6 tSMPL_CLK

ns

tWH_SMPL_SYNC

Pulse duration: SMPL_SYNC low

10

ns

tWL_SMPL_SYNC

Pulse duration: SMPL_SYNC high

10

ns

ADVANCE INFORMATION

ns

SPI INTERFACE TIMINGS (CONFIGURATION INTERFACE)

fSCLK

Maximum SCLK frequency

20

MHz

tPH_CK

SCLK high time

0.48

0.52

tCLK

tPL_CK

SCLK low time

0.48

0.52

tCLK

thi_CS

Pulse duration: CS high

220

ns

td_CSCK

Delay time: CS falling to the first SCLK capture edge

20

ns

tsu_CKDI

Setup time: SDI data valid to the SCLK rising edge

10

ns

tht_CKDI

Hold time: SCLK rising edge to data valid on SDI

5

ns

tD_CKCS

Delay time: last SCLK falling to CS rising

5

ns

CMOS DATA INTERFACE

tsu_SS

Setup time: SMPL_SYNC rising edge to SMPL_CLK falling edge

10

ns

tht_SS

Hold time: SMPL_CLK falling edge to SMPL_SYNC high

10

ns

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

9

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

6.7 Switching Characteristics

at AVDD_5V = 4.75 V to 5.25 V, AVDD_1V8 = 1.75 V to 1.85 V, DVDD_1V8 = 1.75 V to 1.85 V, IOVDD = 1.15 V to 1.85 V,

and maximum throughput (unless otherwise noted); minimum and maximum values at TA = -40°C to +125°C; typical values

at TA = 25°C.

PARAMETER

TEST CONDITIONS

MIN

MAX

UNIT

RESET

tPU

Power-up time for device

25

ms

SPI INTERFACE TIMINGS (CONFIGURATION INTERFACE)

ADVANCE INFORMATION

tden_CKDO

Delay time: 8th SCLK rising-edge to data

enable

22

ns

tdz_CKDO

Delay time: 24th SCLK rising-edge to SDO

going Hi-Z

50

ns

td_CKDO

Delay time: SCLK falling-edge to

corresponding data valid on SDO

16

ns

tht_CKDO

Delay time: SCLK falling-edge to previous

data valid on SDO

2

ns

CMOS DATA INTERFACE

tDCLK

Data clock output

DDR mode

10

SDR mode

20

Clock duty cycle

ns

45

55

%

toff_DCLKDO_r

Time offset: DCLK rising to corresponding

data valid

DDR mode

tDCLK/4 – 3

tDCLK/4 + 3

ns

toff_DCLKDO_f

Time offset: DCLK falling to corresponding

data valid

DDR mode

tDCLK/4 – 3

tDCLK/4 + 3

ns

td_DCLKDO

Time delay: DCLK rising to corresponding

data valid

SDR mode

–2

2

ns

td_SYNC_FCLK

Time delay: SMPL_CLK falling edge with

SYNC signal to corresponding FCLKOUT

rising edge

3

4 tSMPL_CLK

6.8 Timing Diagrams

thi_CS

CS

td_CKCS

td_CSCK

SCLK

tsu_CKDI

SDI

A

7

A

6

tht_CKDI

A

5

A

4

A

3

A

2

A

1

A

0

D

15

D

14

D

13

tden_CKDO

Hi-Z

SDO

DO

15

DO

14

D

12

D

11

D

10

D

9

td_CKDO

DO

13

DO

12

DO

11

D

8

D

7

D

6

D

5

D

4

D

3

D

2

DO

9

DO

8

DO

7

D

0

tdz_CKDO

tht_SDO

DO

10

D

1

DO

6

DO

5

DO

4

DO

3

DO

2

DO

1

DO

0

SDO active only when reading registers; Hi-Z otherwise

Figure 6-1. SPI Configuration Interface

10

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

SMPL_SYNC

tht_SS

tsu_SS

SMPL_CLK

24 DCLKs

td_SYNC_FCLK

DCLKOUT

tFCLK

FCLKOUT

D D D

13 11 9

6 DCLK

D3

D D D

23 21 19

D2

D D D

22 20 18

D D D

12 10 8

D D D D

0 22 20 18

D D D

12 10 8

D D D D

0 22 20 18

D D D

12 10 8

D D D D

0 22 20 18

D D D

12 10 8

D D D D

0 22 20 18

D D D

12 10 8

D1

D D D

23 21 19

D D D

13 11 9

D D D D

1 23 21 19

D D D

13 11 9

D D D D

1 23 21 19

D D D

13 11 9

D D D D

1 23 21 19

D D D

13 11 9

D D D D

1 23 21 19

D D D

13 11 9

D0

D D D

22 20 18

Channel 1

Channel 8

D D D

12 10 8

D D D D

1 23 21 19

toff_DCLKDO_r

D D D

13 11 9

D D D D

1 23 21 19

Channel 3

Channel 2

Channel 6

Channel 7

D D D D

0 22 20 18

D D D

13 11 9

D D D

12 10 8

D D D D

0 22 20 18

D D D D

1 23 21 19

D D D

13 11 9

Channel 4

Channel 5

D D D

12 10 8

D D D D

0 22 20 18

D D D

12 11 10

D D D D

0 23 22 21

D D D

12 10 8

D D D D

1 23 21 19

D D D

13 11 9

ADVANCE INFORMATION

toff_DCLKDO_f

Channel 1

Channel 8

D D D D

0 22 20 18

D D D

12 10 8

D D D D

0 23 22 21

D D D

12 11 10

Figure 6-2. 4-SDO DDR CMOS Data Interface

SMPL_SYNC

tht_SS

tsu_SS

SMPL_CLK

48 DCLKs

td_SYNC_FCLK

DCLKOUT

tFCLK

FCLKOUT

toff_DCLKDO_r

D D D

23 22 21

D3

D D D

12 11 10

12 DCLK

D D D D

0 23 22 21

D D D

23 22 21

D D D

12 11 10

Channel 8

toff_DCLKDO_f

D D D D

0 23 22 21

Channel 3

Channel 2

Channel 1

D1

D D D

12 11 10

D D D D

0 23 22 21

D D D

12 11 10

D D D D

0 23 22 21

Channel 7

D D D

12 11 10

Channel 6

D D D

12 11 10

Channel 4

D D D D

0 23 22 21

D D D

12 11 10

Channel 5

Channel 1

D D D D

0 23 22 21

D D D

12 11 10

Channel 8

Figure 6-3. 2-SDO DDR CMOS Data Interface

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

11

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

SMPL_SYNC

tht_SS

tsu_SS

SMPL_CLK

td_SYNC_FCLK

48 DCLKs

DCLKOUT

tFCLK

FCLKOUT

td_DCLKDO

ADVANCE INFORMATION

D3

D

23

D

21

D2

D

22

D

20

D1

D

23

D

21

D

11

D

1

D

23

D

21

D

10

D

0

D

22

D

20

D

11

D

1

D

23

D

21

Channel 1

D

22

D

20

D

10

D

1

D

23

D

21

D

10

D

0

D

22

D

20

D

11

D

1

D

23

D

21

D

22

D

20

D

10

D

1

D

23

D

21

D

10

D

0

D

22

D

20

D

0

D

22

D

20

D

10

D

0

D

11

D

1

D

23

D

21

D

11

D

1

D

10

D

11

D

1

Channel 4

Channel 6

Channel 7

D

0

D

11

Channel 3

Channel 2

Channel 8

D0

D

11

Channel 5

D

0

D

22

D

20

D

10

D

0

Figure 6-4. 4-SDO SDR CMOS Data Interface

SMPL_SYNC

tht_SS

tsu_SS

SMPL_CLK

td_SYNC_FCLK

96 DCLKs

DCLKOUT

tFCLK

FCLKOUT

td_DCLKDO

D3

D

23

D

22

D

11

D

0

Channel 1

D1

D

23

D

22

D

11

Channel 2

Channel 3

Channel 4

Channel 7

Channel 6

Channel 5

D

0

Channel 8

Figure 6-5. 2-SDO SDR CMOS Data Interface

12

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

6.9 Typical Characteristics

1.5

1.5

1

1

0.5

0

-0.5

-1

0.5

0

-0.5

-1

-1.5

-1.5

0

65536

131072

Output Code

196608

262144

0

65536

Typical INL = ±1 LSB

196608

262144

Figure 6-7. Typical INL With Wide-Bandwidth LPF

0.6

Differential Nonlinearity (LSB)

0.6

Differential Nonlinearity (LSB)

131072

Output Code

Typical INL = ±1.2 LSB

Figure 6-6. Typical INL With Low-Noise LPF

0.3

0

-0.3

-0.6

0.3

0

-0.3

-0.6

0

65536

131072

Output Code

196608

262143

0

65536

Typical DNL = ±0.35 LSB

Figure 6-8. Typical DNL With Low-Noise LPF

-12

-12

Amplitude (dB)

-6

-18

-24

-30

-18

-24

-30

-36

-36

-42

-42

-48

3 4 5 67 10

20 30 50 70100

Frequency (kHz)

262143

0

-6

2

196608

Figure 6-9. Typical DNL With Wide-Bandwidth LPF

All input ranges

1

131072

Output Code

Typical DNL = ±0.35 LSB

0

Amplitude (dB)

ADVANCE INFORMATION

Integral Nonlinearity (LSB)

Integral Nonlinearity (LSB)

at TA = 25°C, AVDD_5V = 5 V, AVDD_1V8 = 1.8 V, DVDD_1V8 = 1.8 V, internal VREF = 4.096 V, and maximum throughput

(unless otherwise noted)

200

500 1000

-48

10

2

±.5 V range

3

±.5 V range

5

± V range

7

± V range

1

±0 V range

1

±2 V range

20 30 4050 70 100

200 300 500

Frequency (kHz)

1000

2000

Typical bandwidth (–3 dB) = 21.2 kHz

Figure 6-10. Low-Noise LPF Frequency Response Across Input

Ranges

Figure 6-11. Wide-Bandwidth LPF Frequency Response Across

Input Ranges

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

13

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7 Detailed Description

7.1 Overview

The ADS981x is an 18-bit data acquisition (DAQ) system with 8-channel analog inputs that can be configured

as either single-ended or differential. Each analog input channel consists of an input clamp protection circuit,

a programmable gain amplifier (PGA), and a second-order, low-pass filter. The input signals are digitized using

an 18-bit analog-to-digital converter (ADC), based on the successive approximation register (SAR) architecture.

This overall system can achieve a maximum throughput of 2 MSPS/channel for all channels. The device features

a 4.096-V internal reference with a fast-settling buffer, a programmable digital averaging filter to improve noise

performance, and high-speed data interface for communication with a wide variety of digital hosts.

ADVANCE INFORMATION

The device operates from 5-V and 1.8-V analog supplies and can accommodate true bipolar input signals. The

input clamp protection circuitry can tolerate voltages up to ±18 V. The device offers a constant 1-MΩ resistive

input impedance irrespective of the sampling frequency or the selected input range. The ADS981x offers a

simplified end solution without requiring external high-voltage bipolar supplies and complicated driver circuits

7.2 Functional Block Diagram

AVDD_5V

AVDD_1V8

DVDD_1V8

REFOUT_2V5

2.5 V

1M

OVP

AIN1P

Prog. LPF

PGA

AIN1M

OVP

ADC

Driver

1M

4.096 V

VREF

VB0

REFIO

REFM

1M

OVP

AIN2P

Prog. LPF

PGA

OVP

AIN2M

ADC REF

ADC

Driver

18-Bit, 8-MSPS

SAR ADC

ADC A

1M

VB1

1M

AIN3P

OVP

AIN3M

OVP

Prog. LPF

PGA

IOVDD

ADC

Driver

1M

VB2

RESET

PWDN

1M

AIN4P

OVP

AIN4M

OVP

SMPL_CLK

Prog. LPF

PGA

ADC

Driver

SMPL_SYNC

1M

ADC REF

VB3

Digital logic

and

Data Interface

1M

Prog. LPF

PGA

OVP

AIN5M

FCLKOUT

D0

OVP

AIN5P

DCLKOUT

ADC

Driver

D1

D2

1M

VB4

D3

1M

AIN6P

OVP

AIN6M

OVP

Prog. LPF

PGA

ADC

Driver

1M

VB5

18-Bit, 8-MSPS

SAR ADC

ADC B

1M

OVP

AIN7P

Prog. LPF

PGA

OVP

AIN7M

ADC

Driver

1M

VB6

SPI_EN

CS / EXTREF

1M

AIN8P

OVP

AIN8M

OVP

Prog. LPF

PGA

ADC

Driver

1M

Con�gura�on

Registers

SCLK

SDI

SDO

VB7

GND

14

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.3 Feature Description

7.3.1 Analog Inputs

The ADS981x incorporates dual, simultaneous-sampling, 18-bit successive approximation register (SAR)

analog-to-digital converters (ADCs). Each ADC is connected to four analog input channels through a multiplexer.

The device has a total of eight analog input pairs. The ADC digitizes the voltage difference between the analog

input pairs AINxP – AINxM. Figure 7-1 shows the simplified circuit schematic for each analog input channel,

including the input clamp protection circuit, PGA, low-pass filter, multiplexer, high-speed ADC driver, and a

precision 18-bit SAR ADC.

1M �

Clamp

1M

AINxM

PGA

2nd order

Prog. LPF

18 bit

SAR

ADC

MUX

Clamp

ADVANCE INFORMATION

AINxP

Figure 7-1. Front-End Circuit Schematic for the Selected Analog Input Channel

7.3.1.1 Programmable Gain Amplifier (PGA)

The ADS981x features a PGA at every analog input channel. The PGA supports single-ended and differential

inputs with a bipolar signal swing. Table 7-1 lists the supported analog input ranges. The analog input range can

be configured independently for each channel by using the RANGE_CHx register fields in address 0xC2 and

address 0xC3.

Table 7-1. Analog Input Ranges

DIFFERENTIAL INPUTS

SINGLE-ENDED INPUTS

±12 V

±12 V

±10 V

±10 V

±7 V

±7 V

±5 V

±5 V

±3.5 V

±3.5 V

±2.5 V

±2.5 V

7.3.1.2 Input Clamp Protection Circuit

The ADS981x features an internal clamp protection circuit on each of the eight analog input channels, see

Figure 7-1. The input clamp protection circuit allows each analog input to swing up to a maximum voltage of

±18 V. Beyond an input voltage of ±18 V, the input clamp circuit turns on and still operates from the single 5-V

supply. Figure 7-2 illustrates a typical current versus voltage characteristic curve for the input clamp.

For input voltages above the clamp threshold, make sure that the input current never exceeds ±10 mA. A

resistor placed in series with the analog inputs is an effective way to limit the input current. In addition to limiting

the input current, the series resistor can also provide an antialiasing, low-pass filter (LPF) when coupled with a

capacitor. Matching the external source impedance on the AINxP and AINxM pins cancels any additional offset

error.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

15

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

50

Input Clamp Current (mA)

40

30

20

10

0

-10

-20

-30

-40

-50

-20

-15

-10

-5

0

5

Input Voltage (V)

10

15

20

D007

ADVANCE INFORMATION

Figure 7-2. Input Protection Clamp Profile, Input Clamp Current vs Source Voltage

7.3.1.3 Wide-Common-Mode Voltage Rejection Circuit

The ADS981x features a common-mode (CM) rejection circuit at the analog inputs that supports CM voltages up

to ±12 V. The CM voltage for differential inputs is given by Equation 1.

Common mode voltage =

Voltage on AINP + Voltage on AINM

2

(1)

As shown in Table 7-2, the CM voltage rejection circuit can be optimized for various CM voltages for differential

inputs. The CM voltage rejection setting is common for two groups of four analog inputs. Analog input channels

1, 2, 3, and 4 are configured using CM_ADC_A[1:0] and analog input channels 5, 6, 7, and 8 are configured

using CM_ADC_B[1:0].

Table 7-2. Wide-Common-Mode Configuration for Differential Inputs

COMMON-MODE (CM) RANGE

WIDE_CM_EN1

WIDE_CM_EN2[1:0]

CM_ADC_A[1:0]

CM_ADC_B[1:0]

0

No effect

CM ≤ ±1 V

1

CM ≤ ±RANGE / 2

1

CM ≤ ±6 V

1

CM ≤ ±12 V

1

0

1: Only AIN[4:1] are differential

2: Only AIN[8:5] are differential

3: All AIN[8:1] are differential

2

1

Table 7-3 lists the recommended configuration for single-ended inputs.

Table 7-3. Wide-Common-Mode Configuration for Single-Ended Inputs

WIDE_CM_EN2[1:0]

CM_ADC_A[1:0]

CM_ADC_B[1:0]

1

0

No effect

1

1: Only AIN[4:1] are single-ended

2: Only AIN[8:5] are single-ended

3: All AIN[8:1] are single-ended

0

INPUT RANGE

WIDE_CM_EN1

±2.5 V, ±3.5 V, and ±5 V

±7 V, ±10 V, and ±12 V

On power-up or after reset, the common-mode voltage range for the analog input channels is ±6 V

(WIDE_CM_EN1 = 0b). Voltage at the analog inputs, in all cases, must be within the Absolute Maximum

Ratings.

16

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.3.1.4 Programmable Low-Pass Filter

Each analog input channel features a second-order, programmable, antialiasing, low-pass filter (LPF) at the

output of the PGA. Table 7-4 lists the various programmable LPF options available in the ADS981x. Figure 6-10

and Figure 6-11 illustrate the frequency responses for low-noise and wide-bandwidth LPF configurations. Analog

input bandwidth can be configured using the ANA_BW[7:0] bits in address 0xC0 of register bank 1.

LPF

ANALOG INPUT RANGE

CORNER FREQUENCY (–3 dB)

Low-noise

All input ranges

21.2 kHz

±12 V

375 kHz

±10 V

385 kHz

±7 V

400 kHz

±5 V

320 kHz

±3.5 V

240 kHz

±2.5 V

185 kHz

Wide-bandwidth

ADVANCE INFORMATION

Table 7-4. Low-Pass Filter Corner Frequency

7.3.1.5 Gain Error Calibration

The ADS981x features calibration logic to minimize gain error from the analog inputs. Gain error calibration can

be enabled by configuring the GE_CAL_EN1 (address = 0xD), GE_CAL_EN2, and GE_CAL_EN3 bits (address

= 0x33). Enable gain error calibration for optimum performance.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

17

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.3.2 ADC Transfer Function

The ADS981x outputs 18 bits of conversion data in either straight-binary or binary two's complement formats.

The format for the output codes is the same across all analog channels. The format for the output codes can be

selected using the DATA_FORMAT field in address 0xD in register bank 1. Figure 7-3 and Table 7-5 show the

transfer characteristics for the ADS981x. The LSB size depends on the analog input range selected.

ADC OUTPUT CODE

ADVANCE INFORMATION

Straight

Binary

Twos

Complement

0x3FFFF

0x1FFFF

0x3FFFE

0x1FFFE

0x20001

0x00001

0x20000

0x00000

0x1FFFF

0x3FFFF

0x00002

0x20002

0x00001

0x20001

0x00000

0x20000

–FS+(0.5)LSB

0V–(0.5)LSB

+FS–(1.5)LSB

ANALOG INPUT

Figure 7-3. Transfer Characteristics

Table 7-5. ADC Full-Scale Range and LSB Size

RANGE

+FS

MIDSCALE

–FS

LSB

±2.5 V

2.5 V

0V

–2.5 V

19.07 µV

±3.5 V

3.5 V

0V

–3.5 V

26.70 µV

±5 V

5V

0V

–5 V

38.15 µV

±7 V

7V

0V

–7 V

53.41 µV

±10 V

10 V

0V

–10 V

76.29 µV

±12 V

12 V

0V

–12 V

91.55 µV

7.3.3 ADC Sampling Clock Input

Use a low-jitter external clock with a high slew rate to maximize SNR performance. The ADS981x can be

operated using a differential or a single-ended clock input, where the single-ended clock consumes less power

consumption. Clock amplitude impacts the ADC aperture jitter and consequently the SNR. For maximum SNR

performance, provide a large clock signal with fast slew rates.

The sampling clock must be a free-running continuous clock. The ADC generates a valid output data, data

clock, and frame clock tPU_SMPL_CLK, as specified in the Switching Characteristics section after a free-running

sampling clock is applied. The ADC output data, data clock, and frame clock are invalid when the sampling clock

is stopped.

18

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

Figure 7-4 shows a diagram of the differential sampling clock input. For this configuration, connect the differential

sampling clock input to the SMPL_CLKP and SMPL_CLKM pins. Figure 7-5 shows a diagram of the singleended sampling clock input. In this configuration, connect the single-ended sampling clock to SMPL_CLKP and

connect SMPL_CLKM to ground.

1.8V

SMPL_CLKP

100

Differential

sampling clock

5.4 k�

�

SMPL_CLKP

0V

+

Bias

SMPL_CLKM

–

5.4 k

ADS92XX

SMPL_CLKM

GND

Figure 7-5. Single-Ended Sampling Clock

ADVANCE INFORMATION

Figure 7-4. AC Coupled Differential Sampling

Clock

7.3.4 Reference

The ADS981x has a precision, low-drift voltage reference internal to the device. For best performance, filter

the internal reference noise by connecting a 10-µF ceramic bypass capacitor to the REFIO pin. An external

reference can also be connected at the REFIO pin and the internal reference voltage can be disabled by writing

to PD_REF = 1b in address 0xC1 of register bank 1.

7.3.4.1 Internal Reference Voltage

The ADS981x features an internal reference voltage with a nominal output voltage of 4.096 V. On power-up, the

internal reference is enabled by default. As shown in Figure 7-6, place a minimum 10-µF decoupling capacitor

between the REFIO and REFM pins.

AVDD_5V

REFIO

ADC REF

10 μF

1 k�

REFM

PD_REF = 0

External capacitor

for reference

noise reduction

GND

User register bit

4.096 V

GND

Figure 7-6. Internal Reference Voltage

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

19

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.3.4.2 External Reference Voltage

An external 4.096-V reference voltage, as shown in Figure 7-7, can be connected at the REFIO pin with

an appropriate decoupling capacitor placed between the REFIO and REFM pins. For improved thermal drift

performance, the REF7040 is recommended. To disable the internal reference, set PD_REF = 1b in address

0xC1 in register bank 1. The REFIO pin has ESD protection diodes connected to the AVDD_5V and REFM pins.

5V

VIN

EN

OUTF

AVDD_5V

REF7040

OUTS

ADVANCE INFORMATION

GND

REFIO

ADC REF

10 μF

1 k�

REFM

PD_REF = 1

GND

User register bit

4.096 V

GND

Figure 7-7. External Reference Voltage

20

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.3.5 Test Patterns for Data Interface

The ADS981x features test patterns that can be used by the host for debugging and verifying the data interface.

The test patterns replace the ADC output data with predefined digital data. The test patterns can be enabled by

configuring the corresponding register addresses 0x13 through 0x1B in bank 1.

The ADS981x supports the following test patterns:

• User-defined output: User-defined, 24-bit pattern. Separate patterns for ADC A and ADC B; see the UserDefined Test Pattern section.

• Ramp output: Digital ramp output with a user-defined increment between two steps. There are separate ramp

outputs for ADC A and ADC B; see the Ramp Test Pattern section.

• Alternate output: User-defined, 24-bit outputs that alternate between ADC A and ADC B user-defined

patterns; see the User-Defined Alternating Test Pattern section.

ADVANCE INFORMATION

To disable the test patterns, set TEST_PAT_EN_CHA and TEST_PAT_EN_CHB to 0b.

7.3.5.1 User-Defined Test Pattern

The user-defined test pattern allows the host to specify a fixed 24-bit value that is output by the ADS981x.

Configure the registers in bank 1 to enable the user-defined test pattern:

• Configure the test patterns in TEST_PAT0_CHA (address = 0x14, 0x15) and TEST_PAT0_CHB (address =

0x19, 0x1A)

• Set TEST_PAT_EN_CHA = 1, TEST_PATMODE_CHA = 0 (address = 0x13) and TEST PAT_EN_CHB = 1,

TEST_PATMODE_CHB = 0 (address = 0x18)

The ADS981x outputs the TEST_PAT0_CHA and TEST_PAT0_CHB register values in place of the ADC A and

ADC B data, respectively.

7.3.5.2 User-Defined Alternating Test Pattern

The user-defined alternating test pattern allows the host to specify two fixed 24-bit values that are output by the

ADS981x alternately. Configure the registers in bank 1 to enable the user-defined alternating test pattern:

• Configure the test patterns in TEST_PAT0_CHA (address = 0x14, 0x15), TEST_PAT1_CHA (address = 0x15,

0x16) and TEST_PAT0_CHB (address = 0x19, 0x1A), TEST_PAT1_CHB (address = 0x1A, 0x1B)

• Set TEST_PAT_EN_CHA = 1, TEST_PATMODE_CHA = 3 (address = 0x13) and TEST PAT_EN_CHB = 1,

TEST_PATMODE_CHB = 3 (address = 0x18)

The ADS981x outputs the TEST_PAT0_CHA and TEST_PAT0_CHB register values in place of the ADC A and

ADC B data, respectively, in one output frame and the TEST_PAT1_CHA and TEST_PAT1_CHB register values

in the next frame.

7.3.5.3 Ramp Test Pattern

The ramp test pattern allows the host to specify a digital ramp that is output by the ADS981x. Configure the

registers in bank 1 to enable the ramp test pattern:

• Configure the increment value between two successive steps of the digital ramp in the RAMP_INC_CHA

(address = 0x13) and RAMP_INC_CHB (address = 0x18) registers, respectively. The digital ramp increments

by N + 1, where N is the value configured in these registers.

• Set TEST_PAT_EN_CHA = 1, TEST_PATMODE_CHA = 2 (address = 0x13) and TEST PAT_EN_CHB = 1,

TEST_PATMODE_CHB = 2 (address = 0x18).

The ADS981x outputs digital ramp values in place of the ADC A and ADC B data, respectively.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

21

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.4 Programming

7.4.1 Register Write

Register write access is enabled by setting SPI_RD_EN = 0b. The 16-bit configuration registers are grouped in

three register banks and are addressable with an 8-bit register address. Register bank 1 and register bank 2

can be selected for read or write operation by configuring the PAGE_SEL0 and PAGE_SEL1 bits, respectively.

Registers in bank 0 are always accessible, irrespective of the PAGE_SELx bits because the register addresses

are unique and are not used in register banks 1 and 2.

ADVANCE INFORMATION

As shown in Figure 7-8, steps to write to a register are:

1. Frame 1: Write to register address 0x03 in register bank 0 to select either register bank 1 or bank 2 for a

subsequent register write. This frame has no effect when writing to registers in bank 0.

2. Frame 2: Write to a register in the bank selected in frame 1. Repeat this step for writing to multiple registers

in the same register bank.

Frame 1

CS

Frame 2

24-bits

SCLK

SDI

{ addr[23:16] = 0x03, data[15:0] = 0x0002 or

0x0010 }

{ addr[23:16] = REG_ADDR, data[15:0] = DATA }

Register Write for Bank Selection (ADDR = 0x03)

Not Required for Register Bank 0

Register Write

SDO

Logic 0 (when SPI_MODE = 0b) and Hi-Z (when SPI_MODE = 1b)

Figure 7-8. Register Write

7.4.2 Register Read

Select the desired register bank by writing to register address 0x03 in register bank 0. Register read access is

enabled by setting SPI_RD_EN = 1b and SPI_MODE = 1b in register bank 0. As shown in Figure 7-9, registers

can be read using two 24-bit SPI frames after SPI_RD_EN and SPI_MODE are set. The first SPI frame selects

the register bank. The ADC returns the 16-bit register value in the second SPI frame corresponding to the 8-bit

register address.

As illustrated in Figure 7-9, steps to read a register are:

1. Frame 1: With SPI_RD_EN = 0b, write to register address 0x03 in register bank 0 to select the desired

register bank 0 for reading.

2. Frame 2: Set SPI_RD_EN = 1b and SPI_MODE = 1b in register address 0x00 in register bank 0.

3. Frame 3: Read any register in the selected bank using a 24-bit SPI frame containing the desired register

address. Repeat this step with the address of any register in the selected bank to read the corresponding

register.

4. Frame 4: Set SPI_RD_EN = 0 to disable register read and re-enable register writes.

5. Repeat steps 1 through 4 to read registers in a different bank.

22

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

Frame 1

Frame 2

Frame 3

Frame 4

{ addr[23:16] = 0x03, data[15:0] = 0x0002 or

0x0010 }

{ addr[23:16] = 0x00, data[15:0] = 0x0006 }

{ addr[23:16] = REG_ADDR, data[15:0] = 0 }

{ addr[23:16] = 0x00, data[15:0] = 0x0004 }

Register Write for Bank Selection (ADDR = 0x03)

Not Required for Register Bank 0

Register Write for Read Enable (ADDR = 0x00)

Register Read: 8-bit address of register to be read

Register Write for Read Disable (ADDR = 0x00)

CS

24-bits

SCLK

SDI

Logic 0 (when SPI_MODE = 0b)

SDO

Hi-Z (when SPI_MODE = 1b)

16-bit Register Data

Figure 7-9. Register Read

ADVANCE INFORMATION

7.4.3 Multiple Devices: Daisy-Chain Topology for SPI Configuration

Figure 7-10 shows a typical connection diagram showing multiple devices in a daisy-chain topology.

SCLK

CS

SCLK

CS

SCLK

ADS98XX

ADC4

SDO

ADS98XX

ADC3

SDI

24-bit

SCLK

CS

SDO

SCLK

ADS98XX

ADC2

SDI

24-bit

CS

SDO

SDI

24-bit

CS

ADS98XX

ADC1

SDO

HOST

SDI

24-bit

PICO

POCI

Figure 7-10. Daisy-Chain Connections for SPI Configuration

The CS and SCLK inputs of all ADCs are connected together and controlled by a single CS and SCLK pin of

the controller, respectively. The SDI input pin of the first ADC in the chain (ADC1) is connected to the peripheral

IN controller OUT (PICO) pin of the controller, the SDO output pin of ADC1 is connected to the SDI input pin of

ADC2, and so on. The SDO output pin of the last ADC in the chain (ADC4) is connected to the peripheral OUT

controller IN (POCI) pin of the controller. The data on the PICO pin passes through ADC1 with a 24-SCLK delay,

as long as CS is active.

The daisy-chain mode must be enabled after power-up or after the device is reset. Set the daisy-chain length

in the DAISY_CHAIN_LENGTH register to enable daisy-chain mode. The daisy-chain length is the number of

ADCs in the chain excluding ADC1. In Figure 7-10, the DAISY_CHAIN_LENGTH = 3.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

23

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.4.3.1 Register Write With Daisy-Chain

Writing to registers in a daisy-chain configuration requires N × 24-SCLKs in one SPI frame. A register write in a

daisy-chain containing four ADCs, as shown in Figure 7-11, requires 96 SCLKs.

CS

N x 24 bits

SCLK

ADVANCE INFORMATION

DADCN

PICO

DADC3

DADC2

DADC1

Logic 0 (when SPI_MODE = 0b)

POCI

Figure 7-11. Register Write With Daisy-Chain

Daisy-chain mode is enabled on power-up or after device reset. Configure the DAISY_CHAIN_LENGTH field

to enable daisy-chain mode. The waveform shown in Figure 7-11 must be repeated N times, where N is the

number of ADCs in the daisy-chain. Figure 7-12 provides the SPI waveform, containing N SPI frames, for

enabling daisy-chain mode for N ADCs.

DADC1[23:0] = DADC2[23:0] = DADC3[23:0] = DADCN[23:0] = { 0000 0001, 0000 0000, N-1, 00}

Frame 1

CS

Frame 2

Frame 3

Frame N

N x 24 bits

SCLK

PICO

DADCN

DADC3

DADC2

DADC1

DADCN

DAISY_CHAIN_LENGTH = 3 {ADC1}

DAISY_CHAIN_LENGTH = 0 {ADC2, ADC3, and ADCN}

POCI

DADC3

DADC2

DADC1

DADCN

DAISY_CHAIN_LENGTH = 3 {ADC1 and ADC2}

DAISY_CHAIN_LENGTH = 0 {ADC3, ADCN}

DADC3

DADC2

DADC1

DADCN

DAISY_CHAIN_LENGTH = 3 {ADC1, ADC2 and ADC3}

DAISY_CHAIN_LENGTH = 0 {ADCN}

DADC3

DADC2

DADC1

DAISY_CHAIN_LENGTH = 3 {ADC1,

ADC2, ADC3 and ADCN}

Logic 0 (when SPI_MODE = 0b)

Figure 7-12. Register Write to Configure Daisy-Chain Length

7.4.3.2 Register Read With Daisy-Chain

Figure 7-13 illustrates an SPI waveform for reading registers in a daisy-chain configuration. The steps for

reading registers from N ADCs connected in a daisy-chain are as follows:

1. Register read is enabled by writing to the following registers using the Register Write With Daisy-Chain:

a. Write to PAGE_SEL to select the desired register bank

b. Enable register read by writing SPI_RD_EN = 0b (default on power-up)

2. With the register bank selected and SPI_RD_EN = 0b, the controller can read register data in the following

two steps:

a. N × 24-bit SPI frame containing the 8-bit register address to be read: N-times {0xFE, 0x00, 8-bit register

address}

b. N × 24-bit SPI frame to read out register data: N-times {0xFF, 0xFF, 0xFF}

24

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

The 0xFE in step 2a configures the ADC for register read from the specified 8-bit address. At the end of step 2a,

the output shift register in the ADC is loaded with register data. The ADC returns the 8-bit register address and

corresponding 16-bit register data in step 2b.

CS

N x 24 bits

N x 24 bits

SCLK

24 bits

PICO

0xFE

0x00

8-bit register

address

0xFE

0xFF

8-bit

address

POCI

0xFF

0xFF

16-bit register data

0xFF

ADVANCE INFORMATION

24 bits

8-bit

address

Figure 7-13. Register Read With Daisy-Chain

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

25

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.5 Register Map

7.5.1 Register Bank 0

Figure 7-14. Register Bank 0 Map

ADD

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

RESERVED

00h

01h

RESERVED

03h

D2

D1

D0

SPI_MO

DE

SPI_RD

_EN

RESET

DAISY_CHAIN_LEN

RESERVED

RESERVED

REG_BANK_SEL

06h

REG_00H_READBACK

7.5.1.1 Register 0h (offset = 0h) [reset = 0h]

Figure 7-15. Register 0h

ADVANCE INFORMATION

15

14

13

12

11

10

9

8

3

2

1

0

RESERVED

SPI_MODE

SPI_RD_EN

RESET

W-0h

W-0h

W-0h

W-0h

RESERVED

W-0h

7

6

5

4

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Figure 7-16. Register 00 Field Descriptions

Bit

Field

Type

Reset

15-3

RESERVED

W

0h

Description

Reserved. Do not change from the default reset value.

2-2

SPI_MODE

W

0h

Select between legacy SPI mode and daisy-chain SPI

mode for the configuration interface for register access.

0: Daisy-chain SPI mode

1: Legacy SPI mode

1-1

SPI_RD_EN

W

0h

Enable register read access in legacy SPI mode. This bit

has no effect in daisy-chain SPI mode.

0: Register read disabled

1: Register read enabled

0-0

RESET

W

0h

ADC reset control

0: Normal device operation

1: Reset ADC and all registers

7.5.1.2 Register 1h (offset = 1h) [reset = 0h]

Figure 7-17. Register 1h

15

14

13

12

11

10

3

2

9

8

RESERVED

R/W-0h

1

0

RESERVED

7

6

5

DAISY_CHAIN_LEN

4

RESERVED

RESERVED

R/W-0h

R/W-0h

R/W-0h

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

26

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

Figure 7-18. Register 01 Field Descriptions

Bit

Field

Type

Reset

15-7

RESERVED

R/W

0h

Description

Reserved. Do not change from the default reset value.

6-2

DAISY_CHAIN_L

EN

R/W

0h

Configure the number of ADCs connected in daisy-chain for

configuring the SPI interface.

0: 1 ADC

1: 2 ADCs

31: 32 ADCs

1-0

RESERVED

R/W

0h

Reserved. Do not change from the default reset value.

15

14

13

12

11

10

9

8

3

2

1

0

ADVANCE INFORMATION

7.5.1.3 Register 3h (offset = 3h) [reset = 2h]

Figure 7-19. Register 3h

RESERVED

R/W-0h

7

6

5

4

REG_BANK_SEL

R/W-2h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Figure 7-20. Register 03 Field Descriptions

Bit

Field

Type

Reset

Description

15-8

RESERVED

R/W

0h

Reserved. Do not change from the default reset value.

7-0

REG_BANK_SEL

R/W

2h

Register bank selection for read and write operations.

0: Select register bank 0

1: Select register bank 1

7.5.1.4 Register 6h (offset = 6h) [reset = 5h]

Figure 7-21. Register 6h

15

14

13

12

11

10

9

8

2

1

0

REG_00H_READBACK

R-0h

7

6

5

4

3

REG_00H_READBACK

R-5h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Figure 7-22. Register 06 Field Descriptions

Bit

Field

Type

Reset

15-0

REG_00H_READ

BACK

R

5h

Description

This register is a copy of the register address 0x00 for

readback. Register address 0x00 is write-only.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

27

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.5.2 Register Bank 1

Figure 7-23. Register Bank 1 Map

ADD

D15

D14

RESERVED

0Dh

D13

D12

D11

DATA_F

ORMAT

D10

D9

D8

RESERVED

D7

D6

D5

D4

D3

GE_CAL

_EN1

D2

D1

D0

2

RESERVED

XOR_EN

DATA_WIDTH

DATA_L

ANES

12h

RESERVED

RAMP_INC_ADC_A

TEST_PAT_MODE_ TEST_P

ADC_A

AT_EN_ RESERV

ADC_A

ED

13h

14h

TEST_PAT0_ADC_A

15h

TEST_PAT1_ADC_A

TEST_PAT0_ADC_A

16h

TEST_PAT1_ADC_A

RESERVED

RAMP_INC_ADC_B

TEST_PAT_MODE_ TEST_P

ADC_B

AT_EN_ RESERV

ADC_B

ED

18h

ADVANCE INFORMATION

19h

TEST_PAT0_ADC_B

1Ah

TEST_PAT1_ADC_B

TEST_PAT0_ADC_B

1Bh

TEST_PAT1_ADC_B

1Ch

USER_BITS_ADC_B

RESERVED

33h

GE_CAL

_EN3

USER_BITS_ADC_A

RESERVED

40h

RESERVED

USER_GAIN_CAL_CH1

42h

USER_GAIN_CAL_CH2

43h

RESERVED

USER_GAIN_CAL_CH2

44h

USER_GAIN_CAL_CH3

45h

RESERVED

USER_GAIN_CAL_CH3

46h

USER_GAIN_CAL_CH4

47h

RESERVED

USER_GAIN_CAL_CH4

48h

USER_GAIN_CAL_CH5

49h

RESERVED

USER_GAIN_CAL_CH5

4Ah

USER_GAIN_CAL_CH6

4Bh

RESERVED

USER_GAIN_CAL_CH6

4Ch

USER_GAIN_CAL_CH7

4Dh

RESERVED

USER_GAIN_CAL_CH7

4Eh

USER_GAIN_CAL_CH8

4Fh

RESERVED

USER_GAIN_CAL_CH8

RESERV RD_TEM

ED

P

91h

C0h

RESERVED

USER_GAIN_CAL_CH1

41h

90h

GE_CAL

_EN2

RESERVED

RESERVED

RESERVED

DATA_CLK_CFG1

RESERVED

TEMP_SENSE

DATA_CLK_CFG2

PD_REF

ANA_BW

RESERVED

C1h

DATA_R

ATE

C2h

RANGE_CH4

RANGE_CH3

RANGE_CH2

C3h

RANGE_CH8

RANGE_CH7

RANGE_CH6

RESERVED

CM_ADC_B

PD_CH

RESERVED

CM_ADC_A

RANGE_CH1

RANGE_CH5

DATA_CLK_CFG3

C4h

RESERVED

C5h

28

Submit Document Feedback

WIDE_C

M_EN1

WIDE_CM_EN2

RESERV

ED

PD_CHI

P

RESERVED

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

7.5.2.1 Register Dh (offset = Dh) [reset = 2002h]

Figure 7-24. Register Dh

15

14

13

12

11

10

RESERVED

DATA_FORMAT

RESERVED

R/W-0h

R/W-1h

R/W-0h

7

6

5

4

3

2

GE_CAL_EN1

RESERVED

R/W-0h

R/W-2h

9

8

1

0

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Figure 7-25. Register 0D Field Descriptions

Field

Type

Reset

15-14

RESERVED

R/W

0h

Description

Reserved. Do not change from default reset value.

13-13

DATA_FORMAT

R/W

1h

Select data format for ADC conversion result

0 : Straight binary

1 : 2's complement

12-8

RESERVED

R/W

0h

Reserved. Do not change from default reset value.

7-7

GE_CAL_EN1

R/W

0h

Global control for gain error calibration.

0 : Gain error calibration disabled for all channels.

1 : Gain error calibration enabled for all channels.

6-0

2

R/W

2h

Reserved. Do not change from default reset value.

ADVANCE INFORMATION

Bit

7.5.2.2 Register 12h (offset = 12h) [reset = 2h]

Figure 7-26. Register 12h

15

14

13

12

11

10

3

2

9

8

RESERVED

R/W-0h

7

6

5

4

1

0

RESERVED

XOR_EN

DATA_WIDTH

DATA_LANES

R/W-0h

R/W-0h

R/W-1h

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Figure 7-27. Register 12 Field Descriptions

Bit

Field

Type

Reset

15-4

RESERVED

R/W

0h

Reserved. Do not change from default reset value.

0h

Enables XOR operation on ADC conversion result.

0 : XOR operation is disabled.

1 : ADC conversion result is bit-wise XOR with LSB of the

ADC conversion result.

1h

Select the output data frame width.

0 : 20-bit output frame. Use with 2-lane mode

(DATA_LANES = 0).

1 : 24-bit output frame. Use with 2-lane mode

(DATA_LANES = 0).

2 : 40-bit output frame. Use with 1-lane mode

(DATA_LANES = 1).

3 : 48-bit output frame. Use with 1-lane mode

(DATA_LANES = 1).

3-3

2-1

XOR_EN

DATA_WIDTH

R/W

R/W

Description

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

29

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

Figure 7-27. Register 12 Field Descriptions (continued)

Bit

0-0

Field

Type

DATA_LANES

Reset

R/W

Description

Select number of output data lanes per ADC channel.

0 : 2-lane mode. ADC A data is output on pins D3 and D2.

ADC B data is output on pins D1 and D0.

1 : 1-lane mode. ADC A data is output on pin D3. ADC B

data is output on pin D1.

0h

7.5.2.3 Register 13h (offset = 13h) [reset = 0h]

Figure 7-28. Register 13h

15

14

13

12

11

10

3

2

9

8

RESERVED

R/W-0h

ADVANCE INFORMATION

7

1

0

RAMP_INC_ADC_A

6

5

4

TEST_PAT_MODE_ADC_A

TEST_PAT_EN

_ADC_A

RESERVED

R/W-0h

R/W-0h

R/W-0h

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Figure 7-29. Register 13 Field Descriptions

Bit

Field

Type

Reset

15-8

RESERVED

R/W

0h

Reserved. Do not change from default reset value.

7-4

RAMP_INC_ADC

_A

R/W

0h

Increment value for the ramp pattern output. The output

ramp will increment by N+1 where N is the value configured

in this register.

0h

Select digital test pattern for analog input channels 1, 2, 3,

and 4.

0 : Fixed pattern as configured in TEST_PAT0_ADC_A

register.

1 : Fixed pattern as configured in TEST_PAT1_ADC_A

register.

2 : Digital ramp output.

3 : Alternate fixed pattern output as configured in

TEST_PAT0_ADC_A and TEST_PAT1_ADC_A registers.

3-2

TEST_PAT_MOD

E_ADC_A

R/W

Description

1-1

TEST_PAT_EN_A

DC_A

R/W

0h

Enable digital test pattern for data for data corresponding to

channel 1, 2, 3, and 4.

0 : ADC conversion result will be launched on the data

interface.

1 : Digital test pattern will be launched corresponding to

channels 1, 2, 3, and 4 on the data interface.

0-0

RESERVED

R/W

0h

Reserved. Do not change from default reset value.

7.5.2.4 Register 14h (offset = 14h) [reset = 0h]

Figure 7-30. Register 14h

15

14

13

12

11

10

9

8

2

1

0

TEST_PAT0_ADC_A[23:8]

R/W-0h

7

6

5

4

3

TEST_PAT0_ADC_A[23:8]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

30

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: ADS9817 ADS9815

�ADS9817, ADS9815

www.ti.com

SBASA81 – JANUARY 2023

Figure 7-31. Register 14 Field Descriptions

Bit

Field

Type

Reset

15-0

TEST_PAT0_ADC

_A[23:8]

R/W

0h

Description

Test pattern 0 for channels 1, 2, 3, and 4 corresponding to

ADC A.

7.5.2.5 Register 15h (offset = 15h) [reset = 0h]

Figure 7-32. Register 15h

15

14

13

12

11

10

9

8

2

1

0

TEST_PAT1_ADC_A[23:16]

R/W-0h

7

6

5

4

3

ADVANCE INFORMATION

TEST_PAT0_ADC_A[7:0]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Figure 7-33. Register 15 Field Descriptions

Bit

Field

Type

Reset

Description

15-8

TEST_PAT1_ADC

_A[23:16]

R/W

0h

Test pattern 1 for channels 1, 2, 3, and 4 corresponding to

ADC A.

7-0

TEST_PAT0_ADC

_A[7:0]

R/W

0h

Test pattern 0 for channels 1, 2, 3, and 4 corresponding to

ADC A.

7.5.2.6 Register 16h (offset = 16h) [reset = 0h]

Figure 7-34. Register 16h

15

14

13

12

11

10

9

8

2

1

0

TEST_PAT1_ADC_A[15:0]

R/W-0h

7

6

5

4

3

TEST_PAT1_ADC_A[15:0]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset