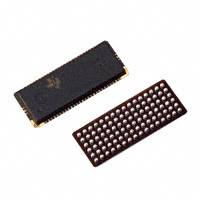

SN74GTLPH32945

32-BIT LVTTL-TO-GTLP BUS TRANSCEIVER

SCES293C – OCTOBER 1999 – REVISED NOVEMBER 2001

D

D

D

D

D

D

Member of the Texas Instruments

Widebus+ Family

TI-OPC Circuitry Limits Ringing on

Unevenly Loaded Backplanes

OEC Circuitry Improves Signal Integrity

and Reduces Electromagnetic Interference

Bidirectional Interface Between GTLP

Signal Levels and LVTTL Logic Levels

LVTTL Interfaces Are 5-V Tolerant

Medium-Drive GTLP Outputs (50 mA)

D

D

D

D

D

D

LVTTL Outputs (–24 mA/24 mA)

GTLP Rise and Fall Times Designed for

Optimal Data-Transfer Rate and Signal

Integrity in Distributed Loads

Ioff, Power-Up 3-State, and BIAS VCC

Support Live Insertion

Bus Hold on A-Port Data Inputs

Distributed VCC and GND Pins Minimize

High-Speed Switching Noise

Latch-Up Performance Exceeds 100 mA Per

JESD 78, Class II

description

The SN74GTLPH32945 is a medium-drive, 32-bit bus transceiver that provides LVTTL-to-GTLP and

GTLP-to-LVTTL signal-level translation. It is partitioned as four 8-bit transceivers. The device provides a

high-speed interface between cards operating at LVTTL logic levels and a backplane operating at GTLP signal

levels. High-speed (about three times faster than standard TTL or LVTTL) backplane operation is a direct result

of GTLP’s reduced output swing ( VCC.

3. The package thermal impedance is calculated in accordance with JESD 51-7.

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

5

�SN74GTLPH32945

32-BIT LVTTL-TO-GTLP BUS TRANSCEIVER

SCES293C – OCTOBER 1999 – REVISED NOVEMBER 2001

recommended operating conditions (see Notes 4 through 7)

VCC,

BIAS VCC

Supply voltage

VTT

Termination voltage

VREF

Reference voltage

VI

Input voltage

VIH

High level input voltage

High-level

VIL

Low level input voltage

Low-level

IIK

IOH

Input clamp current

Low level output current

Low-level

∆t/∆v

Input transition rise or fall rate

∆t/∆VCC

TA

Power-up ramp rate

NOM

MAX

UNIT

3.15

3.3

3.45

V

GTL

1.14

1.2

1.26

GTLP

1.35

1.5

1.65

GTL

0.74

0.8

0.87

GTLP

0.87

1

1.1

VCC

VTT

5.5

B port

Except B port

B port

Except B port

VREF+0.05

2

B port

V

V

V

V

VREF–0.05

0.8

V

–18

mA

A port

–24

mA

A port

24

B port

50

Except B port

High-level output current

IOL

MIN

Outputs enabled

10

–40

ns/V

µs/V

20

Operating free-air temperature

mA

85

°C

NOTES: 4. All unused inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

5. Proper connection sequence for use of the B-port I/O precharge feature is GND and BIAS VCC = 3.3 V first, I/O second, and

VCC = 3.3 V last, because the BIAS VCC precharge circuitry is disabled when any VCC pin is connected. The control and VREF inputs

can be connected anytime, but normally are connected during the I/O stage. If B-port precharge is not required, any connection

sequence is acceptable, but generally, GND is connected first.

6. VTT and RTT can be adjusted to accommodate backplane impedances if the dc recommended IOL ratings are not exceeded.

7. VREF can be adjusted to optimize noise margins, but normally is two-thirds VTT. TI-OPC circuitry is enabled in the A-to-B direction

and is activated when VTT > 0.7 V above VREF. If operated in the A-to-B direction, VREF should be set to within 0.6 V of VTT to

minimize current drain.

6

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

�SN74GTLPH32945

32-BIT LVTTL-TO-GTLP BUS TRANSCEIVER

SCES293C – OCTOBER 1999 – REVISED NOVEMBER 2001

electrical characteristics over recommended operating free-air temperature range for GTLP

(unless otherwise noted)

PARAMETER

VIK

VOH

A port

TEST CONDITIONS

VCC = 3.15 V,

VCC = 3.15 V to 3.45 V,

II = –18 mA

IOH = –100 µA

VCC = 3

3.15

15 V

IOH = –12 mA

IOH = –24 mA

VOL

B port

II

Control inputs

A port

IOZH‡

B port

TYP†

MAX

UNIT

–1.2

V

VCC–0.2

2.4

V

2

IOL = 100 µA

IOL = 12 mA

0.2

0.5

VCC = 3.15 V to 3.45 V,

IOL = 24 mA

IOL = 100 µA

0.2

VCC = 3.15 V

IOL = 10 mA

IOL = 40 mA

IOL = 50 mA

0.55

VI = 0 or 5.5 V

±10

VCC = 3.15 V to 3.45 V,

A port

MIN

VCC = 3

3.15

15 V

VCC = 3.45 V,

VCC = 3

3.45

45 V

0.4

0.2

0.4

VO = VCC

10

VO = 1.5 V

10

–10

IOZL‡

IBHL§

A and B ports

VCC = 3.45 V,

VO = GND

A port

IBHH¶

IBHLO#

IBHHO||

A port

VCC = 3.15 V,

VCC = 3.15 V,

VI = 0.8 V

VI = 2 V

VCC = 3.45 V,

VCC = 3.45 V,

VI = 0 to VCC

VI = 0 to VCC

VCC = 3.45 V, IO = 0,

VI (A-port or control input) = VCC or GND,

VI (B port) = VTT or GND

Outputs high

100

Outputs low

100

Outputs disabled

100

ICC

A port

A port

A or B port

Ci

Ciio

Control inputs

µA

µA

µA

75

µA

–75

µA

500

µA

µA

–500

VCC = 3.45 V, One A-port or control input at VCC – 0.6 V,

Other A-port or control inputs at VCC or GND

∆ICCk

V

mA

1

mA

pF

4.5

5

A port

VI = 3.15 V or 0

VO = 3.15 V or 0

7.5

9

B port

VO = 1.5 V or 0

7.5

9

pF

† All typical values are at VCC = 3.3 V, TA = 25°C.

‡ For I/O ports, the parameters IOZH and IOZL include the input leakage current.

§ The bus-hold circuit can sink at least the minimum low sustaining current at VILmax. IBHL should be measured after lowering VIN to GND and

then raising it to VILmax.

¶ The bus-hold circuit can source at least the minimum high sustaining current at VIHmin. IBHH should be measured after raising VIN to VCC and

then lowering it to VIHmin.

# An external driver must source at least IBHLO to switch this node from low to high.

|| An external driver must sink at least IBHHO to switch this node from high to low.

k This is the increase in supply current for each input that is at the specified TTL voltage level rather than VCC or GND.

hot-insertion specifications for A port over recommended operating free-air temperature range

PARAMETER

TEST CONDITIONS

MIN

MAX

UNIT

10

µA

VO = 0.5 V to 3 V,

VI or VO = 0 to 5.5 V

OE = 0

±30

µA

VO = 0.5 V to 3 V,

OE = 0

±30

µA

Ioff

IOZPU

VCC = 0,

VCC = 0 to 1.5 V,

BIAS VCC = 0,

IOZPD

VCC = 1.5 V to 0,

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

7

�SN74GTLPH32945

32-BIT LVTTL-TO-GTLP BUS TRANSCEIVER

SCES293C – OCTOBER 1999 – REVISED NOVEMBER 2001

live-insertion specifications for B port over recommended operating free-air temperature range

PARAMETER

TEST CONDITIONS

BIAS VCC = 0,

±30

µA

BIAS VCC = 0,

VO = 0.5 V to 1.5 V, OE = 0

±30

µA

BIAS VCC = 3

3.15

15 V to 3

3.45

45 V

V,

VO (B port) = 0 to 1.5

15V

BIAS VCC = 3.3 V,

IO = 0

VO (B port) = 0.6 V

IOZPD

VCC = 1.5 V to 0,

VCC = 0 to 3.15 V

VO

IO

VCC = 0,

UNIT

µA

BIAS VCC = 0,

VCC = 3.15 V to 3.45 V

VCC = 0,

MAX

10

VCC = 0,

VCC = 0 to 1.5 V,

ICC (BIAS VCC)

MIN

VI or VO = 0 to 1.5 V

VO = 0.5 V to 1.5 V, OE = 0

Ioff

IOZPU

BIAS VCC = 3.15 V to 3.45 V,

0.95

5

mA

10

µA

1.05

V

µA

–1

switching characteristics over recommended ranges of supply voltage and operating free-air

temperature, VTT = 1.5 V and VREF = 1 V for GTLP (see Figure 1)

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

tPLH

tPHL

A

B

OE

B

ten

tdis

tr

tf

tPLH

tPHL

ten

tdis

TYP†

MAX

2.1

6.3

2.1

6.3

2

6.9

2

6.9

UNIT

ns

ns

Rise time, B outputs (20% to 80%)

2.5

ns

Fall time, B outputs (80% to 20%)

2.1

ns

B

A

OE

A

† All typical values are at VCC = 3.3 V, TA = 25°C.

8

MIN

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

2.1

5.3

2.1

5.3

0.3

5.7

0.3

5.7

ns

ns

�SN74GTLPH32945

32-BIT LVTTL-TO-GTLP BUS TRANSCEIVER

SCES293C – OCTOBER 1999 – REVISED NOVEMBER 2001

PARAMETER MEASUREMENT INFORMATION

1.5 V

6V

500 Ω

From Output

Under Test

S1

Open

GND

CL = 50 pF

(see Note A)

TEST

tPLH/tPHL

tPLZ/tPZL

tPHZ/tPZH

500 Ω

25 Ω

From Output

Under Test

CL = 30 pF

(see Note A)

S1

Open

6V

GND

LOAD CIRCUIT FOR A OUTPUTS

Test

Point

LOAD CIRCUIT FOR B OUTPUTS

3V

1.5 V

Input

1.5 V

0V

tPLH

tPHL

VOH

1V

Output

1V

VOL

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

(A port to B port)

1V

0V

tPLH

1.5 V

1.5 V

0V

Output

Waveform 1

S1 at 6 V

(see Note B)

tPHL

tPLZ

3V

1.5 V

VOL + 0.3 V

VOL

tPHZ

tPZH

VOH

Output

1.5 V

tPZL

1.5 V

1V

Input

3V

Output

Control

1.5 V

VOL

Output

Waveform 2

S1 at GND

(see Note B)

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

(B port to A port)

1.5 V

VOH

VOH – 0.3 V

≈0 V

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES

(A port)

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≈ 10 MHz, ZO = 50 Ω, tr ≈ 2 ns, tf ≈ 2 ns.

D. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuits and Voltage Waveforms

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

9

�SN74GTLPH32945

32-BIT LVTTL-TO-GTLP BUS TRANSCEIVER

SCES293C – OCTOBER 1999 – REVISED NOVEMBER 2001

DISTRIBUTED-LOAD BACKPLANE SWITCHING CHARACTERISTICS

The preceding switching characteristics table shows the switching characteristics of the device into a lumped load

(Figure 1). However, the designer’s backplane application probably is a distributed load. The physical representation

is shown in Figure 2. This backplane, or distributed load, can be approximated closely to a resistor inductance

capacitance (RLC) circuit, as shown in Figure 3. This device has been designed for optimum performance in this RLC

circuit. The following switching characteristics table shows the switching characteristics of the device into the RLC

load, to help the designer better understand the performance of the GTLP device in this typical backplane. See

www.ti.com/sc/gtlp for more information.

38 Ω

.25”

ZO = 70 Ω

2”

2”

.25”

38 Ω

1.5 V

1.5 V

1.5 V

Conn.

Conn.

1”

Conn.

1”

1”

Conn.

19 Ω

From Output

Under Test

1”

Rcvr

Rcvr

Rcvr

Slot 2

Slot 9

Slot 10

LL = 19 nH

CL = 9 pF

Drvr

Slot 1

Test

Point

Figure 2. Medium-Drive Test Backplane

Figure 3. Medium-Drive RLC Network

switching characteristics over recommended ranges of supply voltage and operating free-air

temperature, VTT = 1.5 V and VREF = 1 V for GTLP (see Figure 3)

PARAMETER

tPLH

tPHL

ten

tdis

tr

tf

FROM

(INPUT)

TO

(OUTPUT)

A

B

OE

B

4.3

4.3

5

4.4

UNIT

ns

ns

Rise time, B outputs (20% to 80%)

1

ns

Fall time, B outputs (80% to 20%)

2

ns

† All typical values are at VCC = 3.3 V, TA = 25°C. All values are derived from TI-SPICE models.

10

TYP†

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

��IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI’s terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty. Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. To minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third-party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application

solutions:

Products

Applications

Amplifiers

amplifier.ti.com

Audio

www.ti.com/audio

Data Converters

dataconverter.ti.com

Automotive

www.ti.com/automotive

DSP

dsp.ti.com

Broadband

www.ti.com/broadband

Interface

interface.ti.com

Digital Control

www.ti.com/digitalcontrol

Logic

logic.ti.com

Military

www.ti.com/military

Power Mgmt

power.ti.com

Optical Networking

www.ti.com/opticalnetwork

Microcontrollers

microcontroller.ti.com

Security

www.ti.com/security

Telephony

www.ti.com/telephony

Video & Imaging

www.ti.com/video

Wireless

www.ti.com/wireless

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright 2004, Texas Instruments Incorporated

�