THS9000

www.ti.com

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

50 MHz to 750 MHz CASCADEABLE AMPLIFIER

Check for Samples: THS9000

FEATURES

APPLICATIONS

•

•

1

23

•

•

•

High Dynamic Range

– OIP3 = 36 dBm

– NF < 4.5 dB

Single-Supply Voltage

High Speed

– VS = 3 V to 5 V

– IS = Adjustable

Input/Output Impedance

– 50 Ω

IF

–

–

–

–

Amplifiers

TDMA: GSM, IS-136, EDGE/UWE-136

CDMA: IS-95, UMTS, CDMA2000

Wireless Local Loops

Wireless LAN: IEEE802.11

DESCRIPTION

The THS9000 is a medium power, cascadeable, gain block optimized for high IF frequencies. The amplifier

incorporates internal impedance matching to 50 Ω. The part mounted on the standard EVM achieves greater

than 15-dB input and output return loss from 50 MHz to 325 MHz with VS = 5 V, R(BIAS) = 237 Ω, L(COL) = 470 nH.

Design requires only two dc-blocking capacitors, one power-supply bypass capacitor, one RF choke, and one

bias resistor.

Figure 1. FUNCTIONAL BLOCK DIAGRAM

VS

C(BYP)

L(COL)

IF(OUT)

C(BLK)

6

5

4

1

2

3

THS9000

IF(IN)

C(BLK)

VS

R(BIAS)

1

2

3

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2003–2013, Texas Instruments Incorporated

�THS9000

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

AVAILABLE OPTIONS

PACKAGED DEVICE

(1)

THS9000DRWT

THS9000DRWR

(1)

(2)

PACKAGE TYPE

TRANSPORT MEDIA, QUANTITY

Tape and Reel, 250

2 × 2 QFN (2)

Tape and Reel, 3000

For the most current package and ordering information, see the Package Option Addendum at the end

of this document, or see the TI Web site at www.ti.com.

The PowerPAD™ is electrically isolated from all other pins.

ABSOLUTE MAXIMUM RATINGS

Over operating free-air temperature (unless otherwise noted) (1)

THS9000

Supply voltage, GND to VS

UNIT

5.5

Input voltage

V

GND to VS

Continuous power dissipation

See Dissipation Rating table

Maximum junction temperature, TJ

+150

Maximum junction temperature, continuous operation, long term reliability,

TJ (2)

+125

Storage temperature, Tstg

(1)

(2)

°C

–65 to +150

°C

+300

°C

HBM

2000

V

CDM

1500

V

MM

100

V

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds

ESD Ratings:

°C

The absolute maximum ratings under any condition is limited by the constraints of the silicon process. Stresses above these ratings may

cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are

stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

The maximum junction temperature for continuous operation is limited by package constraints. Operation above this temperature may

result in reduced reliability and/or lifetime of the device.

DISSIPATION RATING TABLE

PACKAGE

DRW

(1)

(2)

(3)

(2) (3)

POWER RATING (1)

θJA

(°C/W)

TA ≤ +25°C

TA = +85°C

91

1.1 W

440 mW

Power rating is determined with a junction temperature of +125°C. Thermal management of the final PCB should strive to keep the

junction temperature at or below +125°C for best performance.

This data was taken using the JEDEC standard High-K test PCB.

The THS9000 incorporates a PowerPAD on the underside of the chip. This acts as a heatsink and must be connected to a thermally

dissipating plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature, which could

permanently damage the device. See TI Technical Brief SLMA002 for more information about utilizing the PowerPAD thermallyenhanced package.

RECOMMENDED OPERATING CONDITIONS

MIN

NOM

MAX

UNIT

Supply voltage

2.7

5

V

Operating free-air temperature, TA

–40

+85

°C

Supply current

2

100

Submit Documentation Feedback

mA

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

�THS9000

www.ti.com

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

ELECTRICAL CHARACTERISTICS

Typical Performance (VS = 5 V, R(BIAS) = 237 Ω, L(COL) = 470 nH) (unless otherwise noted)

PARAMETER

TEST CONDITIONS

Gain

OIP3

1-dB compression

Input return loss

Output return loss

Reverse isolation

Noise figure

MIN

TYP

f = 50 MHz

15.9

f = 350 MHz

15.6

f = 50 MHz

36

f = 350 MHz

35

f = 50 MHz

20.8

f = 350 MHz

20.6

f = 50 MHz

15

f = 350 MHz

19.7

f = 50 MHz

17.2

f = 350 MHz

15.1

f = 50 MHz

21

f = 350 MHz

20

f = 50 MHz

3.6

f = 350 MHz

4

MAX

UNITS

dB

dBm

dBm

dB

dB

dB

dB

PIN ASSIGNMENT

IF(IN) 1

6

VS

GND 2

5

L(COL)

BIAS 3

4

IF(OUT)

Terminal Functions

PIN NUMBERS

NAME

DESCRIPTION

1

IF(IN)

Signal input

2

GND

Negative power-supply input

3

BIAS

Bias current adjustment input

4

IF(OUT)

Signal output

5

L(COL)

Output transistor load inductor

6

VS

Positive power-supply input

SIMPLIFIED SCHEMATIC

VS

L(COL)

BIAS

IF(OUT)

IF(IN)

GND

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

3

�THS9000

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

www.ti.com

TABLE OF GRAPHS

FIGURE

IS

S21 Frequency response

1

S22 Frequency response

2

S11 Frequency response

3

S12 Frequency response

4

S21 vs R(Bias)

5

Output power vs Input power

6

OIP2 vs Frequency

7

Noise figure vs Frequency

8

OIP3 vs Frequency

9

Supply current vs R(Bias)

10

S21 Frequency response

11

S22 Frequency response

12

S11 Frequency response

13

S12 Frequency response

14

Noise figure vs Frequency

15

OIP2 vs Frequency

16

Output power vs Input power

17

OIP3 vs Frequency

18

TYPICAL CHARACTERISTICS

S-Parameters of THS9000 as mounted on the EVM with VS = 5 V, R(BIAS) = 237 Ω, and L(COL) = 68 nH to 470 nH

at room temperature.

S21

FREQUENCY RESPONSE

17

S22

FREQUENCY RESPONSE

0

L(COL) = 470 nH

L(COL) = 68 nH

L(COL) = 220 nH

16

L(COL) = 100 nH

L(COL) = 330 nH

−5

S22 − dB

S21 − dB

15

14

−10

L(COL) = 220 nH

13

L(COL) = 100 nH

L(COL) = 330 nH

12

−15

L(COL) = 470 nH

L(COL) = 68 nH

11

VS = 5 V,

R(BIAS) = 237W,

10

1M

10 M

100 M

VS = 5 V,

R(BIAS) = 237W,

−20

1G

1M

4

10 M

100 M

1G

f − Frequency − Hz

f − Frequency − Hz

Figure 2.

Figure 3.

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

�THS9000

www.ti.com

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS (continued)

S11

FREQUENCY RESPONSE

0

S12

FREQUENCY RESPONSE

−15

L(COL) = 68 nH

−5

L(COL) = 470 nH

L(COL) = 220 nH

−15

S12 − dB

S11 − dB

−20

L(COL) = 100 nH

−10

L(COL) = 330 nH

−20

L(COL) = 470 nH

−25

VS = 5 V,

R(BIAS) = 237W,

L(COL) = 330 nH

−25

L(COL) = 220 nH

−30

L(COL) = 100 nH

−30

L(COL) = 68 nH

−35

−35

VS = 5 V,

R(BIAS) = 237W,

−40

−45

1M

10 M

100 M

f − Frequency − Hz

Figure 4.

−40

1G

10 M

100 M

f − Frequency − Hz

Figure 5.

1M

1G

S-Parameters of THS9000 as mounted on the EVM with VS = 3 V and 5 V, R(BIAS) = various, and L(COL) = 470 nH

at room temp.

S21

vs

R(BIAS)

17

OUTPUT POWER

vs

INPUT POWER

22

R(BIAS) = 56.2 W,

VS = 3 V

R(BIAS) = 237 W,

VS = 5 V

VS = 5 V, IS = 97 mA

21

16

PO − Output Power − dBm

15

S21 − dB

VS = 5 V, IS = 71 mA

20

R(BIAS) = 97.7W,

VS = 3 V

14

R(BIAS) = 340 W,

VS = 5 V

13

R(BIAS) = 174 W, VS = 3 V

R(BIAS) = 549 W, VS = 5 V

12

19

VS = 5 V, IS = 48 mA

18

17

16

15

VS = 3 V, IS = 69 mA

14

VS = 3 V, IS = 49 mA

13

VS = 3 to 5 V,

R(BIAS) = Various,

L(COL) = 470 nH

11

11

10

1M

10 M

100 M

f − Frequency − Hz

VS = 3 V, IS = 91 mA

12

1G

10

−6

Figure 6.

−4

−2

0

2

4

6

8

PI − Input Power − dBm

Figure 7.

10

12

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

14

5

�THS9000

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS (continued)

OIP2

vs

FREQUENCY

NOISE FIGURE

vs

FREQUENCY

50

5

VS = 5 V,

IS = 97 mA

48

VS = 3 V,

IS = 91 mA

VS = 3 V,

IS = 69 mA

44

42

40

VS = 5 V, IS = 71 mA

4.5

Noise Figure − dB

OIP2 − dBm

46

VS = 5 V, IS = 97 mA

4.75

VS = 5 V, IS = 71 mA

VS = 5 V, IS = 48 mA

4.25

4

VS = 3 V,

IS = 70 mA

3.75

VS = 3 V, IS = 49 mA

VS = 3 V, IS = 49 mA

38

3.5

36

VS = 3 V, IS = 91 mA

3.25

VS = 5 V, IS = 48 mA

34

0

50

150

100

200

f − Frequency − MHz

250

3

300

0

100

Figure 8.

OIP3

vs

FREQUENCY

500

450

550

200

VS = 5 V, IS = 71 mA

38

VS = 5 V, IS = 97 mA

180

I S − Supply Current − mA

VS = 3 V, IS = 91 mA

36

OIP3 − dBm

400

SUPPLY CURRENT

vs

R(BIAS)

40

34

32

VS = 3 V, IS = 69 mA

30

28

26

24

100

200

300

f − Frequency − MHz

140

120

VS = 5 V

100

80

VS = 3 V

40

VS = 5 V, IS = 48 mA

0

160

60

VS = 3 V, IS = 49 mA

400

500

20

50

Figure 10.

6

200

300

f − Frequency − MHz

Figure 9.

150

250

350

R(BIAS) − W

Figure 11.

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

�THS9000

www.ti.com

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS (continued)

THS9000 as mounted on the EVM with VS = 5 V, R(BIAS) = 237 Ω, and L(COL) = 470 nH at +40°C, +25°C, and

+85°C.

S21

FREQUENCY RESPONSE

17

S22

FREQUENCY RESPONSE

0

TA = −455C

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 470 nH

16

15

−5

TA = 855C

S22 − dB

S21 − S-Parameters − dB

TA = 255C

14

−10

TA = 855C

13

12

VS = 5 V,

R(BIAS) = 327 W,

L(COL) = 470 nH

11

10

TA = 255C

−15

1M

TA = −455C

−20

10 M

100 M

f − Frequency − Hz

Figure 12.

1G

1M

S12

FREQUENCY RESPONSE

−15

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 470 nH

−5

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 470 nH

TA = −455C

−20

−10

−15

S12 − dB

S11 − dB

1G

Figure 13.

S11

FREQUENCY RESPONSE

0

10 M

100 M

f − Frequency − Hz

−20

TA = 255C

−25

TA = 855C

−25

−30

TA = 855C

−30

−35

TA = −455C

−40

TA = 255C

−45

−35

−40

1M

10 M

100 M

1G

1M

f − Frequency − Hz

Figure 14.

10 M

100 M

f − Frequency − Hz

1G

Figure 15.

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

7

�THS9000

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

www.ti.com

TYPICAL CHARACTERISTICS (continued)

NOISE FIGURE

vs

FREQUENCY

OIP2

vs

FREQUENCY

50

6

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 470 nH

5.5

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 470 nH

49

48

47

5

OIP2 − dBm

Noise Figure − dB

TA = 855C

4.5

TA = 255C

4

TA = −455C

46

45

44

TA = 255C

43

TA = 855C

42

3.5

41

TA = −455C

3

40

0

100

200

300

f − Frequency − MHz

Figure 16.

400

100

50

500

150

OUTPUT POWER

vs

INPUT POWER

TA = 855C

39

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 470 nH

TA = 255C

38

OIP3 − dBm

PO − Output Power − dBm

300

40

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 470 nH

f = 100 MHz

20

19

18

250

OIP3

vs

FREQUENCY

22

21

200

f − Frequency − MHz

Figure 17.

TA = −455C

37

TA = −455C

36

TA = 855C

35

17

34

16

TA = 255C

33

15

14

−2

8

0

2

4

6

8

PI − Input Power − dBm

Figure 18.

10

12

32

50

100 150 200 250 300 350 400 450 500

f − Frequency − MHz

Figure 19.

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

�THS9000

www.ti.com

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

TYPICAL CHARACTERISTICS

Table 1. S-Parameters Tables of THS9000 with EVM De-Embedded

VS = 5 V, R(BIAS) = 237 Ω, L(COL) = 470 nH

S21

S11

S22

S12

FREQUENCY

(MHz)

GAIN (dB)

PHASE (°)

GAIN (dB)

PHASE (°)

GAIN (dB)

PHASE (°)

GAIN (dB)

PHASE (°)

1.0

–4.2

–169.5

–2.4

–0.9

–1.9

158.1

–63.1

167.0

5.0

11.3

–124.5

–1.5

–14.5

–2.6

138.0

–32.9

122.4

10.2

15.8

–147.8

–2.2

–42.3

–5.0

101.0

–24.0

80.4

19.7

16.4

–169.4

–6.5

–69.7

–10.5

66.6

–21.3

41.6

50.1

16.0

177.2

–15.6

–91.4

–16.7

30.1

–20.7

14.4

69.7

15.9

173.5

–19.8

–97.7

–17.8

17.7

–20.7

9.1

102.4

15.9

168.4

–26.9

–102.6

–18.2

4.3

–20.7

4.4

150.5

15.8

162.0

–39.0

14.1

–18.1

–8.6

–20.7

–0.7

198.1

15.7

155.8

–27.6

50.8

–17.4

–19.6

–20.7

–1.7

246.9

15.7

149.6

–23.7

40.6

–16.4

–26.7

–20.7

–3.5

307.6

15.6

141.9

–19.8

33.1

–14.9

–37.2

–20.6

–5.7

362.8

15.6

134.7

–17.3

24.7

–13.3

–44.3

–20.4

–7.7

405.0

15.6

129.2

–15.5

20.3

–12.1

–51.0

–20.2

–10.0

452.2

15.6

122.3

–13.8

14.7

–10.6

–58.1

–19.9

–12.5

504.7

15.5

114.9

–11.8

6.3

–9.0

–66.5

–19.7

–16.2

563.4

15.4

105.8

–9.7

–2.9

–7.2

–77.5

–19.4

–22.4

595.3

15.3

100.5

–8.6

–9.1

–6.3

–83.6

–19.3

–26.2

664.5

14.9

88.7

–6.3

–24.2

–4.4

–99.7

–19.3

–36.7

702.1

14.6

81.0

–5.3

–33.2

–3.7

–109.2

–19.6

–43.4

741.8

14.1

76.3

–4.4

–42.9

–3.0

–118.8

–19.9

–50.2

828.1

12.7

60.2

–2.9

–65.5

–2.3

–142.8

–21.7

–69.2

874.9

11.2

51.0

–2.5

–77.9

–2.5

–155.0

–23.6

–75.0

924.4

10.1

50.2

–2.4

–90.4

–3.1

–166.0

–25.8

–85.2

976.7

8.8

51.8

–2.5

––100.7

–4.3

–173.7

–28.4

–78.9

1031.9

9.2

58.2

–2.6

–108.7

–4.7

–175.2

–29.7

–68.7

1090.3

8.9

48.0

–2.5

–115.2

–4.4

–164.7

–31.4

–69.1

1151.9

8.8

39.9

–2.3

–123.3

–3.5

–175.4

–33.6

–83.4

1217.1

8.0

27.7

–2.1

–132.0

–3.0

175.3

–38.2

–81.4

1285.9

7.0

30.5

–2.0

–140.7

–2.8

168.7

–42.3

–25.5

1358.6

5.6

20.6

–1.9

–149.4

–2.9

159.1

–42.2

41.6

1435.5

4.3

19.5

–1.8

–159.4

–3.0

151.3

–38.7

63.3

1516.6

3.4

17.7

–1.9

–168.3

–3.2

144.7

–33.6

62.4

1602.4

2.8

16.5

–2.0

–177.2

–3.5

138.2

–30.5

59.6

1693.0

2.2

8.6

–2.1

174.0

–3.8

131.4

–28.1

56.2

1788.8

1.4

–0.7

–2.2

165.4

–4.1

124.6

–26.2

50.4

1889.9

0.5

–4.1

–2.3

157.0

–4.5

118.2

–24.7

42.4

1996.8

–0.6

–4.5

–2.6

150.0

–4.9

111.2

–24.2

39.5

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

9

�THS9000

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

www.ti.com

APPLICATION INFORMATION

The THS9000 is a medium power, cascadeable, amplifier optimized for high intermediate frequencies in radios.

The amplifier is unconditionally stable and the design requires only two dc-blocking capacitors, one power-supply

bypass capacitor, one RF choke, and one bias resistor. Refer to Figure 26 for the circuit diagram.

The THS9000 operates with a power-supply voltage ranging from 2.5 V to 5.5 V.

The value of R(BIAS) sets the bias current to the amplifier. Refer to Figure 11. This allows the designer to trade-off

linearity versus power consumption. R(BIAS) can be removed without damage to the device.

Component selection of C(BYP), CIN, and COUT is not critical. The values shown in Figure 26 were used for all the

data shown in this data sheet.

The amplifier incorporates internal impedance matching to 50 Ω that can be adjusted for various frequencies of

operation by proper selection of L(COL).

Figure 20 shows the s-parameters of the part mounted on the standard EVM with VS = 5 V, R(BIAS) = 237 Ω, and

L(COL) = 470 nH. With this configuration, the part is very broadband, and achieves greater than 15-dB input and

output return loss from 50 MHz to 325 MHz.

Figure 21 shows the S-parameters of the part mounted on the standard EVM with VS = 5 V, R(BIAS) = 237 Ω, and

L(COL) = 68 nH. With this configuration, the part achieves greater than 15-dB input and output return loss from

250 MHz to 400 MHz.

16

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 470 nH

0

0

15

−15

13

S22

−20

12

−10

13

−15

12

11

11

−25

S12

−30

1M

10 M

100 M

1G

S12

10

−20

VS = 5 V,

R(BIAS) = 237 W,

L(COL) = 68 nH

−25

10

−30

1M

f − Frequency − Hz

Figure 20. S-Parameters of THS9000 mounted on

the standard EVM with VS = 5 V, R(BIAS) = 237 Ω,

and L(COL) = 470 nH

−5

S11

14

S21 − dB

−10

14

S11, S12, S22 − dB

−5

15

10

5

S21

S22

S11, S12, S22 − dB

S21

S11

S21 − dB

16

5

17

100 M

10 M

f − Frequency − Hz

1G

Figure 21. S-Parameters of THS9000 mounted on

the standard EVM with VS = 5 V, R(BIAS) = 237 Ω,

and L(COL) = 68 nH

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

�THS9000

www.ti.com

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

Figure 22 shows an example of a single conversion receiver architecture and where the THS9000 would typically

be used.

900 MHz − 2 GHz

900 MHz − 2 GHz

Image Rejection

Filter

LNA 2

LNA 1

LO Drive

Amp 1

RX LO

IF Amp 1

Mixer

IF Amp 2

IF SAW

PGA

IF SAW

ADC

LO Drive

Amp 2

THS9000

2x for Diversity

Figure 22. Example Single Conversion Receiver Architecture

Figure 23 shows an example of a dual conversion receiver architecture and where the THS9000 would typically

be used.

900 MHz − 2 GHz

LNA 1

100 MHz − 300 MHz

1st IF Amp

Image Reject

Filter 1st Mixer

1st IF SAW PGA

LNA 2

LO1 Drive LO1 Drive

Amp 2

RX LO 1 Amp 1

20 MHz − 70 MHz

2nd IF Amp1

2nd IF SAW 2nd IF

Amp2

2nd Mixer

Alias Filter

ADC

LO2 Drive LO2 Drive

Amp 1

Amp 2

RX LO2

THS9000

2x for Diversity

Figure 23. Example Dual Conversion Receiver Architecture

Figure 24 shows an example of a dual conversion transmitter architecture and where the THS9000 would

typically be used.

BB

100 MHz − 300 MHz

900 MHz − 2 GHz

1st IF amp

DAC

RX LO1

BB Amp

Alias Filter 1st Mixer

LO1 Drive LO1 Drive

Amp 2

Amp 1

IF SAW

RX LO2

PGA

2nd Mixer

PA

LO2 Drive LO2 Drive

Amp 2

Amp 1

THS9000

2x for Diversity

Figure 24. Example Dual Conversion Transmitter Architecture

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

11

�THS9000

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

www.ti.com

Figure 25 shows the THS9000 and Sawtek #854916 SAW filter frequency response along with the frequency

response of the SAW filter alone. The SAW filter has a center frequency of 140 MHz with 10-MHz bandwidth and

8-dB insertion loss. It can be seen that the frequency response with the THS9000 is the same as with the SAW

except for a 15-dB gain. The THS9000 is mounted on the standard EVM with VS = 5 V, R(BIAS) = 237 Ω, and

L(COL) = 470 nH. Note the amplifier does not add artifacts to the signal.

SAW + THS9000

THS9000

SAW

RED =

SAW

140 MHz

SAW Only

GREEN =

140 MHz SAW: Sawtek #854916

Figure 25. Frequency Response of the THS9000 and SAW Filter, and SAW Filter Only

VS

C(BYP)

0.1 mF

CO IF(OUT)

L(COL)

1 nF

6

5

4

1

2

3

THS9000

IF(IN)

CI

R(BIAS)

1 nF

VS

Figure 26. THS9000 Recommended Circuit (used for all tests)

12

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

�THS9000

www.ti.com

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

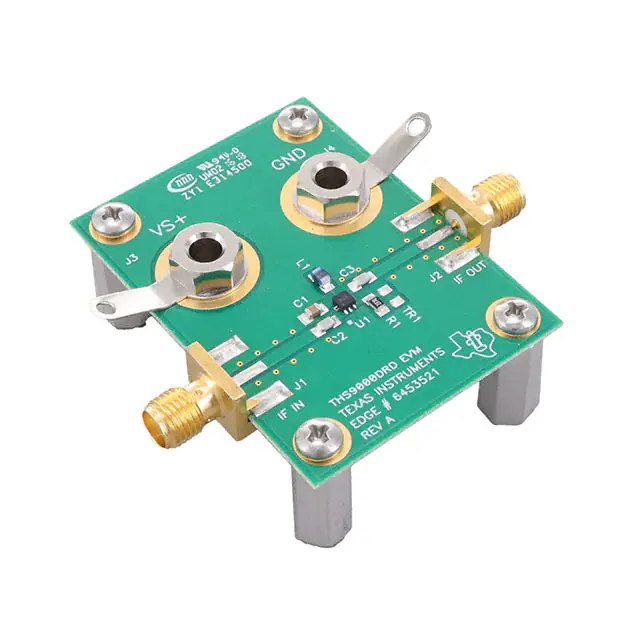

Evaluation Module

Table 1 is the bill of materials, and Figure 27 and Figure 28 show the EVM layout.

Bill Of Materials

ITEM

(1)

DESCRIPTION

1

Cap, 0.1 μF, ceramic, X7R, 50 V

2

Cap, 1000 pF, ceramic, NPO, 100 V

3

Inductor, 470 nH, 5%

4

Resistor, 237 Ω, 1/8 W, 1%

5

Open

6

REF DES

QTY

PART NUMBER (1)

(AVX) 08055C104KAT2A

C1

1

C2, C3

2

(AVX) 08051A102JAT2A

L1

1

(Coilcraft) 0805CS-471XJBC

(Phycomp) 9C08052A2370FKHFT

R1

1

TR1

1

Jack, banana receptance, 0.25" dia.

J3, J4

2

(SPC) 813

7

Connector, edge, SMA PCB jack

J1, J2

2

(Johnson) 142-0701-801

8

Standoff, 4-40 Hex, 0.625" Length

4

(KEYSTONE) 1808

9

Screw, Phillips, 4-40, .250"

4

SHR-0440-016-SN

10

IC, THS9000

1

(TI) THS9000DRD

11

Board, printed-circuit

1

(TI) EDGE # 6453521 Rev.A

U1

The manufacturer's part numbers are used for test purposes only.

Figure 27. EVM Top Layout

Figure 28. EVM Bottom Layout

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

13

�THS9000

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

www.ti.com

0.110

(2,79)

0.050

(1,27)

0.025

(0,64)

0.140

(3,56)

0.010

(0,254)

vias

0.080

(2,03)

0.028

(0,711)

0.032

(0,81)

0.011

(0,28)

0.015

(0,381)

Figure 29. THS9000 Recommended Footprint dimensions are in inches (millimeters)

14

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

�THS9000

www.ti.com

SLOS425E – DECEMBER 2003 – REVISED DECEMBER 2013

REVISION HISTORY

Changes from Revision D (October 2008) to Revision E

•

Page

Changed the data sheet title From: 50 MHz to 400 MHz CASCADEABLE AMPLIFIER To: 50 MHz to 750 MHz

CASCADEABLE AMPLIFIER ............................................................................................................................................... 1

Changes from Revision C (February 2007) to Revision D

Page

•

Removed the DRD ordering options from the Available Options table ................................................................................ 2

•

Formatted the Absolute Maximum Ratings table to current standards ................................................................................ 2

•

Deleted DRD row from the Dissipation Rating table ............................................................................................................. 2

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

Product Folder Links: THS9000

15

�PACKAGE OPTION ADDENDUM

www.ti.com

10-Dec-2020

PACKAGING INFORMATION

Orderable Device

Status

(1)

Package Type Package Pins Package

Drawing

Qty

Eco Plan

(2)

Lead finish/

Ball material

MSL Peak Temp

Op Temp (°C)

Device Marking

(3)

(4/5)

(6)

THS9000DRWR

ACTIVE

VSON

DRW

6

3000

RoHS & Green

NIPDAUAG

Level-2-260C-1 YEAR

-40 to 85

BQX

THS9000DRWT

ACTIVE

VSON

DRW

6

250

RoHS & Green

NIPDAUAG

Level-2-260C-1 YEAR

-40 to 85

BQX

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance

do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may

reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of