Order

Now

Product

Folder

Support &

Community

Tools &

Software

Technical

Documents

TLV62085

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

TLV62085 High Efficiency 3-A Step-Down Converter in 2-mm × 2-mm VSON Package

1 Features

3 Description

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

The TLV62085 device is a high-frequency

synchronous step-down converter optimized for small

solution size and high efficiency. With an input

voltage range of 2.5 V to 6.0 V, common battery

technologies are supported. The devices focus on

high-efficiency step-down conversion over a wide

output current range. At medium to heavy loads, the

converter operates in PWM mode and automatically

enters Power Save Mode operation at light load to

maintain high efficiency over the entire load current

range.

1

DCS-Control™ Topology

Up to 95% Efficiency

17-μA Operating Quiescent Current

31mΩ and 23mΩ Power MOSFET Switch

2.5-V to 6.0-V Input Voltage Range

0.8-V to VIN Adjustable Output Voltage

Power Save Mode for Light Load Efficiency

100% Duty Cycle for Lowest Dropout

Hiccup Short-Circuit Protection

Output Discharge

Power Good Output

Thermal Shutdown Protection

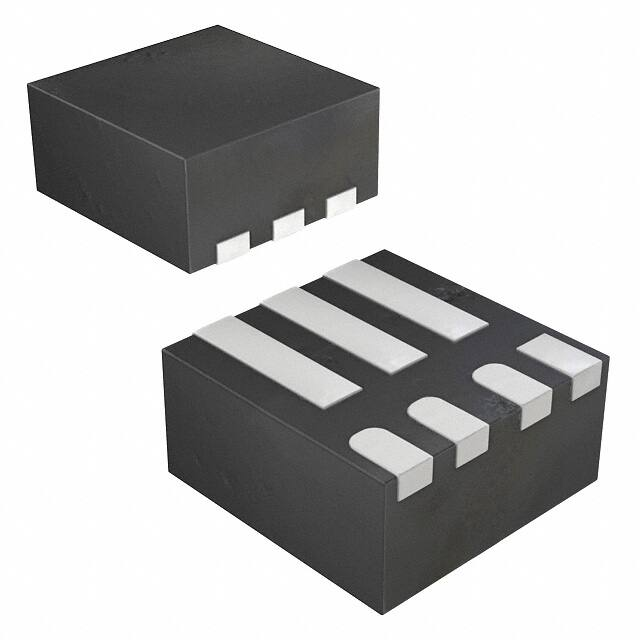

Available in 2-mm × 2-mm VSON Package

For Improved Feature Set, See TPS62085

Create a Custom Design using the TLV62085 with

the WEBENCH® Power Designer

To address the requirements of system power rails,

the internal compensation circuit allows a large

selection of external output capacitor values ranging

from 10 µF to 150 µF and above. Together with its

DCS-Control™ architecture, excellent load transient

performance and output voltage regulation accuracy

are achieved. The device is available in a 2-mm × 2mm VSON package.

Device Information(1)

2 Applications

•

•

•

•

PART NUMBER

TLV62085

Battery-Powered Applications

Point-of-Load

Processor Supplies

Hard Disk Drives (HDD) / Solid State Drives

(SSD)

PACKAGE

VSON (7)

BODY SIZE (NOM)

2.00 mm × 2.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

spacer

spacer

spacer

Typical Application Schematic

TLV62085

VIN

2.5V to 6V C1

10µF

VIN

SW

EN

VOS

Efficiency at VIN = 5 V

L1

0.47µH

R1

138k

R3

1M

C2

22µF

100

VOUT

1.8V

FB

PG

90

R2

110k

POWER GOOD

Efficiency (%)

GND

80

70

VOUT = 1.2 V

VOUT = 1.8 V

VOUT = 3.3 V

60

1m

10m

100m

Load (A)

1

5

D008

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TLV62085

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

www.ti.com

Table of Contents

1

2

3

4

5

6

7

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

1

1

1

2

3

4

6.1

6.2

6.3

6.4

6.5

6.6

4

4

4

4

5

5

Absolute Maximum Ratings ......................................

ESD Ratings..............................................................

Recommended Operating Conditions.......................

Thermal Information ..................................................

Electrical Characteristics..........................................

Typical Characteristics ..............................................

Detailed Description .............................................. 6

7.1

7.2

7.3

7.4

Overview ...................................................................

Functional Block Diagram .........................................

Feature Description...................................................

Device Functional Modes..........................................

6

6

7

8

8

Application and Implementation .......................... 9

8.1 Application Information.............................................. 9

8.2 Typical Application ................................................... 9

9 Power Supply Recommendations...................... 15

10 Layout................................................................... 15

10.1 Layout Guidelines ................................................. 15

10.2 Layout Example .................................................... 15

10.3 Thermal Considerations ........................................ 15

11 Device and Documentation Support ................. 16

11.1

11.2

11.3

11.4

11.5

11.6

11.7

Development Support ...........................................

Documentation Support ........................................

Receiving Notification of Documentation Updates

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

16

16

16

16

16

17

17

12 Mechanical, Packaging, and Orderable

Information ........................................................... 17

4 Revision History

Changes from Revision A (January 2017) to Revision B

•

Page

Added Figure 3 to power save mode section......................................................................................................................... 7

Changes from Original (October 2015) to Revision A

Page

•

Added WEBENCH™ information and hyperlinks to Features, Detailed Design Procedure, and Device Support sections .. 1

•

Added SW (AC) to the Absolute Maximum Rating table ....................................................................................................... 4

•

Added Table 1, PG Pin Logic ................................................................................................................................................. 8

2

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Product Folder Links: TLV62085

�TLV62085

www.ti.com

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

5 Pin Configuration and Functions

RLT Package

7-Pin VSON

Top View

EN

1

PG

2

FB

3

VOS

4

7

VIN

6

SW

5

GND

Pin Functions

PIN

NAME

NO.

I/O

DESCRIPTION

EN

1

IN

Device enable pin. To enable the device, this pin needs to be pulled high. Pulling this pin low disables the

device. This pin has a pulldown resistor of typically 400 kΩ when the device is disabled.

FB

3

IN

Feedback pin. Connect a resistor divider to set the output voltage.

GND

5

PG

2

OUT

Power good open drain output pin. The pullup resistor can not be connected to any voltage higher than 6 V. If

unused, leave it floating.

SW

6

PWR

Switch pin of the power stage.

VIN

7

PWR

Input voltage pin.

VOS

4

IN

Ground pin.

Output voltage sense pin. This pin must be directly connected to the output capacitor.

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Product Folder Links: TLV62085

3

�TLV62085

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

www.ti.com

6 Specifications

6.1 Absolute Maximum Ratings (1)

Voltage at Pins (2)

Temperature

(1)

(2)

(3)

MIN

MAX

VIN, FB, VOS, EN, PG

– 0.3

7

SW (DC)

UNIT

– 0.3

VIN + 0.3

SW (AC, less than 100ns) (3)

–3

11

V

Operating Junction, TJ

– 40

150

°C

Storage, Tstg

– 65

150

°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating

Conditions is not implied. Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.

All voltage values are with respect to network ground terminal.

While switching.

6.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

UNIT

±2000

Charged device model (CDM), per JEDEC specification JESD22-C101 (2)

V

±500

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions (1)

MIN

NOM

MAX

VIN

Input voltage range

2.5

6

VOUT

Output voltage range

0.8

VIN

UNIT

V

V

ISINK_PG Sink current at PG pin

1

mA

VPG

Pullup resistor voltage

6

V

TJ

Operating junction temperature

125

°C

(1)

–40

Refer to Application and Implementation for further information.

6.4 Thermal Information

TLV62085

THERMAL METRIC (1)

RLT [VSON]

UNIT

7 PINS

RθJA

Junction-to-ambient thermal resistance

107.8

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

66.2

°C/W

RθJB

Junction-to-board thermal resistance

17.1

°C/W

ψJT

Junction-to-top characterization parameter

2.1

°C/W

ψJB

Junction-to-board characterization parameter

17.1

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

N/A

°C/W

(1)

4

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Product Folder Links: TLV62085

�TLV62085

www.ti.com

6.5

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

Electrical Characteristics

TJ = 25 °C, and VIN = 3.6 V, unless otherwise noted.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

SUPPLY

IQ

Quiescent current into VIN

No load, device not switching

17

ISD

Shutdown current into VIN

EN = Low

0.7

Under voltage lock out threshold

VIN falling

Under voltage lock out hysteresis

VIN rising

200

mV

Thermal shutdown threshold

TJ rising

150

°C

Thermal shutdown hysteresis

TJ falling

20

°C

VUVLO

TJSD

2.1

2.2

µA

µA

2.3

V

LOGIC INTERFACE EN

VIH

High-level input voltage

VIN = 2.5 V to 6.0 V

VIL

Low-level input voltage

VIN = 2.5 V to 6.0 V

1.0

V

IEN,LKG

Input leakage current into EN pin

EN = High

0.01

µA

RPD

Pull-down resistance at EN pin

EN = Low

400

kΩ

Time from EN high to 95% of VOUT nominal

0.8

ms

0.4

V

SOFT START, POWER GOOD

tSS

Soft start time

VPG

Power good threshold

VPG,OL

Low-level output voltage

Isink = 1 mA

IPG,LKG

Input leakage current into PG pin

VPG = 5.0 V

VFB

Feedback regulation voltage

PWM mode, 2.5 V ≤ VIN ≤ 6 V

TJ = 0°C to 85 °C

IFB,LKG

Feedback input leakage current

VFB = 1 V

0.01

µA

RDIS

Output discharge resistor

EN = LOW, VOUT = 1.8 V

260

Ω

mΩ

VOUT rising, referenced to VOUT nominal

95%

VOUT falling, referenced to VOUT nominal

90%

0.4

0.01

V

µA

OUTPUT

792

800

808

mV

POWER SWITCH

RDS(on)

High-side FET on-resistance

ISW = 500 mA

31

Low-side FET on-resistance

ISW = 500 mA

23

ILIM

High-side FET switch current limit

fSW

PWM switching frequency

3.7

IOUT = 1 A

4.6

mΩ

5.5

2.4

A

MHz

6.6 Typical Characteristics

Switching Frequency (Hz)

5x106

106

105

104

103

1m

VIN = 2.5 V

VIN = 3.6 V

VIN = 6.0 V

10m

100m

Load (A)

1

5

D007

VOUT = 1.2 V

Figure 1. Switching Frequency

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Product Folder Links: TLV62085

5

�TLV62085

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

www.ti.com

7 Detailed Description

7.1 Overview

The TLV62085 synchronous step-down converter is based on the DCS-Control (Direct Control with Seamless

transition into Power Save Mode) topology. This is an advanced regulation topology that combines the

advantages of hysteretic, voltage, and current mode control schemes.

The DCS-Control topology operates in PWM (pulse width modulation) mode for medium to heavy load conditions

and in Power Save Mode at light load currents. In PWM mode, the converter operates with its nominal switching

frequency of 2.4 MHz, having a controlled frequency variation over the input voltage range. As the load current

decreases, the converter enters Power Save Mode, reducing the switching frequency and minimizing the IC's

current consumption to achieve high efficiency over the entire load current range. Because DCS-Control supports

both operation modes (PWM and PFM) within a single building block, the transition from PWM mode to Power

Save Mode is seamless and without effects on the output voltage. The device offers both excellent DC voltage

and superior load transient regulation, combined with very low output voltage ripple, minimizing interference with

RF circuits.

7.2 Functional Block Diagram

PG

Hiccup

Counter

VFB

VREF

EN

400kΩ

(1)

VIN

High Side

Current Sense

Bandgap

Undervoltage Lockout

Thermal Shutdown

SW

MOSFET Driver

Control Logic

GND

Ramp

Direct Control

and

Compensation

Comparator

Timer

ton

VOS

FB

VREF

Error Amplifier

DCS - Control

TM

EN

260Ω

Output Discharge

Logic

Note:

(1) When the device is enabled, the 400 kΩ resistor is disconnected.

Figure 2. Functional Block Diagram

6

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Product Folder Links: TLV62085

�TLV62085

www.ti.com

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

7.3 Feature Description

7.3.1 Power Save Mode

As the load current decreases, the TLV62085 enters Power Save Mode (PSM) operation. During Power Save

Mode, the converter operates with reduced switching frequency and with a minimum quiescent current

maintaining high efficiency. Power Save Mode occurs when the inductor current becomes discontinuous. Power

Save Mode is based on a fixed on-time architecture, as related in Equation 1. The switching frequency over the

whole load current range is also shown in Figure 1 for a shown typical application.

V

t ON = 420 ns ´ OUT

VIN

fPFM =

t ON2

2 ´ IOUT

V - VOUT

VIN

´

´ IN

VOUT

L

(1)

In PSM, the output voltage rises slightly above the nominal output voltage, as shown in Figure 10. This effect is

minimized by increasing the output capacitor or inductor value.

During PAUSE period in PSM (shown in Figure 3), the device does not change the PG pin state nor does it

detect an UVLO event, in order to achieve a minimum quiescent current and maintain high efficiency at light

loads.

VOUT

tPAUSE

IINDUCTOR

tON

Figure 3. Power Save Mode Waveform Diagram

7.3.2 100% Duty Cycle Low Dropout Operation

The device offers low input-to-output voltage difference by entering 100% duty cycle mode. In this mode, the

high-side MOSFET switch is constantly turned on and the low-side MOSFET is switched off. This is particularly

useful in battery powered applications to achieve the longest operation time by taking full advantage of the whole

battery voltage range. The minimum input voltage to maintain output regulation, depending on the load current

and output voltage can be calculated as:

VIN,MIN = VOUT + IOUT,MAX ´ (RDS(on) + RL )

with

•

•

•

•

VIN,MIN = Minimum input voltage to maintain an output voltage

IOUT,MAX = Maximum output current

RDS(on) = High-side FET ON-resistance

RL = Inductor ohmic resistance (DCR)

(2)

7.3.3 Soft Start

The TLV62085 has an internal soft-start circuitry which monotonically ramps up the output voltage and reaches

the nominal output voltage during a soft-start time of typically 0.8 ms. This avoids excessive inrush current and

creates a smooth output voltage slope. It also prevents excessive voltage drops of primary cells and

rechargeable batteries with high internal impedance. The device is able to start into a prebiased output capacitor.

The device starts with the applied bias voltage and ramps the output voltage to its nominal value.

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Product Folder Links: TLV62085

7

�TLV62085

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

www.ti.com

Feature Description (continued)

7.3.4 Switch Current Limit and Hiccup Short-Circuit Protection

The switch current limit prevents the device from high inductor current and from drawing excessive current from

the battery or input voltage rail. Excessive current might occur with a shorted or saturated inductor or a heavy

load or shorted output circuit condition. If the inductor current reaches the threshold ILIM, the high-side MOSFET

is turned off and the low-side MOSFET is turned on to ramp down the inductor current. When this switch current

limits is triggered 32 times, the device stops switching and enables the output discharge. The device then

automatically starts a new start-up after a typical delay time of 66 µs has passed. This is named HICCUP shortcircuit protection. The device repeats this mode until the high load condition disappears.

7.3.5 Undervoltage Lockout

To avoid misoperation of the device at low input voltages, an undervoltage lockout (UVLO) is implemented,

which shuts down the device at voltages lower than VUVLO with a hysteresis of 200 mV.

7.3.6 Thermal Shutdown

The device goes into thermal shutdown and stops switching when the junction temperature exceeds TJSD. When

the device temperature falls below the threshold by 20°C, the device returns to normal operation automatically.

7.4 Device Functional Modes

7.4.1 Enable and Disable

The device is enabled by setting the EN pin to a logic HIGH. Accordingly, shutdown mode is forced if the EN pin

is pulled LOW with a shutdown current of typically 0.7 μA.

In shutdown mode, the internal power switches as well as the entire control circuitry are turned off. An internal

resistor of 260 Ω discharges the output through the VOS pin smoothly. The output discharge function also works

when thermal shutdown, UVLO, or short-circuit protection are triggered.

An internal pulldown resistor of 400 kΩ is connected to the EN pin when the EN pin is LOW. The pulldown

resistor is disconnected when the EN pin is HIGH.

7.4.2 Power Good

The TLV62085 has a power good output. The power good goes high impedance once the output is above 95%

of the nominal voltage, and is driven low once the output voltage falls below typically 90% of the nominal voltage.

The PG pin is an open-drain output and is specified to sink up to 1 mA. The power good output requires a pull-up

resistor connecting to any voltage rail less than 6 V. The PG signal can be used for sequencing of multiple rails

by connecting it to the EN pin of other converters. Leave the PG pin unconnected when not used. Table 1 shows

the PG pin logic.

Table 1. PG Pin Logic

DEVICE CONDITIONS

EN = High, VFB ≥ VPG

Enable

LOGIC STATUS

HIGH Z

LOW

√

EN = High, VFB ≤ VPG

√

Shutdown

EN = Low

√

Thermal Shutdown

TJ > TJSD

√

UVLO

0.5 V < VIN < VUVLO

Power Supply Removal

VIN ≤ 0.5 V

8

√

√

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Product Folder Links: TLV62085

�TLV62085

www.ti.com

SLVSD63B – OCTOBER 2015 – REVISED JULY 2018

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component

specification, and TI does not warrant its accuracy or completeness. TI’s customers are

responsible for determining suitability of components for their purposes. Customers should

validate and test their design implementation to confirm system functionality.

8.1 Application Information

The TLV62085 is a synchronous step-down converter in which output voltage is adjusted by component

selection. The following section discusses the design of the external components to complete the power supply

design for several input and output voltage options by using the typical applications as a reference.

8.2 Typical Application

TLV62085

VIN

2.5V to 6V C1

10µF

L1

0.47µH

SW

VIN

VOS

EN

R1

138k

R3

1M

C2

22µF

VOUT

1.8V

FB

GND

PG

R2

110k

POWER GOOD

Figure 4. 1.8-V Output Voltage Application

8.2.1 Design Requirements

For this design example, use the parameters listed in Table 2 as the input parameters.

Table 2. Design Parameters

DESIGN PARAMETER

EXAMPLE VALUE

Input voltage

2.5 V to 6 V

Output voltage

1.8 V

Output current

≤3A

Output ripple voltage