Order

Now

Product

Folder

Support &

Community

Tools &

Software

Technical

Documents

TMDS171, TMDS171I

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

TMDS171/I 3.4 Gbps TMDS RETIMER

1 Features

3 Description

•

The TMDS171 is a digital video interface (DVI) or

high-definition multimedia interface (HDMI) retimer.

The TMDS171 supports four TMDS channels, Audio

Return Channel (SPDIF_IN/ARC_OUT), Hot Plug

Detect (HPD) and Digital Display Control (DDC)

interfaces. The TMDS171 supports signaling rates up

to 3.4 Gbps to allow for the highest resolutions of

4k2k30p 24 bits per pixel and up to WUXGA 12-bit

color depth or 1080p with higher refresh rates. The

TMDS171 automatically configures itself as a redriver at low data rate (< 1 Gbps) or as a re-timer

above this data rate.

1

•

•

•

•

•

•

•

•

•

•

•

HDMI Input Port to Output Port with CDR

Supporting up to 3.4 Gbps Data Rates

Compatible with HDMI1.4b Electrical Parameters.

Support for 4k2k30p and up to WUXGA 12-bit

Color Depth or 1080p with Higher Refresh

Rates™

Retimes Input Stream to Compensate for Random

Jitter

Adaptive Receiver Equalizer or Programmable

Fixed Equalizer

I2C and Pin Strap Programmable

Inter-Pair Skew Compensation of 5+ Bits

Link Debug Tools Including Eye Diagram After RX

Equalizer

Single Ended Mode ARC Support

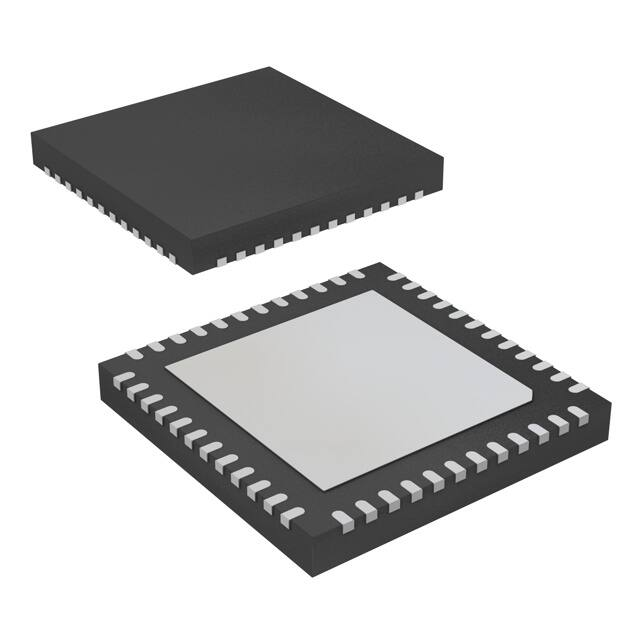

48-pin 7mm x 7mm 0.5 mm Pitch VQFN Package

Extended Commercial Temperature Support

0°C – 85°C (TMDS171)

Industrial Temperature Support -40°C – 85°C

(TMDS171I)

The TMDS171 supports dual power supply rails of

1.2 V on VDD and 3.3 V on VCC for active power

reduction. Several methods of power management

are implemented to reduce overall power

consumption. TMDS171 supports fixed EQ gain or

adaptive EQ control by I2C or pin strap to

compensate for different lengths input cable or board

traces.

Device Information(1)

PART NUMBER

TMDS171

PACKAGE

BODY SIZE (NOM)

(VQFN) 48 Pins

7.00 mm x 7.00 mm

2 Applications

TMDS171I

•

•

•

•

•

•

•

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Digital TV

Digital Projector

Audio/Video Equipment

Blu-Ray DVD

Monitors

Desktops/ All-in-Ones

Active Cables

Simplified Schematic

HDMI/DVI

Connector

IN_D2p/n

3.3 V t 5 V

HDMI

Receiver

TMDS171

Digital TV

OUT_D2p/n

IN_D1p/n

OUT_D1p/n

IN_D0p/n

OUT_D0p/n

IN_CLKp/n

OUT_CLKp/n

TMDS RX

3.3 V t 5 V

Interface

Unit

SCL_SRC

SDA_SRC

SCL_SNK

SDA_SNK

DDC

HPD_SRC

HPD_SNK

HPD

ARC_OUT

SPDIF_IN

SPDIF

3.3 V

OE

VSADJ

I2C

Audiovisual

Processing

Unit

HDMI

SW/HD

TMDS

171

SCL_CTL

SDA_CTL

Copyright © 2016, Texas Instruments Incorporated

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TMDS171, TMDS171I

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

www.ti.com

Table of Contents

1

2

3

4

5

6

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

6.1

6.2

6.3

6.4

6.5

6.6

6.7

7

8

1

1

1

2

4

6

Absolute Maximum Ratings ...................................... 6

ESD Ratings.............................................................. 6

Recommended Operating Conditions....................... 7

Thermal Information .................................................. 7

Electrical Characteristics........................................... 8

Switching Characteristics ........................................ 10

Typical Characteristics ............................................ 12

Parameter Measurement Information ................ 12

Detailed Description ............................................ 20

8.1 Overview ................................................................. 20

8.2 Functional Block Diagram ....................................... 21

8.3 Feature Description................................................. 21

8.4 Device Functional Modes........................................ 28

8.5 Register Maps ........................................................ 30

9

Application and Implementation ........................ 43

9.1 Application Information............................................ 43

9.2 Source Side Application.......................................... 45

9.3 System Examples ................................................... 49

10 Power Supply Recommendations ..................... 50

11 Layout................................................................... 52

11.1 Layout Guidelines ................................................. 52

11.2 Layout Example .................................................... 53

12 Device and Documentation Support ................. 54

12.1

12.2

12.3

12.4

12.5

12.6

Related Documentation .......................................

Receiving Notification of Documentation Updates

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

54

54

54

54

54

54

13 Mechanical, Packaging, and Orderable

Information ........................................................... 54

4 Revision History

Changes from Revision D (August 2016) to Revision E

Page

•

Added Note 3 to the Electrical Characteristics table .............................................................................................................. 8

•

Deleted text "which is needed for certain HDMI CTS test." from the second paragraph in the Overview section .............. 20

•

Changed section: Input Signal Detect Block ........................................................................................................................ 25

•

Changed H to X in the first row of the HPD_SNK column in Table 36 ................................................................................ 51

•

Changed the IN_Dx column in Table 36 .............................................................................................................................. 51

Changes from Revision C (April 2016) to Revision D

Page

•

Recommended Operating Conditions, Changed the CONTROL PINS section ..................................................................... 7

•

Electrical Characteristics Changed the DDC and I2C section................................................................................................ 9

Changes from Revision B (February 2016) to Revision C

Page

•

Changed pin 36 Description From: TX_TERM_CTL = L: 150 - 300 Ω To: TX_TERM_CTL = L: Reserved in the Pin

Functions table ...................................................................................................................................................................... 6

•

Added OE to VIL "Low-level input voltage" in the Recommended Operating Conditions table ............................................. 7

•

Added OE to VIH "High-level input voltage" in the Recommended Operating Conditions table ............................................ 7

•

Changed Figure 23 .............................................................................................................................................................. 22

•

Deleted the VDD_ramp and VCC_ramp MIN values in Table 1 ......................................................................................... 23

•

Changed TX_TERM_CTL = L to Reserved in Table 3 ........................................................................................................ 25

•

Changed text "address 22h through the I2C interface" To: "address 0Bh through the I2C interface" DDC Functional

Description............................................................................................................................................................................ 29

•

Added Note to 11–400-kbps in Table 8................................................................................................................................ 32

•

Added Note to 11–400-kbps in Table 10.............................................................................................................................. 34

2

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

�TMDS171, TMDS171I

www.ti.com

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

Changes from Revision A (December 2015) to Revision B

•

Page

Changed Pin 44 From: AUX_SRCn To: ARC_OUT Pin 45 From: AUX_SRCn To: SPDIF_IN in the Pin Configuration

and Functions image ............................................................................................................................................................. 4

Changes from Original (October 2015) to Revision A

•

Page

Changed the device status From: Product Preview To: Production ...................................................................................... 1

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

3

�TMDS171, TMDS171I

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

www.ti.com

5 Pin Configuration and Functions

VDD

SDA_SRC

SCL_SRC

SPDIF_IN

ARC_OUT

VCC

OE

GND

NC

SDA_SNK

SCL_SNK

VDD

RGZ (QFN) Package

48 Pins

Top View

48

47

46

45

44

43

42

41

40

39

38

37

SWAP/POL

1

36

TX_TERM_CTL

IN_D2p

2

35

OUT_D2p

IN_D2n

3

34

OUT_D2n

HPD_SRC

4

33

HPD_SNK

IN_D1p

5

32

OUT_D1p

IN_D1n

6

31

OUT_D1n

GND

7

30

GND

IN_D0p

8

29

OUT_D0p

IN_D0n

9

28

OUT_D0n

I2C_EN/PIN

10

27

A1

IN_CLKp

11

26

OUT_CLKp

IN_CLKn

12

25

OUT_CLKn

4

16

17

18

19

20

21

VDD

SCL_CTL

SDA_CTL

SIG_EN

NC

GND

PRE_SEL

EQ_SEL/A0

Submit Documentation Feedback

22

23

24

VDD

15

VDD

14

VSADJ

13

VCC

GND

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

�TMDS171, TMDS171I

www.ti.com

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

Pin Functions

PIN

NAME

NO.

I/O (1)

DESCRIPTION

VCC

13, 43

P

3.3 V Power Supply

VDD

14, 23, 24, 37, 48

P

1.2 V Power Supply

GND

7, 19, 41, 30

G

Ground

G

Ground

Thermal Pad

MAIN LINK INPUT PINS (FAIL SAFE)

IN_D2p/n

2, 3

I

Channel 2 Differential Input

IN_D1p/n

5, 6

I

Channel 1 Differential Input

8, 9

I

Channel 0 Differential Input

11, 12

I

Clock Differential Input

IN_D0p/n

IN_CLKp/n

MAIN LINK OUTPUT PINS (FAIL SAFE)

OUT_D2n/p

34, 35

O

TMDS Data 2 Differential Output

OUT_D1n/p

31, 32

O

TMDS Data 1 Differential Output

OUT_D0n/p

28, 29

O

TMDS Data 0 Differential Output

OUT_CLKn/p

25, 26

O

TMDS Clock Differential Output

HPD_SRC

4

O

Hot Plug Detect Output to source side

HPD_SNK

33

I

Hot Plug Detect Input from sink side

HOT PLUG DETECT PINS

AUDIO RETURN CHANNEL and DDC PINS

SPDIF_IN

45

I

SPDIF signal input

ARC_OUT

44

O

Audio return channel output

SDA_SRC

47

I/O

Source Side TMDS Port Bidirectional DDC Data line

SCL_SRC

46

I/O

Source Side TMDS Port Bidirectional DDC Clock line

SDA_SNK,

39

I/O

Sink Side TMDS Port Bidirectional DDC Data Line

SCL_SNK

38

I/O

Sink Side TMDS Port Bidirectional DDC Clock Line

42

I

Operation Enable/Reset Pin

OE = L: Power Down Mode

OE = H: Normal Operation

Internal weak pull up: Resets device when transitions from H to L

17

I

Signal detector circuit enable

SIG_EN = L: Signal Detect Circuit Disabled: Term resistors always connected (Default)

SIG_EN = H: Signal Detect Circuit Enabled: When no valid clock device enters Standby

Mode.

Internal weak pull down

20

I

3-Level

CONTROL PINS (2)

OE

SIG_EN

PRE_SEL

De-emphasis Control when I2C_EN/PIN = Low.

PRE_SEL = L: -2 dB

PRE_SEL = No Connect: 0 dB

PRE_SEL = H: Reserved

When I2C_EN/PIN = High; De-emphasis is controlled through I2C

EQ_SEL/A0

21

I

Input Receive Equalization pin strap when I2C_EN/PIN = Low

EQ_SEL = L: Fixed EQ at 7.5 dB

EQ_SEL = No Connect: Adaptive EQ

EQ_SEL = H: Fixed at 14 dB

When I2C_EN/PIN = High Address Bit 1

Note: 3 level for pin strap programming but 2 level when I2C address

I2C_EN/PIN

10

I

I2C_EN/PIN = High; Puts Device into I2C Control Mode

I2C_EN/PIN = Low; Puts Device into Pin Strap Mode

SCL_CTL

15

I/O

I2C Clock Signal when I2C_EN/PIN = High.

Note: When I2C_EN = Low; Pin strapping takes priority and those functions cannot be

changed by I2C

SDA_CTL

16

I/O

I2C Data Signal when I2C_EN/PIN = High

Note: When I2C_EN = Low; Pin strapping takes priority and those functions cannot be

changed by I2C

VSadj

22

I

(1)

(2)

TMDS Output Voltage Swing Control; Nominal 7.06 kΩ Resistor to GND

(1) G = Ground, I = Input, O = Output, P = Power

(H) Logic High (Pin strapped to VCC through 65 kΩ resistor); (L) Logic Low (Pin strapped to GND through 65 kΩ resistor); (Mid-Level =

No connect)

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

5

�TMDS171, TMDS171I

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

www.ti.com

Pin Functions (continued)

PIN

NAME

I/O (1)

NO.

A1

27

I

DESCRIPTION

High address bit 2 for I2C programming

Weak internal pull down.

Note: When I2C_EN/PIN = Low for Pin Strapping Mode leave this pin as No connect

TX_TERM_CTL

36

I

3-Level

Transmit Termination Control

TX_TERM_CTL = H: No transmit Termination

TX_TERM_CTL = L: Reserved

TX_TERM_CTL = No Connect: Automatically selects the termination impedance

2 Gbps > DR ≤ 3.4 Gbps – 150 - 300 Ω differential near end termination

DR < 2 Gbps – no termination

Note: If left floating; the device will be in Automatic Select Mode. DR stands for Data Rate

SWAP/POL

1

I

3-Level

Receive Polarity Swap and Receive Lane Swap control pin

SWAP/POL = H: Receive Lanes Polarity Swap (Retimer Mode Only)

SWAP/POL = L: Receive Lanes (Retimer and Redriver Mode)

Swap SWAP/POL = No Connect, Normal Operation

18, 40

–

NC

No connect

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

Supply Voltage Range

(1) (2) (3)

MIN

MAX

VCC

–0.3

4

VDD

–0.3

1.4

VCC - 0.75 V

VCC + 0.3 V

TMDS Outpus ( OUT_Dx)

–0.3

4

HPD_SRC, Vsadj, SDA_CTL, SCL_CTL, OE, A1,

PRE_SEL, EQ_SEL/A0, I2C_EN/PIN, SIG_EN,

TX_TERM_CTL,

–0.3

4

HDP_SNK, SDA_SNK, SCL_SNK, SDA_SRC,

SCL_SRC

–0.3

6

Main Link Input Differential Voltage (IN_Dx,

IN_CLKx); IIN = 15mA

Voltage Range

Input Current IIN

Main Link Input Differential Voltage (IN_Dx,

IN_CLKx);

Continuous power dissipation

(2)

(3)

V

15

mA

See Thermal Information

Storage temperature, Tstg

(1)

UNIT

–65

150

°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values, except differential voltages, are with respect to network ground terminal.

Tested in accordance with JEDEC Standard 22, Test Method A114-B

6.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

6

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)

±2000

Charged-device model (CDM), per JEDEC specification JESD22C101 (2)

±500

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

�TMDS171, TMDS171I

www.ti.com

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

VCC

Supply Voltage Nominal Value 3.3 V

3.135

3.3

3.465

V

VDD

Supply Voltage Nominial Value 1.2 V

1.1

1.2

1.27

V

TSTG

Storage temperature

–65

150

°C

TCASE

Case temperature

TA

92.7

°C

Operating free-air temperature (TMDS171)

0

85

°C

Operating free-air temperature (TMDS171I)

–40

85

°C

MAIN LINK DIFFERENTIAL PINS

VID(PP)

Peak-to-peak input differential voltage

VIC

Input Common Mode Voltage

dR

Data rate

R(VSADJ)

TMDS compliant swing voltage bias resistor 1%

75

1560

VCC – 0.4

VCC + 0.1

0.25

3.4

7.06

mVpp

V

Gbps

KΩ

CONTROL PINS

VI(DC)

3.6

V

Low-level input voltage OE

0.8

V

VIL (1)

Low-level input voltage at PRE_SEL, EQ_SEL/A0, TX_TERM_CTL,

SWAP/POL pins only (1)

0.3

V

VIM (1)

Mid-Level input voltage at PRE_SEL, EQ_SEL/A0, TX_TERM_CTL,

SWAP/POL pins only (1)

1

1.4

V

VIH (1)

High-level input voltage at PRE_SEL, EQ_SEL/A0, TX_TERM_CTL,

SWAP/POL, OE (2) pins only (1)

2.6

VOL

Low-level output voltage

VOH

High-level output voltage

2.4

IIH

High level input current

IIL

IOS

IOZ

High impedance output current

R(OEPU)

Pull up resistance on OE pin

(1)

(2)

DC Input Voltage

–0.3

1.2

V

0.4

V

30

30

µA

Low level input current

–25

25

µA

Short circuit output current

–50

50

mA

10

µA

150

250

KΩ

V

These values are based upon a microcontroller driving the control pins. The pull up/down/floating resistor configuration will set control

pins properly which will have a different value than shown due to internal biasing.

This value is based upon a microcontroller driving the OE pin. A passive reset circuit using an external capacitor and the internal pullup

resistor will set OE pin properly, but may have a different value than shown due to internal biasing.

6.4 Thermal Information

THERMAL METRIC (1)

RGZ (QFN)

48 PINS

RθJA

Junction-to-ambient thermal resistance

31.1

RθJC(top)

Junction-to-case (top) thermal resistance

18.2

RθJB

Junction-to-board thermal resistance

8.1

ψJT

Junction-to-top characterization parameter

0.4

ψJB

Junction-to-board characterization parameter

8.1

RθJC(bot)

Junction-to-case (bottom) thermal resistance

3.2

(1)

UNIT

°C/W

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

7

�TMDS171, TMDS171I

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

www.ti.com

6.5 Electrical Characteristics

The Maximum rating is simulated at 3.465 V VCC and 1.27 V VDD and at 85°C temperature. The Typical rating is simulated at

3.3 VCC and 1.2 V VDD and at 27°C temperature (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

675

875

mW

400

600

mW

Power Supply

P(D1) (1) (2)

Device power Dissipation

(Retimer Operation)

P(D2) (1) (2)

Device power Dissipation

(Redriver Operation)

P(SD1) (1) (2) (3)

Device power in Standby

OE = H, VCC = 3.3 V / 3.465 V

VDD = 1.2 V / 1.27 V , HPD = H,

No Valid input Signal

50

100

mW

P(SD2) (1) (2) (3)

Device power in PowerDown

OE = L, VCC = 3.3 V / 3.465 V

VDD = 1.2 V / 1.27 V

10

30

mW

ICC1 (1) (2)

VCC Supply current (TMDS 3.4

Gpbs Retimer Mode)

80

140

mA

IDD1 (1) (2)

VDD Supply current (TMDS 3.4

Gpbs Retimer Mode)

286

325

mA

ICC2 (1) (2)

VCC Supply current (TMDS 3.4

Gpbs Redriver Mode)

IDD2 (1) (2)

VDD Supply current (TMDS 3.4

Gpbs Redriver Mode)

OE = H, VCC = 3.3 V / 3.465 V, VDD = 1.2 V / 1.27 V

IN_Dx: VID_PP = 1200 mV, I2C_EN/PIN = L, PRE_SEL= H,

EQ_CTL= H, SDA_CTL/CLK_CTL = 0 V

3.4 Gbps TMDS pattern, VI = 3.3 V; VSADJ = 7.06 kΩ

OE = H, VCC = 3.3 V / 3.465 V

VDD = 1.2 V / 1.27 V

IN_Dx: VID_PP = 1200 mV,

3.4 Gbps TMDS pattern I2C_EN/PIN = L, PRE_SEL = H,

EQ_CTL = H, SDA_CTL/CLK_CTL = 0 V, SLEW_CTL = H

OE = H, VCC = 3.3 V / 3.465 V

VDD = 1.2 V / 1.27 V

IN_Dx: VID_PP = 1200 mV,

3.4 Gbps TMDS pattern I2C_EN/PIN = L, PRE_SEL = H,

EQ_CTL = H, SDA_CTL/CLK_CTL = 0V, SLEW_CTL = H

(1)

Standby current

OE = H, VCC = 3.3 V / 3.465 V

VDD = 1.2 V / 1.27 V

HPD = H: No valid signal on

IN_CLK

3.3V Rail

I(SD1) (3)

I(SD2) (3)

PowerDown current

OE = L, VCC = 3.3 V / 3.465 V

VDD = 1.2 V / 1.27 V

3.3V Rail (1)

1.2V Rail

1.2V Rail

51

mA

188

mA

6

15

40

50

2

5

3.5

15

mA

mA

TMDS Differential Input

D(R_RX_DATA)

TMDS data lanes data rate

D(R_RX_CLK)

TMDS clock lanes clock rate

0.25

3.4

Gbps

25

340

tRX_DUTY

Input clock duty circle

MHz

tCLK_JIT

Input clock jitter tolerance

tDATA_JIT

Input data jitter tolerance

Test the TTP2 See Figure 11

tRX_INTRA

Input intra-pair skew tolerance

Test at TTP2 when DR = 1.6 Gbps See Figure 11

tRX_INTER

Input inter-pair skew tolerance

EQH(D)

Fixed EQ gain for data lane

IN_D(0,1,2)n/p

EQ_SEL/A0=H; Fixed EQ gain, test at 3.4 Gbps

14

EQL(D)

Fixed EQ gain for data lane

IN_D(0,1,2)n/p

EQ_SEL/A0=L; Fixed EQ gain, test at 3.4 Gbps

7.5

EQZ(D)

Adaptive EQ gain for data lane

EQ_SEL/A0=NC; adaptive EQ

IN_D(0,1,2)n/p

EQ(C)

EQ gain for clock lane

IN_CLKn/p

R(INT)

Input differential termination

impedance

40%

50%

60%

0.3

Tbit

150

ps

112

ps

1.8

ns

dB

2

EQ_SEL/A0=H,LNC

14

0

90

100

115

Ω

TMDS Differential Output

VOH

Single-ended high level output

voltage

VOL

Single-ended low level output

voltage No Pre-emphasis,

Load is 50 Ω pull ups to 3.135

V and 3.465 V

(1)

(2)

(3)

8

PRE_SEL = NC; TX_TERM_CTL = H; OE = H; DR = 750

Mbps; VSadj = 7.06 kΩ

VCC 10mV

VCC +

10mV

PRE_SEL = NC; TX_TERM_CTL = H; OE = NC; DR = 2.97

Gbps; VSadj = 7.06 kΩ

VCC 200mV

VCC +

10mV

PRE_SEL = NC; TX_TERM_CTL = H; OE = H; DR = 750

Mbps; VSadj = 7.06 kΩ

VCC 600mV

VCC 400mV

PRE_SEL = NC; TX_TERM_CTL = H; OE = NC; DR = 2.97

Gbps; VSadj = 7.06 kΩ

VCC 700mV

VCC 400mV

V

ICC is a direct result of the source design as the TMDS171 integrated receive termination resistor accounts for 85 mA to 100 mA.

IDD is impacted by ARC usage. Connecting a 500 KΩ resistor to GND at SPDIF reduces the value by more than 20 mA.

The measurements were made with no active source connected.

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

�TMDS171, TMDS171I

www.ti.com

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

Electrical Characteristics (continued)

The Maximum rating is simulated at 3.465 V VCC and 1.27 V VDD and at 85°C temperature. The Typical rating is simulated at

3.3 VCC and 1.2 V VDD and at 27°C temperature (unless otherwise noted)

PARAMETER

MIN

TYP

MAX

V(SWING_DA)

Single-ended output voltage

swing on data lane

PRE_SEL = NC; TX_TERM_CTL = H/NC; OE = NC;

DR = ≤ 3.4 Gbps; VSadj = 7.06 kΩ

TEST CONDITIONS

400

500

600

V(SWING_CLK)

Single-ended output voltage

swing on clock lane

PRE_SEL = NC; TX_TERM_CTL = H/NC; OE = NC;

DR = ≤ 3.4 Gbps; VSadj = 7.06 kΩ

400

500

600

ΔV(SWING)

Change in single-end output

voltage swing per 100Ω

ΔVSadj

ΔVOCM(SS)

Change in steady state output

common mode voltage

between logic levels

VOD(PP)

Initial output differential

voltage before steady state

when pre-emphasis or deemphasis is implemented

VOD(SS)

UNIT

20

mV

–5

5

VSadj = 7.06 kΩ; PRE_SEL = NC, See Figure 8

800

1200

Steady state output differential

voltage

VSadj = 7.06 kΩ; PRE_SEL = L, See Figure 9

600

1075

IOS

Short circuit current limit

Main link output shorted to GND

50

mA

ILEAK

Failsafe condition leakage

current

VCC = 0 V; VDD = 0 V; TMDS Outputs pulled to 3.3V through

50 Ω resistor

45

µA

R(TERM)

Source Termination resistance

150

300

Ω

SCL/SDA_SNK,

SCL/SDA_SRC DC input

voltage

–0.3

5.5

V

SCL/SDA_CTL, DC input

voltage

–0.3

3.6

V

SCL/SDA_SNK,

SCL/SDA_SRC Low level

input voltage

0.3 x VCC

V

SCL/SDA_CTL Low level input

voltage

0.3 x VCC

V

DDC and I2C

VI-DC

VIL

VIH

SCL/SDA_SNK,

SCL/SDA_SRC high level

input voltage

SCL/SDA_CTL high level input

voltage

3

V

0.7 x VCC

V

VOL

SCL/SDA_CTL,

SCL/SDA_SRC low level

output voltage

IO = 3 mA and VCC > 2 V

0.4

V

IO = 3 mA and VCC < 2 V

0.2 x VCC

V

fSCL

SCL clock frequency fast I2C

mode for local I2C control

400

kHz

Cbus

Total capacitive load for each

bus line (DDC and local I2C

pins)

400

pF

HPD

VIH

High-level input voltage

HPD_SNK

VIL

Low-level input voltage

HPD_SNK

VOH

High-level output voltage

IOH = -500 µA; HPD_SRC

2.4

3.6

VOL

Low-level output voltage

IOL = -500 µA; HPD_SRC

0

0.1

ILEAK

Failsafe condition leakage

current

VCC = 0 V; VDD = 0 V; HPD_SNK = 5 V

40

Device powered; VIH = 5 V; IH(HPD) includes Rpd(HPD) resistor

current

40

Device powered; VIL = 0.8 V; IH(HPD) includes Rpd(HPD)

resistor current

30

IH(HPD)

Rpd(HPD)

High level input current

HPD input termination to GND; VCC < 0 V

2.1

0.8

V

µA

150

190

220

kΩ

5

V

SPDIF and ARC

V(EL)

Operating DC voltage for

single mode ARC output

Test at ARC_OUT, see Figure 19

0

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

9

�TMDS171, TMDS171I

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

www.ti.com

Electrical Characteristics (continued)

The Maximum rating is simulated at 3.465 V VCC and 1.27 V VDD and at 85°C temperature. The Typical rating is simulated at

3.3 VCC and 1.2 V VDD and at 27°C temperature (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

VIN(DC)

Operating DC voltage for

SPDIF input

V(SP_SW)

Signal amplitude of SPDIF

input

V(ElSWING)

Signal amplitude on the ARC

output

Test at ARC_OUT, 75 Ω external termination resistor, see

Figure 19

CLK(ARC)

Signal frequency on ARC

Test at ARC_OUT, see Figure 19

Duty Cycle

Output Clock Duty cycle

Data Rate

SPDIF Input DR

tEDGE

The rise/fall time for ARC

output

R(IN_SPDIF)

The Input Termination

resistance for SPDIF

R(EST)

Single mode Output

Termination resistance

TYP

MAX

UNIT

0.05

V

0.2

0.5

0.6

V

0.4

0.5

0.6

V

3.687

5.645±0.

1%

13.517

45%

50%

55%

7.373

11.29

27.034

From 10% to 90% voltage level, see Figure 19

0.4

75

0.1 MHz to 128 times the maximum frame rate

36

MHz

Mbps

UI

Ω

55

75

Ω

6.6 Switching Characteristics

The Maximum rating is simulated at 3.465 V VCC and 1.27 V VDD and at 85°C temperature. The Typical rating is simulated at

3.3 V VCC and 1.2 V VDD and at 27°C temperature (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Mbps

TMDS Redriver Mode

DR

Data rate (Redriver mode)

250

3400

tPLH

Propagation delay time (low to high)

250

600

tPHL

Propagation delay time (high to low)

250

800

tT1

Transition time (rise and fall time);

measured at 20% and 80% levels

for Data Lanes.

TX_TERM_CTL=L; PRE_SEL=NC;

Data Rate 3.4 Gbps; Clock 340 MHz

tSK1(T)

Intra-pair output skew

TX_TERM_CTL=NC;

PRE_SEL=NC;

40

tSK2(T)

Inter-pair output skew

TX_TERM_CTL=NC;

PRE_SEL=NC;

100

tJITD1

Total output data jitter

tJITC1

Total output clock jitter

75

ps

DR = 750 Mbps, PRE_SEL = NC,

EQ_SEL/A0 = NC. See Figure 5 at

TTP3

0.2

0.25

Tbit

TMDS Retimer Mode

DR

Data rate (retimer mod )

d(XVR)

Automatic redriver to Retimer Cross- Measured with input signal applied

Over

from 0 to 200 mVPP

1.2

f(CROSSOVE

Crossover frequency hysteresis

0.75

1.00

3.4

Gbps

1.25

Gbps

250

MHz

R)

PLL(BW)

Data Retimer PLL bandwidth

tACQ

Input Clock Frequency Detection

and Retimer Acquisition Time

IJT1

Input Clock Jitter Tolerance

tT1

Transition time (rise and fall time);

measured at 20% and 80% levels

for Data Lanes. TMDS

tDCD

OUT_CLK ± duty cycle

tSK_INTER

Inter-pair output skew

10

Default loop bandwidth setting

0.4

1

180

Tested when data rate > 1.0 Gbps

µs

0.3

75

40%

Default setting for internal inter-pair

skew adjust, PRE_SEL = NC;

TX_TERM_CTL = NC, DR ≤ 3.4

Gbps; See Figure 6

Submit Documentation Feedback

MHz

Tbit

ps

50%

60%

0.2

Tch

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

�TMDS171, TMDS171I

www.ti.com

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

Switching Characteristics (continued)

The Maximum rating is simulated at 3.465 V VCC and 1.27 V VDD and at 85°C temperature. The Typical rating is simulated at

3.3 V VCC and 1.2 V VDD and at 27°C temperature (unless otherwise noted)

PARAMETER

TEST CONDITIONS

tSK_INTRA

Intra-pair output skew

Default setting for internal intra-pair

skew adjust, PRE_SEL = NC;

TX_TERM_CTL = NC, DR ≤ 3.4

Gbps; See Figure 6

tJITC2

Total output clock jitter

CLK Rate ≤ 340 MHz

tJITD2

Total output data jitter

DR ≤ 3.4 Gbps; See Figure 11

MIN

TYP

MAX

UNIT

0.15

Tbit

0.25

Tbit

0.2

Tbit

120

ns

HPD

tPD(HPD)

Propagation delay from HPD_SNK

see Figure 13; not valid during

to HPD_SRC; rising edge and falling

switching time

(1)

edge

tT(HPD)

HPD logical disconnected timeout

40

see Figure 14

2

ms

DDC and I2C

tr

Rise time of both SDA and SCL

signals

tf

Fall time of both SDA and SCL

signals

tHIGH

Pulse duration, SCL high

0.6

tLOW

Pulse duration, SCL low

1.3

tSU1

Setup time, SDA to SCL

100

tST,STA

Setup time, SCL to start condition

0.6

tHD,STA

Hold time, start condition to SCL

0.6

tST,STO

Setup time, SCL to stop condition

0.6

t(BUF)

Bus free time between stop and start

condition

1.3

tPLH1

Propagation delay time, low-to-highlevel output

tPHL1

Propagation delay time, high-to-lowlevel output

tPLH2

Propagation delay time, low-to-highlevel output

tPHL2

Propagation delay time, high-to-lowlevel output

(1)

(2)

VCC = 3.3 V

300

ns

300

Source to Sink:100 kbps pattern;

Cb(Sink) = 400 pF (2); see Figure 17

µs

ns

µs

360

230

ns

Sink to Source: 100 kbps pattern;

Cb(Source) = 100 pF (2); see Figure 18

250

200

The Maximum rating is simulated at 3.465 V VCC and 1.27 V VDD

Cb = total capacitance of one bus line in pF.

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

11

�TMDS171, TMDS171I

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

www.ti.com

200

300

180

270

160

240

Current (mA)

Current (mA)

6.7 Typical Characteristics

140

120

1.2V

3.3V

100

210

180

1.2V

3.3V

150

80

120

60

90

60

40

0

0.5

1

1.5

2

Data Rate (Gbps)

2.5

3

0

3.5

0.5

1

1.5

2

Data Rate (Gbps)

D001

Figure 1. Current vs Data Rate Redriver Mode

2.5

3

3.5

D002

Figure 2. Current vs Data Rate Retimer Mode

1600

VOD No Term

VOD 150 to 300 :

1400

VOD (mVpp)

1200

1000

800

600

400

200

0

4

4.5

5

5.5

6

6.5

Vsadj (k:)

7

7.5

8

D003

Figure 3. VOD vs VSadj

7 Parameter Measurement Information

VCC

3.3V

50Ÿ

50Ÿ

50Ÿ

50Ÿ

0.5 pF

D+

VD+

VID

Receiver

Driver

DVD-

Y

VY

Z

VID = VD+ - VD-

VOD = VY - VZ

VICM = (VD+ + VD-)

2

VOC = (VY + VZ)

2

VZ

Figure 4. TMDS Main Link Test Circuit

12

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

�TMDS171, TMDS171I

www.ti.com

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

Parameter Measurement Information (continued)

2.2V

VID

VTERM

1.8V

VID+

VID(pp)

0V

VIDtPLH

tPHL

80%

80%

VOD

VOD(pp)

0V

20%

tf

20%

tr

Figure 5. Input/Output Timing Measurements

tSK_INTRA

tSK_INTRA

TMDS_OUTxp

50%

TMDS_OUTxn

tSK_INTER

TMDS_OUTyp

TMDS_OUTyn

Figure 6. TMDS Output Skew Measurements

Figure 7. HDMI/DVI TMDS Output Common Mode Measurement

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Product Folder Links: TMDS171

13

�TMDS171, TMDS171I

SLLSEN7E – OCTOBER 2015 – REVISED SEPTEMBER 2017

www.ti.com

Parameter Measurement Information (continued)

VOD(PP)

PRE_SEL=Z

Rsadj = 7.06