Product

Folder

Sample &

Buy

Support &

Community

Tools &

Software

Technical

Documents

TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

TPS54061-Q1 Wide-Input, 60-V, 200-mA Synchronous Step-Down

DC–DC Converter With Low IQ

1 Features

3 Description

•

•

The TPS54061-Q1 device is a 60-V, 200-mA,

synchronous step-down DC-DC converter with

integrated high-side and low-side MOSFETs. Currentmode control provides simple external compensation

and flexible component selection. The non-switching

supply current is 90 µA. Using the enable pin reduces

the shutdown supply current to 1.4 µA.

1

•

•

•

•

•

•

•

•

•

•

•

•

Qualified for Automotive Applications

AEC-Q100 Qualified With the Following Results:

– Device Temperature Grade 1: –40°C to 125°C

Ambient Operating Temperature Range

– Device HBM ESD Classification Level H2

– Device CDM ESD Classification Level C3B

Integrated High-Side and Low-Side MOSFETs

Diode Emulation for Light-Load Efficiency

Peak-Current Mode Control

90-µA Operating Quiescent Current

1.4-µA Shutdown Supply Current

50-kHz to 1.1-MHz Adjustable Switching

Frequency

Synchronizes to External Clock

0.8 V ±1% Voltage Reference

Stable With Ceramic Output Capacitors or LowCost Aluminum Electrolytic

Cycle-by-Cycle Current Limit, Thermal, OVP, and

Frequency Foldback Protection

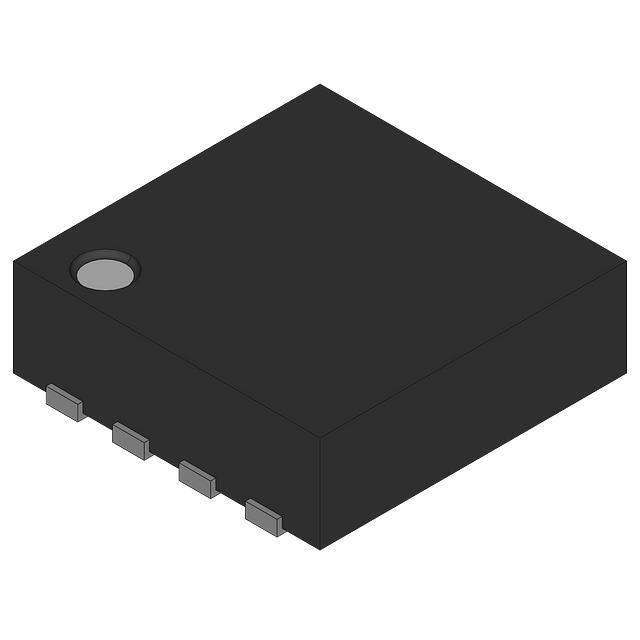

3-mm x 3-mm, 8-Pin SON Package With Thermal

Pad

–40°C to 150°C Operating Junction Temperature

The internal undervoltage lockout setting is 4.5 V, but

using two resistors on the enable pin can increase

the setting. The internal slow-start time controls the

output-voltage start-up ramp.

The adjustable switching-frequency range allows

optimization of efficiency and external component

size. Frequency foldback and thermal shutdown

protect the part during an overload condition.

The TPS54061-Q1 enables small designs by

integrating the MOSFETs and boot recharge diode,

and by minimizing the IC footprint with a small 3-mm

× 3-mm thermally-enhanced SON package.

The TPS54061-Q1 is supported in the WEBENCH™

Designer at www.ti.com.

Device Information(1)

2 Applications

•

•

To increase light-load efficiency, the low-side

MOSFET emulates a diode when the inductor current

reaches zero.

PART NUMBER

Low-Power Standby or Bias Voltage Supplies

High-Efficiency Replacement for High-Voltage

Linear Regulators

TPS54061-Q1

PACKAGE

BODY SIZE (NOM)

SON (8)

3.00 mm × 3.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Simplified Schematic

Efficiency

100

VIN

BOOT

VIN

90

TPS54061-Q1

80

RT /CLK

VSNS

VOUT

Efficiency (%)

PH

EN

70

60

50

40

COMP

30

PowerPAD

GND

VOUT = 5 V, fSW = 50 kHz

VOUT = 5 V, fSW = 400 kHz

VOUT = 3.3 V, fSW = 400 kHz

20

10

0

0.001

0.010

Load Current (A)

0.100

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

Table of Contents

1

2

3

4

5

6

7

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

1

1

1

2

3

4

6.1

6.2

6.3

6.4

6.5

6.6

4

4

4

5

5

7

Absolute Maximum Ratings ......................................

ESD Ratings..............................................................

Recommended Operating Conditions.......................

Thermal Information ..................................................

Electrical Characteristics...........................................

Typical Characteristics ..............................................

Detailed Description ............................................ 10

7.1 Overview ................................................................. 10

7.2 Functional Block Diagram ....................................... 11

7.3 Feature Description................................................. 11

7.4 Device Functional Modes........................................ 15

8

Applications and Implementation ...................... 16

8.1 Application Information............................................ 16

8.2 Typical Applications ................................................ 16

9 Power Supply Recommendations...................... 30

10 Layout................................................................... 30

10.1 Layout Guidelines ................................................. 30

10.2 Layout Example .................................................... 30

11 Device and Documentation Support ................. 31

11.1

11.2

11.3

11.4

11.5

11.6

Device Support......................................................

Documentation Support ........................................

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

31

31

31

31

31

31

12 Mechanical, Packaging, and Orderable

Information ........................................................... 31

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original (March 2013) to Revision A

•

2

Page

Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional

Modes section, Application and Implementation section, Power Supply Recommendations section, Layout section,

Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section .................. 1

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

5 Pin Configuration and Functions

DRB Package

8-Pin SON

Bottom View

PH 8

Thermal

Pad (9)

GND 7

COMP 6

VSENSE 5

1 BOOT

2 VIN

See appended

Mechanical

Data for

size and shape

3 EN

4 RT/CLK

Pin Functions

PIN

I/O

DESCRIPTION

NO.

NAME

1

BOOT

O

The device requires a bootstrap capacitor between BOOT and PH. If the voltage on this capacitor is

below the minimum required by the output device, the output switches off until refreshing of the

capacitor is complete.

2

VIN

I

Input supply voltage, 4.7 V to 60 V

3

EN

I

Enable pin with internal pullup current source. Pull below 1.18 V to disable. Float to enable. Adjust

the input undervoltage lockout (UVLO) with two resistors, see Enable and Adjusting Undervoltage

Lockout.

4

RT/CLK

I

Resistor timing and external clock. An internal amplifier holds this pin at a fixed voltage when using

an external resistor to ground to set the switching frequency. Pulling the pin above the PLL upper

threshold causes a mode change, and the pin becomes a synchronization input. The change

disables the internal amplifier, and the pin becomes a high-impedance clock input to the internal PLL.

Stoppage of the clocking edges re-enables the internal amplifier, and the mode returns to a resistor

frequency programming.

5

VSENSE

I

Inverting input of the transconductance (gm) error amplifier

6

COMP

O

Error amplifier output and input to the output switch current comparator. Connect frequency

compensation components to this pin.

7

GND

G

Ground

8

PH

O

The source of the internal high-side power MOSFET and drain of the internal low-side MOSFET

9

Thermal pad

–

Connect the GND pin electrically to the exposed pad on the printed circuit board for proper operation.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

3

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

VIN

EN

Voltage

(2)

MAX

UNIT

62

V

–0.3

8

V

BOOT-PH

8

V

BOOT

70

V

VSENSE

–0.3

6

V

COMP

–0.3

3

V

PH

–0.6

62

V

–2

62

V

–0.3

6

V

100

mA

PH, 10-ns transient

RT/CLK

VIN

Current

MIN

–0.3

Internally limited

BOOT

PH

A

Internally limited

A

Operating junction temperature

–40

150

ºC

Storage temperature, Tstg

–65

150

ºC

(1)

(2)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

See Enable and Adjusting Undervoltage Lockout.

6.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic discharge

Human body model (HBM), per QSS 009-105 (JESD22-A114A) and

AEC-Q100 Classification Level H2 (1)

±2000

Charged-device model (CDM), per QSS 009-147 (JESD22-C101B.01)

and AEC-Q100 500V Classification Level C3B (2)

±750

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

Input voltage, VIN

4.7

Switching frequency synchronized to external clock

4

Submit Documentation Feedback

UNIT

60

V

200

mA

50

1100

kHz

300

1100

kHz

Output current

Switching frequency set by RT/CLK resistor

MAX

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

6.4 Thermal Information

TPS54061-Q1

THERMAL METRIC (1)

DRB (SON)

UNIT

8 PINS

RθJA

Junction-to-ambient thermal resistance

42.9

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

46.0

°C/W

RθJB

Junction-to-board thermal resistance

18.1

°C/W

ψJT

Junction-to-top characterization parameter

0.5

°C/W

ψJB

Junction-to-board characterization parameter

18.3

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

3.0

°C/W

(1)

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

6.5 Electrical Characteristics

TJ = –40°C to 150°C, VIN = 4.7 to 60 V (unless otherwise noted) (1)

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNIT

SUPPLY VOLTAGE (VIN PIN)

Operating input voltage

4.7

60

V

Shutdown supply current

EN = 0 V

1.4

µA

IQ operating; non-switching

VSENSE = 0.9 V, VIN = 12 V

90

110

µA

1.23

1.4

V

ENABLE AND UVLO (EN PIN)

Enable threshold

Input current

Rising

Falling

1

1.18

V

Enable threshold 50 mV

–4.7

µA

Enable threshold –50 mV

–1.2

µA

Hysteresis

–3.5

µA

Enable high to start switching time

450

µs

4.5

V

VIN

VIN start voltage

VIN rising

VOLTAGE REFERENCE

Voltage reference

TJ = 25°C, VIN = 12 V

0.792

0.8

0.808

1 mA < IOUT < Minimum current limit

0.784

0.8

0.816

BOOT-PH = 5.7 V

1.5

3

Ω

VIN = 12 V

0.8

1.5

Ω

V

HIGH-SIDE MOSFET

Switch resistance

LOW-SIDE MOSFET

Switch resistance

ERROR AMPLIFIER

Input current

VSENSE pin

Error-amplifier gm

–2 µA < I(COMP) < 2 µA, V(COMP) = 1 V

EA gm during slow-start

–2 µA < I(COMP) < 2 µA, V(COMP) = 1 V, VSENSE = 0.4 V

Error amplifier DC gain

VSENSE = 0.8 V

Minimum unity-gain bandwidth

Error amplifier source and sink

V(COMP) = 1 V, 100-mV overdrive

Start-switching threshold

COMP to Iswitch gm

(1)

20

nA

108

µMhos

27

µMhos

1000

V/V

0.5

MHz

±8

µA

0.57

V

1

A/V

The electrical ratings specified in this section apply to all specifications in this document unless otherwise noted. These specifications

are interpreted as conditions that do not degrade the parametric or functional specifications of the device for the life of the product

containing it.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

5

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

Electrical Characteristics (continued)

TJ = –40°C to 150°C, VIN = 4.7 to 60 V (unless otherwise noted)(1)

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNIT

250

350

500

mA

CURRENT LIMIT

High-side sourcing current-limit

threshold

BOOT-PH = 5.7 V

Zero-cross detect current

–1.1

mA

176

C

THERMAL SHUTDOWN

Thermal shutdown

RT/CLK

Operating frequency using RT mode

Switching frequency

50

R(RT/CLK) = 120 kΩ

425

Minimum CLK pulse duration

RT/CLK voltage

472

1100

kHz

520

kHz

40

R(RT/CLK) = 120 kΩ

ns

0.53

RT/CLK high threshold

V

1.8

RT/CLK low threshold

0.5

RT/CLK falling-edge to PH risingedge delay

Measure at 500 kHz with RT resistor

PLL lock-in time

Measure at 500 kHz

PLL frequency range

V

V

67

ns

100

300

µs

1100

kHz

PH

Minimum ON-time

Measured at 50% to 50%, IOUT = 200 mA

120

ns

Dead time

VIN = 12 V, IOUT = 200 mA, one transition

30

ns

BOOT

BOOT-to-PH regulation voltage

VIN = 12 V

BOOT-PH UVLO

6

V

2.9

V

2.36

ms

INTERNAL SLOW-START TIME

Slow-start time

6

fSW = 472 kHz, RT = 120 kΩ, 10% to 90%

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

3

1.4

2.5

1.2

On Resistance (Ω)

On Resistance (Ω)

6.6 Typical Characteristics

2

1.5

1

0.5

1

0.8

0.6

0.2

0

–50

–25

50

75

0

100

25

Junction Temperature (°C)

125

0

–50

150

VIN = 12 V

Figure 1. High-Side rDS(on) vs Temperature

150

Figure 2. Low-Side rDS(on) vs Temperature

% of Normal Switching Frequency

Voltage Reference (V)

125

120

0.801

0.799

0.797

0.795

0.793

0.791

0.789

–25

0

25

50

75

100

Junction Temperature (Deg)

125

100

Rising

80

60

40

20

0

150

Falling

0

100

200

300

400

500

600

700

800

Feedback Voltage (mV)

VIN = 12 V

Figure 3. VREF Voltage vs Temperature

RT = 120 kΩ

TJ = 25°C

Figure 4. Frequency vs VSENSE Voltage

540

1100

1000

520

Oscillator Frequency (kHz)

Oscillator Frequency (kHz)

50

75

0

25

100

Junction Temperature (°C)

VIN = 12 V

0.803

0.787

–50

–25

500

480

460

440

420

900

800

700

600

500

400

300

200

100

400

-50

-25

0

25

50

75

100

Junction Temperature (°C)

VIN = 12 V

125

150

RT = 120 kΩ

Figure 5. Frequency vs Temperature

0

25

100

Timing Resistance (kW)

VIN = 12 V

1K

25K

TJ = 25°C

Figure 6. Frequency vs RT/CLK Resistance

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

7

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

140

1.26

120

1.24

Enable Voltage (V)

Transconductance (mS)

Typical Characteristics (continued)

100

80

60

40

VEN Rising

1.22

1.20

VEN Falling

1.18

1.16

1.14

20

1.12

0

–50

–25

50

75

0

25

100

Junction Temperature (°C)

125

1.10

–50

150

VIN = 12 V

0

25

50

75

100

Junction Temperature (°C)

125

150

VIN = 12 V

Figure 7. Error Amplifier Transconductance vs Temperature

Figure 8. Enable-Pin Voltage vs Temperature

-3.35

4.6

4.55

-3.40

4.5

-3.45

Input Voltage (V)

Enable Hysteresis Current (µA)

–25

-3.50

-3.55

-3.60

-3.65

4.45

4.4

4.35

4.3

UVLO Start

4.25

4.2

4.15

UVLO Stop

4.1

4.05

-3.70

-3.75

–50

–25

50

75

0

25

100

Junction Temperature (°C)

125

4

-50

150

-25

0

25

50

75

100

125

150

Junction Temperature (°C)

VIN = 12 V

Figure 9. Enable-Pin Hysteresis Current

vs Temperature

Figure 10. Input Voltage (UVLO) vs Temperature

3

-1

-1.05

2.5

Shutdown Current (µA)

Enable Current (µA)

-1.1

-1.15

-1.2

-1.25

-1.3

-1.35

-1.4

2

1.5

1

TJ = 150°C

TJ = −40°C

TJ = 25°C

0.5

-1.45

-1.5

0

0

5

10

15

20

25 30 35 40

Input Voltage (V)

VIN = 12 V

45

50

55

60

5

10

15

20

25 30 35 40

Input Voltage (V)

45

50

55

60

EN = 0 V

TJ = 25°C

Figure 11. Enable-Pin Pullup Current vs Input Voltage

8

0

Figure 12. Shutdown Supply Current (VIN Pin)

vs Input Voltage

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

98

2

96

1.75

94

Supply Current (µA)

Supply Current (µA)

Typical Characteristics (continued)

92

90

88

86

84

TJ = 150°C

TJ = −40°C

TJ = 25°C

82

80

0

5

10

15

20

25 30 35 40

Input Voltage (V)

45

EN = Open

50

55

1.5

1.25

1

0.75

0.5

0.25

0

60

VSENSE = 0.83 V

1

2

3

Input Voltage (V)

4

5

Figure 14. Supply Current (VIN Pin)

vs Input Voltage (0 V to VSTART), EN Pin Low

160

2.48

TJ = 150°C

120

TJ = –40°C

100

TJ = 25°C

2.46

2.44

SS Time (ms)

140

Supply Current (µA)

0

EN = 0 V

Figure 13. Supply Current (VIN Pin) vs Input Voltage

80

60

2.42

2.40

2.38

40

2.36

20

2.34

0

TJ = 150°C

TJ = −40°C

TJ = 25°C

0

1

2

3

Input Voltage (V)

4

2.32

-50

5

EN = Open

-25

0

25

50

75

100

Junction Temperature (°C)

VIN = 12 V

Figure 15. Supply Current (VIN Pin) vs

Input Voltage (0 V to VSTART), EN Pin Open

125

150

fsw = 472 kHz

Figure 16. Slow-Start Time vs Temperature

Current Limit Threshold (A)

0.45

TJ = 25°C

TJ = –40°C

0.4

0.35

0.3

TJ = 150°C

0.25

0.2

0

5

10

15

20

25 30 35 40

Input Voltage (V)

45

50

55

60

Figure 17. Current Limit vs Input Voltage

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

9

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

7 Detailed Description

7.1 Overview

The TPS54061-Q1 device is a 60-V, 200-mA, step-down (buck) regulator with integrated high-side and low-side

N-channel MOSFETs. To improve performance during line and load transients, the device implements a

constant-frequency, current-mode control which reduces output capacitance and simplifies external frequencycompensation design.

The switching frequency of 50 kHz to 1100 kHz allows for efficiency and size optimization when selecting the

output filter components. Adjustment of the switching frequency is by use of a resistor to ground on the RT/CLK

pin. The device has an internal phase-lock loop (PLL) on the RT/CLK pin that synchronizes the power-switch

turnon to a falling edge of an external system clock.

The TPS54061-Q1 has a default start-up voltage of approximately 4.5 V. The EN pin has an internal pullup

current source, a possible use of which is to adjust the input voltage undervoltage lockout (UVLO) threshold with

two external resistors. In addition, the pullup current provides a default condition. When the EN pin is floating, the

device operates. The operating current is 90 µA when not switching and under no load. When the device is

disabled, the supply current is 1.4 µA.

The integrated 1.5-Ω high-side MOSFET and 0.8-Ω low-side MOSFET allow for high-efficiency power-supply

designs capable of delivering 200 milliamperes of continuous current to a load.

The TPS54061-Q1 reduces the external component count by integrating the boot recharge diode. A capacitor

between the BOOT and PH pins supplies the bias voltage for the integrated high-side MOSFET. The boot

capacitor voltage is monitored by an UVLO circuit and turns the high-side MOSFET off when the boot voltage

falls below a preset threshold. The TPS54061-Q1 can operate at high duty cycles because of the boot UVLO.

The output voltage can be adjusted down to as low as the 0.8-V reference.

The TPS54061-Q1 has an internal output OV protection that disables the high-side MOSFET if the output voltage

is 109% of the nominal output voltage.

The TPS54061-Q1 reduces external component count by integrating the slow-start time using a reference DAC

system.

The TPS54061-Q1 resets the slow-start times during overload conditions with an overload recovery circuit. The

overload recovery circuit slow-starts the output from the fault voltage to the nominal regulation voltage once a

fault condition is removed. A frequency foldback circuit reduces the switching frequency during start-up and

overcurrent fault conditions to help control the inductor current.

10

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

7.2 Functional Block Diagram

VIN

EN

Thermal

Shutdown

Enable

Comparator

UVLO

Shutdown

Shutdown

Logic

Enable

Threshold

VSENSE

Boot

Charge

Regulator

OV

ERROR

AMPLIFIER

Boot

UVLO

Minimum

Clamp

Current

Sense

PWM

Comparator

BOOT

Deadtime

Control Logic

Reference DAC

With

Slow Start

Shutdown

S

Slope

Compensation

PH

COMP

Frequency

Shift

DRV

REG

Maximum

Clamp

Oscillator

with PLL

ZX

detect

GND

RT /CLK

THERMAL PAD

7.3 Feature Description

7.3.1 Fixed Frequency PWM Control

The TPS54061-Q1 uses adjustable fixed frequency, peak current mode control. The output voltage is sensed

through external resistors on the VSENSE pin and compared to an internal voltage reference by an error

amplifier which drives the COMP pin. An internal oscillator initiates the turnon of the high-side power switch. The

error amplifier output is compared to the high-side power switch current. When the power switch current reaches

the level set by the COMP voltage, the power switch is turned off. The COMP pin voltage increases and

decreases as the output current increases and decreases. The device implements current limiting by clamping

the COMP pin voltage to a maximum level.

7.3.2 Slope Compensation Output Current

The TPS54061-Q1 adds a compensating ramp to the switch current signal. This slope compensation prevents

sub-harmonic oscillations.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

11

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

Feature Description (continued)

7.3.3 Error Amplifier

The TPS54061-Q1 uses a transconductance amplifier for the error amplifier. The error amplifier compares the

VSENSE voltage to the lower of the internal slow-start voltage or the internal 0.8-V voltage reference. The

transconductance (gm) of the error amplifier is 108 µA/V during normal operation. During the slow-start

operation, the transconductance is a fraction of the normal operating gm. The frequency compensation

components (capacitor, and the series resistor and capacitor) are added to the COMP pin to ground.

7.3.4 Voltage Reference

The voltage reference system produces a precise voltage reference over temperature by scaling the output of a

temperature stable band-gap circuit.

7.3.5 Adjusting the Output Voltage

The output voltage is set with a resistor divider from the output node to the VSENSE pin. TI recommends using

1% tolerance or better divider resistors. Start with 10 kΩ for the RLS resistor and use Equation 1 to calculate RHS.

- 0.8 V ö

æV

RHS = RLS ´ ç OUT

÷÷

ç

0.8 V

è

ø

(1)

7.3.6 Enable and Adjusting Undervoltage Lockout (UVLO)

The TPS54061-Q1 is enabled when the VIN pin voltage rises above 4.5 V and the EN pin voltage exceeds the

EN rising threshold of 1.23 V. The EN pin has an internal pull-up current source, I1, of 1.2 µA that provides the

default enabled condition when the EN pin floats.

If an application requires a higher input undervoltage lockout (UVLO) threshold, use the circuit shown in

Figure 18 to adjust the input voltage UVLO with two external resistors. When the EN pin voltage exceeds 1.23 V,

an additional 3.5 µA of hysteresis current, Ihys, is sourced out of the EN pin. When the EN pin is pulled below

1.18 V, the 3.5-µA Ihys current is removed. This additional current facilitates adjustable input voltage hysteresis.

Use Equation 2 to calculate RUVLO1 for the desired input start and stop voltages. Use Equation 3 to similarly

calculate RUVLO2.

In applications designed to start at relatively low input voltages (for example, from 4.7 V to 10 V) and withstand

high input voltages (for example, from 40 V to 60 V), the EN pin may experience a voltage greater than the

absolute maximum voltage of 8 V during the high input voltage condition. TI recommends to use a Zener diode to

clamp the pin voltage below the absolute maximum rating.

VIN

TPS54061

i1

ihys

Ruvlo1

EN

Optional

VEN

Ruvlo2

Figure 18. Adjustable Undervoltage Lockout

æV

ö

VSTART ç ENAFALLING ÷ - VSTOP

è VENARISING ø

RUVLO 1 =

æ V

ö

I1 × ç 1- ENAFALLING ÷ + IHYS

VENARISING ø

è

12

Submit Documentation Feedback

(2)

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

Feature Description (continued)

RUVLO 2 =

RUVLO 1 ´ VENAFALLING

VSTOP - VENAFALLING + RUVLO 1 ´ (I1 + IHYS )

(3)

7.3.7 Internal Slow-Start

The TPS54061-Q1 has an internal digital slow-start that ramps the reference voltage from 0 V to its final value in

1114 switching cycles. The internal slow-start time is calculated by Equation 4:

1114

tss(ms) =

fSW (kHz)

(4)

If the EN pin is pulled below the stop threshold of 1.18 V, switching stops and the internal slow-start resets. The

slow-start also resets in thermal shutdown.

7.3.8 Constant Switching Frequency and Timing Resistor (RT/CLK Pin)

The switching frequency of the TPS54061-Q1 is adjustable over a wide range from 50 kHz to 1100 kHz by

varying the resistor on the RT/CLK pin. The RT/CLK pin voltage is typically 0.53 V and must have a resistor to

ground to set the switching frequency. To determine the timing resistance for a given switching frequency, use

Equation 5. To reduce the solution size, the switching frequency is typically set as high as possible, but tradeoffs

of the supply efficiency, maximum input voltage, and minimum controllable ON-time should be considered. The

minimum controllable ON-time is typically 120 ns and limits the operating frequency for high input voltages. The

maximum switching frequency is also limited by the frequency shift circuit. More discussion on the details of the

maximum switching frequency, refer to Selecting the Switching Frequency.

71657

RT (kW) =

fSW (kHz)1.039

(5)

7.3.9 Selecting the Switching Frequency

The TPS54061-Q1 implements current mode control which uses the COMP pin voltage to turn off the high-side

MOSFET on a cycle-by-cycle basis. Each cycle the switch current and COMP pin voltage are compared, when

the peak switch current intersects the COMP voltage, the high-side switch is turned off. During overcurrent

conditions that pull the output voltage low, the error amplifier responds by driving the COMP pin high, increasing

the switch current. The error amplifier output is clamped internally, which functions as a switch current limit.

To enable higher switching frequency at high input voltages, the TPS54061-Q1 implements a frequency shift.

The switching frequency is divided by 8, 4, 2, and 1 as the voltage ramps from 0 to 0.8 V on VSENSE pin. The

device implements a digital frequency shift to enable synchronizing to an external clock during normal start-up

and fault conditions. Because the device can only divide the switching frequency by 8, there is a maximum input

voltage limit in which the device operates and still have frequency shift protection. During short-circuit events

(particularly with high input voltage applications), the control loop has a finite minimum controllable ON-time and

the output has a low voltage. During the switch ON-time, the inductor current ramps to the peak current limit

because of the high input voltage and minimum ON-time. During the switch OFF-time, the inductor would

normally not have enough OFF-time and output voltage for the inductor to ramp down by the ramp up amount.

The frequency shift effectively increases the OFF-time allowing the current to ramp down.

æ 1 ö

æ V OUT + R LS ´ I O + R DC ´ I O ö

fSW (maxskip) = ç

÷ ´ ç

÷

è t ON ø

è V IN - I O ´ R HS + I O ´ R LS ø

where

•

•

•

•

•

•

•

tON = Controllable ON-time

VOUT = Output Voltage

RLS = Low-side MOSFET resistance

IO = Output Current

RDC = Inductor resistance

VIN = Input Voltage

RHS = High-side MOSFET resistance

(6)

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

13

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

Feature Description (continued)

f

SW (shift)

æ f div ö æ V OUTSC + R LS × I CL + R DC ´ I CL ö

= ç

÷ × ç

÷

è t ON ø è V IN - I CL ´ R HS + I CL ´ R LS ø

where

•

•

•

fdiv = Frequency divide (equals 1, 2, 4, or 8)

VOUTSC Output Voltage during short

ICL = Current Limit

(7)

7.3.10 Synchronization to RT/CLK Pin

The RT/CLK pin can be used to synchronize the regulator to an external system clock. To implement the

synchronization feature connect a square wave to the RT/CLK pin through one of the circuit networks shown in

Figure 19. The square wave amplitude must extend lower than 0.5 V and higher than 1.8 V on the RT/CLK pin

and have high and low states greater than 40 ns. The synchronization frequency range is 300 kHz to 1100 kHz.

The rising edge of the PH is synchronized to the falling edge of RT/CLK pin signal. The external synchronization

circuit should be designed in such a way that the device has the default frequency set resistor connected from

the RT/CLK pin to ground should the synchronization signal turn off. TI recommends using a frequency set

resistor connected as shown in Figure 19 through another resistor (for example, 50 Ω) to ground for clock signal

that are not Hi-Z or tristate during the OFF-state. The sum of the resistance should set the switching frequency

close to the external CLK frequency. TI recommends to AC couple the synchronization signal through a 10-pF

ceramic capacitor to RT/CLK pin. The first time the CLK is pulled above the CLK threshold the device switches

from the RT resistor frequency to PLL mode. The internal 0.5-V voltage source is removed and the CLK pin

becomes high impedance as the PLL starts to lock onto the external signal. The switching frequency can be

higher or lower than the frequency set with the RT/CLK resistor. The device transitions from the resistor mode to

the PLL mode and lock onto the CLK frequency within 100 microseconds. When the device transitions from the

PLL mode to the resistor mode, the switching frequency reduces from the external CLK frequency to 150 kHz,

then reapply the 0.5-V voltage source and the resistor then sets the switching frequency. The switching

frequency is divided by 8, 4, 2, and 1 as the voltage ramps from 0 to 0.8 V on VSENSE pin. The device

implements a digital frequency shift to enable synchronizing to an external clock during normal start-up and fault

conditions.

TPS54061

TPS54061

RT/CLK

RT/CLK

PLL

PLL

RT

Hi -Z

Clock

Source

Clock

Source

RT

Figure 19. Synchronizing to a System Clock

7.3.11 Overvoltage Protection

The TPS54061-Q1 incorporates an output overvoltage transient protection (OVP) circuit to minimize voltage

overshoot when recovering from output fault conditions or strong unload transients on power supply designs with

low value output capacitance. For example, when the power supply output is overloaded the error amplifier

compares the actual output voltage to the internal reference voltage. If the VSENSE pin voltage is lower than the

internal reference voltage for a considerable time, the output of the error amplifier responds by clamping the error

amplifier output to a high voltage. Thus, requesting the maximum output current. Once the condition is removed,

the regulator output rises and the error amplifier output transitions to the steady-state duty cycle. In some

applications, the power supply output voltage can respond faster than the error amplifier output can respond, this

actuality leads to the possibility of an output overshoot.

14

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

Feature Description (continued)

The OVP feature minimizes the output overshoot when using a low value output capacitor by comparing the

VSENSE pin voltage to OVP threshold which is 109% of the internal voltage reference. If the VSENSE pin

voltage is greater than the OVP threshold, the high-side MOSFET is disabled to minimize output overshoot.

When the VSENSE voltage drops lower than the OVP threshold, the high-side MOSFET resumes normal

operation.

7.3.12 Thermal Shutdown

The device implements an internal thermal shutdown until the junction temperature exceeds 176°C. The thermal

shutdown forces the device to stop switching until the junction temperature falls below the thermal trip threshold.

Once the die temperature decreases below 176°C, the device reinitiates the power up sequence by restarting the

internal slow-start.

7.4 Device Functional Modes

7.4.1 Operation Near Minimum Input Voltage

The TPS54061-Q1 is recommended to operate with input voltages above 4.7 V. The typical VIN UVLO threshold

is 4.5 V and the device may operate at input voltages down to the UVLO voltage. At input voltages below the

actual UVLO voltage the device does not switch. If EN is floating or externally pulled up to greater up than the

typical 1.23-V rising threshold, when V(VIN) passes the UVLO threshold the TPS54061-Q1 becomes active.

Switching is enabled and the slow-start sequence is initiated. The TPS54061-Q1 starts linearly ramping up the

internal reference DAC from 0 V to the reference voltage over the internal slow-start time period set by the

switching frequency.

7.4.2 Operation With Enable Control

The enable start threshold voltage is 1.23 V typical. With EN held below the 1.23-V typical rising threshold

voltage, the TPS54061-Q1 is disabled and switching is inhibited even if VIN is above its UVLO threshold. The

quiescent current is reduced in this state. If the EN voltage is increased above the rising threshold voltage while

V(VIN) is above the UVLO threshold, the device becomes active. Switching is enabled and the slow-start

sequence is initiated. The TPS54061-Q1 starts linearly ramping up the internal reference DAC from 0 V to the

reference voltage over the internal slow-start time period set by the switching frequency. If EN is pulled below the

1.18-V typical falling threshold, the TPS54061-Q1 enters the reduced quiescent current state again.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

15

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

8 Applications and Implementation

NOTE

Information in the following applications sections is not part of the TI component

specification, and TI does not warrant its accuracy or completeness. TI’s customers are

responsible for determining suitability of components for their purposes. Customers should

validate and test their design implementation to confirm system functionality.

8.1 Application Information

The TPS54061-Q1 is a 60-V, 200-mA step-down regulator with an integrated high-side and low-side MOSFET.

This device is typically used to convert a higher DC voltage to a lower DC voltage with a maximum available

output current of 200 mA. Example applications are: Low-Power Standby or Bias Voltage Supplies or an efficient

replacement for high-voltage linear regulator. Use the following design procedure to select component values for

the TPS54061-Q1. This procedure shows the design of a high-frequency switching regulator. These calculations

can be done with the aid of the TPS54x40/x60 design calculator (SLVC431). Alternatively, use the WEBENCH

software to generate a complete design. The WEBENCH software uses an iterative design procedure and

accesses a comprehensive database of components when generating a design.

8.2 Typical Applications

8.2.1 Continuous Conduction Mode Application

C BOOT

0.01 μ F

LO

U1

TPS54061

8 V to 60 V

R UVLO1

C IN

196 kΩ

2.2 μ F

R UVLO2

1

8

2

7

3

6

4

3.3 V 200 mA

2

1

R COMP

R HS

CO

5

RT

36.5 kΩ

100 μ H

31.6 kΩ

26.1 kΩ

C POLE

C COMP

33 pF

4700 pF

10 μ F

R LS

143 kΩ

10 kΩ

* See Enable and Adjusting Undervoltage Lockout.

Figure 20. CCM Application Schematic

8.2.1.1 Design Requirements

This example details the design of a continuous conduction mode (CCM) switching regulator design using

ceramic output capacitors. If a low output current design is needed, see Discontinuous Conduction Mode

Application. A few parameters must be known in order to start the design process. These parameters are

typically determined at the system level. For this example, the following known parameters are listed in Table 1.

Table 1. Design Parameters

PARAMETER

VALUE

Output voltage, VOUT

5.0 V

Transient response 50 to 150-mA load step

ΔVOUT = 4%

Maximum output current

200 mA

Input voltage, VIN

24 V nominal, 8 V to 60 V

Output voltage ripple

0.5% of VOUT

16

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

Typical Applications (continued)

Table 1. Design Parameters (continued)

PARAMETER

VALUE

Start input voltage (rising VIN)

7.50 V

Stop input voltage (falling VIN)

6.50 V

8.2.1.2 Detailed Design Procedure

8.2.1.2.1 Selecting the Switching Frequency

The first step is to decide on a switching frequency for the regulator. Typically, the user wants to choose the

highest switching frequency possible because this produces the smallest solution size. The high switching

frequency allows for lower valued inductors and smaller output capacitors compared to a power supply that

switches at a lower frequency. The switching frequency is limited by the minimum on-time of the internal power

switch, the maximum input voltage, the output voltage and the frequency shift limitation.

Equation 6 and Equation 7 must be used to find the maximum switching frequency for the regulator, choose the

lower value of the two results. Switching frequencies higher than these values results in pulse skipping or a lack

of overcurrent protection during short circuit conditions. The typical minimum ON-time, tonmin, is 120 ns for the

TPS54061-Q1. To ensure overcurrent runaway does not occur during short circuits in your design, use

Equation 7 to determine the maximum switching frequency. With a maximum input voltage of 60 V, inductor

resistance of 0.77 Ω, high-side switch resistance of 3.0 Ω, low-side switch resistance of 1.5 Ω, a current limit

value of 350 mA, and a short circuit output voltage of 0.1 V, the maximum switching frequency is 524 kHz and

1003 kHz in each case respectively. A switching frequency of 400 kHz is used. To determine the timing

resistance for a given switching frequency, use Equation 5. The switching frequency is set by resistor RT shown

in Figure 20. RT is calculated to be 142 kΩ. A standard value of 143 kΩ is used.

8.2.1.2.2 Output Inductor Selection (LO)

To calculate the minimum value of the output inductor, use Equation 8. KIND is a coefficient that represents the

amount of inductor ripple current relative to the maximum output current. The inductor ripple current is filtered by

the output capacitor. Therefore, choosing high inductor ripple currents impacts the selection of the output

capacitor because the output capacitor must have a ripple current rating equal to or greater than the inductor

ripple current. In general, the inductor ripple value is at the discretion of the designer; however, the following

guidelines may be used. TI typically recommends using KIND values in the range of 0.2 to 0.4; however, for

designs using low ESR output capacitors such as ceramics and low output currents, a KIND value as high as 1

may be used. In a wide input voltage regulator, it is best to choose an inductor ripple current on the larger side.

This allows the inductor to still have a measurable ripple current with the input voltage at its minimum. For this

design example, use KIND of 0.4 and the minimum inductor value is calculated to be 97 µH. For this design, a

standard 100-µH value was chosen. It is important that the RMS current and saturation current ratings of the

inductor not be exceeded. The RMS and peak inductor current can be found from Equation 10 and Equation 11.

For this design, the RMS inductor current is 200 mA and the peak inductor current is 239 mA. The chosen

inductor is a Würth 74408943101. It has a saturation current rating of 680 mA and an RMS current rating of

520 mA. Equation 8 through Equation 11 show lower ripple currents reduce the output voltage ripple of the

regulator but require a larger value of inductance. Selecting higher ripple currents increases the output voltage

ripple of the regulator but allow for a lower inductance value. The current flowing through the inductor is the

inductor ripple current plus the average output current. During power up, faults or transient load conditions, the

inductor current can increase above the peak inductor current level calculated above. In transient conditions, the

inductor current can increase up to the switch current limit of the device. For this reason, the most conservative

approach is to specify an inductor with a saturation current rating equal to or greater than the switch current limit

rather than the calculated peak inductor current.

V max - VOUT

VOUT

´

LO min ³ IN

Kind ´ IO

VIN max ´ ¦ sw

(8)

IRIPPLE ³

VOUT ´

(VINmax

- VOUT )

VINmax ´ LO ´ fSW

(9)

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

17

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

IL rms = IO

2

IL peak = IOUT

www.ti.com

æ VOUT ´ (VINmax - VOUT ) ö

1

+

´ ç

÷÷

ç

12

VINmax ´ LO ´ fSW

è

ø

2

I

+ RIPPLE

2

(10)

(11)

8.2.1.2.3 Output Capacitor

There are three primary considerations for selecting the value of the output capacitor. The output capacitor

determines the modulator pole, the output voltage ripple, and how the regulator responds to a large change in

load current. The output capacitance needs to be selected based on the most stringent of these three criteria.

The desired response to a large change in the load current is the first criteria. The output capacitor needs to

supply the load with current until the regulator increases the inductor current. This situation occurs if there are

desired hold-up times for the regulator where the output capacitor must hold the output voltage above a certain

level for a specified amount of time after the input power is removed. The regulator also is temporarily not able to

supply sufficient output current if there is a large, fast increase in the current needs of the load such as

transitioning from no load to a full load. The regulator usually needs two or more clock cycles for the control loop

to see the change in load current and output voltage and adjust the duty cycle to react to the change. The output

capacitor must be sized to supply the extra current to the load until the control loop responds to the load change.

The output capacitance must be large enough to supply the difference in current for 2 clock cycles while only

allowing a tolerable amount of droop in the output voltage. Equation 15 shows the minimum output capacitance

necessary to accomplish this, where ΔIout is the change in output current, ƒsw is the regulators switching

frequency and ΔVOUT is the allowable change in the output voltage.

For this example, the transient load response is specified as a 4% change in VOUT for a load step from 50 mA to

150 mA. For this example, ΔIOUT = 0.150 – 0.05 = 0.10 and ΔVOUT = 0.04 × 3.3 = 0.132.

Using these values gives a minimum capacitance of 3.79 µF. This does not take the ESR of the output capacitor

into account in the output voltage change. For ceramic capacitors, the ESR is usually small enough to ignore in

this calculation. Aluminum electrolytic and tantalum capacitors have higher ESR that should be taken into

account.

The low-side FET of the regulator emulates a diode so it can not sink current so any stored energy in the

inductor produces an output voltage overshoot when the load current rapidly decreases, as in Figure 28. The

output capacitor must also be sized to absorb energy stored in the inductor when transitioning from a high load

current to a lower load current. The excess energy that gets stored in the output capacitor increases the voltage

on the capacitor. The capacitor must be sized to maintain the desired output voltage during these transient

periods. Equation 14 is used to calculate the minimum capacitance input the output voltage overshoot to a

desired value, where LO is the value of the inductor, IOH is the output current under heavy load, IOL is the output

under light load, VOUT + ΔVOUT is the final peak output voltage, and VI is the initial capacitor voltage. For this

example, the worst case load step is from 150 mA to 50 mA. The output voltage increases during this load

transition and must be limited to 4% of the output voltage to satisy the design goal. This makes VOUT+ΔVOUT =

1.04 × 3.3 = 3.432 V. VOUT is the initial capacitor voltage which is the nominal output voltage of 3.3 V. Using

these numbers in Equation 14 yields a minimum capacitance of 2.25 µF.

Equation 13 calculates the minimum output capacitance needed to meet the output voltage ripple specification,

where fSW is the switching frequency, VRIPPLE is the maximum allowable output voltage ripple, and IRIPPLE is the

inductor ripple current. Equation 13 yields 1.48 µF. Equation 16 calculates the maximum ESR an output

capacitor can have to meet the output voltage ripple specification. Equation 16 indicates the ESR should be less

than 0.160 Ω.

The most stringent criteria for the output capacitor is 3.79 µF of capacitance to maintain the output voltage

regulation during an load transient.

Additional capacitance de-ratings for aging, temperature, and DC bias increases this minimum value. For this

example, a 100-µF, 10-V X5R ceramic capacitor with 0.003 Ω of ESR if a 1206 package is used.

Capacitors generally have limits to the amount of ripple current they can handle without failing or producing

excess heat. An output capacitor that can support the inductor ripple current must be specified. Some capacitor

data sheets specify the Root Mean Square (RMS) value of the maximum ripple current.

Equation 12 can be used to calculate the RMS ripple current the output capacitor needs to support. For this

example, Equation 12 yields 10.23 mA.

18

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

ICOrms =

CO 1 ³

æ VOUT ´ (VINmax - VOUT ) ö

´ ç

÷÷

ç

VINmax ´ LO ´ fSW

12

è

ø

1

(12)

æ

ö

IRIPPLE

1

´ ç

÷

VRIPPLE

è 8 ´ fSW ø

CO 2 ³ LO ´

IOH2

(VOUT

(13)

- IOL

2

+ DVOUT )

2

- VOUT 2

(14)

DIOUT

2

CO 3 ³

´

DVOUT f sw

RC

(15)

V

£ RIPPLE

IRIPPLE

(16)

8.2.1.2.4 Input Capacitor

The TPS54061-Q1 requires a high-quality ceramic, type X5R or X7R, input decoupling capacitor of at least

1-µF of effective capacitance. The effective capacitance includes any deration for DC bias effects. The voltage

rating of the input capacitor must be greater than the maximum input voltage. The capacitor must also have an

RMS current rating greater than the maximum RMS input current. The input RMS current can be calculated using

Equation 17. The value of a ceramic capacitor varies significantly over temperature and the dc bias applied to the

capacitor. The capacitance variations with temperature can be minimized by selecting a dielectric material that is

stable over temperature. X5R and X7R ceramic dielectrics are usually selected for power regulator capacitors

because they have a high capacitance to volume ratio and are fairly stable over temperature. The effective value

of a capacitor decreases as the DC bias across a capacitor increases. For this example design, a ceramic

capacitor with at least a 60-V voltage rating is required to support the maximum input voltage. The input

capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated

by rearranging Equation 18.

Using the design example values, IOUTmax = 200 mA, CIN = 2.2 µF, ƒSW = 400 kHz, yields an input voltage ripple

of 56.8 mV and an RMS input ripple current of 98.5 mA.

ICINrms = IOUT ´

CIN ³

VOUT

´

VINmin

(VINmin

- VOUT )

VINmin

(17)

æ 0.25 ö

IO

´ ç

÷

VINripple

è fSW ø

(18)

8.2.1.2.5 Bootstrap Capacitor Selection

A 0.01-µF ceramic capacitor must be connected between the BOOT and PH pins for proper operation. TI

recommends using a ceramic capacitor with X5R or better grade dielectric. The capacitor should have 10-V or

higher voltage rating.

8.2.1.2.6 Undervoltage Lockout Set Point

The Undervoltage Lockout (UVLO) can be adjusted using an external voltage divider on the EN pin of the

TPS54061-Q1. The UVLO has two thresholds: one for power up when the input voltage is rising and one for

power down or brown outs when the input voltage is falling. For the example design, the supply should turn on

and start switching once the input voltage increases above 7.50 V (enabled). After the regulator starts switching,

it should continue to do so until the input voltage falls below 6.50 V (UVLO stop). The programmable UVLO and

enable voltages are set by connecting resistor divider between VIN and ground to the EN pin. Equation 2 and

Equation 3 can be used to calculate the resistance values necessary. For example, a 196-kΩ resistor between

VIN and EN and a 36.5-kΩ resistor between EN and ground are required to produce the 7.50-V and 6.50-V start

and stop voltages. See Enable and Adjusting Undervoltage Lockout for additional considerations in high input

voltage applications.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

19

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

8.2.1.2.7 Output Voltage and Feedback Resistors Selection

For the example design, 10 kΩ was selected for RLS. Using Equation 1, RHS is calculated as 31.46 kΩ. The

nearest standard 1% resistor is 31.6 kΩ.

8.2.1.2.8 Closing the Loop

There are several methods used to compensate DC–DC regulators. The method presented here is easy to

calculate and ignores the effects of the slope compensation that is internal to the device. Because the slope

compensation is ignored, the actual cross over frequency is usually lower than the crossover frequency used in

the calculations. This method assume the crossover frequency is between the modulator pole and the ESR zero

and the ESR zero is at least 10 times greater the modulator pole.

To get started, the modulator pole, fpole, and the ESR zero, fzero must be calculated using Equation 19 and

Equation 20. For COUT, use a derated value of 6.0 µF. Use Equation 21 and Equation 22 to estimate a starting

point for the crossover frequency, fco, to design the compensation. For the example design, fpole is 1015 Hz and

fzero is 5584 kHz.

Equation 21 is the geometric mean of the modulator pole and the ESR zero and Equation 22 is the mean of

modulator pole and the switching frequency. Equation 21 yields 119.2 kHz and Equation 22 gives 17.9 kHz. Use

a frequency near the lower value of Equation 21 or Equation 22 for an initial crossover frequency.

For this example, fco of 17.9 kHz is used. Next, the compensation components are calculated. A resistor in

series with a capacitor is used to create a compensating zero. A capacitor in parallel to these two components

forms the compensating pole.

To determine the compensation resistor, RCOMP, use Equation 23. Assume the power stage transconductance,

gmps, is 1.00 A/V. The output voltage, VOUT, reference voltage, VREF, and amplifier transconductance, gmea, are

3.3 V, 0.8 V and 108 µA/V, respectively.

RCOMP is calculated to be 25.9 kΩ, use the nearest standard value of 26.1 kΩ. Use Equation 24 to set the

compensation zero equal to the modulator pole frequency. Equation 24 yields a 3790 pF for capacitor CCOMP and

a 4700 pF is chosen. Use the larger value of Equation 25 and Equation 26 to calculate the CPOLE value to set the

compensation pole. Equation 26 yields 30.5 pF so the nearest standard of 33 pF is selected.

1

f pole(Hz) =

VOUT

´ Co ´ 2 ´ p

Io

(19)

1

f zero(Hz) =

RC ´ CO ´ 2 ´ p

(20)

0.5

f co1(Hz) = ( f zero ´ f pole)

(21)

0.5

æ f sw

ö

f co2(Hz) = ç

´ f pole ÷

2

è

ø

RCOMP =

(22)

2 ´ p ´ ¦ CO ´ CO

VOUT

´

gmps

VREF ´ gmea

1

C5 =

2 ´ p ´ R4 ´ fPOLE

(24)

R ´ CO

C6 = C

R4

1

C6 =

R4 ´ fSW ´ p

20

(23)

(25)

(26)

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

100

100

90

90

80

80

70

70

60

50

40

VIN = 8 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

VIN = 60 V

30

20

10

0

0

0.025

0.05

0.075 0.1 0.125

Load Current (A)

0.15

0.175

Efficiency (%)

Efficiency (%)

8.2.1.3 Application Curves

60

50

40

20

10

0

0.001

0.2

fsw = 400 kHz

90

80

80

70

70

60

50

40

VIN = 8 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

VIN = 60 V

30

20

10

0.075 0.1 0.125

Load Current (A)

0.15

VOUT = 5 V

0.175

Efficiency (%)

Efficiency (%)

100

90

0.05

50

40

10

0

0.001

0.2

1

VOUT = 5 V

20

60

0

0

–60

–120

–40

Gain

Phase

–180

100K

Output Voltage Normalized (%)

120

–20

fsw = 400 kHz

0.25

Phase (º)

Gain (dB)

40

0.2

0.15

0.1

0.05

0

–0.05

–0.1

–0.15

–0.2

–0.25

0

10

IOUT = 200 mA

Figure 25. Gain vs Phase

0.1

Figure 24. Efficiency vs Output Current

180

10K

0.01

Load Current (A)

60

1K

Frequency (Hz)

VIN = 8 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

VIN = 60 V

30

20

fsw = 400 kHz

100

fsw = 400 kHz

60

Figure 23. Efficiency vs Output Current

–60

10

1

Figure 22. Efficiency vs Output Current

100

0.025

0.1

VOUT = 3.3 V

Figure 21. Efficiency vs Output Current

0

0.01

Load Current (A)

VOUT = 3.3 V

0

VIN = 8 V

VIN = 12 V

VIN = 24 V

VIN = 36 V

VIN = 60 V

30

30

20

40

Input Voltage (V)

50

60

fsw = 400 kHz

Figure 26. Output Voltage vs Input Voltage

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

21

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

Output Voltage Normalized (%)

0.50

0.40

0.30

IOUT = 100 mA /div

0.20

0.10

0

–0.10

–0.20

–0.30

–0.40

–0.50

0

0.025

0.05

VIN = 24 V

0.075 0.1 0.125

Load Current (A)

0.15

VOUT = 3.3 V

0.175

VOUT = 50 mV /div ac coupled

0.2

fsw = 400 kHz

500 µs /div

Figure 27. Output Voltage vs Output Current

Figure 28. Load Transient

VIN = 10 V /div

VIN = 10 V /div

VEN = 5 V /div

VOUT = 20 mV /div ac coupled

VOUT = 2 V /div

1 ms /div

5 ms /div

Figure 30. Start-Up With ENA

Figure 29. Line Transient

PH = 20 V /div

VIN = 10 V /div

Inductor Current = 200 mA /div

VEN = 2 V /div

VOUT = 2 V /div

VIN = 10 mV /div ac coupled

2 ms /div

2 µs /div

Figure 31. Start-Up With VIN

22

Submit Documentation Feedback

Figure 32. Input Ripple in DCM

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

PH = 20 V /div

PH = 20 V /div

Inductor Current = 200 mA /div

Inductor Current = 200 mA /div

VIN = 50 mV /div ac coupled

VIN = 10 mV /div ac coupled

2 µs /div

2 µs /div

Figure 33. Input Ripple in CCM

Figure 34. Input Ripple Skip

PH = 20 V /div

PH = 20 V /div

Inductor Current = 200 mA /div

Inductor Current = 200 mA/div

VOUT = 10 mV /div

VOUT = 10 mV /div ac coupled

2 µs /div

2 µs /div

Figure 35. Output Ripple in DCM

Figure 36. Output Ripple in CCM

PH = 20 V /div

Inductor Current = 200 mA /div ac coupled

VOUT = 20 mV /div ac coupled

2 µs /div

Figure 37. Output Ripple Skip

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

23

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

www.ti.com

8.2.2 Discontinuous Conduction Mode Application

It is most desirable to have a power supply that is efficient and has a fixed switching frequency at low output

currents. A fixed-frequency power supply has a predictable output voltage ripple and noise. Using a traditional

continuous conduction mode (CCM) design method to calculate the output inductor yields a large inductance for

a low output current supply. Using a CCM inductor results in a large sized supply or affects efficiency from the

large DC resistance, an alternative is to operate in discontinuous conduction mode (DCM). Use the procedure

below to calculate the components values for designing a power supply operating in discontinuous conduction

mode. The advantage of operating a power supply in DCM for low output current is the fixed switching frequency,

lower output inductance, and lower DC resistance on the inductor. Use the frequency shift and skip equations to

estimate the maximum switching frequency.

C BOOT

0.01 µF

LO

U1

220 µH

TPS54061

8 V to 40 V

R UVLO1

C IN

2.2 µF

8

2

7

3

6

4

255 kΩ

1

5.0 V

2

744 053 221

R COMP

R HS

CO

5

52.3 kΩ

35.7 kΩ

RT

R UVLO2

45.3 kΩ

1

C POLE

C COMP

220 pF

0.33 µF

1240 kΩ

22 µF

R LS

10 kΩ

Figure 38. DCM Application Schematic

8.2.2.1 Design Requirements

This example details the design of a low output current, fixed switching regulator design using ceramic output

capacitors. A few parameters must be known in order to start the design process. These parameters are typically

determined at the system level. For this example, follow the design parameters listed in Table 2.

Table 2. Design Parameters

PARAMETER

VALUE

Output voltage

5.0 V

Transient response 37.5 to 75-mA load step

ΔVOUT = 4%

Maximum output current

75 mA

Minimum output currert

1 mA

Input voltage

24 V nominal, 8 V to 40 V

Output voltage ripple

1 % of VOUT

Switching frequency

50 kHz

Start input voltage (rising VIN)

8V

Stop input voltage (falling VIN)

6.8 V

8.2.2.2 Detailed Design Procedure

The TPS54061-Q1 is designed for applications which require a fixed operating frequency and low output voltage

ripple at low output currents, thus, the TPS54061-Q1 does not have a pulse skip mode at light loads. Because

the device has a minimum controllable ON-time, there is an output current at which the power supply pulse skips.

To ensure that the supply does not pulse skip at output current of the application the inductor value needs to be

selected greater than a minimum value. The minimum inductance needed to maintain a fixed switching frequency

24

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

at the minimum load is calculated to be 227 µH using Equation 27. Because the equation is ideal and was

derived without losses, assume the minimum controllable light load ON-time, tonminll, is 180 ns. To maintain DCM

operation, the inductor value and output current need to stay below a maximum value. The maximum inductance

is calculated to be 250 µH using Equation 28. A 744053221 inductor from Würth Elektronik is selected. If CCM

operation is necessary, use the previous design procedure.

Use Equation 29, to make sure the minimum current limit on the high-side power switch is not exceeded at the

maximum output current. The peak current is calculated as 244 mA and is lower than the 350-mA current limit.

To determine the RMS current for the inductor and output capacitor, it is necessary to calculate the duty cycle.

The duty cycle, D1, for a step down regulator in DCM is calculated in Equation 30. D1 is the portion of the

switching cycle the high-side power switch is on, and is calculated to be 0.1345. D2 is the portion of the

switching cycle the low-side power switch is on, and is calculated to be 0.5111.

Using the Equation 32 and Equation 33, the RMS current of the inductor and output capacitor are calculated, to

be 0.1078 A and 0.0774 A, respectively. Select components that ratings exceed the calculated RMS values.

Calculate the output capacitance using the Equation 34 to Equation 36 and use the largest value. VRIPPLE is the

steady-state voltage ripple and ΔV is voltage change during a transient. A minimum of 7.5-µF capacitance is

calculated. Additional capacitance de-ratings for aging, temperature, and DC bias should be factored in, which

increases this minimum value. For this example, a 22-µF, 10-V X7R ceramic capacitor with 5-mΩ ESR is used.

To have a low output ripple power supply use a low ESR capacitor. Use Equation 37 to estimate the maximum

ESR for the output capacitor. Equation 38 and Equation 39 estimate the RMS current and capacitance for the

input capacitor. An RMS current of 38.7 mA and capacitance of 1.56 µF is calculated. A 2.2-µF, 100-V X7R

ceramic is used for this example.

æ V max - VOUT ö

t Onmin2

æ VINmax ö

x f sw

Lomin ³ ç IN

´

÷ ´ ç

÷

VOUT

2

IOmin

è

ø

è

ø

(27)

æ VOUT ö

1

æ V min - VOUT ö

LOmax £ ç IN

÷ ´

÷ ´ ç

f sw ´ IO

2

è

ø

è VINmin ø

(28)

æ 2 ´ VOUT ´ Iomax ´ (VINmax - VOUT ) ö

IL peak = ç

÷÷

ç

VINmax ´ LO ´ f sw

è

ø

æ 2 ´ VOUT ´ IO ´ LO ´ f sw

D1 = ç

ç

VIN ´ (VIN - VOUT )

è

ö

÷÷

ø

0.5

(29)

0.5

(30)

æ V - VOUT ö

D2 = ç IN

÷ ´ D1

VOUT

è

ø

(31)

æ D1 + D2 ö

IL rms = IL peak ´ ç

÷

3

è

ø

0.5

(32)

æ æ D1 + D2 ö

ICOrms = IL peak ´ ç ç

÷ çè

3

ø

è

(D1 + D2 )2 ö÷

4

0.5

÷

ø

(33)

æ D1 + D2 ö

I peak

CO 1 £ L

´ ç

÷

VRIPPLE

è 8 ´ fSW ø

CO 2 ³ LO ´

Co3 ³

RC

Io

(VOUT

2

- 0

2

+ DV )

(34)

2

- VOUT 2

(35)

IOUT

1

´

DVOUT fco

(36)

V

£ RIPPLE

IL peak

(37)

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

25

�TPS54061-Q1

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

æ

æ (D1)2

æ D1 ö

ç

ICINrms = IL peak ´ ç ç

ç è 3 ÷ø

ç 4

è

è

CIN ³

www.ti.com

öö

÷÷

÷÷

øø

0.5

(38)

æ 0.25 ö

IO

´ ç

÷

VINRIPPLE

è fSW ø

(39)

8.2.2.2.1 Closing the Feedback Loop

The method presented here is easy to calculate and includes the effect of the slope compensation that is internal

to the TPS54061-Q1. This method assumes the crossover frequency is between the modulator pole and the ESR

zero and the ESR zero is at least 10 times greater than the modulator pole. Once the output components are

determined, use the equations below to close the feedback loop. A current mode controlled power supply

operating in DCM has a transfer function which includes an ESR zero and pole as shown in Equation 40. To

calculate the current mode power stage gain, first calculate, Kdcm, the DCM gain, and Fm, the modulator gain,

using Equation 41 and Equation 42. Kdcm and Fm are 32.4 and 0.475, respectively. The location of the pole and

ESR zero are calculated using Equation 43 and Equation 44 . The pole and zero are 491 Hz and 2.8 MHz,

respectively. Use the lower value of Equation 45 and Equation 46 as a starting point for the crossover frequency.

Equation 45 is the geometric mean of the power stage pole and the ESR zero and Equation 46 is the mean of

power stage pole and the switching frequency. The crossover frequency is chosen as 5 kHz from Equation 46.

To determine the compensation resistor, RCOMP, use Equation 47. Assume the power stage transconductance,

gmps, is 1.0 A/V. The output voltage, VOUT, reference voltage, VREF, and amplifier transconductance, gmea, are

5.0 V, 0.8 V and 108 µA/V, respectively. RCOMP is calculated to be 38.3 kΩ; use the nearest standard value of

35.7 kΩ. Use Equation 48 to set the compensation zero to equal the modulator pole frequency. Equation 48

yields 290 nF for compensating capacitor CCOMP, and a 330 nF is used. Use the larger value of Equation 49 or

Equation 50 to calculate the CPOLE, which sets the compensation pole. Equation 50 yields 178-pF standard value

of 220 pF is selected.

s

1+

2 ´ p ´ f ZERO

Gdcm(s) » Fm ´ Kdcm ´

s

1+

2 ´ p ´ fPOLE

(40)

Kdcm =

(VIN

VOUT ´

2

´

D1

- VOUT )

æ

ö

ç

Rdc ÷÷

VIN ´ ç 2 +

- VOUT

VOUT ÷

ç

ç

IO ÷ø

è

gmps

Fm =

æ VIN - VOUT ö

ç

÷ + 0.380

è LO ´ f sw ø

V

æ

2 - OUT

ç

VIN

1

fPOLE (Hz) =

´ ç

VOUT

VOUT

ç

´ CO ´ 2 ´ p

ç1 - V

IO

IN

è

1

f ZERO (Hz) =

RC ´ CO ´ 2 ´ p

fCO1(Hz) =

fCO2 (Hz) =

RCOMP =

26

( f ZERO

( fSW

(41)

(42)

ö

÷

÷

÷

÷

ø

(43)

(44)

0.5

´ fPOLE )

(45)

0.5

´ fPOLE )

¦ co

Kdcm ´ Fm ´ ¦POLE

(46)

x

VOUT

VREF ´ gmea

Submit Documentation Feedback

(47)

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPS54061-Q1

�TPS54061-Q1

www.ti.com

SLVSBM7A – MARCH 2013 – REVISED JANUARY 2016

1

CCOMP =

CPOLE1

2 ´ p ´ RCOMP ´ Kdcm ´ Fm

(48)

R ´ CO

= C

RCOMP

(49)

1

RCOMP ´ fSW ´ p

CPOLE2 =

(50)

100

100

90

90

80

80

70

70

Efficiency (%)

Efficiency (%)

8.2.2.3 Application Curves

60

50

40

30

VIN

VIN

VIN

VIN

20

10

0

0

0.025

0.05

Load Current (A)

VOUT = 5 V

0.075

=

=

=

=

60

50

40

30

8V

12 V

24 V

36 V

10

0

0.001

0.1

100

90

90

80