Product

Folder

Sample &

Buy

Support &

Community

Tools &

Software

Technical

Documents

TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

TPS56221 4.5-V to 14-V Input, High-Current, Synchronous Buck SWIFT™ Converter

1 Features

3 Description

•

•

•

•

The TPS56221 device is a high-efficiency and highcurrent synchronous buck converter designed to

operate from a supply from 4.5 V to 14 V. The device

can produce an output voltage as low as 0.6 V at

loads up to 25 A. Integrated NexFET™ Power

MOSFETs provide a small footprint and ease of use.

1

•

•

•

•

•

•

•

•

4.5-V to 14-V Input Voltage Range

Incorporates Power Block Technology

Up to 25-A Output Current

Fixed-Frequency Options of 300 kHz, 500 kHz,

and 1 MHz

High-Side and Low-Side MOSFET RDS(on) Sensing

Programmable Soft-Start

600-mV Reference Voltage With 1% Accuracy

Voltage Mode Control with Feed-Forward

Supports Prebiased Output

Thermal Shutdown

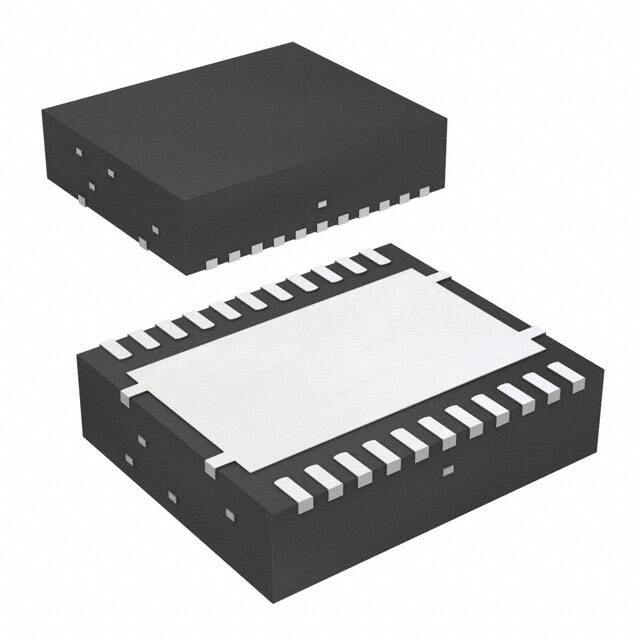

22-Pin 5-mm × 6-mm PQFN PowerPAD™

Package

For SWIFT™ Power Products Documentation,

see http://www.ti.com/swift

The device implements a voltage-mode control with

voltage feed-forward compensation that responds

instantly to input voltage change.

The TPS56221 is available in a thermally enhanced

22-pin PQFN (DQP) PowerPAD package.

The device offers design flexibility with a variety of

user programmable functions, including soft-start,

overcurrent protection (OCP) levels, and loop

compensation. OCP levels are programmed by a

single external resistor connected from the ILIM pin to

the circuit ground. During the initial power-on

sequence, the device enters a calibration cycle,

measures the voltage at the ILIM pin, and sets an

internal OCP voltage level. During operation, the

programmed OCP voltage level is compared to the

voltage drop across the low-side FET when it is on to

determine whether there is an overcurrent condition.

It then enters a shutdown/restart cycle until the fault

is removed.

2 Applications

•

•

Point-of-Load (POL) Power Modules

High-Density DC-DC Converters for Telecom and

Networking Applications

Device Information(1)

PART NUMBER

TPS56221

PACKAGE

BODY SIZE (NOM)

LSON-CLIP (22)

6.00 mm × 5.00 mm

(1) For all available packages, see the orderable addendum at

the end of the datasheet.

Simplified Application Schematic

TPS56221

VOUT

FB

VIN

COMP

PGD

VIN

BOOT

SW

EN/SS

VDD

VIN

VOUT

ILIM

BP

GND

SD

UDG-11045

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

Table of Contents

1

2

3

4

5

6

7

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

1

1

1

2

3

4

6.1

6.2

6.3

6.4

6.5

6.6

4

4

4

5

5

7

Absolute Maximum Ratings ......................................

ESD Ratings..............................................................

Recommended Operating Conditions.......................

Thermal Information ..................................................

Electrical Characteristics...........................................

Typical Characteristics ..............................................

Detailed Description ............................................ 10

7.1 Overview ................................................................. 10

7.2 Functional Block Diagram ....................................... 10

7.3 Feature Description................................................. 10

7.4 Device Functional Modes........................................ 14

8

Application and Implementation ........................ 15

8.1 Application Information............................................ 15

8.2 Typical Application ................................................. 15

9 Power Supply Recommendations...................... 22

10 Layout................................................................... 22

10.1 Layout Guidelines ................................................. 22

10.2 Layout Example .................................................... 22

11 Device and Documentation Support ................. 24

11.1

11.2

11.3

11.4

Device Support......................................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

24

24

24

24

12 Mechanical, Packaging, and Orderable

Information ........................................................... 24

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision C (January 2015) to Revision D

Page

•

Changed the datasheet Title From: "TPS56221 4.5-V to 14-V Input, High-Current, Synchronous Buck Converter"

To: "TPS56221 4.5-V to 14-V Input, High-Current, Synchronous Buck SWIFT™ Converter" .............................................. 1

•

Added Features: " For SWIFT™ Power Products Documentation..." .................................................................................... 1

Changes from Revision B (September 2012) to Revision C

•

Added Pin Configuration and Functions section, ESD Rating table, Feature Description section, Device Functional

Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device

and Documentation Support section, and Mechanical, Packaging, and Orderable Information section .............................. 1

Changes from Revision A (JUNE 2012) to Revision B

•

Page

Page

Corrected typographical error in Equation 6......................................................................................................................... 18

Changes from Original (MARCH 2011) to Revision A

Page

•

Added conditions to Electrical Characteristics table............................................................................................................... 5

•

Changed characteristic data conditions.................................................................................................................................. 6

•

Changed Figure 15................................................................................................................................................................. 9

•

Changed Figure 16................................................................................................................................................................. 9

•

Changed Figure 17................................................................................................................................................................. 9

•

Changed Figure 18................................................................................................................................................................. 9

•

Added Switching Node (SW) section.................................................................................................................................... 13

•

Changed replaced design example ..................................................................................................................................... 15

•

Added Layout Recommendations section ............................................................................................................................ 22

•

Added EVM Layout section .................................................................................................................................................. 22

2

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

5 Pin Configuration and Functions

DQP PACKAGE

PQFN-22

(TOP VIEW)

COMP

1

22

PGD

FB

2

21

EN/SS

GND

3

20

VDD

BOOT

4

19

BP

GND

5

18

ILIM

GND

(Thermal Pad)

SW

6

17

VIN

SW

7

16

VIN

SW

8

15

VIN

SW

9

14

VIN

SW

10

13

VIN

SW

11

12

VIN

Note: The thermal pad is also an electrical ground connection.

Pin Functions

PIN

I/O

DESCRIPTION

4

O

Gate drive voltage for the high-side FET. A 100-nF capacitor (typical) must be connected between this pin

and the SW pin. To reduce a voltage spike at SW, a BOOT resistor between 5 Ω to 10 Ω may be placed in

series with the BOOT capacitor to slow down turnon of the high-side FET.

BP

19

O

Output bypass for the internal regulator. Connect a low-ESR bypass ceramic capacitor of 1 µF or greater

from this pin to GND.

COMP

1

O

Output of the error amplifier and connection node for loop feedback components. Optionally, a 40.2-kΩ

resistor from this pin to GND sets switching frequency to 300 kHz instead of the default value of 500 kHz;

while a 13.3 kΩ resistor from this pin to GND sets switching frequency to 1 MHz.

NAME

NO.

BOOT

EN/SS

21

I

Logic-level input starts or stops the controller via an external user command. Allowing this pin to float turns

the controller on. Pulling this pin low disables the controller. This is also the soft-start programming pin. A

capacitor connected from this pin to GND programs the soft-start time. The capacitor is charged with an

internal current source of 10 µA. The resulting voltage ramp of this pin is also used as a second

noninverting input to the error amplifier after a 0.8 V (typical) level shift downwards. Output regulation is

controlled by the internal level shifted voltage ramp until that voltage reaches the internal reference voltage

of 600 mV. The voltage ramp of this pin reaches 1.4 V (typical).

FB

2

I

Inverting input to the error amplifier. In normal operation, the voltage on this pin is equal to the internal

reference voltage.

–

Ground reference for the device.

–

Ground reference for the device. This is also the thermal pad used to conduct heat from the device. This

connection serves two purposes. The first is to provide an electrical ground connection for the device. The

second is to provide a low thermal impedance path from the device die to the PCB. This pad should be

tied externally to a ground plane.

GND

3

5

GND

Thermal

Pad

ILIM

18

I

A resistor connected from this pin to GND sets the overcurrent threshold for the device (the low-side FET).

PGD

22

O

Open-drain power good output.

I

Switching node of the power conversion stage. Sense line for the adaptive anti-cross conduction circuitry.

Acts as the common connection for the flying high-side FET driver.

6

7

SW

8

9

10

11

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

3

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

Pin Functions (continued)

PIN

NAME

I/O

NO.

VDD

20

DESCRIPTION

I

Power input to the controller. A low-ESR bypass ceramic capacitor of 1 µF should be connected from this

pin close to GND.

I

Power input to the high-side FET.

12

13

14

VIN

15

16

17

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)

VDD, VIN

Voltage

MIN

MAX

–0.3

16.5

SW

–3

25

SW (< 100 ns pulse width, 10 µJ)

–5

UNIT

V

BOOT

–0.3

30

BOOT-SW (differential from BOOT to SW)

–0.3

7

COMP, PGOOD, FB, BP, EN/SS, ILIM

–0.3

7

Junction Temperature, TJ

–40

150

°C

Storage temperature, Tstg

–55

150

°C

(1)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other condition beyond those included under Recommended Operating

Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods of time may affect device reliability.

6.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

UNIT

±2000

Charged-device model (CDM), per JEDEC specification JESD22-C101 (2)

V

±1500

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

VDD

VIN Input voltage

4.5

14

V

TJ

Operating junction temperature

–40

125

°C

4

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

6.4 Thermal Information

TPS56221

THERMAL METRIC (1)

PQFN

UNIT

22 PINS

RθJA

Junction-to-ambient thermal resistance

34.6

RθJC(top)

Junction-to-case (top) thermal resistance

22.9

ψJT

Junction-to-top characterization parameter

0.6

ψJB

Junction-to-board characterization parameter

5.0

RθJC(bot)

Junction-to-case (bottom) thermal resistance

0.3

(1)

°C/W

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report (SPRA953).

6.5 Electrical Characteristics

–40°C ≤ TJ ≤ 125°C, VVDD = 12 V, all parameters at zero power dissipation (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

TJ = 25°C, 4.5 V ≤ VVDD ≤ 14 V

597

600

603

–40°C ≤ TJ ≤ 125°C,

4.5 V ≤ VVDD ≤ 14 V

594

600

606

UNIT

VOLTAGE REFERENCE

VFB

FB input voltage

mV

INPUT SUPPLY

VVDD

Input supply voltage range

14

V

IVDDSD

Shutdown supply current

VEN/SS = 0.2 V

4.5

80

120

µA

IVDDQ

Quiescent, nonswitching

Let EN/SS float, VFB = 1 V

2.5

5.0

mA

VUVLO

UVLO ON Voltage

4.0

4.3

V

VUVLO(HYS)

UVLO hysteresis

500

700

mV

V

ENABLE/SOFT-START

VIH

High-level input voltage, EN/SS

0.55

0.70

1.00

VIL

Low-level input voltage, EN/SS

0.27

0.30

0.33

V

ISS

Soft-start source current

8

10

12

µA

VSS

Soft-start voltage level – start of

ramp

0.4

0.8

1.3

V

6.2

6.5

6.8

V

70

125

mV

BP REGULATOR

VBP

Output voltage

IBP = 10 mA

VDO

Regulator dropout voltage, VVDD –

VBP

IBP = 25 mA, VVDD = 4.5 V

OSCILLATOR

fSW

Switching frequency

VRAMP

(1)

RCOMP = 40.2 kΩ,

4.5 V ≤ VVDD ≤ 14 V

270

300

330

kHz

RCOMP = open,

4.5 V ≤ VVDD ≤ 14 V

450

500

550

kHz

RCOMP = 13.3 kΩ,

4.5 V ≤ VVDD ≤ 14 V

0.8

0.95

1.1

MHz

VVDD/6.6

VVDD/6

VVDD/5.4

V

100

ns

Ramp amplitude

PWM

DMAX

(1)

tON(min)

(1)

(1)

Maximum duty cycle

fsw = 300 kHz, VFB = 0 V,

4.5 V ≤ VVDD ≤ 14 V

93%

fsw = 500 kHz, VFB = 0 V,

4.5 V ≤ VVDD ≤ 14 V

90%

fsw = 1 MHz, VFB = 0 V,

4.5 V ≤ VVDD ≤ 14 V

85%

Minimum controllable pulse width

Ensured by design. Not production tested

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

5

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

Electrical Characteristics (continued)

–40°C ≤ TJ ≤ 125°C, VVDD = 12 V, all parameters at zero power dissipation (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

Gain bandwidth product

10

24

Open loop gain

60

MAX

UNIT

ERROR AMPLIFIER

(1)

GBWP

AOL

(1)

MHz

dB

IIB

Input bias current (current out of

FB pin)

VFB = 0.6 V

IEAOP

Output source current

VFB = 0 V

1.5

mA

IEAOM

Output sink current

VFB = 1 V

1.5

mA

75

nA

POWER GOOD

VOV

Feedback upper voltage limit for

PGOOD

655

675

700

mV

VUV

Feedback lower voltage limit for

PGOOD

500

525

550

mV

VPGD-HYST

PGOOD hysteresis voltage at FB

30

45

mV

RPGD

PGOOD pull down resistance

VFB = 0 V, IFB = 5 mA

30

70

Ω

IPGDLK

PGOOD leakage current

550 mV < VFB < 655 mV,

VPGOOD = 5 V

10

20

µA

OUTPUT STAGE

RHI

High-side device resistance

TJ = 25°C, (VBOOT– VSW) = 5.5 V

4.5

6.5

mΩ

RLO

Low side device resistance

TJ = 25°C

1.9

2.7

mΩ

OVERCURRENT PROTECTION (OCP)

tPSSC(min)

tBLNKH

(1)

(1)

Minimum pulse time during short

circuit

250

Switch leading-edge blanking pulse

time (high-side detection)

150

ns

IOCH

OC threshold for high-side FET

TJ = 25°C, (VBOOT– VSW) = 5.5 V

IILIM

ILIM current source

TJ = 25°C

VOCLPRO (1)

Programmable OC range for low

side FET

TJ = 25°C

tOFF

OC retry cycles on EN/SS pin

45

54

65

10.0

12

100

4

A

µA

mV

Cycle

BOOT DIODE

VDFWD

Bootstrap diode forward voltage

IBOOT = 5 mA

0.8

V

145

ºC

20

ºC

THERMAL SHUTDOWN

TJSD

(1)

TJSDH

6

Junction shutdown temperature

(1)

Hysteresis

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

6.6 Typical Characteristics

Figure 13 to Figure 18 are measured on a 2.5 inch × 2.5 inch, 0.062 inch thick FR4 board with 4 layers and 2-oz. copper, a

0.32-µH output inductor and a DCR of 0.32 mΩ.

602

306

Switching Frequency (kHz)

FB Pin Reference Voltage (mV)

fSW = 300 kHz

601

600

599

598

597

596

305

304

303

302

301

595

594

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

VVDD = 4.5 V

VVDD = 12 V

300

−40 −25 −10

110 125

Figure 1. Reference Voltage vs. Junction Temperature

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

Figure 2. Switching Frequency vs. Junction Temperature

(300 kHz)

504

975

fSW = 500 kHz

fSW = 1 MHz

Switching Frequency (kHz)

Switching Frequency (kHz)

502

500

498

496

494

492

5

20 35 50 65 80

Junction Temperature (°C)

95

875

850

−40 −25 −10

725

700

675

650

625

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

Figure 5. EN Pin High-Level Threshold Voltage vs. Junction

Temperature

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

Figure 4. Switching Frequency vs. Junction Temperature (1

MHz)

EN Pin Low−Level Threshold Voltage (mV)

EN Pin High−Level Threshold Voltage (mV)

900

VVDD = 4.5 V

VVDD = 12 V

110 125

Figure 3. Switching Frequency vs. Junction Temperature

(500 kHz)

600

−40 −25 −10

925

VVDD = 4.5 V

VVDD = 12 V

490

488

−40 −25 −10

950

292.5

292.0

291.5

291.0

290.5

290.0

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

Figure 6. EN Pin Low-Level Threshold Voltage vs. Junction

Temperature

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

7

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

Typical Characteristics (continued)

82

2.44

80

2.43

Quiescent Current (mA)

Shutdown Current (µA)

Figure 13 to Figure 18 are measured on a 2.5 inch × 2.5 inch, 0.062 inch thick FR4 board with 4 layers and 2-oz. copper, a

0.32-µH output inductor and a DCR of 0.32 mΩ.

78

76

74

72

2.42

2.41

2.40

2.39

VVDD = 12 V

70

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

VVDD = 12 V

2.38

−40 −25 −10

110 125

975

10.4

950

10.3

10.2

10.1

10.0

9.9

9.8

9.7

925

900

875

850

825

800

775

5

20 35 50 65 80

Junction Temperature (°C)

95

725

−40 −25 −10

110 125

Figure 9. Soft-Start Source vs. Junction Temperature

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

Figure 10. Soft-Start Voltage Level vs. Junction

Temperature

2.5

5.5

5.0

4.5

4.0

VVDD = 4.5 V

VVDD = 12 V

3.5

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

Figure 11. High-Side On Resistance vs. Junction

Temperature

Low−Side On−Resistance (mΩ)

6.0

High−Side On−Resistance (mΩ)

110 125

750

9.6

−40 −25 −10

8

95

Figure 8. Quiescent Current vs. Junction Temperature

10.5

Soft−Start Voltage Level (mV)

Soft−Start Source Current (µA)

Figure 7. Shutdown Current vs. Junction Temperature

5

20 35 50 65 80

Junction Temperature (°C)

2.4

2.3

2.2

2.1

2.0

1.9

VVDD = 4.5 V

VVDD = 12 V

1.8

1.7

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

Figure 12. Low-Side On Resistance vs. Junction

Temperature

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

Typical Characteristics (continued)

Figure 13 to Figure 18 are measured on a 2.5 inch × 2.5 inch, 0.062 inch thick FR4 board with 4 layers and 2-oz. copper, a

0.32-µH output inductor and a DCR of 0.32 mΩ.

750

Power−Good Threshold Voltage (mV)

High−Side Overcurrent Threshold (A)

54

52

50

48

46

44

42

VVDD = 4.5 V

VVDD = 12 V

40

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

600

550

500

100

100

95

95

90

90

85

85

80

75

VOUT = 0.8 V

VOUT = 1.0 V

VOUT = 1.2 V

VOUT = 1.8 V

VOUT = 2.5 V

VOUT = 3.3 V

70

65

fSW = 500 kHz

VVIN = 12 V

TA = 25°C

60

55

50

0

5

10

15

Load Current (A)

20

50

25

Output Current (A)

25

0

10

20

30

40

50

60

70

Ambient Temperature (°C)

0

5

10

15

Load Current (A)

80

90

100

G001

15

VOUT = 0.8 V

VOUT = 1.0 V

VOUT = 1.2 V

VOUT = 1.8 V

VOUT = 2.5 V

VOUT = 3.3 V

10

0

0

G001

Figure 17. Output Current vs. Ambient Temperature

(VVIN = 12 V)

25

20

5

fDW = 500 kHz

VVIN = 12 V

20

Figure 16. Efficiency vs. Load Current (VVIN = 5 V)

25

0

fSW = 500 kHz

VVIN = 5 V

TA = 25°C

G001

30

5

VOUT = 0.8 V

VOUT = 1.0 V

VOUT = 1.2 V

VOUT = 1.8 V

VOUT = 2.5 V

VOUT = 3.3 V

70

55

15

110 125

75

60

20

95

80

30

10

5

20 35 50 65 80

Junction Temperature (°C)

65

Figure 15. Efficiency vs. Load Current (VVIN = 12 V)

VOUT = 0.8 V

VOUT = 1.0 V

VOUT = 1.2 V

VOUT = 1.8 V

VOUT = 2.5 V

VOUT = 3.3 V

VOV

VUV

Figure 14. Power Good Threshold Voltage vs. Junction

Temperature

Efficiency (%)

Efficiency (%)

650

450

−40 −25 −10

110 125

Figure 13. High-Side Overcurrent Threshold vs. Junction

Temperature

Output Current (A)

700

10

20

30

40

50

60

70

Ambient Temperature (°C)

fSW = 500 kHz

VVIN = 5 V

80

90

100

G001

Figure 18. Output Current vs. Ambient Temperature

(VVIN = 5 V)

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

9

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

7 Detailed Description

7.1 Overview

The TPS56221 is a 25-A high-performance synchronous buck converter with two integrated N-channel NexFET

power MOSFETs. The device implements a voltage-mode control with voltage feed-forward compensation that

responds instantly to input voltage change. Prebias capability eliminates concerns about damaging sensitive

loads.

7.2 Functional Block Diagram

+

10 mA

Soft Start

SS

0.6 VREF + 12.5%

SS

EN/SS

+

SD

Fault

Controller

Clock

6-V

Regulator

VDD

BP

+

Calibration

Circuit

Clock

Oscillator

FB

OC

PWM

Anti-Cross

Conduction

and

Pre-Bias

Circuit

SW

BP

+

10 mA

0.6 VREF

SS

BOOT

VIN

PWM

Logic

+

0.6 VREF –12.5%

0.6

VREF

SD

References

BP

COMP

BP

FB

Thermal

Shutdown

750 kW

PGOOD

OC

Threshold

Setting

ILIM

Fault Controller

TPS56221

PAD

OC

UDG-11046

GND

7.3 Feature Description

7.3.1 Voltage Reference

The 600-mV bandgap cell is internally connected to the noninverting input of the error amplifier. The reference

voltage is trimmed with the error amplifier in a unity gain configuration to remove amplifier offset from the final

regulation voltage. The 1% tolerance on the reference voltage allows the user to design a very accurate power

supply.

10

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

Feature Description (continued)

Input Voltage (V)

2.0

1.6

VEN/SS

Calibration

Time(1.9 ms)

1.3 V

1.2

0.8

0.7 V

0.4

VSS_INT

0

Time (ms)

Figure 19. Start-Up Sequence and Timing

7.3.2 Enable Functionality, Start-Up, Sequence, and Timing

After input power is applied, an internal 40-μA current source begins to charge the soft-start capacitor connected

from EN/SS to GND. When the voltage across that capacitor increases to 0.7 V, it enables the internal BP

regulator followed by a calibration. Total calibration time is approximately 1.9 ms. See Figure 19. During the

calibration, the device performs the following two functions.

7.3.2.1 COMP Pin Impedance Sensing

The device samples the impedance at the COMP pin and determines the appropriate operating switching

frequency. If there is no resistor connected from the COMP pin to GND, the switching frequency is set to the

default value of 500 kHz. If a resistor of 40.2 kΩ ± 10% is connected from the COMP pin to GND, the switching

frequency is set to 300 kHz. Alternatively, if a resistor of 13.3 kΩ ± 10% is connected from the COMP pin to

GND, the switching frequency is set to 1 MHz.

After a 1.1-ms time period, the COMP pin is then brought low for 0.8 ms. This ensures that the feedback loop is

preconditioned at start-up and no sudden output rise occurs at the output of the converter when it is allowed to

start switching.

7.3.2.2 Overcurrent Protection (OCP) Setting

The device sources 10 μA (typical) to the resistor connected from the ILIM pin to GND. The voltage developed

across that resistor multiplied by a factor of 2 is then sampled and latched off internally as the OCP trip level for

the low-side FET until one cycles the input or toggles the EN/SS.

The voltage at EN/SS is internally clamped to 1.3 V before and/or during calibration to minimize the discharging

time once calibration is complete. The discharging current is from an internal current source of 140 μA and it

pulls the voltage down to 0.4 V. It then initiates the soft-start by charging up the capacitor using an internal

current source of 10 μA. The resulting voltage ramp on this pin is used as a second noninverting input to the

error amplifier after an 800 mV (typical) downward level-shift; therefore, the actual soft-start does not take place

until the voltage at this pin reaches 800 mV.

If the EN/SS pin is left floating, the controller starts automatically. EN/SS must be pulled down to less than 270

mV to ensure that the chip is in shutdown mode.

7.3.3 Soft-Start Time

The soft-start time of the TPS56221 is user programmable by selecting a single capacitor. The EN/SS pin

sources 10 μA to charge this capacitor. The actual output ramp-up time is the amount of time that it takes for the

10 μA to charge the capacitor through a 600 mV range. There is some initial lag due to calibration and an offset

(800 mV) from the actual EN/SS pin voltage to the voltage applied to the error amplifier.

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

11

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

Feature Description (continued)

The soft-start is accomplished in a closed-loop, meaning that the error amplifier controls the output voltage at all

times during the soft-start period and the feedback loop is never open as occurs in duty cycle limit soft-start

schemes. The error amplifier has two noninverting inputs, one connected to the 600-mV reference voltage, and

the other connected to the offset EN/SS pin voltage. The lower of these two voltages is what the error amplifier

controls the FB pin to. As the voltage on the EN/SS pin ramps up past approximately 1.4 V (800 mV offset

voltage plus the 600 mV reference voltage), the 600-mV reference voltage becomes the dominant input and the

converter has reached its final regulation voltage.

The capacitance required for a given soft-start ramp time for the output voltage is calculated in Equation 1.

æI

ö

CSS = ç SS ÷ ´ tSS

è VFB ø

where

•

•

•

•

CSS is the required capacitance on the EN/SS pin (nF)

ISS is the soft-start source current (10 μA)

VFB is the feedback reference voltage (0.6 V)

tSS is the desired soft-start ramp time (ms)

(1)

7.3.4 Oscillator

The oscillator frequency is internally fixed at 500 kHz if there is no resistor connected from COMP pin to GND.

Optionally, a 40.2-kΩ resistor from the COMP pin to GND sets the frequency to 300 kHz. Alternatively, a 13.3-kΩ

resistor from COMP pin GND sets the frequency to 1 MHz.

7.3.5 Overcurrent Protection (OCP)

Programmable OCP level at ILIM is from 6 mV to 50 mV. With a scale factor of 2, the actual OC trip point across

the low-side FET is in the range of 12 mV to 100 mV.

If the voltage drop across ROCSET reaches 300 mV during calibration (No ROCSET resistor included), it disables

OC protection. Once disabled, there is no low-side or high-side current sensing.

OCP level for the high-side FET is fixed at 54 A (typical). The high-side OCP provides pulse-by-pulse current

limiting.

OCP sensing for the low-side FET is a true inductor valley current detection, using sample and hold. Equation 2

can be used to calculate ROCSET:

æ

æ I

öö

ROCSET = ç IOUT(max ) - ç P-P ÷ ÷ ´ 95 + 62.5

è 2 øø

è

where

•

•

•

IP-P is the peak-to-peak inductor current (A)

IOUT(max) is the trip point for OCP (A)

ROCSET is the resistor used for setting the OCP level (Ω)

(2)

An overcurrent (OC) condition is detected by sensing voltage drop across the low-side FET and across the highside FET. If the voltage drop across either FET exceeds OC threshold, a count increments one count. If no OC

condition is detected on either FET, the fault counter decrements by one counter. If three OC pulses are

summed, a fault condition is declared which cycles the soft-start function in a hiccup mode. Hiccup mode is

defined as four dummy soft-start time-outs followed by a real one if overcurrent condition is encountered during

normal operation; or five dummy soft-start time-outs followed by a real one if overcurrent condition occurs from

the beginning during start. This cycle continues indefinitely until the fault condition is removed.

12

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

Feature Description (continued)

7.3.6 Switching Node (SW)

The SW pin connects to the switching node of the power conversion stage. It acts as the return path for the highside gate driver. When configured as a synchronous buck stage, the voltage swing on SW normally traverses

from below ground to well above the input voltage. Parasitic inductance in the high-side FET and the output

capacitance (COSS) of both power FETs form a resonant circuit that can produce high frequency ( > 100 MHz)

ringing on this node. The voltage peak of this ringing, if not controlled, can be significantly higher than the input

voltage. Ensure that the peak ringing amplitude does not exceed the absolute maximum rating limit for the pin.

In many cases, a series resistor and capacitor snubber network connected from the switching node to PGND can

be helpful in damping the ringing and decreasing the peak amplitude. Provide provisions for snubber network

components in the layout of the printed circuit board. If testing reveals that the ringing amplitude at the SW pin

exceeds the limit, then include snubber components.

Placing a BOOT resistor with a value from 5 Ω to 10 Ω in series with the BOOT capacitor slows down the turnon

of the high-side FET and can help to reduce the peak ringing at the switching node.

7.3.7 Input Undervoltage Lockout (UVLO)

The TPS56221 has fixed input UVLO. In order for the device to turn on, the following conditions must be met:

• The EN/SS pin voltage must be greater than VIH

• The input voltage must exceed UVLO on voltage VUVLO

The UVLO has a minimum of 500 mV hysteresis built-in.

7.3.8 Prebias Start-Up

The TPS56221 contains a unique circuit to prevent current from being pulled from the output during start-up in

the condition the output is prebiased. There are no PWM pulses until the internal soft-start voltage rises above

the error amplifier input (FB pin), if the output is prebiased. Once the soft-start voltage exceeds the error amplifier

input, the controller slowly initiates synchronous rectification by starting the synchronous rectifier with a narrow

on time. It then increments the on-time on a cycle-by-cycle basis until it coincides with the time dictated by (1–D),

where D is the duty cycle of the converter.

This approach prevents the sinking of current from a prebiased output, and ensures the output voltage start-up

and ramp to regulation is smooth and controlled.

7.3.9 Power Good

The TPS56221 provides an indication that output is good for the converter. This is an open-drain signal and pulls

low when any condition exists that would indicate that the output of the supply might be out of regulation. These

conditions include:

• VFB is more than ±12.5% from nominal

• soft-start function is active

• a short-circuit condition has been detected

NOTE

When there is no power to the device, PGOOD cannot pull close to GND if an auxiliary

supply is used for the power good indication. In this case, a built-in resistor connected

from drain to gate on the PGOOD pulldown device makes the PGOOD pin look

approximately like a diode to GND.

7.3.10 Thermal Shutdown

If the junction temperature of the device reaches the thermal shutdown limit of 145°C, both high-side FET and

low-side FET are kept off. When the junction cools to the required level (125°C typical), the PWM initiates soft

start as during a normal power-up cycle.

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

13

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

7.4 Device Functional Modes

The TPS56221 devices operate in continuous conduction mode (CCM) at a fixed frequency, regardless of the

output current. For the first 128 switching cycles, the low-side MOSFET on-time is slowly increased to prevent

excessive current sinking in the event the device is started with a prebiased output. Following the first 128

switching cycles, the low-side MOSFET and the high-side MOSFET on-times are fully complementary.

14

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component

specification, and TI does not warrant its accuracy or completeness. TI’s customers are

responsible for determining suitability of components for their purposes. Customers should

validate and test their design implementation to confirm system functionality.

8.1 Application Information

The TPS56221 is highly integrated synchronous step-down DC-DC converters. The device is used to convert a

higher DC input voltage (4.5 V to 14 V recommended) to a lower DC output voltage (as low as 0.6 V), with a

maximum output current of 25 A, for a variety of applications. Use the following design procedure to select key

component values for this device.

8.2 Typical Application

This design example describes a 25-A, 12-V to 1.0-V design using the TPS56221 high-current integrated buck

converter. The system specifications are listed in Table 1.

TPS56221

VOUT

FB

VIN

COMP

PGD

VDD

VIN

BOOT

SW

EN/SS

VIN

VOUT

ILIM

BP

GND

SD

UDG-11045

Figure 20. Typical Application Schematic

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

15

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

+

Figure 21. Design Example Schematic

16

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

8.2.1 Design Requirements

Table 1. Design Example Parameters

PARAMETER

TEST CONDITIONS

VIN

Input voltage

VIN(ripple)

Input ripple

IOUT = 25 A

VOUT

Output voltage

0 A ≤ IOUT ≤ 25 A

Line regulation

8 V ≤ VIN ≤ 14 V

Load regulation

0 A ≤ IOUT ≤ 25 A

VP-P

Output ripple

IOUT= 25 A

VOVER

Output overshoot

ITRAN = 10 A

VUNDER

Output undershoot

ITRAN = 10 A

IOUT

Output current

8 V ≤ VIN ≤ 14 V

tSS

Softstart time

VIN = 12 V

ISCP

Short circuit current trip point

η

Efficiency

fSW

Switching frequency

MIN

TYP

8.0

0.98

1.00

MAX

UNIT

14

V

0.2

V

1.02

V

0.1%

1.0%

20

mV

100

mV

100

0

mV

25

2.0

32

VIN = 12 V, IOUT = 25 A

A

ms

A

87%

500

kHz

8.2.2 Detailed Design Procedure

Table 2. List of Materials for TPS56221 Design Example

REFERENCE

DESiGNATOR

QTY

C1, C2, C3, C4

4

22 µF

C5, C11

2

1.0 µF

C6

0

100 µF

Capacitor, Ceramic, 16 Vdc, ±20%

C7, C8, C9,

C10, C19

5

100 µF

C12

1

C13

1

C14

C15, C18

VALUE

DESCRIPTION

SIZE

PART NUMBER

MANUFACTURER

Capacitor, Ceramic, 25 V, X5R, 20%

1210

Std

Std

Capacitor, Ceramic, 25 V, X7R, 20%

0805

Std

Std

Code D8

Std

EEEFP1C101AP

Capacitor, Ceramic, 6.3 V, X5R, 20%

1210

Std

Std

4.7 µF

Capacitor, Ceramic, 10 V, X5R, 20%

0805

Std

Std

33 nF

Capacitor, Ceramic, 16 V, X7R, 20%

0603

Std

Std

1

100 nF

Capacitor, Ceramic, 16V, X7R, 20%

0402

Std

Std

2

2200 pF

Capacitor, Ceramic, 50 V, X7R, 10%

0603

Std

Std

C16

1

100 pF

Capacitor, Ceramic, 50 V, C0G, 10%

0603

Std

Std

C17

1

680 pF

Capacitor, Ceramic, 50 V, C0G, 10%

0603

Std

Std

C20, C21

0

100 µF

Capacitor, Ceramic, 6.3 V, X5R, 20%

1210

Std

Std

ED120/4DS

J1, J2

2

Terminal Block, 4-pin, 15-A, 5.1 mm

0.80 x

0.35 inch

J3

1

Header, Male 2-pin, 100 mil spacing

0.100 inch

x2

PEC02SAAN

L1

1

320 nH

Inductor, 320 nH, 41 A, 0.32 mΩ

0.530 x

0.510 inch

PA2202-321NL

Pulse

R1

1

1.78 kΩ

Resistor, Chip, 1/16W, 1%

0603

Std

Std

R2

1

5.10 Ω

Resistor, Chip, 1/16W, 1%

0603

Std

Std

R3

1

7.87 kΩ

Resistor, Chip, 1/16W, 1%

0603

Std

Std

R4

1

20.5 kΩ

Resistor, Chip, 1/16W, 1%

0603

Std

Std

49.9Ω

Resistor, Chip, 1/16W, 1%

0603

R5

R6

1

1.00 kΩ

Resistor, Chip, 1/16W, 1%

0603

Std

Std

R7

1

30.1 kΩ

Resistor, Chip, 1/16W, 1%

0603

Std

Std

R8

1

0Ω

Resistor, Chip, 1/16W, 1%

0603

R9

1

1Ω

Resistor, Chip, 1/16W, 1%

0603

R10

1

100 kΩ

Resistor, Chip, 1/16W, 1%

0603

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

17

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

Table 2. List of Materials for TPS56221 Design Example (continued)

REFERENCE

DESiGNATOR

QTY

TP1, TP3, TP11

3

TP2, TP4, TP8,

TP9, TP12

VALUE

DESCRIPTION

SIZE

PART NUMBER

Test Point, Red, Thru Hole

0.125 x

0.125 inch

5010

5

Test Point, Black, Thru Hole

0.125 x

0.125 inch

5011

TP5, TP6

2

Test Point, Yellow, Thru Hole

0.125 x

0.125 inch

5014

TP7, TP10

2

Test Point, White, Thru Hole

0.125 x

0.125 inch

5012

U1

1

4.5-V to 14-V Input, 25-A, synchronous

buck converter

6 × 5 mm

TPS56221DQP

QFN-22

MANUFACTURER

TI

8.2.2.1 Switching Frequency Selection

To achieve a balance between small size and high efficiency for this design, use switching frequency of 500 kHz.

8.2.2.2 Inductor Selection

Synchronous buck power inductors are typically sized for between approximately 20% and 40% peak-to-peak

ripple current (IP-P).

Using this target ripple current, the required inductor size can be calculated as shown in Equation 3.

VIN(max) - VOUT

V

1

14 V - 1.0 V 1.0 V

1

L»

´ OUT ´

=

´

´

= 186nH

0.3 ´ IOUT

VIN(max) fSW

0.3 ´ 25 A

14 V 500kHz

(3)

Selecting a standard 320-nH inductor value, IP-P = 5.8 A.

The RMS current through the inductor is approximated in Equation 4.

2

IL(rms ) =

(I ( ) ) + (

L avg

2

1 ´ I

RIPPLE

12

(

)

)=

(IOUT )2 +

(

2

1 ´ I

P -P

12

(

)

)=

(25 )2 +

(

1 ´

12

(5.8 )2

)= 25.06 A

(4)

8.2.2.3 Output Capacitor Selection

The selection of the output capacitor is typically driven by the output transient response. For applications with

VIN(min) > 2 x VOUT, use overshoot to calculate the minimum output capacitance and the equation is shown in

Equation 5.

COUT(min ) =

(ITRAN )2 ´ L

VOUT ´ VOVER

=

(10 )2 ´ 320nH

1.0 ´ 100mV

= 320 mF

(5)

For applications where VIN(min) < 2 × VOUT, use undershoot to calculate minimum output capacitance. The

equation is shown in Equation 6.

COUT(min ) =

(ITRAN )2 ´ L

(VIN - VOUT )´ VUNDER

(6)

To meet the low ESR and high-capacitance requirements of this design, five 100-µF, 1210 ceramic capacitors

are selected. With a minimum capacitance, the maximum allowable ESR is determined by the maximum ripple

voltage and is approximated by Equation 7.

æ

ö

IP-P

æ

ö

5.8A

VRIPPLE - ç

÷ 20mV - ç

÷

VRIPPLE - VRIPPLE(COUT)

´

´

8

C

f

OUT

SW ø

è

è 8 ´ 500 mF ´ 500kHz ø = 2.9mW

=

=

ESRCOUT(max ) =

IP-P

IP-P

5.8 A

(7)

18

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

8.2.2.4 Inductor Peak Current Rating

With output capacitance, it is possible to calculate the charge current during start-up and determine the minimum

saturation current rating for the inductor. The start-up charging current is approximated by Equation 8.

V

´ COUT 1.0 V ´ 500 mF

ICHARGE = OUT

=

= 0.25 A

tSS

2ms

(8)

The peak current in the inductor IL(peak) is approximated by Equation 9.

IL(peak ) = IOUT(max) + (12 ´ IRIPPLE )+ ICHARGE = 25 A + (12 ´ 5.8A )+ 0.25 A = 28.2 A

(9)

With the short circuit current trip point IOUT(max) set at 32 A, the maximum allowable peak current IL(peak max) is

IL(peak max ) = IOUT(max) + (12 ´ IRIPPLE ) = 30 A + (12 ´ 5.8A ) = 32.9 A

(10)

The selection of output capacitor meets the maximum allowable peak current requirement.

Table 3. Inductor Requirements Summary

PARAMETER

VALUE

UNIT

L

Inductance

320

nH

IL(rms)

RMS current (thermal rating)

25.1

A

IL(peak max)

Peak current (saturation rating)

32.9

A

The PA0513.321NLT, 320-nH, 0.32-mΩ, 41-A inductor is selected.

8.2.2.5 Input Capacitor Selection

The input voltage ripple is divided between capacitance and ESR. For this design VIN_RIPPLE(CAP) = 150 mV and

VIN_RIPPLE(ESR) = 50 mV. The minimum capacitance and maximum ESR are estimated in Equation 11.

IOUT ´ VOUT

25 ´ 1.0V

=

= 41.7 mF

CIN(min) =

VIN _ RIPPLE(CAP) ´ VIN(min) ´ fSW 150mV ´ 8 V ´ 500kHz

(11)

ESRCIN(max ) =

VIN _ RIPPLE(ESR)

IOUT + 12 (IP-P )

=

50mV

= 1.8mW

25A + 12 (5.8A )

(12)

The RMS current in the input capacitors is estimated by Equation 13.

IRMS(cin ) = ILOAD ´ D ´ (1 - D ) = 25 A ´

1 æ

1ö

´ ç 1 - ÷ = 8.3 ARMS

8 è 8ø

(13)

Four 1210, 22-µF, 25-V, X5R ceramic capacitors with about 2.5-mΩ of ESR and a 2.5-A RMS current rating are

selected. Higher voltage capacitors are selected to minimize capacitance loss at the DC bias voltage to ensure

the capacitors will have sufficient capacitance at the working voltage while a 1.0-µF capacitor in smaller case

size is used to reduce high frequency noise from the MOSFET switching.

8.2.2.6 Boot-Strap Capacitor (C14)

The bootstrap capacitor maintains power to the high-side driver during the high-side switch ON time. Per the

requirements of the integrated MOSFET, CBOOT is 100 nF with a minimum 10-V rating.

8.2.2.7 Boot-Strap Resistor (R2)

The bootstrap resistor slows the rising edge of the SW voltage to reduce ringing and improve EMI. Per the

datasheet recommendation a 5.10-Ω resistor is selected.

8.2.2.7.1 RC Snubber (R9 and C18)

To effectively limit the switch node ringing, a 1.0-Ω resistor and a 2200-pF capacitor are selected.

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

19

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

8.2.2.8 VDD Bypass Capacitor (C11)

In accordance with pin terminations recommended in the data sheet, VDD is bypassed to GND with a 1.0-µF

capacitor.

8.2.2.9 BP5 Bypass Capacitor (C12)

Per the datasheet recommended pin terminations, BP5 is bypassed to GND with at least 1.0-µF capacitor. For

additional filtering and noise immunity a 4.7-µF capacitor is selected.

8.2.2.10 Soft-Start Capacitor (C13)

The soft-start capacitor provides a constant ramp voltage to the error amplifier to provide controlled, smooth

start-up. The soft-start capacitor is sized using Equation 14.

I

10 mA

CSS = SS ´ tSS =

´ 2.0ms = 33nF

VFB

0.6 V

(14)

8.2.2.11 Current Limit (R1)

The TPS56221 uses the negative drop across the internal low-side FET at the end of the OFF-time to measure

the valley of the inductor current. Allowing for a minimum of 30% over maximum load, the programming resistor

is selected using Equation 15.

æ

æ

æI

öö

æ 5.8 A ö ö

ROCSET = 95 ´ ç IOUT(max) - ç P-P ÷ ÷ + 62.5 W = 95 ´ ç 30 A - ç

÷ ÷ + 62.5 W = 2.83 kW

2

è 2 øø

è

øø

è

è

(15)

A standard 2.87-kΩ resistor is selected from the E-48 series.

8.2.2.12 Feedback Divider (R4, R7)

The TPS56221 converter uses a full operational amplifier with an internally fixed 0.600-V reference. R4 is

selected between 10 kΩ and 50 kΩ for a balance of feedback current and noise immunity. With R4 set to

20.5 kΩ, The output voltage is programmed with a resistor divider given by Equation 16.

VFB ´ R4

0.600 V ´ 20.5kW

R7 =

=

= 30.8kW

(VOUT - VFB ) 1.0 V - 0.600 V

(16)

A standard 30.1-kΩ resistor is selected from the E-48 series.

8.2.2.13 Compensation (C15, C16, C17, R3, R6)

Using the TPS40k Loop Stability Tool for 50 kHz of bandwidth and 60 degrees of phase margin with an R4 value

of 20.5 kΩ, the following values are obtained.

• C17 = C_1 = 680 pF

• C15 = C_2 = 2200 pF

• C16 = C_3 = 100 pF

• R6 = R_2 = 1.00 kΩ

• R3 = R_3 = 7.87 kΩ

20

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

8.2.3 Application Curves

40

200

90

30

160

85

20

120

10

80

0

40

80

75

70

65

60

fSW = 500 kHz

VVIN = 5 V

TA = 25°C

55

50

0

5

20

0

−20

−40

−30

−80

−50

25

−60

1000

G001

Figure 22. Efficiency vs Load Current

−120

−40

VIN = 8 V

VIN = 12 V

VIN = 14 V

10

15

Load Current (A)

−10

Phase (°)

95

Gain (dB)

Efficiency (%)

Output voltage 12 V to 1.0 V, input current 0 A to 25 A.

Gain

Phase

−160

10000

Frequency (kHz)

100000

−200

400000

G001

Figure 23. Loop Response 51 kHz Bandwidth, 48° Phase

Margin

Figure 24. TPS56221 Design Example Output Ripple 20 mV/div, 1.0 µs/div, 20 MHz Bandwidth, AC Coupled

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

21

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

9 Power Supply Recommendations

The TPS56221 devices are designed to operate from an input voltage supply between 4.5 V and 14 V. This

supply must be well regulated. These devices are not designed for split-rail operation. The VIN and VDD

terminals must be the same potential for accurate high-side short circuit protection. Proper bypassing of input

supplies and internal regulators is also critical for noise performance, as is PCB layout and grounding scheme.

See the recommendations in Layout Guidelines.

10 Layout

10.1 Layout Guidelines

•

Place input capacitors next to the VIN pin and on the same side as the device. Use wide and short traces or

copper planes for the connection from the VIN pin to the input capacitor and from the input capacitor to the

power pad of the device.

Place the BP decoupling capacitor close to the BP pin and on the same side as the device in order to avoid

the use of vias. Use wide and short traces for the connection from the BP pin to the capacitor and from the

capacitor to the power pad. If vias are not evitable, use at least three vias to reduce the parasitic inductance.

Include a Kelvin VDD connection, or separate from VIN connection (bypass input capacitors); add a

placeholder for a filter resistor between the VDD pin and the input bus. Place the VDD decoupling capacitor

near the VDD pin and on the same side as the device to avoid the use of vias. Use wide and short traces for

the connection from the VDD pin to the capacitor and from the capacitor to the power pad of the device. If

vias are not avoidable, use at least three vias to reduce the parasitic inductance.

Maintain the FB trace away from BOOT and SW traces.

Minimize the area of switch node.

Use a single ground. Do not use separate signal and power ground.

Use 3 × 7 thermal vias as suggested in Land Pattern Data in Mechanical, Packaging, and Orderable

Information.

•

•

•

•

•

•

10.2 Layout Example

The TPS56221EVM layout is shown in Figure 25 through Figure 30 for reference.

TEXAS

I NSTRUMENTS

Figure 25. TPS56221EVM Top Assembly Drawing

(Top view)

22

Figure 26. TPS56221EVM Bottom Assembly

Drawing (Bottom view)

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�TPS56221

www.ti.com

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

Layout Example (continued)

Figure 27. TPS56221EVM Top Copper (Top View)

Figure 28. TPS56221EVM Internal 1 (Top View)

Figure 29. TPS56221EVM Internal 2 (Top View)

Figure 30. TPS56221EVM Bottom Copper (Top

View)

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

23

�TPS56221

SLUSAH5D – MARCH 2011 – REVISED FEBRUARY 2016

www.ti.com

11 Device and Documentation Support

11.1 Device Support

11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT

CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES

OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER

ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

11.2 Trademarks

PowerPAD, SWIFT, NexFET are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most

current data available for the designated devices. This data is subject to change without notice and revision of

this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

24

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: TPS56221

�PACKAGE OPTION ADDENDUM

www.ti.com

20-Aug-2016

PACKAGING INFORMATION

Orderable Device

Status

(1)

Package Type Package Pins Package

Drawing

Qty

Eco Plan

Lead/Ball Finish

MSL Peak Temp

(2)

(6)

(3)

Op Temp (°C)

Device Marking

(4/5)

TPS56221DQPR

ACTIVE

LSON-CLIP

DQP

22

2500

Pb-Free (RoHS

Exempt)

CU NIPDAU | CU SN

Level-2-260C-1 YEAR

-40 to 125

TPS56221

TPS56221DQPT

ACTIVE

LSON-CLIP

DQP

22

250

Pb-Free (RoHS

Exempt)

CU NIPDAU | CU SN

Level-2-260C-1 YEAR

-40 to 125

TPS56221

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability

information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that

lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight

in homogeneous material)

(3)

MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4)

There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5)

Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation

of the previous line and the two combined represent the entire Device Marking for that device.

(6)

Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish

value exceeds the maximum column width.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information

provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.

TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

Addendum-Page 1

Samples

�PACKAGE OPTION ADDENDUM

www.ti.com

20-Aug-2016

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Addendum-Page 2

�PACKAGE MATERIALS INFORMATION

www.ti.com

5-Jun-2019

TAPE AND REEL INFORMATION

*All dimensions are nominal

Device

Package Package Pins

Type Drawing

SPQ

Reel

Reel

A0

Diameter Width (mm)

(mm) W1 (mm)

B0

(mm)

K0

(mm)

P1

(mm)

W

Pin1

(mm) Quadrant

TPS56221DQPR

LSONCLIP

DQP

22

2500

330.0

15.4

5.3

6.3

1.8

8.0

12.0

Q1

TPS56221DQPR

LSONCLIP

DQP

22

2500

330.0

12.4

5.3

6.3

1.8

8.0

12.0

Q1

TPS56221DQPT

LSONCLIP

DQP

22

250

330.0

15.4

5.3

6.3

1.8

8.0

12.0

Q1

TPS56221DQPT

LSONCLIP

DQP

22

250

180.0

12.4

5.3

6.3

1.8

8.0

12.0

Q1

Pack Materials-Page 1

�PACKAGE MATERIALS INFORMATION

www.ti.com

5-Jun-2019

*All dimensions are nominal

Device

Package Type

Package Drawing

Pins

SPQ

Length (mm)

Width (mm)

Height (mm)

TPS56221DQPR

LSON-CLIP

DQP

22

2500

336.6

336.6

41.3

TPS56221DQPR

LSON-CLIP

DQP

22

2500

367.0

367.0

35.0

TPS56221DQPT

LSON-CLIP

DQP

22

250

336.6

336.6

41.3

TPS56221DQPT

LSON-CLIP

DQP

22

250

210.0

185.0

35.0

Pack Materials-Page 2

����IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE

DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS”

AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY

IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD

PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate

TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable

standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you

permission to use these resources only for development of an application that uses the TI products described in the resource. Other

reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third

party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims,

damages, costs, losses, and liabilities arising out of your use of these resources.

TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on

ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable

warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2019, Texas Instruments Incorporated

�