TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

DUAL-OUTPUT, LOW DROPOUT VOLTAGE REGULATORS

WITH INTEGRATED SVS FOR SPLIT VOLTAGE SYSTEMS

FEATURES

1

• Dual Output Voltages for Split-Supply

Applications

• Independent Enable Functions (See Part

Number TPS707xx for Sequenced Outputs)

• Output Current Range of 250 mA on Regulator

1 and 125 mA on Regulator 2

• Voltage Options: 3.3-V/2.5-V, 3.3-V/1.8-V,

3.3-V/1.5-V, 3.3-V/1.2-V, and Dual Adjustable

Outputs

• Open Drain Power-On Reset with 120-ms Delay

• Open Drain Power Good for Regulator 1 and

Regulator 2

• Ultralow 190-µA (typ) Quiescent Current

• 1-µA Input Current During Standby

• Low Noise: 65 µVRMS Without Bypass

Capacitor

• Quick Output Capacitor Discharge Feature

• One Manual Reset Input

• 2% Accuracy Over Load and Temperature

• Undervoltage Lockout (UVLO) Feature

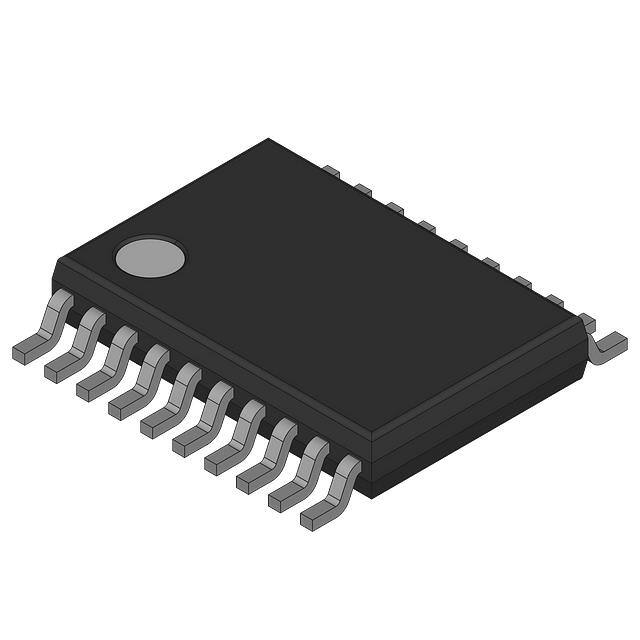

• 20-Pin PowerPAD™ TSSOP Package

• Thermal Shutdown Protection

23

DESCRIPTION

The TPS708xx is a low dropout voltage regulator with

integrated SVS (RESET, POR, or power on reset)

and power good (PG) functions. These devices are

capable of supplying 250 mA and 125 mA by

regulator 1 and regulator 2 respectively. Quiescent

current is typically 190 µA at full load. Differentiated

features, such as accuracy, fast transient response,

SVS supervisory circuit (power on reset), manual

reset input, and independent enable functions provide

a complete system solution.

PWP PACKAGE

(TOP VIEW)

NC

VIN1

VIN1

MR

EN1

EN2

RESET

GND

VIN2

VIN2

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

NC

VOUT1

VOUT1

VSENSE1/FB1

PG1

PG2

VSENSE2/FB2

VOUT2

VOUT2

NC

NC: No internal connection

1

2

3

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2000–2007, Texas Instruments Incorporated

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

TPS70851PWP

VIN1

5V

0.1 mF

VIN2

0.1 mF

EN1

>2 V

2.5 V then VImax = 6 V, VImin = VO + 1 V:

Copyright © 2000–2007, Texas Instruments Incorporated

Submit Documentation Feedback

5

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

ELECTRICAL CHARACTERISTICS (continued)

Over recommended operating junction temperature range (TJ = –40°C to +125°C), VIN1 or VIN2 = VOUT(nom) + 1 V, IO = 1 mA,

EN = 0 V, and COUT = 33 µF (unless otherwise noted).

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

1.0

1.3

95

98 %VOUT

0.5

%VOUT

PG1/PG2 Terminal

Minimum input voltage for valid PGx

I(PGx) = 300 µA,

Trip threshold voltage

VO decreasing

Hysteresis voltage

Measured at VO

tr(PGx)

Rising edge deglitch

Output low voltage

VIN = 2.7V,

Leakage current

V(PGx) = 6V

V(PGx) ≤ 0.8 V

92

µs

30

I(PGx) = 1 mA

0.15

V

0.4

V

1

µA

EN1/EN2 Terminal

High-level ENx input voltage

2

V

Low-level ENx input voltage

Input current (ENx)

–1

0.7

V

1

µA

MR Terminal

High-level input voltage

2

V

Low-level input voltage

Falling edge delay

0.7

Measured at VO

Pull-up current source

V

140

µs

6

µA

VOUT1 Terminal

Dropout voltage (4)

IO = 250 mA, VIN1 = 3.2 V

TJ = +25°C

83

IO = 250 mA, VIN1 = 3.2 V

140

mV

Peak output current

2 ms pulse width

750

mA

Discharge transistor current

VOUT1 = 1.5 V

7.5

mA

Peak output current

2 ms pulse width

375

mA

Discharge transistor current

VOUT2 = 1.5 V

7.5

mA

1

µA

VOUT2 Terminal

FB Terminal

Input current: TPS70802

(4)

6

FB = 1.8 V

Input voltage (VIN1 or VIN2) = VO(typ) – 100 mV. For 1.5-V, 1.8-V, and 2.5-V regulators, the dropout voltage is limited by input voltage

range. The 3.3-V regulator input is set to 3.2 V to perform this test.

Submit Documentation Feedback

Copyright © 2000–2007, Texas Instruments Incorporated

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

DEVICE INFORMATION

Fixed Voltage Version

VIN1 (2 Pins)

VOUT1 (2 Pins)

2.5 V

UVLO

Comp

10 kW

Current

Sense

+

(see Note A)

+

GND

VSENSE1

ENA_1

Reference

Thermal

Shutdown

ENA_1

Vref

FB1

Vref

PG1

VSENSE1

-

0.95 x Vref

+

Rising Edge

Deglitch

VIN1

PG1

Comp

MR

RESET

Falling Edge

Delay

ENA_1

EN1

PG2

Comp

VSENSE2

-

0.95 x Vref

+

ENA_2

PG2

Rising Edge

Deglitch

Vref

FB2

EN2

-

+

ENA_2

VSENSE2

Current

Sense

ENA_2

(see Note A)

10 kW

VOUT2 (2 Pins)

VIN2 (2 Pins)

A.

For most applications, VSENSE1 and VSENSE2 should be externally connected to VOUT1 and VOUT2, respectively, as

close as possible to the device. For other implementations, refer to SENSE terminal connection discussion in the

Application Information section.

Copyright © 2000–2007, Texas Instruments Incorporated

Submit Documentation Feedback

7

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

Adjustable Voltage Version

VIN1 (2 Pins)

VOUT1 (2 Pins)

2.5 V

UVLO

Comp

Current

Sense

(see Note A)

+

GND

FB1

ENA_1

+

Reference

Thermal

Shutdown

ENA_1

Vref

Vref

PG1

FB1

-

0.95 x Vref

+

Rising Edge

Deglitch

VIN1

PG1

Comp

MR

RESET

Falling Edge

Delay

ENA_1

EN1

PG2

Comp

FB2

-

0.95 x Vref

+

ENA_2

PG2

Rising Edge

Deglitch

Vref

FB2

EN2

-

+

ENA_2

FB2

Current

Sense

8

(see Note A)

VOUT2 (2 Pins)

VIN2 (2 Pins)

A.

ENA_2

For most applications, FB1 and FB2 should be externally connected to resistor dividers as close as possible to the

device. For other implementations, refer to FB terminals connection discussion in the Application Information

section.

Submit Documentation Feedback

Copyright © 2000–2007, Texas Instruments Incorporated

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

RESET Timing Diagram

VIN1

VUVLO

VUVLO

VRES

t

VRES

(see Note A)

MR Input

t

RESET Output

120 ms

Delay

Output

Undefined

120 ms

Delay

Output

Undefined

t

NOTE A: VRES is the minimum input voltage for a valid RESET. The symbol VRES is not currently listed within EIA or JEDEC

standards for semiconductor symbology.

PG1 Timing Diagram

VIN1

VUVLO

VUVLO

VPG

VPG1

(see Note A)

t

VOUT1

VIT+

(see Note B)

Threshold

Voltage

VIT(see Note B)

t

PG1 Output

PG1

Output

Undefined

Output

Undefined

t

NOTES A: VPG1 is the minimum input voltage for a valid PG. The symbol VPG1 is not currently listed within EIA or JEDEC

standards for semiconductor symbology.

NOTES B: VIT- trip voltage is typically 5% lower than the output voltage (95%VO). VIT- to VIT+ is the hysteresis voltage.

Copyright © 2000–2007, Texas Instruments Incorporated

Submit Documentation Feedback

9

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

PG2 Timing Diagram (assuming VIN1 already powered up)

VIN2

t

VOUT2

VIT+

(see Note A)

Threshold

Voltage

VIT(see Note A)

t

PG2

Output

t

NOTE A:

VIT- trip voltage is typically 5% lower than the output voltage (95%VO). VIT- to VIT+ is the hysteresis voltage.

TERMINAL FUNCTIONS

TERMINAL

NAME

NO.

I/O

DESCRIPTION

EN1

5

I

Active low enable for VOUT1

EN2

6

I

Active low enable for VOUT2

GND

8

—

MR

4

I

NC

1, 11, 20

—

No connection

PG1

16

O

Open drain output, low when VOUT1 voltage is less than 95% of the nominal regulated voltage

PG2

15

O

Open drain output, low when VOUT2 voltage is less than 95% of the nominal regulated voltage

RESET

7

I

Open drain output, SVS (power-on reset) signal, active low

2, 3

I

Input voltage of regulator 1

VIN1

Ground

Manual reset input, active low, pulled up internally

VIN2

9, 10

I

Input voltage of regulator 2

VOUT1

18, 19

O

Output voltage of regulator 1

VOUT2

12, 13

O

Output voltage of regulator 2

VSENSE2/FB2

14

I

Regulator 2 output voltage sense/regulator 2 feedback for adjustable

VSENSE1/FB1

17

I

Regulator 1 output voltage sense/regulator 1 feedback for adjustable

10

Submit Documentation Feedback

Copyright © 2000–2007, Texas Instruments Incorporated

�www.ti.com

TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

Detailed Description

The TPS708xx low dropout regulator family provides dual regulated output voltages with independent enable

functions. These devices provide fast transient response and high accuracy with small output capacitors, while

drawing low quiescent current. Other features are integrated SVS (power-on reset, RESET) and power good

(PG1, PG2) that monitor output voltages and provide logic output to the system. These differentiated features

provide a complete power solution.

The TPS708xx, unlike many other LDOs, features very low quiescent current that remains virtually constant even

with varying loads. Conventional LDO regulators use a PNP pass element, the base current of which is directly

proportional to the load current through the regulator (IB = IC/β). The TPS708xx uses a PMOS transistor to pass

current; because the gate of the PMOS is voltage-driven, operating current is low and stable over the full load

range.

Pin Functions

Enable (EN1, EN2)

The EN terminals are inputs that enable or shut down each respective regulator. If EN is at a voltage high signal,

the respective regulator is in shutdown mode. When EN goes to voltage low, the respective regulator is enabled.

Power-Good (PG1, PG2)

The PG terminals are open drain, active high output terminals that indicate the status of each respective

regulator. When VOUT1 reaches 95% of its regulated voltage, PG1 goes to a high impedance state. When VOUT2

reaches 95% of its regulated voltage, PG2 goes to a high impedance state. Each PG goes to a low impedance

state when its respective output voltage is pulled below 95% (that is, goes to an overload condition) of its

regulated voltage. The open drain outputs of the PG terminals require a pull-up resistor.

Manual Reset Pin

MR is an active low input terminal used to trigger a reset condition. When MR is pulled to logic low, a POR

(RESET) occurs. The terminal has a 6-µA pull-up current to VIN1.

Sense (VSENSE1, VSENSE2)

The sense terminals of fixed-output options must be connected to the regulator outputs, and the connection

should be as short as possible. Internally, the sense terminal connects to high-impedance, wide-bandwidth

amplifiers through a resistor-divider network and noise pickup feeds through to the regulator output. It is essential

to route the sense connection in such a way as to minimize or avoid noise pickup. Adding RC networks between

sense terminals and VOUT terminals to filter noise is not recommended because these networks can cause the

regulators to oscillate.

Copyright © 2000–2007, Texas Instruments Incorporated

Submit Documentation Feedback

11

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

FB1 and FB2

FB1 and FB2 are input terminals used for adjustable-output devices and must be connected to the external

feedback resistor divider. FB1 and FB2 connections should be as short as possible. It is essential to route them

in such a way as to minimize or avoid noise pickup. Adding RC networks between FB terminals and VOUT

terminals to filter noise is not recommended because these networks can cause the regulators to oscillate.

RESET Indicator

The TPS708xx features a RESET (SVS, POR, or power on reset). RESET can be used to drive power on reset

circuitry or a low-battery indicator. RESET is an active low, open drain output that indicates the status of the

manual reset pin (MR). When MR is in a high-impedance state, RESET goes to a high impedance state after a

120-ms delay. To monitor VOUT1, the PG1 output pin can be connected to MR. To monitor VOUT2, the PG2 output

pin can be connected to MR. The open drain output of the RESET terminal requires a pull-up resistor. If RESET

is not used, it can be left floating.

VIN1 and VIN2

VIN1 and VIN2 are inputs to each regulator. Internal bias voltages are powered by VIN1.

VOUT1 and VOUT2

VOUT1 and VOUT2 are output terminals of each regulator.

12

Submit Documentation Feedback

Copyright © 2000–2007, Texas Instruments Incorporated

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

TYPICAL CHARACTERISTICS

Table of Graphs

FIGURE

VO

Output voltage

PSRR

ZO

vs Output current

Figure 1 to Figure 3

vs Junction temperature

Figure 4 to Figure 5

Ground current

vs Junction temperature

Power-supply rejection ratio

vs Frequency

Figure 7 to Figure 10

Output spectral noise density

vs Frequency

Figure 11 to Figure 14

Output impedance

vs Frequency

Dropout voltage

Figure 6

Figure 15 to Figure 18

vs Temperature

Figure 19 and Figure 20

vs Input voltage

Figure 21 and Figure 22

Load transient response

VO

Figure 23 and Figure 24

Line transient response (VOUT1)

Figure 25

Line transient response (VOUT2)

Figure 26

Output voltage

vs Time (start-up)

Figure 27 and Figure 28

Equivalent series resistance (ESR)

vs Output current

Figure 30 to Figure 33

TPS70851

OUTPUT VOLTAGE

vs

OUTPUT CURRENT

TPS70851

OUTPUT VOLTAGE

vs

OUTPUT CURRENT

3.303

1.802

VIN1 = 4.3 V

VIN2 = 2.8 V

TJ = +25°C

3.302

VOUT2

3.301

VO - Output Voltage - V

VO - Output Voltage - V

TJ = +25°C

1.801

VOUT1

3.3

3.299

3.298

3.297

1.800

1.799

1.798

1.797

1.796

3.296

3.295

1.795

0

0.05

0.1

0.15

0.2

0.25

0

0.025

0.05

0.075

IO - Output Current - A

IO - Output Current - A

Figure 1.

Figure 2.

Copyright © 2000–2007, Texas Instruments Incorporated

0.1

Submit Documentation Feedback

0.125

13

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

TPS70845

OUTPUT VOLTAGE

vs

OUTPUT CURRENT

TPS70851

OUTPUT VOLTAGE

vs

JUNCTION TEMPERATURE

1.201

3.35

VIN2 = 2.7 V

3.33

VOUT2

VO - Output Voltage - V

VO - Output Voltage - V

1.200

1.199

1.198

1.197

IO = 250 mA

3.31

3.29

IO = 1 mA

3.27

3.25

1.196

3.23

-40 -25 -10 5 20 35 50 65 80 95 110 125

TJ - Junction Temperature - °C

1.195

0

0.025

0.05

0.075

0.1

0.125

IO - Output Current - A

1.85

VIN1 = 4.3 V

VOUT1

TJ = +25°C

Figure 3.

Figure 4.

TPS70851

OUTPUT VOLTAGE

vs

JUNCTION TEMPERATURE

TPS70851

GROUND CURRENT

vs

JUNCTION TEMPERATURE

210

VIN2 = 2.8 V

Regulator 1 and Regulator 2

VOUT2

200

IOUT1 = 1 mA

IO = 1 mA

1.81

1.79

IO = 250 mA

1.77

1.75

1.73

40 25

IOUT2 = 1 mA

190

180

IOUT1 = 250 mA

170

IOUT2 = 125 mA

160

10

5 20 35 50 65 80 95 110 125

TJ - Junction Temperature - °C

Figure 5.

14

Ground Current - mA

VO - Output Voltage - V

1.83

Submit Documentation Feedback

150

-40 -25 -10

5

20

35

50 65

80

95 110 125

TJ - Junction Temperature - °C

Figure 6.

Copyright © 2000–2007, Texas Instruments Incorporated

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

TPS70851

POWER-SUPPLY REJECTION RATIO

vs

FREQUENCY

TPS70851

POWER-SUPPLY REJECTION RATIO

vs

FREQUENCY

10

CO = 22 mF

-20

VOUT1

-30

-40

-50

-60

-70

-80

-90

IO = 250 mA

0

CO = 22 mF

VOUT1

-10

-20

-30

-40

-50

-60

-70

-80

-90

10

-10

PSRR - Power Supply Rejection Ratio - dB

PSRR - Power Supply Rejection Ratio - dB

IO = 10 mA

100

1k

10 k

f - Frequency - Hz

100 k

1M

1k

10 k

100 k

Figure 7.

Figure 8.

TPS70851

POWER-SUPPLY REJECTION RATIO

vs

FREQUENCY

TPS70851

POWER-SUPPLY REJECTION RATIO

vs

FREQUENCY

VOUT2

-30

-40

-50

-60

-70

-80

-90

100

1M

10

CO = 22 mF

10

100

f - Frequency - Hz

IO = 10 mA

-20

10

PSRR - Power Supply Rejection Ratio - dB

PSRR - Power Supply Rejection Ratio - dB

-10

1k

10 k

100 k

1M

IO = 150 mA

0

CO = 22 mF

VOUT2

-10

-20

-30

-40

-50

-60

-70

-80

-90

f - Frequency - Hz

1k

10 k

f - Frequency - Hz

Figure 9.

Figure 10.

Copyright © 2000–2007, Texas Instruments Incorporated

10

100

100 k

Submit Documentation Feedback

1M

15

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

OUTPUT SPECTRAL NOISE DENSITY

vs

FREQUENCY

OUTPUT SPECTRAL NOISE DENSITY

vs

FREQUENCY

10

10

VIN1 = 4.3 V

Output Spectral Noise Density - mV/ÖHz

VIN1 = 4.3 V

Output Spectral Noise Density - mV/ÖHz

VOUT1 = 3.3 V

IO = 10 mA

1

0.1

0.01

100

1

0.1

0.01

100

1k

10 k

f - Frequency - Hz

Figure 11.

Figure 12.

OUTPUT SPECTRAL NOISE DENSITY

vs

FREQUENCY

OUTPUT SPECTRAL NOISE DENSITY

vs

FREQUENCY

10 k

100 k

100 k

10

VIN2 = 2.8 V

VIN2 = 2.8 V

VOUT2 = 1.8 V

VOUT2 = 1.8 V

Output Spectral Noise Density - mV/ÖHz

Output Spectral Noise Density - mV/ÖHz

16

IO = 250 mA

f - Frequency - Hz

1k

10

IO = 10 mA

1

0.1

0.01

100

VOUT1 = 3.3 V

1k

10 k

100

IO = 125 mA

1

0.1

0.01

100

f - Frequency - Hz

1k

10 k

f - Frequency - Hz

Figure 13.

Figure 14.

Submit Documentation Feedback

100 k

Copyright © 2000–2007, Texas Instruments Incorporated

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

OUTPUT IMPEDANCE

vs

FREQUENCY

OUTPUT IMPEDANCE

vs

FREQUENCY

100

10

CO = 33 mF

CO = 33 mF

IO = 10 mA

IO = 250 mA

VOUT1 = 3.3 V

ZO - Output Impedance - W

VOUT1 = 3.3 V

ZO - Output Impedance - W

TJ = +25°C

1

0.1

0.01

1

0.1

0.01

10

100

1k

10 k

100 k

1M

TJ = +25°C

10

10 M

10

Figure 16.

OUTPUT IMPEDANCE

vs

FREQUENCY

OUTPUT IMPEDANCE

vs

FREQUENCY

1M

10 M

1M

10 M

CO = 33 mF

IO = 10 mA

IO = 125 mA

VOUT2 = 1.8 V

ZO - Output Impedance - W

VOUT2 = 1.8 V

ZO - Output Impedance - W

100 k

Figure 15.

100

TJ = +25°C

1

100

10 k

f - Frequency - Hz

CO = 33 mF

10

1k

f - Frequency - Hz

10

0.1

100

1k

10 k

100 k

1M

10 M

TJ = +25°C

10

1

0.1

0.01

10

100

1k

10 k

100 k

f - Frequency - Hz

f - Frequency - Hz

Figure 17.

Figure 18.

Copyright © 2000–2007, Texas Instruments Incorporated

Submit Documentation Feedback

17

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

TPS70851

DROPOUT VOLTAGE

vs

TEMPERATURE

TPS70851

DROPOUT VOLTAGE

vs

TEMPERATURE

120

6

CO = 33 mF

VIN1 = 3.2 V

5

IO = 10 mA

IO = 250 mA

Dropout Voltage - mV

Dropout Voltage - mV

100

CO = 33 mF

VIN1 = 3.2 V

80

60

40

20

4

3

2

1

IO = 0 mA

0

-40 -25 -10

5

20

35

50 65

80

0

-40 -25 -10 5 20 35 50 65 80 95 110 125

TJ - Junction Temperature - °C

95 110 125

TJ - Junction Temperature - °C

Figure 19.

Figure 20.

TPS70802

DROPOUT VOLTAGE

vs

INPUT VOLTAGE

TPS70802

DROPOUT VOLTAGE

vs

INPUT VOLTAGE

140

250

IO = 250 mA

IO = 125 mA

VOUT1

120

VOUT2

200

100

Dropout Voltage - mV

Dropout Voltage - mV

TJ = +125°C

TJ = +25°C

80

60

TJ = -40°C

40

TJ = +125°C

150

TJ = +25°C

100

TJ = -40°C

50

20

0

2.5

18

3

3.5

4

4.5

5

0

2.5

VI - Input Voltage - V

3.5

4

VI - Input Voltage - V

Figure 21.

Figure 22.

Submit Documentation Feedback

3

4.5

5

Copyright © 2000–2007, Texas Instruments Incorporated

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

VOUT1 = 3.3 V

0

DVO - Change in

20

0

-20

-40

0.2

0.4 0.6 0.8

1

1.2

1.4 1.6 1.8

20

0

-20

-40

-60

0

0.2

0.4 0.6 0.8

1

1.2

1.4 1.6 1.8

Figure 24.

LINE TRANSIENT RESPONSE

LINE TRANSIENT RESPONSE

VI - Input Voltage - V

Figure 23.

50

0

IO = 250 mA

CO = 33 mF

VOUT1

20

VOUT2 = 1.8 V

0

T - Time - ms

4.3

0

TJ = +25°C

T - Time - ms

5.3

-50

CO = 33 mF

125

-80

2

DVO - Change in

VI - Input Voltage - V

DVO - Change in

IO - Output Current - mA

TJ = +25°C

Output Voltage - mV

CO = 33 mF

250

0

Output Voltage - mV

LOAD TRANSIENT RESPONSE

40

60

80 100 120 140 160 180 200

T - Time - ms

Figure 25.

Copyright © 2000–2007, Texas Instruments Incorporated

Output Voltage - mV

DVO - Change in

Output Voltage - mV

IO - Output Current - mA

LOAD TRANSIENT RESPONSE

2

3.8

2.8

10

0

IO = 125 mA

CO = 33 mF

-10

VOUT2

0

20

40

60

80 100 120 140 160 180 200

T - Time - ms

Figure 26.

Submit Documentation Feedback

19

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

VOUT2 - Output Voltage

VO = 3.3 V

3

CO = 33 mF

IO = 250 mA

2

VOUT2 = Standby

1

0

5

0

0

0.2 0.4

0.6

OUTPUT VOLTAGE AND ENABLE VOLTAGE

vs

TIME (START-UP)

0.8 1.0 1.2 1.4

1.6 1.8 2.0

Enable Voltage (EN2) - V

Enable Voltage (EN1) - V

VOUT1 - Output Voltage

OUTPUT VOLTAGE AND ENABLE VOLTAGE

vs

TIME (START-UP)

VO = 1.5 V

CO = 33 mF

3

IO = 125 mA

VOUT1 = Standby

2

1

0

5

0

0

0.2 0.4

T - Time - ms

0.6

0.8 1.0 1.2 1.4

2.0

T - Time - ms

Figure 27.

VIN

1.6 1.8

Figure 28.

To Load

IN

OUT

+

COUT

EN

RL

GND

ESR

Figure 29. Test Circuit for Typical Regions of Stability

20

Submit Documentation Feedback

Copyright © 2000–2007, Texas Instruments Incorporated

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

TYPICAL REGION OF STABILITY

EQUIVALENT SERIES RESISTANCE(1)

vs

OUTPUT CURRENT

TYPICAL REGION OF STABILITY

EQUIVALENT SERIES RESISTANCE(1)

vs

OUTPUT CURRENT

10

10

TJ = +25°C

1

0.1

50 mW

REGION OF INSTABILITY

0.01

REGION OF INSTABILITY

VO = 3.3 V

CO = 6.8 mF

TJ = +25°C

1

250 mW

REGION OF INSTABILITY

0.1

0

50

100

150

200

50

100

150

200

IO - Output Current - mA

Figure 30.

Figure 31.

TYPICAL REGION OF STABILITY

EQUIVALENT SERIES RESISTANCE(1)

vs

OUTPUT CURRENT

TYPICAL REGION OF STABILITY

EQUIVALENT SERIES RESISTANCE(1)

vs

OUTPUT CURRENT

250

10

REGION OF INSTABILITY

VO = 1.8 V

CO = 10 mF

TJ = +25°C

1

0.1

50 mW

REGION OF INSTABILITY

0.01

0

250

IO - Output Current - mA

10

ESR - Equivalent Series Resistance - W

ESR - Equivalent Series Resistance - W

VO = 3.3 V

CO = 10 mF

ESR - Equivalent Series Resistance - W

ESR - Equivalent Series Resistance - W

REGION OF INSTABILITY

REGION OF INSTABILITY

VO = 1.8 V

CO = 6,8 mF

TJ = +25°C

1

250 mW

REGION OF INSTABILITY

0.1

0

25

50

75

IO - Output Current - mA

Figure 32.

100

125

0

25

50

75

100

125

IO - Output Current - mA

Figure 33.

(1)

Equivalent series resistance (ESR) refers to the total series resistance, including the ESR of the capacitor, any

series resistance added externally, and PWB trace resistance to CO.

Copyright © 2000–2007, Texas Instruments Incorporated

Submit Documentation Feedback

21

�TPS70845, TPS70848

TPS70851, TPS70858

TPS70802

www.ti.com

SLVS301D – JUNE 2000 – REVISED DECEMBER 2007

APPLICATION INFORMATION

TPS708xxPWP

(Fixed Output Option)

Sequencing Timing Diagrams

This section provides a number of timing diagrams

showing how this device functions in different

configurations.

VIN

VIN1

0.1 mF

VSENSE1

Application condition: VIN1 and VIN2 are tied to the

same fixed input voltage greater than VUVLO. PG2 is

tied to MR.

VOUT1

VOUT1

10 mF

250 kW

PG1

VIN2

EN1 and EN2 are initially high; therefore, both

regulators are off, and PG1 and PG2 (tied to MR) are

at logic low. Since MR is at logic low, RESET is also

at logic low. When EN1 is taken to logic low, VOUT1

turns on. Later, when EN2 is taken to logic low, VOUT2

turns on. When VOUT1 reaches 95% of its regulated

output voltage, PG1 goes to logic high. When VOUT2

reaches 95% of its regulated output voltage, PG2

(tied to MR) goes to logic high. When VIN1 is greater

than VUVLO and MR (tied to PG2) is at logic high,

RESET is pulled to logic high after a 120-ms delay.

When EN1 and EN2 return to logic high, both devices

power down and both PG1, PG2 (tied to MR2), and

RESET return to logic low.

MR

250 kW

RESET

0.1 mF

RESET

EN1

>2 V

PG2

PG2

EN1

2 V

MR

EN2

VOUT2

VOUT2

2 V

2 V

250 kW

MR

VSENSE2

EN2

VOUT2

2 V

2 V

RESET

PG2

250 kW

RESET

PG2

EN1

VSENSE2

EN2

VOUT2

VOUT2

2.0 V

EN

OUT

VO