TPS718xx

TPS719xx

www.ti.com..................................................................................................................................................... SBVS088C – FEBRUARY 2007 – REVISED MAY 2008

Dual, 200mA Output, Low Noise, High PSRR

Low-Dropout Linear Regulators

FEATURES

DESCRIPTION

• Dual, 200mA High-Performance LDOs

• Low Total Quiescent Current: 90µA with Both

LDOs Enabled

• Low Noise: 70µVRMS/V

• Active Output Pulldown (TPS719xx)

• Independent Enables for Each LDO

• PSRR: 65dB at 1kHz, 45dB at 1MHz

• Available in Multiple Fixed-Output Voltage

Combinations from 0.9V to 3.6V Using

Innovative Factory EEPROM Programming

• Fast Start-Up Time: 160µs

• Over-Current, Over-Temperature and

Under-Voltage Protection

• Low Dropout: 230mV at 200mA

• Stable with 1µF Ceramic Output Capacitor

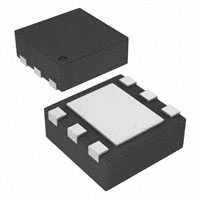

• Available in 2mm × 2mm SON-6 and 6-Ball

WCSP Packages

The TPS718xx and TPS719xx families of low-dropout

(LDO) regulators offer a high power-supply rejection

ratio (PSRR), low noise, fast start-up, and excellent

line and load transient responses while consuming a

very low 90µA (typical) at no load ground current with

both LDOs enabled. The TPS719xx also provides an

active pulldown circuit to quickly discharge output

loads. The TPS718xx and TPS719xx are stable with

ceramic capacitors and use an advanced BiCMOS

fabrication process to yield a typical dropout voltage

of 230mV at 200mA output loads. The TPS718xx and

TPS719xx also use a precision voltage reference and

feedback loop to achieve 3% overall accuracy over all

load, line, process, and temperature variations. Both

families of devices are fully specified from TJ = –40°C

to +125°C and are offered in 2mm × 2mm SON-6 and

6-ball Wafer Chip-Scale (WCSP) packages that are

ideal for applications such as mobile handsets and

WLAN that require good thermal dissipation while

maintaining a very small footprint.

1

23

APPLICATIONS

•

•

•

•

Digital Cameras and Camera Modules

Cellular Camera and TV Phones

Wireless LAN, Bluetooth®

Handheld Products

2.7V to 6.5V

VIN

0.9V to 3.6V

IN

1 mF

On

VOUT

OUT1

1m F

TPS718xx

TPS719xx

6 EN1

0.9V - 3.6V

VOUT

OUT2

On

TPS718xx, TPS719xx

YZC Package

6-BALL WCSP

(Top View)

C2

OUT1 1

EN1

Off

Off

TPS718xx, TPS719xx

DRV Package

2mm x 2mm SON-6

(Top View)

IN 2

GND

5 GND

OUT2 3

EN2

GND

C1

EN1

OUT1

B2

B1

A2

A1

GND

1m F

4 EN2

EN2

TPS718Axx, TPS719Axx

YZC Package

6-BALL WCSP

(Top View)

IN

OUT2

A1

A2

B1

B2

C1

C2

EN1

OUT1

GND

IN

EN2

OUT2

Typical Application Circuit

1

2

3

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Bluetooth is a registered trademark of Bluetooth SIG, Inc.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2007–2008, Texas Instruments Incorporated

�TPS718xx

TPS719xx

SBVS088C – FEBRUARY 2007 – REVISED MAY 2008..................................................................................................................................................... www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

ORDERING INFORMATION (1)

VOUT (2) (3)

PRODUCT

TPS718xx-yywwwz

TPS718Axx-yywwwz

TPS719xx-yywwwz

TPS719Axx-yywwwz

A denotes device with rotated pin 1 orientation of wafer-chipscale package.

XX is nominal output voltage for LDO1 (for example, 28 = 2.8V).

YY is nominal output voltage for LDO2.

WWW is package designator.

Z is tape and reel quantity (R = 3000, T = 250).

Examples: TPS71918–285DRVR

TPS719185-33DRVR

(1)

(2)

(3)

XX = 18 = 1.8V, YYY = 285 = 2.85V

XXX = 185 = 1.85V, YY = 33 = 3.3V

DRV = 2mm x 2mm SON package

Z = R = 3000 piece reel

For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI

website at www.ti.com.

Both outputs are programmable from 0.9V to 3.6V in 50mV increments.

Output voltages from 0.9V to 3.6V in 50mV increments are available through the use of innovative factory EEPROM programming;

minimum order quantities may apply. Contact factory for details and availability.

ABSOLUTE MAXIMUM RATINGS (1)

Over operating temperature range (unless otherwise noted). All voltages are with respect to GND.

PARAMETER

TPS718xx, TPS719xx

UNIT

Input voltage range, VIN

Enable voltage range, VEN1 and VEN2

Output voltage range, VOUT

–0.3 to +7.0

V

–0.3 to VIN + 0.3V

V

–0.3 to +7.0

V

Peak output current

Internally limited

Output short-circuit duration

Indefinite

Junction temperature range, TJ

–55 to +150

°C

Storage temperature range , TSTG

–55 to +150

°C

Total continuous power dissipation, PDISS

See Dissipation Ratings Table

ESD rating, HBM

2

kV

ESD rating, CDM

500

V

(1)

Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may

degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond

those specified is not implied.

DISSIPATION RATINGS

BOARD

PACKAGE

RθJC

RθJA

DERATING FACTOR

ABOVE TA = +25°C

TA < +25°C

TA = +70°C

TA = +85°C

High-K (1)

DRV

20°C/W

95°C/W

10.53mW/°C

1053mW

579mW

421mW

High-K (1)

YZC

27°C/W

190°C/W

5.3mW/°C

530mW

295mW

215mW

(1)

2

The JEDEC high-K (2s2p) board used to derive this data was a 3in × 3in, multilayer board with 1-ounce internal power and ground

planes and 2-ounce copper traces on top and bottom of the board.

Submit Documentation Feedback

Copyright © 2007–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS718xx TPS719xx

�TPS718xx

TPS719xx

www.ti.com..................................................................................................................................................... SBVS088C – FEBRUARY 2007 – REVISED MAY 2008

ELECTRICAL CHARACTERISTICS

Over operating temperature range (TJ = –40°C to +125°C), VIN = VOUT(TYP) + 0.5V or 2.7V, whichever is greater;

IOUT = 0.5mA, VEN1 = VEN2 = VIN, COUT = 1.0µF, unless otherwise noted. Typical values are at TJ = +25°C.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

VIN

Input voltage range (1)

2.7

6.5

VOUT1, VOUT2

Output voltage range

0.9

3.6

Nominal

TJ = +25°C

VOUT1, VOUT2

Output accuracy

ΔVOUT/ ΔVIN

Line regulation

VOUT(NOM) + 0.5V ≤ VIN ≤ 6.5V,

IOUT = 5mA

ΔVOUT/ ΔIOUT

Load regulation

0mA ≤ IOUT ≤ 200mA

VDO

Dropout voltage (2)

(VIN = VOUT(NOM) – 0.1V)

IOUT = 200mA

ICL

Output current limit (per output)

VOUT = 0.9 × VOUT(NOM)

IGND

ISHDN

PSRR

VN

Ground pin current

Shutdown current (IGND)

Power-supply rejection ratio

VIN = 3.8V, VOUT = 2.8V,

IOUT = 200mA

–3.0

240

V

V

mV

+3.0

%

130

µV/V

75

µV/mA

230

400

mV

340

575

mA

IOUT1 = IOUT2 = 0.1mA

90

160

µA

IOUT1 = IOUT2 = 200mA

250

VEN1,2 ≤ 0.4V, 2.7V ≤ VIN < 4.5V,

TJ = –40°C to +85°C

0.3

VEN1,2 ≤ 0.4V, 4.5V ≤ VIN ≤ 6.5V,

TJ = –40°C to +85°C

1.8

µA

f = 100Hz

63

dB

f = 1kHz

63

dB

f = 10kHz

72

dB

f = 100kHz

58

dB

f = 1MHz

44

dB

Output noise voltage

BW = 100Hz to 100kHz

µA

3.0

70 × VOUT

µA

µVRMS

TSTR

Startup time (3)

RL = 14Ω, VOUT = 2.8V,

COUT = 1.0µF

160

µs

TSHUT

Shutdown time (4), (5)

(TPS719xx only)

RL = ∞, COUT = 1.0µF,

VOUT = 2.8V

180

µs

VEN(HI)

Enable high (enabled)

(EN1 and EN2)

VIN ≤ 5.5V

VEN(LO)

Enable low (shutdown)

(EN1 and EN2)

IEN

UVLO

(1)

(2)

(3)

(4)

(5)

Over VIN, IOUT, VOUT + 0.5V ≤ VIN ≤ 6.5V

Temp

0mA ≤ IOUT ≤ 200mA

±2.5

UNIT

5.5V < VIN ≤ 6.5V

Enable pin current, enabled

(EN1 and EN2)

EN1 = EN2 = 6.5V

Undervoltage lockout

VIN rising

Hysteresis

VIN falling

TSD

Thermal shutdown temperature

TJ

Operating junction temperature

1.2

6.5

V

1.25

6.5

V

0

0.4

V

0.04

1.0

µA

2.45

2.52

2.38

V

150

mV

Shutdown, temperature increasing

+160

°C

Reset, temperature decreasing

+140

°C

–40

+125

°C

Minimum VIN = VOUT + VDO or 2.7V, whichever is greater.

VDO is not measured for devices with VOUT(NOM) < 2.8V because minimum VIN = 2.7V.

Time from VEN = 1.25V to VOUT = 95% (VOUT(NOM)).

Time from VEN = 0.4V to VOUT = 5% (VOUT(NOM)).

See Shutdown section in the Applications Information for more details.

Copyright © 2007–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS718xx TPS719xx

Submit Documentation Feedback

3

�TPS718xx

TPS719xx

SBVS088C – FEBRUARY 2007 – REVISED MAY 2008..................................................................................................................................................... www.ti.com

DEVICE INFORMATION

TPS719 only

60W

Bandgap

UVLO

Thermal

Shutdown

Current

Limit

2.5mA

OUT1

EN1

Enable and

Power

Control

Logic

EN2

OUT2

Thermal

Shutdown

IN

2.5mA

Current

Limit

UVLO

Bandgap

60W

TPS719 only

GND

Figure 1. Functional Block Diagram

4

Submit Documentation Feedback

Copyright © 2007–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS718xx TPS719xx

�TPS718xx

TPS719xx

www.ti.com..................................................................................................................................................... SBVS088C – FEBRUARY 2007 – REVISED MAY 2008

DRV PACKAGE

SON-6

(TOP VIEW)

OUT1 1

6 EN1

IN 2

GND

OUT2 3

5 GND

4 EN2

YZC PACKAGE

6-BALL WCSP

(TOP VIEW)

C2

C1

B2

B1

A2

A1

EN1

OUT1

GND

IN

EN2

OUT2

TPS718xx

TPS719xx

YZC PACKAGE

6-BALL WCSP

(TOP VIEW)

A1

A2

B1

B2

C1

C2

EN1

OUT1

GND

IN

EN2

OUT2

TPS718Axx

TPS719Axx

PIN DESCRIPTIONS

TPS718Axx (1)

TPS719Axx (1)

TPS718xx

TPS719xx

(1)

NAME

DRV

YZC

YZC

DESCRIPTION

OUT1

1

C1

A2

Output of Regulator 1. A small ceramic capacitor (typically ≥ 1µF) is

needed from this pin to ground to assure stability.

IN

2

B1

B2

Input supply to both regulators.

OUT2

3

A1

C2

Output of Regulator 2. A small ceramic capacitor (typically ≥ 1µF) is

needed from this pin to ground to assure stability.

EN2

4

A2

C1

Enable pin for Regulator 2. Driving the Enable pin (EN2) high turns on

Regulator 2. Driving this pin low puts Regulator 2 into shutdown mode,

reducing operating current.

GND

5

B2

B1

Ground. DRV thermal pad should also be connected to ground.

EN1

6

C2

A1

Enable pin for Regulator 1. Driving the Enable pin (EN1) high turns on

Regulator 1. Driving this pin low puts Regulator 1 into shutdown mode,

reducing operating current.

A option denotes devices with rotated Pin 1 orientation on Wafer Chipscale packages.

Copyright © 2007–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS718xx TPS719xx

Submit Documentation Feedback

5

�TPS718xx

TPS719xx

SBVS088C – FEBRUARY 2007 – REVISED MAY 2008..................................................................................................................................................... www.ti.com

TYPICAL CHARACTERISTICS

Over operating temperature range (TJ = –40°C to +125°C), VIN = VOUT(TYP) + 0.5V or 2.7V, whichever is greater;

IOUT = 0.5mA, VEN1 = VEN2 = VIN, COUT = 1.0µF, unless otherwise noted. Typical values are at TJ = +25°C.

LINE REGULATION

LINE REGULATION

4

0

TJ = +85°C

IOUT = 5mA

3

-1

TJ = +125°C

TJ = +25°C

DVOUT (mV)

2

DVOUT (mV)

IOUT = 200mA

1

TJ = +25°C

0

-1

TJ = -40°C

-2

-3

TJ = +85°C

-2

TJ = -40°C

-4

TJ = +125°C

-3

-5

-4

2.5

3.5

4.5

VIN (V)

5.5

6.5

2.5

3.5

Figure 2.

4.5

VIN (V)

5.5

6.5

150

200

Figure 3.

LOAD REGULATION UNDER LIGHT LOADS

LOAD REGULATION

4

5

TJ = +85°C

TJ = +25°C

2

0

-5

-2

DVOUT (mV)

DVOUT (mV)

0

TJ = -40°C

-4

-10

-15

-20

-25

-6

TJ = +125°C

TJ = +85°C

TJ = +25°C

TJ = -40°C

-30

TJ = +125°C

-8

-35

-40

-10

0

1

3

2

4

5

0

50

IOUT (mA)

100

IOUT (mA)

Figure 4.

Figure 5.

OUTPUT VOLTAGE vs

TEMPERATURE

DROPOUT VOLTAGE vs

OUTPUT CURRENT

2.805

350

IOUT = 5mA

TJ = +125°C

2.800

300

TJ = +85°C

2.795

2.785

IOUT = 200mA

2.780

2.775

VDO (mV)

IOUT = 0.1mA

2.790

VOUT (V)

250

200

150

TJ = +25°C

100

TJ = -40°C

2.770

50

2.765

0

2.760

-40 -25 -10

5

20

35 50

TJ (°C)

65

80

95 110 125

50

0

Figure 6.

6

Submit Documentation Feedback

100

IOUT (mA)

150

200

Figure 7.

Copyright © 2007–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS718xx TPS719xx

�TPS718xx

TPS719xx

www.ti.com..................................................................................................................................................... SBVS088C – FEBRUARY 2007 – REVISED MAY 2008

TYPICAL CHARACTERISTICS (continued)

Over operating temperature range (TJ = –40°C to +125°C), VIN = VOUT(TYP) + 0.5V or 2.7V, whichever is greater;

IOUT = 0.5mA, VEN1 = VEN2 = VIN, COUT = 1.0µF, unless otherwise noted. Typical values are at TJ = +25°C.

GROUND PIN CURRENT vs

OUTPUT CURRENT

200

GROUND PIN CURRENT vs

INPUT VOLTAGE

60

TJ = +125°C

IOUT = 1mA

TJ = +25°C

50

160

40

IGND (mA)

IGND (mA)

TJ = +85°C

120

TJ = -40°C

80

30

20

40

10

0

0

50

0

150

100

IOUT (mA)

200

2.5

5.5

Figure 9.

GROUND PIN CURRENT vs

TEMPERATURE (BOTH LDOs ENABLED)

SHUTDOWN CURRENT vs

INPUT VOLTAGE

6.5

5.0

IOUT = 0mA

4.5

Shutdown Current (mA)

120

100

IGND (mA)

4.5

VIN (V)

Figure 8.

140

80

60

40

20

4.0

TJ = +125°C

3.5

3.0

TJ = -40°C

2.5

TJ = +85°C

2.0

1.5

1.0

TJ = +25°C

0.5

0

0

-40 -25 -10

5

20

35 50

TJ (°C)

65

80

95 110 125

2.5

3.5

4.5

VIN (V)

5.5

6.5

Figure 10.

Figure 11.

CURRENT LIMIT vs

INPUT VOLTAGE

POWER-SUPPLY RIPPLE REJECTION vs

FREQUENCY (VIN – VOUT = 0.5V)

450

90

425

80

100mA

5mA

70

400

375

PSRR (dB)

Current Limit (mA)

3.5

350

325

275

50

200mA

40

30

TJ = +125°C

TJ = +85°C

TJ = +25°C

TJ = -40°C

300

60

20

10

0

250

2.5

3.5

4.5

VIN (V)

5.5

6.5

10

100

Figure 12.

1k

100k

10k

Frequency (Hz)

1M

10M

Figure 13.

Copyright © 2007–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS718xx TPS719xx

Submit Documentation Feedback

7

�TPS718xx

TPS719xx

SBVS088C – FEBRUARY 2007 – REVISED MAY 2008..................................................................................................................................................... www.ti.com

TYPICAL CHARACTERISTICS (continued)

Over operating temperature range (TJ = –40°C to +125°C), VIN = VOUT(TYP) + 0.5V or 2.7V, whichever is greater;

IOUT = 0.5mA, VEN1 = VEN2 = VIN, COUT = 1.0µF, unless otherwise noted. Typical values are at TJ = +25°C.

POWER-SUPPLY RIPPLE REJECTION vs

FREQUENCY (VIN – VOUT = 1V)

POWER-SUPPLY RIPPLE REJECTION vs

INPUT VOLTAGE

80

90

100mA

80

70

5mA

60

50

40

30

50

100kHz

40

1MHz

30

200mA

VOUT = 2.80V

IOUT = 5mA

10

10

0

0

10

100

1k

100k

10k

Frequency (Hz)

10M

1M

3.0

3.2

3.4

3.6

3.8

Figure 14.

Figure 15.

POWER-SUPPLY RIPPLE REJECTION vs

INPUT VOLTAGE

OUTPUT SPECTRAL NOISE DENSITY vs

FREQUENCY

Output Spectral Noise Density (mVÖHz)

10kHz

70

1kHz

60

100kHz

50

40

1MHz

30

20

VOUT = 2.80V

IOUT = 200mA

10

4.0

VIN (V)

80

PSRR (dB)

10kHz

20

20

0

10

VOUT = 2.80V

1

0.1

0.01

3.0

3.2

3.4

3.6

3.8

100

4.0

10k

1k

VIN (V)

Frequency (Hz)

Figure 16.

Figure 17.

LINE TRANSIENT RESPONSE

LOAD TRANSIENT RESPONSE

6.5V

1V/div 3.3V

IOUTmin = 3mA

dVIN

= 1V/ms

dt

100k

dIOUT

= 200mA/ms

dt

250mA/div

IOUT1

10mV/div

VOUT1

10mV/div

VOUT2

VIN

10mV/div

VOUT1

10mV/div

VOUT2

8

1kHz

60

PSRR (dB)

PSRR (dB)

70

10ms/div

20ms/div

Figure 18.

Figure 19.

Submit Documentation Feedback

Copyright © 2007–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS718xx TPS719xx

�TPS718xx

TPS719xx

www.ti.com..................................................................................................................................................... SBVS088C – FEBRUARY 2007 – REVISED MAY 2008

TYPICAL CHARACTERISTICS (continued)

Over operating temperature range (TJ = –40°C to +125°C), VIN = VOUT(TYP) + 0.5V or 2.7V, whichever is greater;

IOUT = 0.5mA, VEN1 = VEN2 = VIN, COUT = 1.0µF, unless otherwise noted. Typical values are at TJ = +25°C.

TPS719 ENABLE RESPONSE

POWER-UP/POWER-DOWN

IOUT = 200mA

VIN

6.5V

0V

EN1, EN2

4V/div

1V/div

1V/div

VOUT1

1V/div

VOUT2

40ms/div

VOUT

400ms/div

Figure 20.

Figure 21.

Copyright © 2007–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS718xx TPS719xx

Submit Documentation Feedback

9

�TPS718xx

TPS719xx

SBVS088C – FEBRUARY 2007 – REVISED MAY 2008..................................................................................................................................................... www.ti.com

APPLICATION INFORMATION

The TPS718xx/TPS719xx belong to a family of new

generation LDO regulators that use innovative

circuitry to achieve ultra-wide bandwidth and high

loop gain, resulting in extremely high PSRR (up to

1MHz) at very low headroom (VIN – VOUT). These

features, combined with low noise, two independent

enables, low ground pin current and ultra-small

packaging, make this part ideal for portable

applications. This family of regulators offer

sub-bandgap output voltages, current limit and

thermal protection, and is fully specified from –40°C

to +125°C.

VIN

0.9V - 3.6V

IN

1mF

VOUT

OUT1

TPS718xx

1mF

TPS719xx

On

EN1

0.9V - 3.6V

Off

VOUT

OUT2

On

Off

To improve ac performance such as PSRR, output

noise, and transient response, it is recommended that

the board be designed with separate ground planes

for VIN and VOUT, with each ground plane connected

only at the GND pin of the device. In addition, the

ground connection for the output capacitor should

connect directly to the GND pin of the device. High

ESR capacitors may degrade PSRR.

Internal Current Limit

Figure 22 shows the basic circuit connections.

2.7V - 6.5V

Board Layout Recommendations to Improve

PSRR and Noise Performance

1m F

EN2

GND

Figure 22. Typical Application Circuit

The TPS718xx/TPS719xx internal current limits help

protect the regulator during fault conditions. During

current limit, the output sources a fixed amount of

current that is largely independent of output voltage.

For reliable operation, the device should not be

operated in a current limit state for extended periods

of time.

The PMOS pass element in the TPS718xx/TPS719xx

has a built-in body diode that conducts current when

the voltage at OUT exceeds the voltage at IN. This

current is not limited, so if extended reverse voltage

operation is anticipated, external limiting to 5% of

rated output current may be appropriate.

Shutdown

Input and Output Capacitor Requirements

Although an input capacitor is not required for

stability, it is good analog design practice to connect

a 0.1µF to 1.0µF low equivalent series resistance

(ESR) capacitor across the input supply near the

regulator. This capacitor counteracts reactive input

sources and improves transient response, noise

rejection, and ripple rejection. A higher-value

capacitor may be necessary if large, fast rise-time

load transients are anticipated or if the device is

located close to the power source. If source

impedance is not sufficiently low, a 0.1µF input

capacitor may be necessary to ensure stability.

The TPS718xx/TPS719xx are designed to be stable

with standard ceramic capacitors of values 1.0µF or

larger at the output. X5R- and X7R-type capacitors

are best because they have minimal variation in value

and ESR over temperature. Maximum ESR should be