TPS7B6333-Q1, TPS7B6350-Q1

TPS7B6333-Q1,

SLVSDU9B – FEBRUARY

2017 – REVISEDTPS7B6350-Q1

SEPTEMBER 2020

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

www.ti.com

TPS7B63xx-Q1

300-mA, 40-V High-Voltage, Ultra-Low-Quiescent-Current Watchdog LDO

1 Features

3 Description

•

In automotive microcontroller or microprocessor

power-supply applications, the watchdog is used to

monitor the microcontroller working status to prevent

software runaway. It is necessary for the watchdog to

be independent of the microcontroller in a reliable

system.

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

AEC-Q100 qualified for automotive applications:

– Temperature grade 1: –40°C to 125°C, TA

Maximum output current: 300 mA

4-V to 40-V wide VIN input-voltage range with up to

45-V transients

Fixed 3.3-V and 5-V outputs

Maximum dropout voltage: 400 mV at 300 mA

Stable with output capacitor in wide range of

capacitance (4.7 µF to 500 µF) and ESR (0.001 Ω

to 20 Ω)

Low quiescent current (I(Q)):

– < 4 µA when EN is low (shutdown mode)

– 19 µA typical at light loads with WD_EN high

(watchdog disabled)

Configurable for window watchdog or standard

watchdog

Open-to-closed window ratio configurable as 1:1 or

8:1

Fully adjustable watchdog period (from 10 ms to

500 ms)

10% accurate watchdog period

Dedicated WD_EN pin to control watchdog ONOFF

Fully adjustable power-good threshold and powergood delay period

Low input-voltage tracking to UVLO

Integrated fault protection

– Overload current-limit protection

– Thermal shutdown

Functional Safety-Capable

– Documentation available to aid functional safety

system design

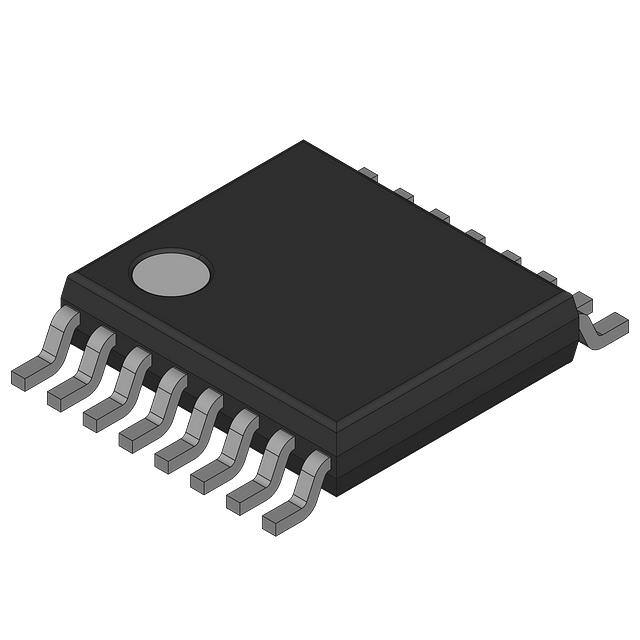

16-pin HTSSOP package

2 Applications

•

•

•

•

•

•

•

The TPS7B63xx-Q1 is a family of 300-mA watchdog

low-dropout regulators (LDOs) designed for an

operating voltage up to 40 V, with typical quiescent

current of only 19 µA at light load. The devices

integrate a programmable function for selecting a

window watchdog or standard watchdog, with an

external resistor to set the watchdog time within 10%

accuracy.

The PG pin on the TPS7B63xx-Q1 devices indicate

when the output voltage is stable and in regulation.

The power-good delay period and power-good

threshold can be adjusted by selecting external

components. The devices also feature integrated

short-circuit and overcurrent protection. The

combination of such features makes these devices

particularly flexible and suitable to supply

microcontroller in automotive applications.

Device Information

PART NUMBER (1)

Fixed 3.3 V

TPS7B6350-Q1

Fixed 5 V

(1)

PACKAGE

HTSSOP (16)

For all available packages, see the orderable addendum at

the end of the data sheet.

IN

Battery

OUT

MCU Supply

EN

RADJ

Digital Output

Automotive MCU power supplies

Body control modules (BCM)

Seat comfort modules

EV and HEV battery management systems (BMS)

Electronic gear shifters

Transmissions

Electrical power steering (EPS)

OUTPUT VOLTAGE

TPS7B6333-Q1

WD_EN

WD

TPS7B63xx-Q1

MCU O

WTS

WDO

PG

ROSC

FSEL

DELAY

WRS

MCU I

MCU RESET

Typical Application Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

Submit Document Feedback

Copyright

© 2020 Texas

Instruments

Incorporated

intellectual

property

matters

and other important disclaimers. PRODUCTION DATA.

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Pin Configuration and Functions...................................3

Pin Functions.................................................................... 3

6 Specifications.................................................................. 4

6.1 Absolute Maximum Ratings........................................ 4

6.2 ESD Ratings............................................................... 4

6.3 Recommended Operating Conditions.........................4

6.4 Thermal Information....................................................5

6.5 Electrical Characteristics.............................................5

6.6 Switching Characteristics............................................7

6.7 Typical Characteristics................................................ 8

7 Detailed Description......................................................12

7.1 Overview................................................................... 12

7.2 Functional Block Diagram......................................... 12

7.3 Feature Description...................................................12

7.4 Device Functional Modes..........................................19

8 Application and Implementation.................................. 20

8.1 Application Information............................................. 20

8.2 Typical Application.................................................... 20

9 Power Supply Recommendations................................23

10 Layout...........................................................................23

10.1 Layout Guidelines................................................... 23

10.2 Layout Example...................................................... 23

11 Device and Documentation Support..........................24

11.1 Documentation Support.......................................... 24

11.2 Receiving Notification of Documentation Updates.. 24

11.3 Support Resources................................................. 24

11.4 Trademarks............................................................. 24

11.5 Electrostatic Discharge Caution.............................. 24

11.6 Glossary.................................................................. 24

12 Mechanical, Packaging, and Orderable

Information.................................................................... 24

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision A (March 2017) to Revision B (September 2020)

Page

• Updated the numbering format for tables, figures, and cross-references throughout the document..................1

• Changed automotive-specific applications bullets in Features section...............................................................1

• Changed accurate watchdog period from 9% to 10% in Features section......................................................... 1

• Added Functional Safety-Capable bullets to Features section........................................................................... 1

• Changed accuracy from 9% to 10% in Description section................................................................................ 1

• Added ESD classification levels to ESD Ratings table....................................................................................... 4

• Changed VOUT parameter: added temperature range to test conditions of first parameter row and added

second row to parameter.................................................................................................................................... 5

• Changed V(dropout) maximum specification in second row of parameter from 260 mV to 325 mV...................... 5

• Changed t(DEGLITCH) minimum specification from 100 μs to 50 μs, changed t(DLY_FIX) maximum specification

from 550 μs to 900 μs, and deleted t(DLY_FIX) minimum specification................................................................. 7

• Changed fault 1 maximum open-window duration from t(WD) / 2 to t(WD) .........................................................18

Changes from Revision * (February 2017) to Revision A (March 2017)

Page

• Changed Typical Application Schematic ............................................................................................................1

• Changed Dropout Voltage vs Output Current graph...........................................................................................8

• Changed Load Regulation graph........................................................................................................................8

• Changed TPS7B63xx-Q1 Typical Application Schematic ................................................................................20

2

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

5 Pin Configuration and Functions

IN

1

16

OUT

EN

2

15

PGADJ

FSEL

3

14

PG

WTS

4

13

GND

Thermal

pad

GND

5

12

WRS

NC

6

11

WD_EN

ROSC

7

10

WDO

DELAY

8

9

WD

Not to scale

NC - No internal connection

Figure 5-1. PWP PowerPAD™ Package, 16-Pin HTSSOP With Exposed Thermal Pad, Top View

Pin Functions

PIN

NAME

NO.

I/O

DESCRIPTION

DELAY

8

O

Power-good delay-period adjustment pin. Connect this pin via a capacitor to ground to adjust the

power-good delay time.

EN

2

I

Device enable pin. Pull this pin down to low-level voltage to disable the device. Pull this pin up to

high-level voltage to enable the device.

FSEL

3

I

Internal oscillator-frequency selection pin. Pull this pin down to low-level voltage to select the

high-frequency oscillator. Pull this pin up to high-level voltage to select the low-frequency

oscillator.

GND

5, 13

—

IN

1

I

Ground reference

NC

6

—

OUT

16

O

Device 3.3-V or 5-V regulated output-voltage pin

Device input power supply pin

Not connected

PG

14

O

Power-good pin. Open-drain output pin. Pull this pin up to VOUT or to a reference through a

resistor. When the output voltage is not ready, this pin is pulled down to ground.

PGADJ

15

O

Power-good threshold-adjustment pin. Connect a resistor divider between the PGADJ and OUT

pins to set the power-good threshold. Connect this pin to ground to set the threshold to 91.6% of

output voltage VOUT.

ROSC

7

O

Watchdog timer adjustment pin. Connect a resistor between the ROSC pin and the GND pin to

set the duration of the watchdog monitor. Leaving this pin open or connecting this pin to ground

results in the watchdog reporting a fault at the watchdog output (WDO).

WD

9

I

Watchdog service-signal input pin.

WDO

10

O

Watchdog status pin. Open-drain output pin. Pull this pin up to OUT or a reference voltage

through a resistor. When watchdog fault occurs, this pin is pulled down to a low-level voltage.

WD_EN

11

I

Watchdog enable pin. Pull this pin down to a low level to enable the watchdog. Pull this pin up to

a high level to disable the watchdog.

WRS

12

I

Window ratio-selection pin (only applicable for the window watchdog). Pull this pin down to a low

level to set the open:closed window ratio to 1:1. Pull this pin up to high level to set the

open:closed window ratio to 8:1.

WTS

4

O

Watchdog type-selection pin. To set the window watchdog, connect this pin to the GND pin. To

set the standard watchdog, pull this pin high.

Thermal pad

—

—

Solder to board to improve the thermal performance.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

3

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

6 Specifications

6.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1) (2)

MIN

MAX

UNIT

Unregulated input

IN, EN

–0.3

45

V

Internal oscillator reference voltage

ROSC

–0.3

7

V

Power-good delay-timer output

DELAY

–0.3

7

V

Regulated output

OUT

–0.3

7

V

Power-good output voltage

PG

–0.3

7

V

Watchdog status output voltage

WDO

–0.3

7

V

Watchdog frequency selection, watchdog-type selection

FSEL, WTS

–0.3

45

V

Watchdog enable

WD_EN

–0.3

7

V

Watchdog service signal voltage

WD

–0.3

7

V

V

Window ratio selection

WRS

–0.3

7

Power-good threshold-adjustment voltage

PGADJ

–0.3

7

V

Operating junction temperature, TJ

–40

150

°C

Storage temperature, Tstg

–65

150

°C

(1)

(2)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under

Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

All voltage values are with respect to ground.

6.2 ESD Ratings

VALUE

V(ESD)

(1)

Electrostatic

discharge

Human-body model (HBM), per AEC

level 2

Q100-002(1),

device HBM ESD classification

Charged-device model (CDM), per AEC Q100-011,

device CDM ESD classification level C4B

UNIT

±2000

All pins

±500

Corner pins (1, 14, 15, and 28)

±750

V

AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.3 Recommended Operating Conditions

Over operating ambient temperature range (unless otherwise noted)

MIN

MAX

Unregulated input

IN

4

40

V

40-V pins

EN, FSEL, WTS

0

VIN

V

Regulated output

OUT

0

5.5

V

Power good, watchdog status,

reference oscillator

PG, WDO, ROSC

0

5.5

V

Low voltage pins

WD, WD_EN, PGADJ, DELAY, WRS

0

5.5

V

0

300

mA

–40

125

°C

Output current

Ambient temperature, TA

4

Submit Document Feedback

UNIT

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

6.4 Thermal Information

TPS7B63xx-Q1

THERMAL

METRIC(1)

UNIT

PWP (HTSSOP)

16 PINS

RθJA

Junction-to-ambient thermal resistance

39.7

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

28.9

°C/W

RθJB

Junction-to-board thermal resistance

23.8

°C/W

ψJT

Junction-to-top characterization parameter

1.3

°C/W

ψJB

Junction-to-board characterization parameter

23.7

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

3.1

°C/W

(1)

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

6.5 Electrical Characteristics

VIN = 14 V, COUT ≥ 4.7 µF, 1 mΩ < ESR < 20 Ω, and TJ = –40°C to 150°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

SUPPLY VOLTAGE AND CURRENT (IN)

VIN

Input voltage

I(SLEEP)

Input sleep current

I(Q)

V(UVLO)

4

EN = OFF

Input quiescent current

Undervoltage lockout, falling

40

V

4

µA

VIN = 5.6 V to 40 V for fixed 5-V VOUT;

VIN = 4 V to 40 V for fixed 3.3-V VOUT;

EN = ON; watchdog disabled; IOUT < 1 mA;

TJ < 80°C

19

29.6

VIN = 5.6 V to 40 V for fixed 5-V VOUT;

VIN = 4 V to 40 V for fixed 3.3-V VOUT;

EN = ON; watchdog enabled; IOUT < 1 mA

28

42

VIN = 5.6 V to 40 V for fixed 5-V VOUT;

VIN = 4 V to 40 V for fixed 3.3-V VOUT;

EN = ON; watchdog enabled;

IOUT < 100 mA

78

98

Ramp VIN down until output is turned off

2.6

V(UVLO_HYST) UVLO hysteresis

0.5

µA

V

V

ENABLE INPUT, WATCHDOG TYPE SELECTION AND FSEL (EN, WTS, AND FSEL)

VIL

Low-level input voltage

VIH

High-level input voltage

Vhys

Hysteresis

0.7

2

V

V

150

mV

WATCHDOG ENABLE (WD_EN PIN)

VIL

Low-level input threshold voltage

for watchdog enable pin

VIH

High-level input threshold voltage

Watchdog disabled

for watchdog enable pin

IWD_EN

Pulldown current for watchdog

enable pin

Watchdog enabled

0.7

2

VWD_EN = 5 V

V

V

3

µA

REGULATED OUTPUT (OUT)

VOUT

ΔVOUT(ΔVIN)

Regulated output

Line regulation

VIN = 5.6 V to 40 V for fixed 5-V VOUT,

VIN = 4 V to 40 V for fixed 3.3-V VOUT,

IOUT = 0 to 300 mA, –40°C ≤ TJ ≤ 125°C

VIN = 5.6 V to 40 V for fixed 5-V VOUT;

VIN = 4 V to 40 V for fixed 3.3-V VOUT;

IOUT = 0 to 300 mA

VIN = 5.6 V to 40 V

–2%

2%

–2.5%

2.5%

10

mV

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

5

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

VIN = 14 V, COUT ≥ 4.7 µF, 1 mΩ < ESR < 20 Ω, and TJ = –40°C to 150°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

ΔVOUT(ΔIOUT) Load regulation

400

170

325

Output current

VOUT in regulation

Output current limit

VOUT shorted to ground, VIN = 5.6 V to

40 V

Power-supply ripple

20

300

IOUT

rejection(1)

MAX

IOUT = 200 mA(2)

IOUT = 300

Dropout voltage (VIN – VOUT)

PSRR

TYP

mA(2)

V(dropout)

I(LIM)

MIN

IOUT = 1 mA to 300 mA

0

301

680

IOUT = 100 mA; COUT = 10 µF;

frequency (f) = 100 Hz

60

IOUT = 100 mA; COUT = 10 µF;

frequency (f) = 100 kHz

40

UNIT

mV

mV

300

mA

1000

mA

dB

POWER-GOOD (PG, PGADJ)

VOL(PG)

PG output, low voltage

IOL = 5 mA, PG pulled low

Ilkg(PG)

PG pin leakage current

PG pulled to VOUT through a 10-kΩ resistor

V(PG_TH)

Default power-good threshold

VOUT powered above the internally set

tolerance, PGADJ pin shorted to ground

V(PG_HYST)

Power-good hysteresis

VOUT falling below the internally set

tolerance hysteresis

Switching voltage for the powergood adjust pin

VOUT is falling

0.4

1

89.6

91.6

93.6

V

µA

% of

VOUT

% of

VOUT

2

PGADJ

V(PGADJ_TH)

1.067

1.1

1.133

V

3

5

10

µA

0.95

1

1.05

V

POWER-GOOD DELAY

I(DLY_CHG)

DELAY capacitor charging current

V(DLY_TH)

DELAY pin threshold to release

PG high

Voltage at DELAY pin is ramped up

I(DLY_DIS)

DELAY capacitor discharging

current

VDELAY = 1 V

0.5

mA

CURRENT VOLTAGE REFERENCE (ROSC)

VROSC

Voltage reference

0.95

1

1.05

V

WATCHDOG (WD, WDO, WRS)

VIL

Low-level threshold voltage for

the watchdog input and windowratio select

For WD and WRS pins

VIH

High-level threshold voltage for

the watchdog input and windowratio select

For WD and WRS pins

V(HYST)

Hysteresis

IWD

Pulldown current for the WD pin

VWDO = 5 V

VOL

Low-levlel watchdog output

IWDO = 5 mA

Ilkg

WDO pin leakage current

WDO pin pulled to VOUT through 10-kΩ

resistor

30

% of

VOUT

% of

VOUT

70

% of

VOUT

10

2

4

µA

0.4

V

1

µA

150

°C

OPERATING TEMPERATURE RANGE

TJ

–40

T(SD)

Junction shutdown temperature

175

°C

T(HYST)

Hysteresis of thermal shutdown

25

°C

(1)

(2)

6

Junction temperature

Design information – not tested, determined by characterization.

This test is done with VOUT in regulation, measuring the VIN – VOUT when VOUT drops by 100 mV from the rated output voltage at the

specified load.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

6.6 Switching Characteristics

VI = 14 V, CO ≥ 4.7 µF, 1 mΩ < ESR < 20 Ω, and TJ = –40°C to 150°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

50

180

250

µs

248

900

POWER-GOOD DELAY (DELAY)

t(DEGLITCH)

Power-good deglitch time

t(DLY_FIX)

Fixed power-good delay

No capacitor connect at DELAY pin

t(DLY)

Power-on-reset delay

Delay capacitor value: C(DELAY) = 100 nF

20

µs

ms

WATCHDOG (WD, WDO, WRS)

t(WD)

Watchdog window duration

t(WD_TOL)

Tolerance of watchdog window

duration using external resistor

tp(WD)

Watchdog service-signal duration

t(WD_HOLD)

Watchdog output resetting time

(percentage of settled watchdog

window duration)

t(WD_RESET)

Watchdog output resetting time

R(ROSC) = 20 kΩ ±1%, FSEL = LOW

9

10

11

R(ROSC) = 20 kΩ ±1%, FSEL = HIGH

45

50

55

Excludes tolerance of R(ROSC) = 20 kΩ to

100 kΩ

–10%

ms

10%

100

µs

20

% of t(WD)

R(ROSC) = 20 kΩ ± 1%, FSEL = LOW

1.8

2

2.2

R(ROSC) = 20 kΩ ± 1%, FSEL = HIGH

9

10

11

ms

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

7

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

6.7 Typical Characteristics

VIN = 14 V, VEN ≥ 2 V, TJ = –40°C to 150°C unless otherwise noted

80

400

40 °C

25 °C

125 °C

IOUT = 1 mA

IOUT = 100 mA

IOUT = 200 mA

350

60

Quiescent Current (PA)

Quiescent Current (PA)

70

50

40

30

20

10

300

250

200

150

100

50

0

0

0

50

100

150

200

Output Current (mA)

250

300

0

5

10

15

20

25

Input Voltage (V)

D001

Figure 6-1. Quiescent Current vs Output Current

30

35

40

D002

Figure 6-2. Quiescent Current vs Input Voltage

4

35

Quiescent Current (PA)

Shudown Current (PA)

30

3

2

1

25

20

IOUT = 1 mA

IOUT = 100 mA

15

10

5

0

-40

-25

-10

5

20 35 50 65 80

Ambient Temperature (qC)

95

0

-40

110 125

Figure 6-3. Shutdown Current vs Ambient

Temperature

-10

5

20 35 50 65 80

Ambient Temperature (°C)

95

110 125

D004

Figure 6-4. Quiescent Current vs Ambient

Temperature

300

350

40 °C

25 °C

125 °C

250

Dropout Voltage (mV)

300

250

Dropout Voltage (mV)

-25

D003

200

150

100

200

150

100

50

50

0

0

50

100

150

200

250

Output Current (mA)

300

350

D005

0

-40

-25

-10

5

20 35 50 65 80

Ambient Temperature (°C)

95

110 125

D006

IOUT = 200 mA

Figure 6-5. Dropout Voltage vs Output Current

8

Figure 6-6. Dropout Voltage vs Ambient

Temperature

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

6

5.06

5

Output Voltage (V)

Output Voltage (V)

5.03

5

4.97

4

3

2

-40qC

25qC

125qC

1

4.94

-40

-25

-10

5

20 35 50 65 80

Ambient Temperature (°C)

95

0

110 125

0

5

10

15

20

25

Input Voltage (V)

D007

VOUT = 5 V

30

35

40

D008

VOUT = 5 V

Figure 6-7. Output Voltage vs Ambient

Temperature

Figure 6-8. Output Voltage vs Input Voltage

900

1

0.8

0.6

Line Regulation (%)

Current Limit (mA)

800

700

600

0.4

0.2

0

-0.2

-0.4

-0.6

40 °C

25 °C

125 °C

-0.8

500

-40

-1

-25

-10

5

20 35 50 65 80

Ambient Temperature (°C)

95

0

110 125

50

100

D009

150

200

250

Output Current (mA)

300

350

D010

VIN = 5.6 V

Figure 6-10. Load Regulation

Figure 6-9. Output Current Limit (ILIM) vs Ambient

Temperature

120

1

-40qC

25qC

125qC

0.8

100

0.4

80

PSRR (dB)

Line Regulation (%)

0.6

0.2

0

-0.2

60

40

-0.4

-0.6

20

-0.8

-1

0

5

10

15

20

25

Input Voltage (V)

30

35

40

0

10

100

D011

1k

10k

100k

Frequency (Hz)

1M

10M

D012

COUT = 10 μF, IOUT = 1 mA, TA = 25°C

Figure 6-11. Line Regulation

Figure 6-12. PSRR vs Frequency

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

9

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

120

1k

Unstable Region

500

Output Capacitance (µF)

100

PSRR (dB)

80

60

40

20

100

Stable Region

10

4.7

Unstable Region

0

10

100

1k

10k

100k

Frequency (Hz)

1M

10M

1

0.001

0.01

D013

0.1

ESR (W)

1

10 20

D014

COUT = 10 μF, IOUT = 100 mA, TA = 25°C

Figure 6-13. PSRR vs Frequency

Figure 6-14. ESR Stability vs Output Capacitance

VIN (10 V/div)

VOUT (1 V/div)

VOUT (1 V/div)

VIN (10 V/div)

VOUT(AC) (100 mV/div)

VOUT(AC) (100 mV/div)

IOUT (10 mA/div)

IOUT (10 mA/div)

VIN = 6 V to 40 V, VOUT = 5 V, COUT = 10 µF, IOUT = 1 mA

Figure 6-15. Line Transient

VIN = 40 V to 6 V, VOUT = 5 V, COUT = 10 µF, IOUT = 1 mA

Figure 6-16. Line Transient

VIN (5 V/div)

VIN (5 V/div)

VOUT (1 V/div)

VOUT (1 V/div)

VOUT(AC) (50 mV/div)

VOUT(AC) (50 mV/div)

IOUT (200 mA/div)

IOUT (200 mA/div)

VIN = 6 V to 40 V, VOUT = 5 V, COUT = 10 µF, IOUT = 200 mA

Figure 6-17. Line Transient

10

VIN = 40 V to 6 V, VOUT = 5 V, COUT = 10 µF, IOUT = 200 mA

Figure 6-18. Line Transient

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

VIN (5 V/div)

VIN (5 V/div)

VOUT (1 V/div)

VOUT (1 V/div)

VOUT(AC) (500 mV/div)

VOUT(AC) (500 mV/div)

IOUT (200 mA/div)

IOUT (200 mA/div)

VOUT = 5 V, COUT = 10 µF, IOUT = 1 mA to 200 mA

Figure 6-19. Load Transient

VOUT = 5 V, COUT = 10 µF, IOUT = 200 mA to 1 mA

Figure 6-20. Load Transient

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

11

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

7 Detailed Description

7.1 Overview

The TPS7B63xx-Q1 device is a family of 300-mA, 40-V monolithic low-dropout linear voltage regulators with

integrated watchdog and adjustable power-good threshold functionality. These voltage regulators consume only

19-µA quiescent current in light-load applications. Because of the adjustable power-good delay (also called

power-on-reset delay) and the adjustable power-good threshold, these devices are well-suited as power supplies

for microprocessors and microcontrollers in automotive applications.

7.2 Functional Block Diagram

IN

OUT

VREG

VBAT

Overcurrent

Protection

Regulator

Control

Undervoltage

Lockout

Band Gap

Thermal

Shutdown

Error

Amp

Vref

EN

PG

DELAY

Power-Good

Control With

Delay

ROSC

Current

Regulator

V(PG_REF )

Watchdog

Oscillator

Amp

PGADJ

WD

MCU I/O

Timer

WD_EN

WDO

Digital I/O

Watchdog

Fault Control

GND

FSEL

WTS

WRS

7.3 Feature Description

7.3.1 Device Enable (EN)

The EN pin is a high-voltage-tolerant pin. A high input activates the device and turns the regulator ON. Connect

this input pin to an external microcontroller or a digital control circuit to enable and disable the device, or connect

to the IN pin for self-bias applications.

12

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

7.3.2 Adjustable Power-Good Threshold (PG, PGADJ)

The PG pin is an open-drain output with an external pullup resistor to the regulated supply, and the PGADJ pin is

a power-good threshold adjustment pin. Connecting the PGADJ pin to GND sets the power-good threshold value

to the default, V(PG_TH). When VOUT exceeds the default power-good threshold, the PG output turns high after

the power-good delay period has expired. When VOUT falls below V(PG_TH) – V(PG_HYST), the PG output turns low

after a short deglitch time.

The power-good threshold is also adjustable from 1.1 V to 5 V by using an external resistor divider between

PGADJ and OUT. The threshold can be calculated using Equation 1:

V PG _ ADJ

falling

V PGADJ _ TH

falling

V PG _ ADJ

risng

ªV

¬ PGADJ _ TH

falling

u

R1 R2

R2

R1 R2

26 mV typ º u

¼

R2

(1)

where

•

•

V(PG_ADJ) is the adjustable power-good threshold

V(PG_REF) is the internal comparator reference voltage of the PGADJ pin, 1.1 V typical, 2% accuracy specified

under all conditions

By setting the power-good threshold V(PG_ADJ), when VOUT exceeds this threshold, the PG output turns high after

the power-good delay period has expired. When VOUT falls below V(PG_ADJ) – V(PG_HYST), the PG output turns

low after a short deglitch time. Figure 7-1 shows typical hardware connections for the PGADJ pin and DELAY

pin.

OUT

VREG

Adjustable PowerGood Threshold

PG

R1

DELAY

Power-Good

Control

R2

V(PG_REF)

Amp

PGADJ

Figure 7-1. Adjustable Power-Good Threshold

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

13

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

7.3.3 Adjustable Power-Good Delay Timer (DELAY)

The power-good delay period is a function of the value set by an external capacitor on the DELAY pin before

turning the PG pin high. Figure 7-2 illustrates typical power-good and delay behavior. Connecting an external

capacitor from this pin to GND sets the power-good delay period. The constant current charges an external

capacitor until the voltage exceeds a threshold to trip an internal comparator, and Equation 2 determines the

power-good delay period:

P:&.;; = P@HU _BET +

%&'.#; T 18

5 ä#

(2)

where

•

•

t(DLY) is the adjustable power-good delay period

CDELAY is the value of the power-good delay capacitor

VIN

V(UVLO)

t < t(DEGLITCH)

VOUT

V(PG_HYST)

V(PG_TH) rising

V(PG_ADJ) rising

DELAY

V(PG_TH) falling

V(PG_ADJ) falling

V(DLY _TH)

t(DEGLITCH)

t(DLY )

t(DEGLITCH)

t(DLY )

PG

Power Up

Input Voltage Drop

Undervoltage

Power Down

Figure 7-2. Power Up and Conditions for Activating Power-Good

If the DELAY pin is open, the default delay time is t(DLY_FIX).

7.3.4 Undervoltage Shutdown

These devices have an integrated undervoltage lockout (UVLO) circuit to shut down the output if the input

voltage falls below an internal UVLO threshold, V(UVLO). This ensures that the regulator does not latch into an

unknown state during low-input-voltage conditions. If the input voltage has a negative transient which drops

below the UVLO threshold and recovers, the regulator shuts down and powers up with a normal power-up

sequence once the input voltage is above the required level.

7.3.5 Current Limit

These devices feature current-limit protection to keep the device in a safe operating area when an overload or

output short-to-ground condition occurs. This protects devices from excessive power dissipation. For example,

during a short-circuit condition on the output, fault protection limits the current through the pass element to I(LIM)

to protect the device from excessive power dissipation.

7.3.6 Thermal Shutdown

These devices incorporate a thermal shutdown (TSD) circuit as a protection from overheating. For continuous

normal operation, the junction temperature should not exceed the TSD trip point. The junction temperature

exceeding the TSD trip point causes the output to turn off. When the junction temperature falls below the T(SD) –

T(HYST), the output turns on again.

14

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

7.3.7 Integrated Watchdog

These devices have an integrated watchdog with fault (WDO) output option. Both window watchdog and

standard watchdog are available in one device. The watchdog operation, service fault conditions, and

differences between window watchdog and standard watchdog are described as follows.

7.3.7.1 Window Watchdog (WTS, ROSC, FSEL and WRS)

These devices work in the window watchdog mode when the watchdog type selection (WTS) pin is connected to

a to low voltage level. The user can set the duration of the watchdog window by connecting an external resistor

(RROSC) to ground at the ROSC pin and setting the voltage level at the FSEL pin. The current through the RROSC

resistor sets the clock frequency of the internal oscillator. The user can adjust the duration of the watchdog

window (the watchdog timer period) by changing the resistor value. A high voltage level at the FSEL pin sets the

watchdog window duration to 5 times as long as that of a low voltage level with same external component

configuration.

The duration of the watchdog window and the duration of the fault output are multiples of the internal oscillator

frequency, as shown by the following equations:

FSEL low

t(WD) = RROSC × 0.5 × 10-6

(3)

FSEL high

t(WD) = RROSC × 2.5 × 10-6

(4)

t(WD_INI) = 8 × t(WD)

(5)

t(WD) = t(OW) + t(CW)

(6)

t(OW) = t(CW) = 50% × t(WD)

(7)

t(OW) = 8 × t(CW) = (8 / 9) × t(WD)

(8)

Watchdog initialization

Open and closed windows

WRS low

WRS high

where:

• t(WD) is the duration of the watchdog window

• RROSC is the resistor connected at the ROSC pin

• t(WD_INI) is the duration of the watchdog initialization

• t(OW) is the duration of the open watchdog window

• t(CW) is the duration of the closed watchdog window

For all the foregoing items, the unit of resistance is Ω and the unit of time is s.

Table 7-1 illustrates several periods of watchdog window with typical conditions.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

15

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

Table 7-1. Several Typical Periods of Watchdog Window

FSEL

High

Low

R(ROSC) (kΩ)

I(ROSC) (µA)

t(WD) (ms)

WATCHDOG PERIOD

TOLERANCE

200

5

500

15%

100

10

250

50

20

125

40

25

100

25

40

62.5

10%

20

50

50

100

10

50

50

20

25

40

25

20

25

40

12.5

20

50

10

10%

As illustrated in Figure 7-3, each watchdog window consists of an open window and a closed window. While the

window ratio selection (WRS) pin is low, each open window (t(OW)) and closed window (t (CW)) has a width

approximately 50% of the watchdog window (t (WD)). While the WRS pin is high, the ratio between open window

and closed window is about 8:1. However, there is an exception to this; the first open window after watchdog

initialization (t(WD_INI)) is eight times the duration of the watchdog window. The watchdog must receive the

service signal (by software, external microcontroller, and so forth) during this initialization open window.

A watchdog fault occurs when servicing the watchdog during a closed window, or not servicing during an open

window.

t(WD_INI)

WRS = Low

t(WD)

Open Window

Closed Window

Open Window

After Watchdog Initialization

(Must Be Serviced to Prevent Fault)

(Must Not Be Serviced

to Prevent Fault)

(Must Be Serviced

to Prevent Fault)

8 ´ t(WD)

t(CW) = ½ ´ t(WD)

t(OW) = ½ ´ t(WD)

Open Window

WRS = High

After Watchdog Initialization

(Must Be Serviced to Prevent Fault)

Open Window

CW

(Must Be Serviced

to Prevent Fault)

t(OW) = 8 / 9 ´ t(WD)

8 ´ t(WD)

Closed Window

Event Causing

Watchdog Initialization

(Must Not Be Serviced

to Prevent Fault)

t(CW) = 1 / 9 ´ t(WD)

Figure 7-3. Watchdog Initialization, Open Window and Closed Window

7.3.7.2 Standard Watchdog (WTS, ROSC and FSEL)

These devices work in the standard watchdog mode when the watchdog type selection (WTS) pin is connected

to a high voltage level. The same as in window watchdog mode, the user can set the duration of the watchdog

window by adjusting the external resistor (RROSC) value at the ROSC pin and setting the voltage level at the

FSEL pin. The current through the RROSC resistor sets the clock frequency of the internal oscillator. The user can

adjust the duration of the watchdog window (the watchdog timer period) by changing the resistor value. A high

voltage level at the FSEL pin sets the watchdog window duration to 5 times as long as that of a low voltage level

with same external component configuration.

16

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

The duration of the watchdog window and the duration of the fault output are multiples of the internal oscillator

frequency, as shown by the following equations:

FSEL low

t(WD) = RROSC × 0.5 × 10-6

(9)

FSEL high

t(WD) = RROSC × 2.5 × 10-6

(10)

t(WD_INI) = 8 × t(WD)

(11)

Watchdog initialization

where:

•

•

•

t(WD) is the duration of the watchdog window

RROSC is the resistor connected at the ROSC pin

t(WD_INI) is the duration of the watchdog initialization

For all the foregoing items, the unit of resistance is Ω and the unit of time is s

Compared with window watchdog, there is no closed window in standard watchdog mode. The standard

watchdog receives a service signal at any time within the watchdog window. The watchdog fault occurs when not

servicing watchdog during the watchdog window.

7.3.7.3 Watchdog Service Signal and Watchdog Fault Outputs (WD and WDO)

The watchdog service signal (WD) must stay high for at least 100 µs. The WDO pin is the fault output terminal

and is tied high through a pullup resistor to a regulated output supply. When a watchdog fault occurs, the devices

momentarily pull WDO low for a duration of t(WD_HOLD).

t (WD _ HOLD) = 20% ´ t (WD)

(12)

7.3.7.4 ROSC Status Detection (ROSC)

When a watchdog function is enabled, if the ROSC pin is shorted to GND or open, the watchdog output (WDO)

pin remains low, indicating a fault status. If the watchdog function is disabled, ROSC pin status detection does

not work.

7.3.7.5 Watchdog Enable (PG and WD_EN)

When PG (power good) is high, an external microcontroller or a digital circuit can apply a high or low logic signal

to the WD_EN pin to disable or enable the watchdog. A low input to this pin turns the watchdog on, and a high

input turns the watchdog off. If PG is low, the watchdog is disabled and the watchdog-fault output (WDO) pin

stays in the high-impedance state.

7.3.7.6 Watchdog Initialization

On power up and during normal operation, the watchdog initializes under the conditions shown in Table 7-2.

Table 7-2. Conditions for Watchdog Initialization

EDGE

WHAT CAUSES THE WATCHDOG TO INITIALIZE

↑

Rising edge of PG (power good) while the watchdog is in the enabled state, for example,

during soft power up

↓

Falling edge of WD_EN while PG is already high, for example, when the microprocessor

enables the watchdog after the device is powered up

↑

Rising edge of WDO while PG is already high and the watchdog is in the enabled state, for

example, right after a closed window is serviced

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links: TPS7B6333-Q1 TPS7B6350-Q1

17

�TPS7B6333-Q1, TPS7B6350-Q1

www.ti.com

SLVSDU9B – FEBRUARY 2017 – REVISED SEPTEMBER 2020

7.3.7.7 Window Watchdog Operation (WTS = Low)

The window watchdog is able to monitor whether the frequency of the watchdog service signal (WD) is within

certain ranges. A watchdog low-voltage fault is reported when the frequency of the watchdog service signal is

out of the setting range. Figure 7-4 shows the window watchdog initialization and operation for the TPS7B63xxQ1 (WRS is low). After the output voltage is in regulation and PG is high, the window watchdog becomes

enabled when an external signal pulls WD_EN (the watchdog enable pin) low. This causes the watchdog to

initialize and wait for a service signal during the first initialization window for 8 times the duration of t(WD). A

service signal applied to the WD pin during the initialization open window resets the watchdog counter and a

closed window starts. To prevent a fault condition from occurring, watchdog service must not occur during the

closed window. Watchdog service must occur during the following open window to prevent a fault condition from

occurring. The fault output (WDO), externally pulled up to VOUT (typical), stays high as long as the watchdog

receives a proper service signal and there is no other fault condition.

VIN

VOUT

DELAY

V(PG_TH) rising

V(PG_ADJ) rising

)

V(PG_TH) falling

V(PG_ADJ) falling

V(DLY_TH)

t(DLY)

t(DLY)

PG

t(DEGLITCH)

WD_EN

WD

NA

OW

WD Initialization

CW

OW

F

CW L

T