Product

Folder

Order

Now

Technical

Documents

Support &

Community

Tools &

Software

UCC27524A1-Q1

SLVSDH6 – APRIL 2017

UCC27524A1-Q1 Dual 5-A, High-Speed, Low-Side Gate Driver

With Negative Input Voltage Capability

1 Features

3 Description

•

•

The UCC27524A1-Q1 device is a dual-channel, highspeed, low-side, gate-driver device capable of

effectively driving MOSFET and IGBT power

switches. The UCC27524A1-Q1 device is a variant of

the UCC2752x family. The UCC27524A1-Q1 device

adds the ability to handle –5 V directly at the input

pins for increased robustness. The UCC27524A1-Q1

device is a dual, non-inverting driver. Using a design

that inherently minimizes shoot-through current, the

UCC27524A1-Q1 device is capable of delivering

high-peak current pulses of up to 5-A source and 5-A

sink into capacitive loads along with rail-to-rail drive

capability and extremely small propagation delay

(typically 13 ns). In addition, the drivers feature

matched, internal-propagation delays between the

two channels which are very well suited for

applications requiring dual-gate drives with critical

timing, such as synchronous rectifiers. This also

enables connecting two channels in parallel to

effectively increase current-drive capability or driving

two switches in parallel with a single input signal. The

input pin thresholds are based on TTL and CMOS

compatible low-voltage logic, which is fixed and

independent of the VDD supply voltage. Wide

hysteresis between the high and low thresholds offers

excellent noise immunity.

1

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Qualified for Automotive Applications

AEC-Q100 Qualified With the Following Results:

– Device Temperature Grade 1

– Device HBM ESD Classification Level H2

– Device CDM ESD Classification Level C4B

Industry-Standard Pin Out

Two Independent Gate-Drive Channels

5-A Peak Source and Sink-Drive Current

Independent Enable Function for Each Output

TTL and CMOS-Compatible Logic Threshold

Independent of Supply Voltage

Hysteretic-Logic Thresholds for High-Noise

Immunity

Ability to Handle Negative Voltages (–5 V) at

Inputs

Inputs and Enable Pin-Voltage Levels Not

Restricted by VDD Pin Bias Supply Voltage

4.5-V to 18-V Single-Supply Range

Outputs Held Low During VDD-UVLO, (Ensures

Glitch-Free Operation at Power-Up and PowerDown)

Fast Propagation Delays (13-ns typical)

Fast Rise and Fall Times (7-ns and 6-ns Typical)

1-ns Typical Delay Matching Between 2-Channels

Ability to Parallel Two Outputs for High-Drive

Current

Outputs Held in LOW When Inputs are Floating

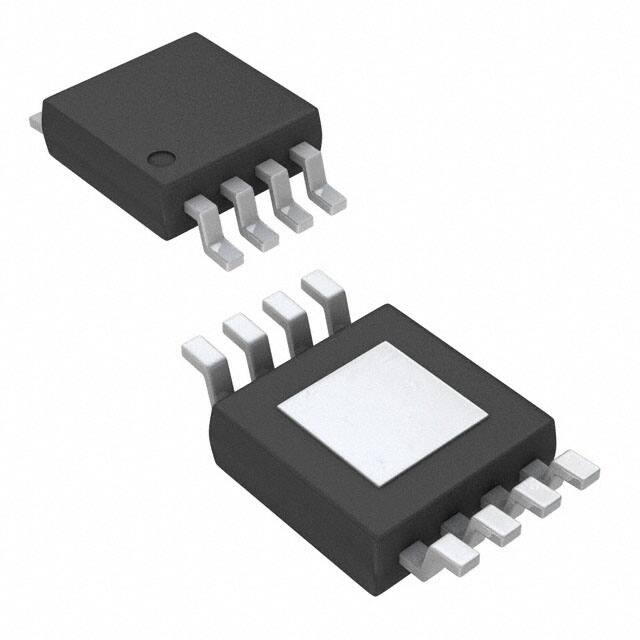

MSOP-8 PowerPad™ Package

Operating Temperature Range of –40°C to

+140°C

2 Applications

•

•

•

•

•

Automotive

Switch-Mode Power Supplies

DC-to-DC Converters

Motor Control, Solar Power

Gate Drive for Emerging Wide Band-Gap Power

Devices Such as GaN

Device Information(1)

PART NUMBER

PACKAGE

BODY SIZE (NOM)

UCC27524A1-Q1 MSOP-PowerPAD (8)

3.00 mm × 3.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Dual Non-Inverting Inputs

UCC27524A1-Q1

ENA

1

8

ENB

INA

2

7

OUTA

GND

3

6

VDD

INB

4

5

OUTB

Copyright © 2016, Texas Instruments Incorporated

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�UCC27524A1-Q1

SLVSDH6 – APRIL 2017

www.ti.com

Table of Contents

1

2

3

4

5

6

7

8

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Description (continued).........................................

Pin Configuration and Functions .........................

Specifications.........................................................

1

1

1

2

3

4

5

7.1

7.2

7.3

7.4

7.5

7.6

7.7

5

5

5

5

6

6

8

Absolute Maximum Ratings ......................................

ESD Ratings ............................................................

Recommended Operating Conditions.......................

Thermal Information ..................................................

Electrical Characteristics...........................................

Switching Characteristics ..........................................

Typical Characteristics ..............................................

8.3 Feature Description................................................. 12

8.4 Device Functional Modes........................................ 17

9

Application and Implementation ........................ 18

9.1 Application Information............................................ 18

9.2 Typical Application .................................................. 18

10 Power Supply Recommendations ..................... 22

11 Layout................................................................... 23

11.1 Layout Guidelines ................................................. 23

11.2 Layout Example .................................................... 24

11.3 Thermal Considerations ........................................ 24

12 Device and Documentation Support ................. 25

12.1

12.2

12.3

12.4

Detailed Description ............................................ 11

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

25

25

25

25

13 Mechanical, Packaging, and Orderable

Information ........................................................... 25

8.1 Overview ................................................................. 11

8.2 Functional Block Diagram ....................................... 12

4 Revision History

2

DATE

REVISION

NOTES

April 2017

*

Initial release.

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

�UCC27524A1-Q1

www.ti.com

SLVSDH6 – APRIL 2017

5 Description (continued)

For protection purposes, internal pull-up and pull-down resistors on the input pins of the UCC27524A1-Q1 device

ensure that outputs are held LOW when input pins are in floating condition. The UCC27524A1-Q1 device

features enable pins (ENA and ENB) to have better control of the operation of the driver applications. The pins

are internally pulled up to VDD for active-high logic and are left open for standard operation.

The UCC27524A1-Q1 devices is available in a MSOP-PowerPAD-8 with exposed pad (DGN) package.

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

3

�UCC27524A1-Q1

SLVSDH6 – APRIL 2017

www.ti.com

6 Pin Configuration and Functions

DGN Package

8-Pin MSOP-PowerPAD

Top View

ENA

1

8

ENB

INA

2

7

OUTA

GND

3

6

VDD

INB

4

5

OUTB

Pin Functions

PIN

NAME

NO.

I/O

DESCRIPTION

ENA

1

I

Enable input for Channel A: ENA is biased LOW to disable the Channel A output regardless of the INA state.

ENA is biased HIGH or left floating to enable the Channel A output. ENA is allowed to float; hence the pinto-pin compatibility with the UCC2732X N/C pin.

ENB

8

I

Enable input for Channel B: ENB is biased LOW to disables the Channel B output regardless of the INB

state. ENB is biased HIGH or left floating to enable Channel B output. ENB is allowed to float hence; the pinto-pin compatibility with the UCC2752A N/C pin.

GND

3

-

Ground: All signals are referenced to this pin.

INA

2

I

Input to Channel A: INA is the non-inverting input in the UCC27524A1-Q1 device. OUTA is held LOW if INA

is unbiased or floating.

INB

4

I

Input to Channel B: INB is the non-inverting input in the UCC27524A1-Q1 device. OUTB is held LOW if INB

is unbiased or floating.

OUTA

7

O

Output of Channel A

OUTB

5

O

Output of Channel B

VDD

6

I

Bias supply input

4

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

�UCC27524A1-Q1

www.ti.com

SLVSDH6 – APRIL 2017

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

Supply voltage

OUTA, OUTB voltage

MIN

MAX

UNIT

VDD

–0.3

20

V

DC

–0.3

VDD + 0.3

V

–2

VDD + 0.3

V

0.3

A

5

A

Repetitive pulse < 200 ns (2)

Output continuous source/sink current

IOUT_DC

Output pulsed source/sink current (0.5 µs) IOUT_pulsed

INA, INB, ENA, ENB voltage (3)

–5

20

V

Operating virtual junction temperature, TJ

–40

150

°C

Storage temperature, Tstg

–65

150

°C

(1)

(2)

(3)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Values are verified by characterization on bench.

The maximum voltage on the Input and Enable pins is not restricted by the voltage on the VDD pin.

7.2 ESD Ratings

VALUE

V(ESD)

(1)

Electrostatic discharge

Human-body model (HBM), per AEC Q100-002 (1)

±2000

Charged-device model (CDM), per AEC Q100-011

±750

UNIT

V

AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

Supply voltage, VDD

4.5

12

18

UNIT

V

Operating junction temperature

–40

140

°C

Input voltage, INA, INB

–2

18

V

Enable voltage, ENA and ENB

–2

18

V

7.4 Thermal Information

UCC27524A1-Q1

THERMAL METRIC

(1)

HVSSOP (DGN)

UNIT

8 PINS

RθJA

Junction-to-ambient thermal resistance

71.8

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

65.6

°C/W

RθJB

Junction-to-board thermal resistance

7.4

°C/W

ψJT

Junction-to-top characterization parameter

7.4

°C/W

ψJB

Junction-to-board characterization parameter

31.5

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

19.6

°C/W

(1)

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

5

�UCC27524A1-Q1

SLVSDH6 – APRIL 2017

www.ti.com

7.5 Electrical Characteristics

VDD = 12 V, TA = TJ = –40 °C to 140 °C, 1-µF capacitor from VDD to GND. Currents are positive into, negative out of the

specified terminal (unless otherwise noted,)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

VDD = 3.4 V, INA = VDD, INB = VDD

55

110

175

VDD = 3.4 V, INA = GND, INB = GND

25

75

145

3.91

4.2

4.5

3.7

4.2

4.65

UNIT

BIAS CURRENTS

Startup current,

(based on UCC27524 Input

configuration)

IDD(off)

μA

UNDER VOLTAGE LOCKOUT (UVLO)

TJ = 25 °C

VON

Supply start threshold

VOFF

Minimum operating voltage

after supply start

3.4

3.9

4.4

V

VDD_H

Supply voltage hysteresis

0.2

0.3

0.5

V

1.9

2.1

2.3

V

1

1.2

1.4

V

0.7

0.9

1.1

V

TJ = –40 °C to 140 °C

V

INPUTS (INA, INB, INA+, INA–, INB+, INB–), UCC27524A1-Q1 (DGN)

VIN_H

Input signal high threshold

Output high for non-inverting input pins

Output low for inverting input pins

VIN_L

Input signal low threshold

Output low for non-inverting input pins

Output high for inverting input pins

VIN_HYS

Input hysteresis

OUTPUTS (OUTA, OUTB)

ISNK/SRC

Sink/source peak current (1)

CLOAD = 0.22 µF, FSW = 1 kHz

VDD-VOH

High output voltage

IOUT = –10 mA

VOL

Low output voltage

IOUT = 10 mA

0.01

V

ROH

Output pullup resistance (2)

IOUT = –10 mA

2.5

5

7.5

Ω

ROL

Output pulldown resistance

IOUT = 10 mA

0.15

0.5

1

Ω

(1)

(2)

±5

A

0.075

V

Ensured by design.

ROH represents on-resistance of only the P-Channel MOSFET device in the pullup structure of the UCC27524A1-Q1 output stage.

7.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

PARAMETER

TEST CONDITIONS

(1)

MIN

TYP

MAX

UNIT

tR

Rise time

CLOAD = 1.8 nF

7

18

ns

tF

Fall time (1)

CLOAD = 1.8 nF

6

10

ns

tM

Delay matching between 2 channels

INA = INB, OUTA and OUTB at 50%

transition point

1

4

ns

tPW

Minimum input pulse width that

changes the output state

15

25

ns

tD1, tD2

Input to output propagation delay (1)

tD3, tD4

(1)

6

EN to output propagation delay

(1)

CLOAD = 1.8 nF, 5-V input pulse

6

13

23

ns

CLOAD = 1.8 nF, 5-V enable pulse

6

13

23

ns

See the timing diagrams in Figure 1 and Figure 2

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

�UCC27524A1-Q1

www.ti.com

SLVSDH6 – APRIL 2017

High

Input

Low

High

Enable

Low

90%

Output

10%

tD3

tD4

UDG-11217

Figure 1. Enable Function

High

Input

Low

High

Enable

Low

90%

Output

10%

tD1

tD2

UDG-11219

Figure 2. Input-Output Operation

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

7

�UCC27524A1-Q1

SLVSDH6 – APRIL 2017

www.ti.com

7.7 Typical Characteristics

4

Operating Supply Current (mA)

Startup Current (mA)

0.14

Input=VDD

Input=GND

0.12

0.1

0.08

3.5

3

VDD = 12 V

fSW = 500 kHz

CL = 500 pF

VDD=3.4V

0.06

−50

0

50

Temperature (°C)

100

2.5

−50

150

0

G001

Figure 3. Start-Up Current vs Temperature

0.5

UVLO Threshold (V)

Supply Current (mA)

0.4

0.3

Enable=12 V

VDD = 12 V

0

50

Temperature (°C)

100

4.5

4

3.5

3

−50

150

0

G012

2.5

2.5

2

2

VDD = 12 V

1.5

1

50

Temperature (°C)

100

150

G003

VDD = 12 V

1

Enable High Threshold

Enable Low Threshold

150

0.5

−50

G004

Figure 7. Input Threshold vs Temperature

100

1.5

Input High Threshold

Input Low Threshold

0

50

Temperature (°C)

Figure 6. UVLO Threshold vs Temperature

Enable Threshold (V)

Input Threshold (V)

G002

UVLO Rising

UVLO Falling

Figure 5. Supply Current vs Temperature (Outputs In DC

On/Off Condition)

8

150

5

Input=GND

Input=VDD

0.5

−50

100

Figure 4. Operating Supply Current vs Temperature

(Outputs Switching)

0.6

0.2

−50

50

Temperature (°C)

0

50

Temperature (°C)

100

150

G005

Figure 8. Enable Threshold vs Temperature

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

�UCC27524A1-Q1

www.ti.com

SLVSDH6 – APRIL 2017

Typical Characteristics (continued)

1

VDD = 12 V

IOUT = −10 mA

Output Pull−down Resistance (Ω)

Output Pull−up Resistance (Ω)

7

6

5

4

3

−50

0

50

Temperature (°C)

100

VDD = 12 V

IOUT = 10 mA

0.8

0.6

0.4

0.2

−50

150

Figure 9. Output Pullup Resistance vs Temperature

G007

8

Fall Time (ns)

Rise Time (ns)

150

VDD = 12 V

CLOAD = 1.8 nF

9

8

7

7

6

6

0

50

Temperature (°C)

100

5

−50

150

0

G008

Figure 11. Rise Time vs Temperature

50

Temperature (°C)

100

150

G009

Figure 12. Fall Time vs Temperature

18

18

Turn−on

Turn−off

EN to Output Propagation Delay (ns)

Input to Output Propagation Delay (ns)

100

9

VDD = 12 V

CLOAD = 1.8 nF

16

14

12

10

VDD = 12 V

CLOAD = 1.8 nF

8

−50

50

Temperature (°C)

Figure 10. Output Pulldown Resistance vs Temperature

10

5

−50

0

G006

0

50

Temperature (°C)

100

150

EN to Output High

EN to Output Low

16

14

12

10

VDD = 12 V

CLOAD = 1.8 nF

8

−50

G010

Figure 13. Input to Output Propagation Delay vs

Temperature

0

50

Temperature (°C)

100

150

G011

Figure 14. En to Output Propagation Delay vs Temperature

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

9

�UCC27524A1-Q1

SLVSDH6 – APRIL 2017

www.ti.com

Typical Characteristics (continued)

22

VDD = 4.5 V

VDD = 12 V

VDD = 15 V

50

Propagation Delays (ns)

Operating Supply Current (mA)

60

40

CLOAD = 1.8 nF

Both channels switching

30

20

Input to Output On delay

Input to Ouptut Off Delay

EN to Output On Delay

EN to Output Off Delay

18

14

10

10

0

CLOAD = 1.8 nF

0

6

100 200 300 400 500 600 700 800 900 1000

Frequency (kHz)

G013

Figure 15. Operating Supply Current vs Frequency

4

8

12

Supply Voltage (V)

G014

10

CLOAD = 1.8 nF

CLOAD = 1.8 nF

14

Fall Time (ns)

Rise Time (ns)

20

Figure 16. Propagation Delays vs Supply Voltage

18

10

6

16

4

8

12

Supply Voltage (V)

16

8

6

4

20

4

8

12

Supply Voltage (V)

G015

Figure 17. Rise Time vs Supply Voltage

16

20

G016

Figure 18. Fall Time vs Supply Voltage

2.5

VDD = 4.5 V

Enable Threshold (V)

Enable High Threshold

Enable Low Threshold

2

1.5

1

0.5

−50

0

50

Temperature (°C)

100

150

G017

Figure 19. Enable Threshold vs Temperature

10

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

�UCC27524A1-Q1

www.ti.com

SLVSDH6 – APRIL 2017

8 Detailed Description

8.1 Overview

The UCC27524A1-Q1 device represents Texas Instruments’ latest generation of dual-channel, low-side, highspeed, gate-driver devices featuring a 5-A source and sink current capability, industry best-in-class switching

characteristics, and a host of other features listed in Table 1 all of which combine to ensure efficient, robust, and

reliable operation in high-frequency switching power circuits.

Table 1. UCC27524A1-Q1 Features and Benefits

FEATURE

BENEFIT

Best-in-class 13-ns (typ) propagation delay

Extremely low-pulse transmission distortion

1-ns (typ) delay matching between channels

Ease of paralleling outputs for higher (2 times) current capability,

ease of driving parallel-power switches

Expanded VDD Operating range of 4.5 to 18 V

Flexibility in system design

Expanded operating temperature range of –40 °C to +140 °C

(See Electrical Characteristics table)

Flexibility in system design

VDD UVLO Protection

Outputs are held Low in UVLO condition, which ensures predictable,

glitch-free operation at power-up and power-down

Outputs held Low when input pins (INx) in floating condition

Protection feature, especially useful in passing abnormal condition

tests during safety certification

Outputs enable when enable pins (ENx) in floating condition

Pin-to-pin compatibility with the UCC27324 device from Texas

Instruments, in designs where Pin 1 and Pin 8 are in floating

condition

CMOS/TTL compatible input and enable threshold with wide

hysteresis

Enhanced noise immunity, while retaining compatibility with

microcontroller logic-level input signals (3.3 V, 5 V) optimized for

digital power

Ability of input and enable pins to handle voltage levels not restricted System simplification, especially related to auxiliary bias supply

by VDD pin bias voltage

architecture

Ability to handle –5 VDC (max) at input pins

Increased robustness in noisy environments

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

11

�UCC27524A1-Q1

SLVSDH6 – APRIL 2017

www.ti.com

8.2 Functional Block Diagram

VDD

VDD

200 kW

ENA

200 kW

1

8

ENB

VDD

INA

OUTA

2

7

400 kW

VDD

VDD

VDD

UVLO

GND

6

3

VDD

INB

OUTB

4

5

400 kW

8.3 Feature Description

8.3.1 Operating Supply Current

The UCC27524A1-Q1 devices feature very low quiescent IDD currents. The typical operating-supply current in

UVLO state and fully-on state (under static and switching conditions) are summarized in Figure 3, Figure 4, and

Figure 5. The IDD current when the device is fully on and outputs are in a static state (DC high or DC low, see

Figure 4) represents lowest quiescent IDD current when all the internal logic circuits of the device are fully

operational. The total supply current is the sum of the quiescent IDD current, the average IOUT current because of

switching, and finally any current related to pullup resistors on the enable pins (see Functional Block Diagram).

Knowing the operating frequency (fSW) and the MOSFET gate (QG) charge at the drive voltage being used, the

average IOUT current can be calculated as product of QG and fSW.

A complete characterization of the IDD current as a function of switching frequency at different VDD bias voltages

under 1.8-nF switching load in both channels is provided in Figure 15. The strikingly linear variation and close

correlation with theoretical value of average IOUT indicates negligible shoot-through inside the gate-driver device

attesting to its high-speed characteristics.

12

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

Product Folder Links: UCC27524A1-Q1

�UCC27524A1-Q1

www.ti.com

SLVSDH6 – APRIL 2017

Feature Description (continued)

8.3.2 Input Stage

The input pins of the UCC27524A1-Q1 gate-driver devices are based on a TTL and CMOS compatible inputthreshold logic that is independent of the VDD supply voltage. With typically high threshold = 2.1 V and typically

low threshold = 1.2 V, the logic level thresholds are conveniently driven with PWM control signals derived from

3.3-V and 5-V digital power-controller devices. Wider hysteresis (typ 0.9 V) offers enhanced noise immunity

compared to traditional TTL logic implementations, where the hysteresis is typically less than 0.5 V.

UCC27524A1-Q1 devices also feature tight control of the input pin threshold voltage levels which eases system

design considerations and ensures stable operation across temperature (refer to Figure 7). The very low input

capacitance on these pins reduces loading and increases switching speed.

The UCC27524A1-Q1 device features an important protection feature that holds the output of a channel when

the respective pin is in a floating condition. This is achieved using GND pulldown resistors on all of the noninverting input pins (INA, INB), as shown in the device block diagrams.

The input stage of each driver is driven by a signal with a short rise or fall time. This condition is satisfied in

typical power supply applications, where the input signals are provided by a PWM controller or logic gates with

fast transition times (