CS3318

8-Channel Analog Volume Control

Features

Complete Analog Volume Control – 8 Independently Controllable Channels – 3 Configurable Master Volume and Muting Controls Wide Adjustable Volume Range – -96 dB to +22 dB in ¼ dB Steps Low Distortion & Noise – -112 dB THD+N – 127 dB Dynamic Range Noise-Free Level Transitions – Zero-Crossing Detection with Programmable Time-Out Low Channel-to-Channel Crosstalk – 120 dB Inter-Channel Isolation Comprehensive Serial Control Port – Supports I²C® and SPITM Communication – Independent Control of up to 128 Devices on a Shared 2-Wire I²C or 3-Wire SPI Control Bus – Supports Individual and Grouped Control of all CS3318 Devices on the I²C or SPI Control Bus Flexible Power Supply Voltages – ±8 V to ±9 V Analog Supply – +3.3 V Digital Supply

Description

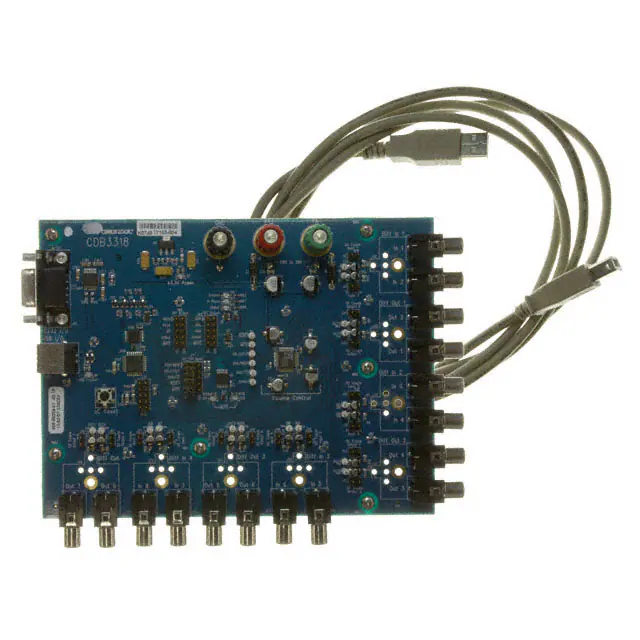

The CS3318 is an 8-channel digitally controlled analog volume control designed specifically for high-end audio systems. It features a comprehensive I²C/SPI serial control port for easy device and volume configuration. The CS3318 includes arrays of well-matched resistors and complementary low-noise active output stages. A total adjustable range of 118 dB, in ¼ dB steps, is spread evenly over 96 dB of attenuation and 22 dB of gain. The CS3318 implements configurable zero-crossing detection to provide glitch-free volume-level changes. The I²C/SPI control interface provides for easy system integration of up to 128 CS3318 devices over a single 2wire I²C or 3-wire SPI bus, allowing many channels of volume control with minimal system controller I/O requirements. Devices may be controlled on an individual and grouped basis, simplifying simultaneous configuration of a group of channels across multiple devices, while allowing discrete control over all channels on an individual basis. The device operates from ±8 V to ±9 V analog supplies and has an input/output voltage range of ±6.65 V to ±7.65 V. The digital control interface operates at +3.3 V. The CS3318 is available in a 48-pin LQFP package in Commercial grade (-10° to 70° C). The CS3318 Customer Demonstration board is also available for device evaluation. Refer to “Ordering Information” on page 44 for complete details.

8-Channel Analog Inputs

±8 V to ±9 V

8

+3.3 V

+

I²C/SPI Serial Control I²C / SPI Control Port

Zero Crossing Detector

8

_

8-Channel Analog Outputs

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2006 (All Rights Reserved)

DECEMBER '06 DS693F1

�CS3318

TABLE OF CONTENTS

1. PIN DESCRIPTIONS ............................................................................................................................ 5 2. CHARACTERISTICS AND SPECIFICATIONS .................................................................................... 7 SPECIFIED OPERATING CONDITIONS .................................................................................................... 7 ABSOLUTE MAXIMUM RATINGS............................................................................................................... 7 ANALOG CHARACTERISTICS ................................................................................................................... 8 DIGITAL INTERFACE CHARACTERISTICS............................................................................................... 9 MUTE SWITCHING CHARACTERISTICS .................................................................................................. 9 CONTROL PORT SWITCHING CHARACTERISTICS - I²C FORMAT...................................................... 10 CONTROL PORT SWITCHING CHARACTERISTICS - SPI™ FORMAT ................................................. 11 3. TYPICAL CONNECTION DIAGRAM ................................................................................................. 12 4. DETAILED BLOCK DIAGRAM .......................................................................................................... 13 5. APPLICATIONS ................................................................................................................................. 14 5.1 General Description ..................................................................................................................... 14 5.2 System Design ............................................................................................................................ 14 5.2.1 Analog Inputs .................................................................................................................... 14 5.2.2 Analog Outputs .................................................................................................................. 15 5.2.3 Recommended Layout, Grounding, and Power Supply Decoupling ................................. 15 5.3 Power-Up and Power-Down ........................................................................................................ 15 5.3.1 Recommended Power-Up Sequence ................................................................................ 16 5.3.2 Recommended Power-Down Sequence ........................................................................... 16 5.4 Volume & Muting Control Architecture ........................................................................................ 17 5.4.1 Control Mapping Matrix ..................................................................................................... 17 5.4.2 Volume & Muting Control Implementation ......................................................................... 18 5.5 Volume Controls .......................................................................................................................... 19 5.5.1 Individual Channel Volume Controls ................................................................................. 19 5.5.2 Master Volume Controls .................................................................................................... 19 5.5.3 Volume Limits .................................................................................................................... 20 5.6 Muting Controls ........................................................................................................................... 21 5.6.1 Individual Channel Mute Controls ..................................................................................... 21 5.6.2 Master Mute Controls ........................................................................................................ 21 5.6.3 Hardware Mute Control ..................................................................................................... 21 5.7 Zero-Crossing Detection .............................................................................................................. 22 5.7.1 Zero-Crossing Modes ........................................................................................................ 22 5.7.2 Zero-Crossing Time-Out .................................................................................................... 22 5.8 System Serial Control Configuration ........................................................................................... 23 5.8.1 Serial Control within a Single-CS3318 System ................................................................. 23 5.8.2 Serial Control within a Multiple-CS3318 System ............................................................... 24 5.8.2.1 SPI Mode Serial Control Configuration .......................................................................................... 24 5.8.2.2 I²C Mode Control Configuration ..................................................................................................... 26 5.9 I²C/SPI Serial Control Formats .................................................................................................... 27 5.9.1 I²C Mode ............................................................................................................................ 27 5.9.2 SPI Mode ........................................................................................................................... 28 6. CS3318 REGISTER QUICK REFERENCE ........................................................................................ 29 7. CS3318 REGISTER DESCRIPTIONS ................................................................................................ 31 7.1 Ch 1-8 Volume - Addresses 01h - 08h ........................................................................................ 31 7.1.1 Volume Control (Bits 7:0) .................................................................................................. 31 7.2 ¼ dB Control - Address 09h ........................................................................................................ 32 7.2.1 ¼ dB Control (Bit 0 - 7) ...................................................................................................... 32 7.3 Mute Control - Address 0Ah ........................................................................................................ 33 7.3.1 Mute Channel X (Bit 0 - 7) ................................................................................................. 33 7.4 Device Configuration 1 - Address 0Bh (Bit 5) .............................................................................. 33 7.4.1 Enable MUTE Input (Bit 5) ................................................................................................ 33 2 DS693F1

�CS3318

7.4.2 MUTE Input Polarity (Bit 4) ................................................................................................ 33 7.4.3 Channel B = Channel A (Bit 0 - 3) ..................................................................................... 34 7.5 Device Configuration 2 - Address 0Ch ........................................................................................ 34 7.5.1 Zero-Crossing Time-Out Period (Bits 4:2) ......................................................................... 34 7.5.2 Zero-Crossing Mode (Bits 1:0) .......................................................................................... 35 7.6 Channel Power - Address 0Dh .................................................................................................... 35 7.6.1 Power Down Channel X (Bit 0 - 7) .................................................................................... 35 7.7 Master Power - Address 0Eh ....................................................................................................... 35 7.7.1 Power Down All (Bit 0) ...................................................................................................... 35 7.8 Freeze Control - Address 0Fh ..................................................................................................... 36 7.8.1 Freeze (Bit 7) ..................................................................................................................... 36 7.9 Master 1 Mask - Address 10h ...................................................................................................... 36 7.10 Master 1 Volume - Address 11h ................................................................................................ 36 7.10.1 Master 1 Volume Control (Bits 7:0) ................................................................................. 36 7.11 Master 1 Control - Address 12h ................................................................................................. 37 7.11.1 Master 1 Mute (Bit 1) ....................................................................................................... 37 7.11.2 Master 1 ¼ dB Control (Bit 0) .......................................................................................... 37 7.12 Master 2 Mask - Address 13h .................................................................................................... 37 7.13 Master 2 Volume - Address 14h ................................................................................................ 37 7.13.1 Master 2 Volume Control (Bits 7:0) ................................................................................. 37 7.14 Master 2 Control - Address 15h ................................................................................................. 38 7.14.1 Master 2 Mute (Bit 1) ....................................................................................................... 38 7.14.2 Master 2 ¼ dB Control (Bit 0) .......................................................................................... 38 7.15 Master 3 Mask - Address 16h .................................................................................................... 38 7.16 Master 3 Volume - Address 17h ................................................................................................ 38 7.16.1 Master 3 Volume Control (Bits 7:0) ................................................................................. 38 7.17 Master 3 Control - Address 18h ................................................................................................. 39 7.17.1 Master 3 Mute (Bit 1) ....................................................................................................... 39 7.17.2 Master 3 ¼ dB Control (Bit 0) .......................................................................................... 39 7.18 Group 2 Chip Address 19h ........................................................................................................ 40 7.18.1 Group 2 Chip Address (Bits 7:1) ..................................................................................... 40 7.18.2 Enable Group 2 Address (Bit 0) ...................................................................................... 40 7.19 Group 1 Chip Address 1Ah ........................................................................................................ 40 7.19.1 Group 1 Chip Address (Bits 7:1) ..................................................................................... 40 7.19.2 Enable Group 1 Address (Bit 0) ...................................................................................... 40 7.20 Individual Chip Address 1Bh ..................................................................................................... 41 7.20.1 Individual Chip Address (Bits 7:1) ................................................................................... 41 7.20.2 Enable Next Device (Bit 0) .............................................................................................. 41 7.21 Chip ID - Address 1Ch ............................................................................................................... 41 7.21.1 Chip ID (Bits 7:4) ............................................................................................................. 41 7.21.2 Chip Revision (Bits 3:0) ................................................................................................... 41 8. PARAMETER DEFINITIONS .............................................................................................................. 42 9. PACKAGE DIMENSIONS .................................................................................................................. 43 10. THERMAL CHARACTERISTICS AND SPECIFICATIONS ............................................................ 43 11. ORDERING INFORMATION ............................................................................................................ 44 12. REVISION HISTORY ........................................................................................................................ 44

DS693F1

3

�CS3318

LIST OF FIGURES

Figure 1.Control Port Timing - I²C Format.................................................................................................. 10 Figure 2.Control Port Timing - SPI Format................................................................................................. 11 Figure 3.Typical Connection Diagram........................................................................................................ 12 Figure 4.Detailed Block Diagram ............................................................................................................... 13 Figure 5.CS3318 Control Mapping Matrix.................................................................................................. 17 Figure 6.Volume & Muting Control Implementation ................................................................................... 18 Figure 7.Standard I²C Connections............................................................................................................ 23 Figure 8.Standard SPI Connections........................................................................................................... 23 Figure 9.SPI Serial Control Connections ................................................................................................... 24 Figure 10.Individual Device Address Configuration Process ..................................................................... 25 Figure 11.I²C Serial Control Connections .................................................................................................. 26 Figure 12.Control Port Timing, I²C Write.................................................................................................... 27 Figure 13.Control Port Timing, I²C Read.................................................................................................... 28 Figure 14.SPI Write Cycle.......................................................................................................................... 28

LIST OF TABLES

Table 1. Example Volume Settings ............................................................................................................ 20 Table 2. Zero-Crossing Modes................................................................................................................... 22 Table 3. Zero-Crossing Time-Out Periods ................................................................................................. 22 Table 4. I²C Mode Default Chip Address ................................................................................................... 27 Table 5. Example Volume Settings ............................................................................................................ 31 Table 6. Example Volume Settings ............................................................................................................ 32 Table 7. Channel B = Channel A Settings ................................................................................................. 34 Table 8. Zero-Crossing Time-Out Settings ................................................................................................ 34 Table 9. Zero-Crossing Mode Settings ...................................................................................................... 35 Table 10. Chip Revision Register Codes ................................................................................................... 41

4

DS693F1

�CS3318 1. PIN DESCRIPTIONS

REFO2

REFO1

REFO3

REFI2

REFI3

OUT1

OUT2

48 47 46 45 44 43 42 41 40 39 38 37

IN1 REFI1 RESET MUTE SCL/CCLK SDA/MOSI AD0/CS ENOut DGND VD REFI8 IN8

OUT3

VA+

VA-

IN2

IN3

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

VA+ OUT8 VAOUT7 REFI7 REFI6 REFO8 REFO6 REF07 OUT6 IN7 IN6

36 35 34 33

VAVA+ OUT4 REFO4 IN4 REFI4 REFI5 IN5 REFO5 OUT5 VAVA+

CS3318

32 31 30 29 28 27 26 25

Pin Name

IN1 IN2 IN3 IN4 IN5 IN6 IN7 IN8

#

1 42 39 32 29 22 19 12

Pin Description

Analog Inputs (Input) - The full-scale level is specified in the Analog Characteristics specification table.

DS693F1

5

�CS3318

Pin Name

OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 OUT8 REFI1 REFI2 REFI3 REFI4 REFI5 REFI6 REFI7 REFI8 REFO1 REFO2 REFO3 REFO4 REFO5 REFO6 REFO7 REFO8

#

47 44 37 34 27 24 17 14 2 41 40 31 30 21 20 11 48 43 38 33 28 23 18 13 15, 25, 35, 45 16, 26, 36, 46 3 4 5 6 7 8 9 10

Pin Description

Analog Outputs (Output) - The full-scale output level is specified in the Analog Characteristics specification table.

Reference In (Input) - Analog reference pin.

Reference Out (Output) - Analog reference pin.

VA+

Positive Analog Power (Input) - Positive power for the internal analog section.

VA-

Negative Analog Power (Input) - Negative power for the internal analog section.

RESET MUTE SCL/CCLK SDA/MOSI AD0/CS ENOut DGND VD

Reset (Input) - The device enters a low-power mode when this pin is driven low. Mute (Input) - This pin defaults to an active low mute input, and may be configured as an active high mute input. Serial Control Port Clock (Input) - Serial clock for the serial control port. Serial Control Data (Input/Output) - SDA is a data I/O line for the control port interface in I²C Mode. MOSI is the input data line for the control port interface in SPI Mode. Default Address Bit 0 (I²C) / Control Port Chip Select (SPI) (Input) - AD0 sets the LSB of the default chip address in I²C Mode. CS is the chip-select signal for SPI format. Enable Output (Output) - Enable output signal for multi-device serial control chain configuration. Digital Ground (Input) - Ground reference for the internal digital section. Digital Power (Input) - Positive power for the internal digital section.

6

DS693F1

�CS3318 2. CHARACTERISTICS AND SPECIFICATIONS

All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and TA = 25°C.

SPECIFIED OPERATING CONDITIONS

(DGND = 0 V; All voltages with respect to ground.) Parameters

DC Power Supplies: Positive Analog Negative Analog Digital

Symbol

VA+ VAVD TA

Min

7.6 -9.45 3.1 -10

Nom

9.0 -9.0 3.3 -

Max

9.45 -7.6 3.5 +70

Units

V V V °C

Ambient Operating Temperature (Power Applied)

ABSOLUTE MAXIMUM RATINGS

(DGND = 0 V; All voltages with respect to ground. (Note 1) Parameter

DC Power Supplies: Positive Analog Negative Analog Digital (Note 2)

Symbol

VA+ VAVD Iin VINA VIND TA Tstg

Min

-0.3 -10.5 -0.3 (VA-) - 0.3 VD - 0.3 -55 -65

Max

10.5 0.3 3.63 ±10 (VA+) + 0.3 VD + 0.3 +125 +150

Units

V V V mA V V °C °C

Input Current Analog Input Voltage Digital Input Voltage Ambient Operating Temperature (Power Applied) Storage Temperature

Notes: 1. Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes. 2. Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause SCR latch-up.

DS693F1

7

�CS3318 ANALOG CHARACTERISTICS

(Test conditions (unless otherwise specified): RS = 0; RL = 20 kΩ; CL = 20 pF; 10 Hz to 20 kHz Measurement Bandwidth) Parameter DC Characteristics

Step Size Gain Error Gain Matching Between Channels Input Resistance Input Capacitance (Vol = +22 dB) (Vol = +22 dB) RIN CIN (Note 3) THD+N (THD+N < 1 %) (Note 4) (1 kHz) (Note 4) VFS 8 121 (VA-) + 1.35 2 0.25 ±0.5 ±0.1 10 10 0.00025 127 1.8 -120 0.75 100 20 5 36 36 0.6 60 650 540 80 dB dB dB kΩ pF

Symbol

Min

Typ

Max

Unit

AC Characteristics

Total Harmonic Distortion + Noise Dynamic Range Input/Output Voltage Range Output Noise Interchannel Isolation 0.00063 % dB (VA+) - 1.35 V 3.6 μVrms dB 5 100 50 50 1.07 904 mV Ω kΩ pF mA MHz mA mA mA μA mW μW dB

Output Buffer

Offset Voltage Output Resistance AC Load Resistance Load Capacitance Short Circuit Current Unity Gain Bandwidth, Small Signal VOS ROUT RLOAD

Power Supplies

Supply Current (No Load, Vin = 0 V) Normal Operation IVA+ IVAIVD IPD

Power-Down, All Supplies (Note 5) Normal Operation Power Down (Note 5) Power Supply Rejection Ratio (250 Hz) Power Consumption

PSRR

3. Vin = [(VFS Max - VFS Min) - 1.6 V] Vp-p, 1 kHz, Volume = 0 dB. Note that for (VA+) = -(VA-) = 9 V, Vin = 13.7 Vp-p = 4.8 VRMS. 4. Measured with input grounded and volume = 0 dB. Will increase as a function of volume settings >0 dB. 5. Power-down is defined as RESET = low, all clock and data lines held static, and no analog input signals applied.

8

DS693F1

�CS3318 DIGITAL INTERFACE CHARACTERISTICS

Parameters

High-Level Input Voltage Low-Level Input Voltage High-Level Output Voltage at Io=2 mA Low-Level Output Voltage at Io=2 mA Input Leakage Current Input Capacitance

Symbol

VIH VIL VOH VOL Iin

Min

0.7 x VD VD - 1.0 -

Typ

8

Max

0.2 x VD 0.4 ±10 -

Units

V V V V μA pF

MUTE SWITCHING CHARACTERISTICS

(Inputs: Logic 0 = DGND, Logic 1 = VD) Parameters

MUTE Active Pulse Width (Note 6)

Symbol

-

Min

2

Typ

-

Max

-

Units

ms

6. The MUTE active state (low/high) is set by the MutePolarity bit in the Device Configuration 1 register (see page 33).

DS693F1

9

�CS3318 CONTROL PORT SWITCHING CHARACTERISTICS - I²C FORMAT

(Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF) Parameter

SCL Clock Frequency RESET Rising Edge to Start Bus Free Time Between Transmissions Start Condition Hold Time (prior to first clock pulse) Clock Low time Clock High Time Setup Time for Repeated Start Condition SDA Hold Time from SCL Falling SDA Setup time to SCL Rising Rise Time of SCL and SDA Fall Time SCL and SDA Setup Time for Stop Condition Acknowledge Delay from SCL Falling (Note 7)

Symbol

fscl tirs tbuf thdst tlow thigh tsust thdd tsud trc, trd tfc, tfd tsusp tack

Min

100 4.7 4.0 4.7 4.0 4.7 0 250 4.7 300

Max

100 1 300 1000

Unit

kHz ns µs µs µs µs µs µs ns µs ns µs ns

7. Data must be held for sufficient time to bridge the transition time, tfc, of SCL.

RESET t Stop irs Start R e p e ate d Sta rt t rd t fd Stop

SDA t buf t hdst t high t hdst t fc t susp

SCL t t t sud t ack t sust t rc

lo w

hdd

Figure 1. Control Port Timing - I²C Format

10

DS693F1

�CS3318 CONTROL PORT SWITCHING CHARACTERISTICS - SPI™ FORMAT

(Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF) Parameter

CCLK Clock Frequency RESET Rising Edge to CS Falling CS High Time Between Transmissions CS Falling to CCLK Edge CCLK Low Time CCLK High Time CDIN to CCLK Rising Setup Time CCLK Rising to DATA Hold Time Rise Time of CCLK and CDIN Fall Time of CCLK and CDIN (Note 8) (Note 9) (Note 9)

Symbol

fsck tsrs tcsh tcss tscl tsch tdsu tdh tr2 tf2

Min

0 100 1.0 20 66 66 40 15 -

Max

6.0 100 100

Unit

MHz ns μs ns ns ns ns ns ns ns

8. Data must be held for sufficient time to bridge the transition time of CCLK. 9. For fsck

很抱歉,暂时无法提供与“CDB3318”相匹配的价格&库存,您可以联系我们找货

免费人工找货- 国内价格 香港价格

- 1+3114.034071+400.19684