CS5368

114 dB, 192 kHz, 8-Channel A/D Converter

Features

Advanced Multi-bit Delta-Sigma Architecture 24-Bit Conversion 114 dB Dynamic Range -105 dB THD+N Supports Audio Sample Rates up to 216 kHz Selectable Audio Interface Formats – Left-Justified, I²S, TDM – 8-Channel TDM Interface Formats Low Latency Digital Filter Less than 680 mW Power Consumption On-Chip Oscillator Driver Operation as System Clock Master or Slave Auto-Detect Speed in Slave Mode Differential Analog Architecture Separate 1.8 V to 5 V Logic Supplies for Control and Serial Ports High-Pass Filter for DC Offset Calibration Overflow Detection Footprint Compatible with the 4-Channel CS5364 and 6-Channel CS5366

Additional Control Port Features

Supports Standard I²C® or SPI™ Control Interface Individual Channel HPF Disable Overflow Detection for Individual Channels Mute Control for Individual Channels Independent Power-Down Control per Channel Pair

VA 5V

VD 3.3 - 5V

VLC 1.8 - 5V

Configuration Registers

Control Interface I2C, SPI or Pins

Level Translator

Voltage Reference Internal Oscillator

Device Control

8 Differential Analog Inputs

Multi-bit ΔΣ ADC

Decimation Filter

High Pass Filter

Serial Audio Out PCM or TDM

Level Translator

Digital Audio

VLS 1.8 - 5V

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2007 (All Rights Reserved)

JULY '07 DS624F2

�CS5368

Description

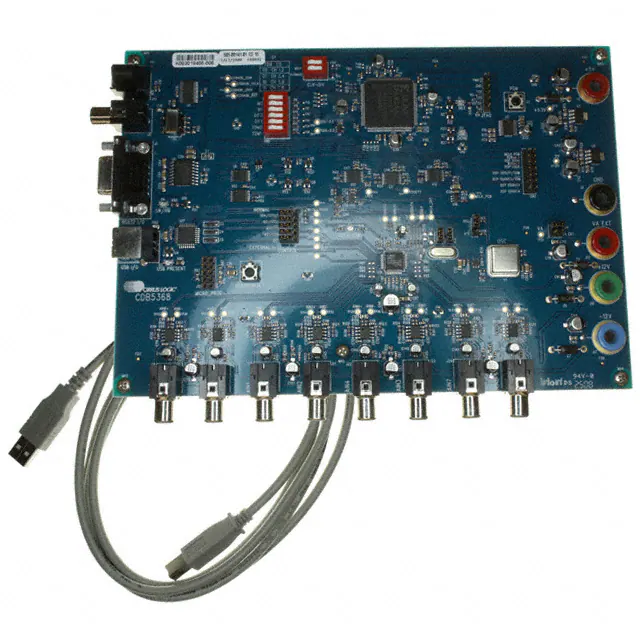

The CS5368 is a complete 8-channel analog-to-digital converter for digital audio systems. It performs sampling, analog-to-digital conversion, and anti-alias filtering, generating 24-bit values for all 8-channel inputs in serial form at sample rates up to 216 kHz per channel. The CS5368 uses a 5th-order, multi-bit delta sigma modulator followed by low latency digital filtering and decimation, which removes the need for an external anti-aliasing filter. The ADC uses a differential input architecture which provides excellent noise rejection. Dedicated level translators for the Serial Port and Control Port allow seamless interfacing between the CS5368 and other devices operating over a wide range of logic levels. In addition, an on-chip oscillator driver provides clocking flexibility and simplifies design. The CS5368 is the industry’s first audio A/D to support a high-speed TDM interface which provides a serial output of 8 channels of audio data with sample rates up to 216 kHz within a single data stream. It further reduces layout complexity and relieves input/output constraints in digital signal processors. The CS5368 is available in 48-pin LQFP package in both Commercial (-40° to 85°C) and Automotive grades (-40° to +105°C). The CDB5368 Customer Demonstration board is also available for device evaluation and implementation suggestions. Please see “Ordering Information” on page 41 for complete ordering information. The CS5368 is ideal for high-end and pro-audio systems requiring unrivaled sound quality, transparent conversion, wide dynamic range and negligible distortion, such as A/V receivers, digital mixing consoles, multi-channel recorders, outboard converters, digital effect processors, and automotive audio systems.

2

DS624F2

�CS5368 TABLE OF CONTENTS

1. PIN DESCRIPTION ................................................................................................................................. 6 2. TYPICAL CONNECTION DIAGRAM ................................................................................................... 9 3. CHARACTERISTICS AND SPECIFICATIONS .................................................................................... 10 RECOMMENDED OPERATING CONDITIONS ................................................................................. 10 ABSOLUTE RATINGS ....................................................................................................................... 10 SYSTEM CLOCKING ......................................................................................................................... 10 DC POWER ........................................................................................................................................ 11 LOGIC LEVELS ................................................................................................................................. 11 PSRR, VQ AND FILT+ CHARACTERISTICS .................................................................................... 11 ANALOG CHARACTERISTICS (COMMERCIAL) .............................................................................. 12 ANALOG CHARACTERISTICS (AUTOMOTIVE) ............................................................................... 13 DIGITAL FILTER CHARACTERISTICS ............................................................................................. 14 OVERFLOW TIMEOUT ...................................................................................................................... 14 SERIAL AUDIO INTERFACE - I²S/LJ TIMING ................................................................................... 15 SERIAL AUDIO INTERFACE - TDM TIMING ..................................................................................... 16 SWITCHING SPECIFICATIONS - CONTROL PORT - I²C TIMING ................................................... 17 SWITCHING SPECIFICATIONS - CONTROL PORT - SPI TIMING .................................................. 18 4. APPLICATIONS ................................................................................................................................... 19 4.1 Power ............................................................................................................................................. 19 4.2 Control Port Mode and Stand-Alone Operation .............................................................................. 19 4.2.1 Stand-Alone Mode ................................................................................................................. 19 4.2.2 Control Port Mode ................................................................................................................. 19 4.3 Master Clock Source ...................................................................................................................... 20 4.3.1 On-Chip Crystal Oscillator Driver .......................................................................................... 20 4.3.2 Externally Generated Master Clock ....................................................................................... 20 4.4 Master and Slave Operation ........................................................................................................... 21 4.4.1 Synchronization of Multiple Devices ...................................................................................... 21 4.5 Serial Audio Interface (SAI) Format ................................................................................................ 22 4.5.1 I²S and LJ Format .................................................................................................................. 22 4.5.2 TDM Format .......................................................................................................................... 23 4.5.3 Configuring Serial Audio Interface Format ............................................................................ 23 4.6 Speed Modes ................................................................................................................................. 23 4.6.1 Sample Rate Ranges ............................................................................................................ 23 4.6.2 Using M1 and M0 to Set Sampling Parameters .................................................................... 23 4.6.3 Master Mode Clock Dividers ................................................................................................. 24 4.6.4 Slave Mode Audio Clocking With Auto-Detect ...................................................................... 24 4.7 Master and Slave Clock Frequencies ............................................................................................. 25 4.8 Reset .............................................................................................................................................. 27 4.8.1 Power-Down Mode ................................................................................................................ 27 4.9 Overflow Detection ......................................................................................................................... 27 4.9.1 Overflow in Stand-Alone Mode .............................................................................................. 27 4.9.2 Overflow in Control Port Mode .............................................................................................. 27 4.10 Analog Connections ..................................................................................................................... 28 4.11 Optimizing Performance in TDM Mode ........................................................................................ 29 4.12 DC Offset Control ......................................................................................................................... 29 4.13 Control Port Operation .................................................................................................................. 30 4.13.1 SPI Mode ............................................................................................................................. 30 4.13.2 I²C Mode .............................................................................................................................. 31 5. REGISTER MAP ................................................................................................................................... 32 5.1 Register Quick Reference ............................................................................................................. 32 5.2 00h (REVI) Chip ID Code & Revision Register ............................................................................... 32 DS624F2 3

�CS5368

5.3 01h (GCTL) Global Mode Control Register ................................................................................... 32 5.4 02h (OVFL) Overflow Status Register ........................................................................................... 33 5.5 03h (OVFM) Overflow Mask Register ............................................................................................ 33 5.6 04h (HPF) High-Pass Filter Register ............................................................................................. 34 5.7 05h Reserved ................................................................................................................................ 34 5.8 06h (PDN) Power Down Register .................................................................................................. 34 5.9 07h Reserved ................................................................................................................................ 34 5.10 08h (MUTE) Mute Control Register .............................................................................................. 34 5.11 09h Reserved .............................................................................................................................. 35 5.12 0Ah (SDEN) SDOUT Enable Control Register ............................................................................ 35 6. FILTER PLOTS ..................................................................................................................................... 36 7. PARAMETER DEFINITIONS ................................................................................................................ 39 8. PACKAGE DIMENSIONS ................................................................................................................... 40 THERMAL CHARACTERISTICS ....................................................................................................... 40 9. ORDERING INFORMATION ................................................................................................................ 41 10. REVISION HISTORY ......................................................................................................................... 41

LIST OF FIGURES

Figure 1. CS5368 Pinout ............................................................................................................................. 6 Figure 2. Typical Connection Diagram ........................................................................................................ 9 Figure 3. I²S/LJ Timing .............................................................................................................................. 15 Figure 4. TDM Timing ............................................................................................................................... 16 Figure 5. I²C Timing .................................................................................................................................. 17 Figure 6. SPI Timing ................................................................................................................................. 18 Figure 7. Crystal Oscillator Topology ........................................................................................................ 20 Figure 8. Master/Slave Clock Flow ........................................................................................................... 21 Figure 9. Master and Slave Clocking for a Multi-Channel Application ...................................................... 21 Figure 10. I²S Format ................................................................................................................................ 22 Figure 11. LJ Format ................................................................................................................................. 22 Figure 12. TDM Format ............................................................................................................................. 23 Figure 13. Master Mode Clock Dividers .................................................................................................... 24 Figure 14. Slave Mode Auto-Detect Speed ............................................................................................... 24 Figure 15. Recommended Analog Input Buffer ......................................................................................... 28 Figure 16. SPI Format ............................................................................................................................... 30 Figure 17. I²C Write Format ...................................................................................................................... 31 Figure 18. I²C Read Format ...................................................................................................................... 31 Figure 19. SSM Passband ........................................................................................................................ 36 Figure 20. DSM Passband ........................................................................................................................ 36 Figure 21. QSM Passband ........................................................................................................................ 36 Figure 22. SSM Stopband ......................................................................................................................... 37 Figure 23. DSM Stopband ......................................................................................................................... 37 Figure 24. QSM Stopband ........................................................................................................................ 37 Figure 25. SSM -1 dB Cutoff ..................................................................................................................... 38 Figure 26. DSM -1 dB Cutoff .................................................................................................................... 38 Figure 27. QSM -1 dB Cutoff ..................................................................................................................... 38

4

DS624F2

�CS5368 LIST OF TABLES

Table 1. Power Supply Pin Definitions ...................................................................................................... 19 Table 2. DIF1 and DIF0 Pin Settings ........................................................................................................ 23 Table 3. M1 and M0 Settings .................................................................................................................... 23 Table 4. Frequencies for 48 kHz Sample Rate using LJ/I²S ..................................................................... 25 Table 5. Frequencies for 96 kHz Sample Rate using LJ/I²S ..................................................................... 25 Table 6. Frequencies for 192 kHz Sample Rate using LJ/I²S ................................................................... 25 Table 7. Frequencies for 48 kHz Sample Rate using TDM ....................................................................... 25 Table 8. Frequencies for 48 kHz Sample Rate using TDM ....................................................................... 25 Table 9. Frequencies for 96 kHz Sample Rate using TDM ....................................................................... 26 Table 10. Frequencies for 96 kHz Sample Rate using TDM ..................................................................... 26 Table 11. Frequencies for 192 kHz Sample Rate using TDM ................................................................... 26 Table 12. Frequencies for 192 kHz Sample Rate using TDM ................................................................... 26

DS624F2

5

�CS5368 1. PIN DESCRIPTION

M0/SDA/CDOUT M1/SCL/CCLK DIF0/AD0/CS DIF1/AD1/CDIN

AIN1+

AIN5+

AIN6+

AIN1-

AIN5-

AIN6-

MDIV

48 47 46 45 44 43 42 41 40 39 38 37

AIN2+ AIN2GND VA REF_GND FILT+ VQ GND VA GND AIN4+ AIN4-

RST

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

GND AIN3+ AIN7+ AIN8+ XTI XTO LRCK/FS AIN3AIN7AIN8MCLK VX

36 35 34 33

OVFL VLC CLKMODE VD GND SDOUT3/TDM SDOUT1/TDM GND VLS SDOUT2 SDOUT4 SCLK

CS5368

32 31 30 29 28 27 26 25

Figure 1. CS5368 Pinout

6

DS624F2

�CS5368

Pin Name

AIN2+, AIN2AIN4+, AIN4AIN3+, AIN3AIN7+, AIN7AIN8+, AIN8AIN6+, AIN6AIN5+, AIN5AIN1+, AIN1GND VA REF_GND FILT+ VQ VX XTI XTO MCLK

Pin #

1,2 11,12 13,14 15,16 17,18 43,44 45,46 47,48 3,8 10,19 29,32 4,9 5 6 7 20 21 22 23

Pin Description

Differential Analog (Inputs) - Audio signals are presented differently to the delta sigma modulators via the AIN+/- pins.

Ground (Input) - Ground reference. Must be connected to analog ground. Analog Power (Input) - Positive power supply for the analog section Reference Ground (Input) - For the internal sampling circuits. Must be connected to analog ground. Positive Voltage Reference (Output) - Reference voltage for internal sampling circuits. Quiescent Voltage (Output) - Filter connection for the internal quiescent reference voltage. Crystal Oscillator Power (Input) - Also powers control logic to enable or disable oscillator circuits. Crystal Oscillator Connections (Input/Output) - I/O pins for an external crystal which may be used to generate MCLK. System Master Clock (Input/Output) - When a crystal is used, this pin acts as a buffered MCLK Source (Output). When the oscillator function is not used, this pin acts as an input for the system master clock. In this case, the XTI and XTO pins must be tied low. Serial Audio Channel Clock (Input/Output) In I²S Mode, Serial Audio Channel Select. When low, the odd channels are selected. In LJ Mode, Serial Audio Channel Select. When high, the odd channels are selected. In TDM Mode, a frame sync signal. When high, it marks the beginning of a new frame of serial audio samples. In Slave Mode, this pin acts as an input pin. Main timing clock for the Serial Audio Interface (Input/Output) - During Master Mode, this pin acts as an output, and during Slave Mode it acts as an input pin. Serial Audio Data (Output) - Channels 7,8. Serial Audio Data (Output) - Channels 3,4. Serial Audio Interface Power (Input) - Positive power for the serial audio interface. Serial Audio Data (Output) - Channels 1,2. Serial Audio Data (Output) - Channels 5,6. TDM is complementary TDM data. Digital Power (Input) - Positive power supply for the digital section/ Control Port Interface Power(Input) - Positive power for the control port interface. Overflow (Output, open drain) - Detects an overflow condition on both left and right channels. Reset (Input) - The device enters a low power mode when low. CLKMODE (Input) - Setting this pin HIGH places a divide-by-1.5 circuit in the MCLK path to the core device circuitry. DIF1, DIF0 (Input) - Inputs of the audio interface format. Mode Selection (Input) - Determines the operational mode of the device. MCLK Divider (Input) - Setting this pin HIGH places a divide-by-2 circuit in the MCLK path to the core device circuitry.

LRCK/FS

24

SCLK SDOUT4 SDOUT2 VLS SDOUT1/TDM SDOUT3/TDM VD VLC OVFL RST

25 26 27 28 30 31 33 35 36 41

Stand-Alone Mode

CLKMODE DIF1 DIF0 M1 M0 MDIV 34 37 38 39 40 42

DS624F2

7

�CS5368

Control Port Mode

CLKMODE AD1/CDIN AD0/CS SCL/CCLK SDA/CDOUT MDIV 34 37 38 39 40 42 CLKMODE (Input) - This pin is ignored in Control Port Mode and the same functionality is obtained from the corresponding bit in the Global Control Register. Note: Should be connected to GND when using the part in Control Port Mode. I²C Format, AD1 (Input) - Forms the device address input AD[1]. SPI Format, CDIN (Input) - Becomes the input data pin. I²C Format, AD0 (Input) - Forms the device address input AD[0]. SPI Format, CS (Input) - Acts as the active low chip select input. I²C Format, SCL (Output) - Acts as the serial clock output from the CS5368. SPI Format, CCLK (Output) - Acts as the serial clock output from the CS5368. I²C Format SDA (Input/Output) - Acts as an input/output data pin. SPI Format CDOUT (Output) - Acts as an output only data pin. MCLK Divider (Input) - This pin is ignored in Control Port Mode and the same functionality is obtained from the corresponding bit in the Global Control Register. Note: Should be connected to GND when using the part in Control Port Mode.

8

DS624F2

�CS5368 2. TYPICAL CONNECTION DIAGRAM

Resistor may only be used if VD is derived from VA. If used, do not drive any other logic from VD.

+

1 μF

+5V to 3.3V

+5V

+

1 μF

0.01 μF

4, 9

5.1 Ω

33

0.01 μF

VA

6

VD

220 μ F 1 μF

+

0.1 μF 0.1 μF

FILT+ REF_GND

VQ GND

5 7

VLC

35

+5V to 1.8V

0.01 μF

39 40 36 37 38 41 42 34

+

8

Channel 1 Analog Input Buffer

47 48 1 2 13 14 11 12 45 46 43 44 15 16 17 18

AIN 1+ AIN 1AIN 2+ AIN 2AIN 3+ AIN 3AIN 4+ AIN 4AIN 5+ AIN 5AIN 6+ AIN 6AIN 7+ AIN 7AIN 8+ AIN 8GND

MODE1/SCL/CCLK MODE0/SDA/CDOUT OVFL DIF1/AD1/CDIN DIF0/AD0/CS RST MDIV

CLKMODE

Power Down and Mode Settings

Channel 2 Analog Input Buffer

Channel 3 Analog Input Buffer

CS5368 A/D CONVERTER

VLS

28

+5V to 1.8V

0.01 μF

30 27 31 26 24 25 23

Channel 4 Analog Input Buffer

SDOUT1/ TDM SDOUT2 SDOUT3/ TDM SDOUT4 LRCK/FS SCLK MCLK

Audio Data Processor

Channel 5 Analog Input Buffer

Timing Logic and Clock

Channel 6 Analog Input Buffer

Channel 7 Analog Input Buffer

VX XTI XTO

20

+5V

21 22

Channel 8 Analog Input Buffer

3, 8, 10, 19, 29, 32

Figure 2. Typical Connection Diagram

For analog buffer configurations, refer to Cirrus Application Note AN241. Also, a low-cost single-ended-to-differential solution is provided on the Customer Evaluation Board.

DS624F2

9

�CS5368 3. CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONS

GND = 0 V, all voltages with respect to 0 V. Parameter

DC Power Supplies: Positive Analog Positive Crystal Positive Digital Positive Serial Logic Positive Control Logic (-CQZ) (-DQZ)

Symbol

VA VX VD VLS VLC TAC TAA

Min

4.75 4.75 3.14 1.711 1.71 -40 -40

Typ

5.0 5.0 3.3 3.3 3.3 -

Max

Unit

5.25

V

Ambient Operating Temperature

85 105

°C

1. TDM Quad-Speed Mode specified to operate correctly at VLS ≥ 3.14 V.

ABSOLUTE RATINGS

Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes. Transient currents up to ±100 mA on the analog input pins will not cause SCR latch-up. Parameter

DC Power Supplies: Positive Analog Positive Crystal Positive Digital Positive Serial Logic Positive Control Logic

Symbol

VA VX VD VLS VLC Iin VIN VIND TA Tstg

Min

Typ

Max

Units

-0.3

-

+6.0

V

Input Current Analog Input Voltage Digital Input Voltage Ambient Operating Temperature (Power Applied) Storage Temperature

-10 -0.3 -50 -65 -

+10 VA+0.3 VL+0.3 +95 +150

mA V °C

SYSTEM CLOCKING

Parameter

Input Master Clock Frequency Input Master Clock Duty Cycle

Symbol

MCLK tclkhl

Min

0.512 40

Typ

Max

55.05 60

Unit

MHz %

10

DS624F2

�CS5368 DC POWER

MCLK = 12.288 MHz; Master Mode; GND = 0 V. Parameter

Power Supply Current (Normal Operation) VA = 5 V VX = 5 V VD = 5 V VD = 3.3 V VLS, VLC = 5 V VLS, VLC = 3.3 V VA = VX = 5 V VLS, VLC, VD = 5 V

Symbol

IA IX ID ID IL IL IA ID+L -

Min

Typ

100 4 70 42 12 5 50 500 930 675 2.75

Max

112 8 88 50 15 8 1115 792 -

Unit

-

mA

Power Supply Current (Power-Down) (Note 1)

-

μA

Power Consumption Normal Operation All Supplies = 5 V VA = VX = 5 V, VD = VLS = VLC = 3.3 V (Power-Down) (Note 1)

-

mW

1. Power-Down is defined as RST = LOW with all clocks and data lines held static at a valid logic level.

LOGIC LEVELS

Parameter

High-Level Input Voltage Low-Level Input Voltage High-Level Output Voltage at 100 μA load Low-Level Output Voltage at -100 μA load OVFL Current Sink Input Leakage Current logic pins only Iin -10 %VLS/VLC %VLS/VLC %VLS/VLC %VLS/VLC

Symbol

VIH VIL VOH VOL

Min

70 85 -

Typ

Max

30 15

Units

-

%

-4 10

mA μA

PSRR, VQ AND FILT+ CHARACTERISTICS

MCLK = 12.288 MHz; Master Mode. Valid with the recommended capacitor values on FILT+ and VQ as shown in the “Typical Connection Diagram”. Parameter

Power Supply Rejection Ratio at (1 kHz) VQ Nominal Voltage Output Impedance Maximum allowable DC current source/sink Filt+ Nominal Voltage Output Impedance Maximum allowable DC current source/sink

Symbol

PSRR

Min

-

Typ

65 VA/2 25 10 VA 4.4 10

Max

-

Unit

dB V kΩ μA V kΩ μA

-

-

DS624F2

11

�CS5368 ANALOG CHARACTERISTICS (COMMERCIAL)

Test Conditions (unless otherwise specified). VA = 5 V, VD = VLS = VLC 3.3 V, and TA = 25° C. Full-scale input sine wave. Measurement Bandwidth is 10 Hz to 20 kHz. Parameter

Single-Speed Mode Dynamic Range Total Harmonic Distortion + Noise referred to typical full scale Double-Speed Mode Dynamic Range Fs = 96 kHz A-weighted unweighted 40 kHz bandwidth unweighted -1 dB -20 dB -60 dB -1dB THD+N 108 105 114 111 108 -105 -91 -51 -102 114 111 108 -105 -91 -51 -102 110 0.1 -99 -45 dB Fs = 48 kHz A-weighted unweighted -1 dB -20 dB -60 dB THD+N 108 105 114 111 -105 -91 -51 -99 -45 dB dB

Symbol

Min

Typ

Max

Unit

Total Harmonic Distortion + Noise referred to typical full scale 40 kHz bandwidth Quad-Speed Mode Dynamic Range Fs = 192 kHz

dB

A-weighted unweighted 40 kHz bandwidth unweighted -1 dB -20 dB -60 dB -1dB THD+N

108 105 -

-99 -45 5 100 1.19*VA -

dB

Total Harmonic Distortion + Noise referred to typical full scale 40 kHz bandwidth

dB

Dynamic Performance for All Modes

Interchannel Isolation -5 HPF enabled HPF disabled 0 1.07*VA CMRR dB dB % ppm/°C LSB

DC Accuracy

Interchannel Gain Mismatch Gain Error Gain Drift Offset Error

± 100

1.13*VA 250 82

Analog Input Characteristics

Full-scale Differential Input Voltage Input Impedance (Differential) Common Mode Rejection Ratio Vpp kΩ dB

12

DS624F2

�CS5368 ANALOG CHARACTERISTICS (AUTOMOTIVE)

Test Conditions (unless otherwise specified). VA = 5.25 to 4.75 V, VD = 5.25 to 3.14 V, VLS = VLC = 5.25 to 1.71 V and TA = -40° to +85° C. Full-scale input sine wave. Measurement Bandwidth is 10 Hz to 20 kHz. Parameter

Single-Speed Mode Dynamic Range Total Harmonic Distortion + Noise referred to typical full scale Double-Speed Mode Dynamic Range Fs = 96 kHz A-weighted unweighted 40 kHz bandwidth unweighted -1 dB -20 dB -60 dB -1 dB THD+N 106 103 114 111 108 -105 -91 -51 -102 114 111 108 -105 -91 -51 -102 110 0.1 -97 -45 dB Fs = 48 kHz A-weighted unweighted -1 dB -20 dB -60 dB THD+N 106 103 114 111 -105 -91 -51 -97 -45 dB dB

Symbol

Min

Typ

Max

Unit

Total Harmonic Distortion + Noise referred to typical full scale 40 kHz bandwidth Quad-Speed Mode Dynamic Range Fs = 192 kHz

dB

A-weighted unweighted 40 kHz bandwidth unweighted -1 dB -20 dB -60 dB -1 dB THD+N

106 103 -

-97 -45 7 100 1.24*VA -

dB

Total Harmonic Distortion + Noise referred to typical full scale 40 kHz bandwidth

dB

Dynamic Performance for All Modes

Interchannel Isolation -7 HPF enabled HPF disabled 0 1.02*VA CMRR dB dB % ppm/°C LSB

DC Accuracy

Interchannel Gain Mismatch Gain Error Gain Drift Offset Error

± 100

1.13*VA 250 82

Analog Input Characteristics

Full-scale Input Voltage Input Impedance (Differential) Common Mode Rejection Ratio Vpp kΩ dB

DS624F2

13

�CS5368 DIGITAL FILTER CHARACTERISTICS

Parameter Single-Speed Mode (2 kHz to 54 kHz sample rates)

Passband (Note 1) Passband Ripple Stopband (Note 1) Stopband Attenuation Total Group Delay (Fs = Output Sample Rate) tgd (-0.1 dB) (-0.1 dB) 0 -0.035 0.58 -95 0 -0.035 0.68 -92 tgd (-0.1 dB) 0 -0.035 0.78 -92 tgd -3.0 dB -0.13 dB @ 20 Hz 5/Fs 1 20 10 105/Fs 9/Fs 0.24 0.035 12/Fs 0.45 0.035 0.47 0.035 Fs dB Fs dB s Fs dB Fs dB s Fs dB Fs dB s

Symbol

Min

Typ

Max

Unit

Double-Speed Mode (54 kHz to 108 kHz sample rates)

Passband (Note 1) Passband Ripple Stopband (Note 1) Stopband Attenuation Total Group Delay (Fs = Output Sample Rate)

Quad-Speed Mode (108 kHz to 216 kHz sample rates)

Passband (Note 1) Passband Ripple Stopband (Note 1) Stopband Attenuation Total Group Delay (Fs = Output Sample Rate)

High-Pass Filter Characteristics

Frequency Response (Note 2) Phase Deviation (Note 2) Passband Ripple Filter Settling Time 0 Hz Deg dB s

Notes: 1. The filter frequency response scales precisely with Fs. 2. Response shown is for Fs equal to 48 kHz. Filter characteristics scale with Fs.

OVERFLOW TIMEOUT

Logic "0" = GND = 0 V; Logic "1" = VLS; CL = 30 pF, timing threshold is 50% of VLS. Parameter OVFL time-out on overrange condition

Fs = 44.1 kHz Fs = 192 kHz -

Symbol

Min

Typ

(217-1)/Fs 2972 683

Max

-

Unit

ms

14

DS624F2

�CS5368 SERIAL AUDIO INTERFACE - I²S/LJ TIMING

The serial audio port is a three-pin interface consisting of SCLK, LRCK and SDOUT. Logic "0" = GND = 0 V; Logic "1" = VLS; CL = 20 pF, timing threshold is 50% of VLS. Parameter

Sample Rates Single-Speed Mode Double-Speed Mode Quad-Speed Mode

Symbol

-

Min

2 54 108 64*Fs 72.3 40 28 20 20 10 20 10 5 72.3 28 20 20 4 10 10 20 10 5

Typ

-

Max

54 108 216 64*Fs 60 38 -

Unit

kHz

Master Mode

SCLK Frequency SCLK Period SCLK Duty Cycle (Note 1) LRCK setup LRCK hold SDOUT setup SDOUT hold 1/(64*216 kHz) (CLKMODE = 0)(Note 2) (CLKMODE = 1)(Note 2) before SCLK rising after SCLK rising before SCLK rising after SCLK rising (VLS = 1.8 V) after SCLK rising (VLS = 3.3 V) after SCLK rising (VLS = 5 V) tPERIOD tHIGH tHIGH tSETUP1 tHOLD1 tSETUP2 tHOLD2 tHOLD2 tHOLD2 tPERIOD tHIGH tSETUP1 tHOLD1 tSETUP2 tSETUP2 tSETUP2 tHOLD2 tHOLD2 tHOLD2 50 33 Hz ns % % ns

-

-

ns

Slave Mode

SCLK Frequency (Note 3) SCLK Period SCLK Duty Cycle LRCK setup LRCK hold SDOUT setup 1/(64*216 kHz) before SCLK rising after SCLK rising before SCLK rising (VLS = 1.8 V) before SCLK rising (VLS = 3.3 V) before SCLK rising (VLS = 5 V) after SCLK rising (VLS = 1.8 V) after SCLK rising (VLS = 3.3 V) after SCLK rising (VLS = 5 V) 64*Fs 65 Hz ns % ns

SDOUT hold

-

-

ns

Notes: 1. Duty cycle of generated SCLK depends on duty cycle of received MCLK as specified under “System Clocking” on page 10. 2. CLKMODE functionality described in Section 4.6.3 "Master Mode Clock Dividers" on page 24. 3. In Slave Mode, the SCLK/LRCK ratio can be set according to preference. However, chip performance is guaranteed only when using the ratios in Section 4.7 Master and Slave Clock Frequencies on page 25.

t PERIOD SCLK t HOLD1 LRCK channel tSET UP1 channel t SET UP2 SDOUT data data t HOLD2 t HIGH

Figure 3. I²S/LJ Timing

DS624F2

15

�CS5368 SERIAL AUDIO INTERFACE - TDM TIMING

The serial audio port is a three-pin interface consisting of SCLK, LRCK and SDOUT. Logic "0" = GND = 0 V; Logic "1" = VLS; CL = 20 pF, timing threshold is 50% of VLS. Parameter

Sample Rates Single-Speed Mode Double-Speed Mode Quad-Speed Mode1

Symbol

-

Min

2 54 108 256*Fs 18 40 28 20 18 5 128 5 5 18 28 20 20 10 1 5 5

Typ

50 33 256*Fs -

Max

54 108 216 256*Fs 60 38 128 65 244 -

Unit

kHz kHz kHz Hz ns % % ns ns ns ns ns Hz ns % ns ns ns ns ns

Master Mode

SCLK Frequency SCLK Period SCLK Duty Cycle (Note 2) FS setup FS setup FS setup FS width SDOUT setup SDOUT hold 1/(256*216 kHz) (CLKMODE = 0)(Note 3) (CLKMODE = 1)(Note 3) tPERIOD tHIGH1 tHIGH1 tSETUP1 tSETUP1 tSETUP1 tHIGH2 tSETUP2 tHOLD2

before SCLK rising (Single-Speed Mode) before SCLK rising (Double-Speed Mode) before SCLK rising (Quad-Speed Mode) in SCLK cycles before SCLK rising after SCLK rising

Slave Mode

SCLK Frequency (Note 4) SCLK Period SCLK Duty Cycle FS setup FS setup FS setup FS width SDOUT setup SDOUT hold 1/(256*216 kHz) tPERIOD tHIGH1 tSETUP1 tSETUP1 tSETUP1 tHIGH2 tSETUP2 tHOLD2

before SCLK rising (Single-Speed Mode) before SCLK rising (Double-Speed Mode) before SCLK rising (Quad-Speed Mode) in SCLK cycles before SCLK rising after SCLK rising

Notes: 1. TDM Quad-Speed Mode only specified to operate correctly at VLS ≥ 3.14 V. 2. Duty cycle of generated SCLK depends on duty cycle of received MCLK as specified under “System Clocking” on page 10. 3. CLKMODE functionality described in Section 4.6.3 "Master Mode Clock Dividers" on page 24. 4. In Slave Mode, the SCLK/LRCK ratio can be set according to preference; chip performance is guaranteed only when using the ratios in Section 4.7 Master and Slave Clock Frequencies on page 25.

t PERIOD t HIGH1

SCLK t SETUP1 FS t SETUP2 SDOUT data data

t HIGH2

new frame t HOLD2 data

Figure 4. TDM Timing

16

DS624F2

�CS5368 SWITCHING SPECIFICATIONS - CONTROL PORT - I²C TIMING

Inputs: Logic 0 = DGND, Logic 1 = VLC, SDA CL = 30 pF Parameter

SCL Clock Frequency RST Rising Edge to Start Bus Free Time Between Transmissions Start Condition Hold Time (prior to first clock pulse) Clock Low time Clock High Time Setup Time for Repeated Start Condition SDA Hold Time from SCL Falling SDA Setup time to SCL Rising Rise Time of SCL and SDA Fall Time SCL and SDA Setup Time for Stop Condition Acknowledge Delay from SCL Falling (Note 1)

Symbol

fscl tirs tbuf thdst tlow thigh tsust thdd tsud trc tfc tsusp tack

Min

600 4.7 4.0 4.7 4.0 4.7 0 600 4.7 300

Max

100

Unit

kHz ns µs

-

µs

ns 1 300 1000 µs ns µs ns

Notes: 1. Data must be held for sufficient time to bridge the transition time, tfc, of SCL.

RST t Stop irs Sta rt

Re p e at e d Sta rt t rd t fd Stop

SDA t buf t hdst t high t hdst t fc t susp

S CL t t t sud t ack t sust t rc

lo w

hdd

Figure 5. I²C Timing

DS624F2

17

�CS5368 SWITCHING SPECIFICATIONS - CONTROL PORT - SPI TIMING

Inputs: Logic 0 = DGND, Logic 1 = VLC, CDOUT CL = 30 pF Parameter

CCLK Clock Frequency RST Rising Edge to CS Falling CS Falling to CCLK Edge CS High Time Between Transmissions CCLK Low Time CCLK High Time CDIN to CCLK Rising Setup Time CCLK Rising to DATA Hold Time CCLK Falling to CDOUT Stable Rise Time of CDOUT Fall Time of CDOUT Rise Time of CCLK and CDIN Fall Time of CCLK and CDIN (Note 2) (Note 2) (Note 1)

Symbol

fsck tsrs tcss tcsh tscl tsch tdsu tdh tpd tr1 tf1 tr2 tf2

Min

0 20 20 1.0 66 66 40 15

Max

6.0

Units

MHz ns μs

-

50 25 100

ns

Notes: 1. Data must be held for sufficient time to bridge the transition time of CCLK. 2. For fsck