EP9312 Data Sheet

FEATURES

•

•

•

•

•

•

•

•

Linux®, Microsoft® Windows® CE-enabled MMU

100-MHz System Bus

MaverickCrunch™ Math Engine

• Floating Point, Integer, and Signal Processing

Instructions

• Optimized for digital music compression and

decompression algorithms.

• Hardware interlocks allow in-line coding.

Peripheral Bus

w/

12 DMA

CHANNEL

CRC

DMA

(3) UARTs

w/

IrDA

(3) USB

Hosts

•

Clocks &

Timers

MaverickCrunchTM

Interrupts

& GPIO

ARM920T

TM

MaverickKeyTM

MaverickLock

Boot

ROM

D-Cache

16KB

I-Cache

16KB

MMU

Bus

Bridge

Keypad &

Touch

Screen I/F

USER INTERFACE

Serial

Audio

Interface

IrDA Interface

8 x 8 Keypad Scanner

One Serial Peripheral Interface (SPI) Port

• 6-channel or 2-channel Serial Audio Interface (I2S)

• 2-channel, Low-cost Serial Audio Interface (AC'97)

• 2 High-resolution PWMs (16 bits each)

Internal Peripherals

• 12 Direct Memory Access (DMA) Channels

• Real-time Clock with Software Trim

• Dual PLL controls all clock domains.

• Watchdog Timer

• Two General-purpose 16-bit Timers

• One General-purpose 32-bit Timer

• One 40-bit Debug Timer

• Interrupt Controller

• Boot ROM

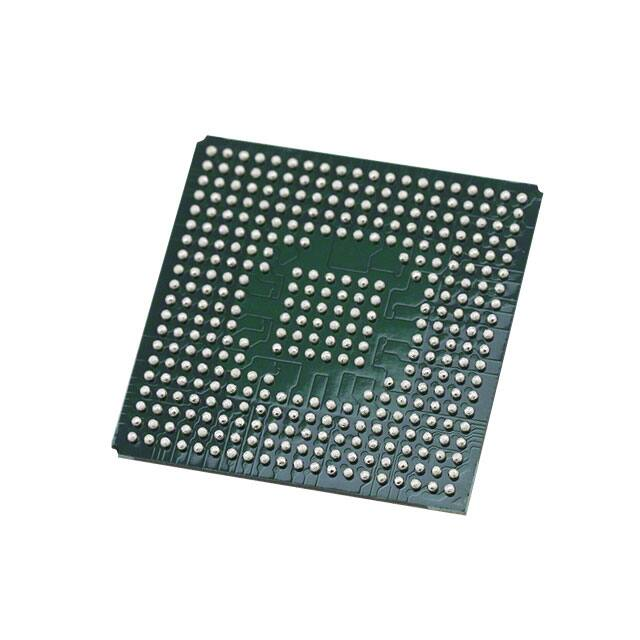

Package

• 352 pin PBGA

•

MaverickKey™ IDs

• 32-bit unique ID can be used for DRM-compliant,

128-bit random ID.

Integrated Peripheral Interfaces

• 32-bit SDRAM Interface (up to 4 banks)

• 32/16-bit SRAM / FLASH / ROM

• Serial EEPROM Interface

• EIDE (up to 2 devices)

• 1/10/100 Mbps Ethernet MAC

• Three UARTs

• Three-port USB 2.0 Full-speed Host (OHCI)

(12 Mbits per second)

• LCD and Raster Interface

• Touchscreen Interface with ADC

COMMUNICATIONS PORTS

•

Universal Platform

System-on-chip Processor

200-MHz ARM920T Processor

• 16-kbyte Instruction Cache

• 16-kbyte Data Cache

Processor Bus

Ethernet

MAC

EIDE

I/F

SRAM &

Flash I/F

Unified

SDRAM I/F

Video/LCD

Controller

MEMORY AND STORAGE

Copyright 2010 Cirrus Logic (All Rights Reserved)

http://www.cirrus.com

Mar ‘10

DS515F2

1

�EP9312

Universal Platform SOC Processor

OVERVIEW

The EP9312 is an ARM920T-based system-on-a-chip

design with a large peripheral set targeted to a variety of

applications:

• Thin client computers for business and home

• Internet radio

• Internet access devices

• Industrial computers

• Specialized terminals

• Point of sale terminals

• Test and measurement equipment

The ARM920T microprocessor core with separate 16kbyte, 64-way set-associative instruction and data

caches is augmented by the MaverickCrunch™ coprocessor

enabling

high-speed

floating

point

calculations.

becoming unreliable. The MaverickKey unique IDs

provide OEMs with a method of utilizing specific

hardware IDs such as those assigned for SDMI (Secure

Digital Music Initiative) or any other authentication

mechanism.

A high-performance 1/10/100 Mbps Ethernet media

access Controller (EMAC) is included along with external

interfaces to SPI, I2S audio, Raster/LCD, IDE storage

peripherals, keypad, and touchscreen. A three-port USB

2.0 Full-speed Host (OHCI) (12 Mbits per second) and

three UARTs are included as well.

The EP9312 is a high-performance, low-power, RISCbased, single-chip computer built around an ARM920T

microprocessor core with a maximum operating clock

rate of 200 MHz (184 MHz for industrial conditions). The

ARM core operates from a 1.8 V supply, while the I/O

operates at 3.3 V with power usage between 100 mW

and 750 mW (dependent on speed).

MaverickKey™ unique hardware programmed IDs are a

solution to the growing concern over secure web content

and commerce. With Internet security playing an

important role in the delivery of digital media such as

books or music, traditional software methods are quickly

Table A. Change History

2

Revision

Date

Changes

PP1

March 2001

PP2

June 2001

PP3

August 2001

Upgrade to revision C silicon.

PP4

May 2003

Upgrade to revision D silicon.

PP5

December 2003

PP6

July 2004

PP7

February 2005

Update with most-current characterization data.

F1

February 2010

Removed “Preliminary Data” statement from legal disclaimer. Removed lead-containing device part numbers.

Increased minimum CVDD & VDD_PLL voltages from 1.65 V min. to 1.71 V min. Changed operating

temperatures to 0 to 60°C commercial, -40 to 70°C industrial.

F2

March 2010

Initial Release.

Upgrade to revision B silicon.

Update timing data.

Update AC data.

Add ADC data.

Increased commercial/industrial temperatures to 70/85 deg. C max.

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Table of Contents

FEATURES .........................................................................................................1

Overview .............................................................................................................2

Processor Core - ARM920T ......................................................................................... 6

MaverickCrunch™ Math Engine .................................................................................. 6

MaverickKey™ Unique ID ............................................................................................ 6

General Purpose Memory Interface (SDRAM, SRAM, ROM, FLASH) ........................ 6

IDE Interface ................................................................................................................ 7

Ethernet Media Access Controller (MAC) .................................................................... 7

Serial Interfaces (SPI, I2S, and AC ’97) ....................................................................... 7

Raster/LCD Interface ................................................................................................... 7

Touch Screen Interface with 12-bit Analog-to-digital Converter (ADC) ........................ 8

64-Key Keypad Interface ............................................................................................. 8

Universal Asynchronous Receiver/Transmitters (UARTs) ............................................ 8

Triple-port USB Host .................................................................................................... 9

Two-Wire Interface ....................................................................................................... 9

Real-time Clock with Software Trim ............................................................................. 9

PLL and Clocking ......................................................................................................... 9

Timers ........................................................................................................................ 10

Interrupt Controller ..................................................................................................... 10

Dual LED Drivers ....................................................................................................... 10

General Purpose Input/Output (GPIO) ....................................................................... 10

Reset and Power Management ................................................................................. 10

Hardware Debug Interface ..........................................................................................11

12-Channel DMA Controller ........................................................................................11

Internal Boot ROM ......................................................................................................11

Electrical Specifications .................................................................................12

Absolute Maximum Ratings ....................................................................................... 12

Recommended Operating Conditions ........................................................................ 12

DC Characteristics ..................................................................................................... 13

Timings .............................................................................................................14

Memory Interface ....................................................................................................... 15

IDE Interface .............................................................................................................. 30

Ethernet MAC Interface ............................................................................................ 43

Audio Interface ........................................................................................................... 45

AC’97 ........................................................................................................................ 49

LCD Interface ............................................................................................................ 50

ADC ........................................................................................................................... 51

JTAG .......................................................................................................................... 52

352 Pin BGA Package Outline .......................................................................53

352-Ball PBGA Diagram

.................................................................................. 53

352 Pin BGA Pinout (Bottom View) ........................................................................... 54

Acronyms and Abbreviations ........................................................................61

Units of Measurement .....................................................................................61

Ordering Information ......................................................................................62

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

3

�EP9312

Universal Platform SOC Processor

List of Figures

Figure 1. Timing Diagram Drawing Key ................................................................................. 14

Figure 2. SDRAM Load Mode Register Cycle Timing Measurement ..................................... 15

Figure 3. SDRAM Burst Read Cycle Timing Measurement ................................................... 16

Figure 4. SDRAM Burst Write Cycle Timing Measurement ................................................... 17

Figure 5. SDRAM Auto Refresh Cycle Timing Measurement ................................................ 18

Figure 6. Static Memory Single Word Read Cycle Timing Measurement .............................. 19

Figure 7. Static Memory Single Word Write Cycle Timing Measurement .............................. 20

Figure 8. Static Memory Multiple Word Read 8-bit Cycle Timing Measurement .................... 21

Figure 9. Static Memory Multiple Word Write 8-bit Cycle Timing Measurement .................... 22

Figure 10. Static Memory Multiple Word Read 16-bit Cycle Timing Measurement ................ 23

Figure 11. Static Memory Multiple Word Write 16-bit Cycle Timing Measurement ................ 24

Figure 12. Static Memory Burst Read Cycle Timing Measurement ....................................... 25

Figure 13. Static Memory Burst Write Cycle Timing Measurement ....................................... 26

Figure 14. Static Memory Single Read Wait Cycle Timing Measurement ............................. 27

Figure 15. Static Memory Single Write Wait Cycle Timing Measurement .............................. 28

Figure 16. Static Memory Turnaround Cycle Timing Measurement ....................................... 29

Figure 17. Register Transfer to/from Device .......................................................................... 31

Figure 18. PIO Data Transfer to/from Device ......................................................................... 33

Figure 19. Initiating an Ultra DMA data-in Burst ..................................................................... 35

Figure 20. Sustained Ultra DMA data-in Burst ....................................................................... 36

Figure 21. Host Pausing an Ultra DMA data-in Burst ............................................................. 36

Figure 22. Device Terminating an Ultra DMA data-in Burst ................................................... 37

Figure 23. Host Terminating an Ultra DMA data-in Burst ....................................................... 38

Figure 24. Initiating an Ultra DMA data-out Burst .................................................................. 39

Figure 25. Sustained Ultra DMA data-out Burst ..................................................................... 40

Figure 26. Device Pausing an Ultra DMA data-out Burst ....................................................... 40

Figure 27. Host Terminating an Ultra DMA data-out Burst .................................................... 41

Figure 28. Device Terminating an Ultra DMA data-out Burst ................................................. 42

Figure 29. Ethernet MAC Timing Measurement ..................................................................... 44

Figure 30. TI Single Transfer Timing Measurement ............................................................... 46

Figure 31. Microwire Frame Format, Single Transfer ............................................................ 46

Figure 32. SPI Format with SPH=1 Timing Measurement ..................................................... 47

Figure 33. Inter-IC Sound (I2S) Timing Measurement ........................................................... 48

Figure 34. AC ‘97 Configuration Timing Measurement .......................................................... 49

Figure 35. LCD Timing Measurement .................................................................................... 50

Figure 36. ADC Transfer Function ......................................................................................... 51

Figure 37. JTAG Timing Measurement .................................................................................. 52

Figure 38. 352 Pin PBGA Pin Diagram .................................................................................. 53

Figure 40. 352 PIN BGA PINOUT

................................................................................... 55

4

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

List of Tables

Table A. Change History .......................................................................................................... 2

Table B. General Purpose Memory Interface Pin Assignments .............................................. 6

Table C. IDE Interface Pin Assignments .................................................................................. 7

Table D. Ethernet Media Access Controller Pin Assignments ................................................. 7

Table E. Audio Interfaces Pin Assignment .............................................................................. 7

Table F. LCD Interface Pin Assignments ................................................................................ 8

Table G. Touch Screen Interface with 12-bit Analog-to-Digital Converter Pin Assignments ... 8

Table H. 64-Key Keypad Interface Pin Assignments ............................................................... 8

Table I. Universal Asynchronous Receiver/Transmitters Pin Assignments ............................ 9

Table J. Triple Port USB Host Pin Assignments ..................................................................... 9

Table K. Two-Wire Port with EEPROM Support Pin Assignments .......................................... 9

Table L. Real-Time Clock with Pin Assignments ..................................................................... 9

Table M.PLL and Clocking Pin Assignments ........................................................................ 10

Table N. Interrupt Controller Pin Assignment ........................................................................ 10

Table O. Dual LED Pin Assignments ..................................................................................... 10

Table P. General Purpose Input/Output Pin Assignment ...................................................... 10

Table Q. Reset and Power Management Pin Assignments ................................................... 10

Table R. Hardware Debug Interface ...................................................................................... 11

Table R. 352 Pin Diagram Dimensions .................................................................................. 54

Table S. Pin Descriptions ..................................................................................................... 59

Table T. Pin Multiplex Usage Information ............................................................................. 60

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

5

�EP9312

Universal Platform SOC Processor

Processor Core - ARM920T

The ARM920T is a Harvard architecture processor with

separate 16-kbyte instruction and data caches with an 8word line length but a unified memory. The processor

utilizes a five-stage pipeline consisting of fetch, decode,

execute, memory, and write stages. Key features include:

•

•

•

•

•

•

•

•

ARM (32-bit) and Thumb (16-bit compressed)

Instruction Sets

32-bit Advanced Microcontroller Bus Architecture

(AMBA)

16-kbyte Instruction Cache with lockdown

16-kbyte Data Cache (programmable write-through or

write-back) with Lockdown

MMU for Linux®, Microsoft® Windows® CE, and other

operating systems

Translation Look Aside Buffers with 64 Data and 64

Instruction Entries

Programmable Page Sizes of 1 Mbyte, 64 kbyte,

4 kbyte, and 1 kbyte

Independent lockdown of TLB Entries

MaverickCrunch™ Math Engine

The MaverickCrunch Engine is a mixed-mode

coprocessor designed primarily to accelerate the math

processing required to rapidly encode digital audio

formats. It accelerates single- and double-precision

integer and floating point operations plus an integer

multiply-accumulate

(MAC)

instruction

that

is

considerably faster than the ARM920T's native MAC

instruction. The ARM920T coprocessor interface is

utilized thereby sharing its memory interface and

instruction stream. Hardware forwarding and interlock

allows the ARM to handle looping and addressing while

MaverickCrunch handles computation. Features include:

•

•

•

•

•

•

•

•

IEEE-754 single and double-precision floating point

32 / 64-bit integer

Add / multiply / compare

Integer MAC 32-bit input with 72-bit accumulate

Integer Shifts

Floating point to/from integer conversion

Sixteen 64-bit register files

Four 72-bit accumulators

provide OEMs with a method of utilizing specific

hardware IDs such as those assigned for SDMI (Secure

Digital Music Initiative) or any other authentication

mechanism.

Both a specific 32-bit ID as well as a 128-bit random ID

are programmed into the EP9312 through the use of

laser probing technology. These IDs can then be used to

match secure copyrighted content with the ID of the

target device the EP9312 is powering, and then deliver

the copyrighted information over a secure connection. In

addition, secure transactions can benefit by also

matching device IDs to server IDs. MaverickKey IDs

provide a level of hardware security required for today’s

Internet appliances.

General Purpose Memory Interface (SDRAM,

SRAM, ROM, FLASH)

The EP9312 features a unified memory address model

where all memory devices are accessed over a common

address/data bus. A separate internal port is dedicated to

the read-only Raster/LCD refresh engine, while the rest

of the memory accesses are performed via the Processor

bus. The SRAM memory controller supports 8, 16 and

32-bit devices and accommodates an internal boot ROM

concurrently with 32-bit SDRAM memory.

•

•

•

•

1 to 4 banks of 32-bit, 66- or 100-MHz SDRAM

One internal port dedicated to the Raster/LCD

Refresh Engine (Read Only)

Address and data bus shared between SDRAM,

SRAM, ROM, and FLASH memory

NOR FLASH memory supported

Table B. General Purpose Memory Interface Pin Assignments

Pin Mnemonic

Pin Description

SDCLK

SDRAM Clock

SDCLKEN

SDRAM Clock Enable

SDCSn[3:0]

SDRAM Chip Selects 3-0

RASn

SDRAM RAS

CASn

SDRAM CAS

SDWEn

SDRAM Write Enable

CSn[7:6] and CSn[3:0]

Chip Selects 7, 6, 3, 2, 1, 0

AD[25:0]

Address Bus 25-0

MaverickKey™ Unique ID

DA[31:0]

Data Bus 31-0

DQMn[3:0]

SDRAM Output Enables / Data Masks

MaverickKey unique hardware programmed IDs are a

solution to the growing concern over secure web content

and commerce. With Internet security playing an

important role in the delivery of digital media such as

books or music, traditional software methods are quickly

becoming unreliable. The MaverickKey unique IDs

WRn

SRAM Write Strobe

RDn

SRAM Read / OE Strobe

WAITn

SRAM Wait Input

6

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

IDE Interface

Serial Interfaces (SPI, I2S, and AC ’97)

The IDE Interface provides an industry-standard

connection to two AT Advanced Packet Interface (ATAPI)

compliant devices. The IDE port will attach to a master

and a slave device. The internal DMA controller performs

all data transfers using the Multiword DMA and Ultra

DMA modes. The interface supports the following

operating modes:

The SPI port can be configured as a master or a slave,

supporting the National Semiconductor®, Motorola®, and

Texas Instruments® signaling protocols.

•

•

PIO Modes 0 thru 4

Ultra DMA Modes 0 thru 3

Table C. IDE Interface Pin Assignments

Pin Mnemonic

Pin Description

The AC'97 port supports multiple codecs for multichannel

audio output with a single stereo input. Three I2S ports

can be configured to support six-channel, 24-bit audio.

These ports are multiplexed so that I2S port 0 will take

over either the AC'97 pins or the SPI pins. The second

and third I2S ports' serial input and serial output pins are

multiplexed with EGPIO[4,5,6,13]. The clocks supplied in

the first I2S port are also used for the second and third

I2S ports.

DD[15-0]

IDE Data bus

IDEDA[2-0]

IDE Device address

•

Normal Mode: One SPI Port and one AC’97 Port

IDECSn[0,1]

IDE Chip Select 0 and 1

•

I2S on SSP Mode: One AC’97 Port and up to three I2S

Ports

•

I2S on AC’97 Mode: One SPI Port and up to three I2S

Ports

DIORn

IDE Read Strobe

DIOWn

IDE Write Strobe

DMACKn

IDE DMA acknowledge

Ethernet Media Access Controller (MAC)

The MAC subsystem is compliant with the ISO/TEC

802.3 topology for a single shared medium with several

stations. Multiple MII-compliant PHYs are supported.

Features include:

•

•

Supports 1/10/100 Mbps transfer rates for home /

small-business / large-business applications

Interfaces to an off-chip PHY through industry

standard Media Independent Interface (MII)

‘

Table E. Audio Interfaces Pin Assignment

Pin

Name

Normal Mode

I2S on SSP

Mode

I2S on AC'97

Mode

Pin

Description

Pin Description

Pin Description

SCLK1

SPI Bit Clock

SFRM1

SPI Frame Clock I2S Frame Clock

SSPRX1 SPI Serial Input

SSPTX1

SPI Serial

Output

Pin Description

MDC

Management Data Clock

MDIO

Management Data I/O

RXCLK

Receive Clock

MIIRXD[3:0]

Receive Data

RXDVAL

Receive Data Valid

RXERR

Receive Data Error

TXCLK

Transmit Clock

SPI Frame Clock

I2S Serial Input

SPI Serial Input

I2S Serial Output

SPI Serial Output

ARSTn

AC'97 Reset

ABITCLK AC'97 Bit Clock

AC'97 Reset

I2S Master Clock

AC'97 Bit Clock

I2S Serial Clock

ASYNC

AC'97 Frame

Clock

AC'97 Frame

Clock

I2S Frame Clock

ASDI

AC'97 Serial

Input

AC'97 Serial Input

I2S Serial Input

ASDO

AC'97 Serial

Output

AC'97 Serial

Output

I2S Serial Output

Raster/LCD Interface

MIITXD[3:0]

Transmit Data

TXEN

Transmit Enable

TXERR

Transmit Error

CRS

Carrier Sense

CLD

Collision Detect

DS515F2

SPI Bit Clock

(No I2S Master

Clock)

Table D. Ethernet Media Access Controller Pin Assignments

Pin Mnemonic

I2S Serial Clock

The Raster/LCD interface provides data and interface

signals for a variety of display types. It features fully

programmable video interface timing for non-interlaced

flat panel or dual scan displays. Resolutions up to

1024 x 768 are supported from a unified SDRAM based

frame buffer. A 16-bit PWM provides control for LCD

panel contrast.

Copyright 2010 Cirrus Logic (All Rights Reserved)

7

�EP9312

Universal Platform SOC Processor

LCD-specific features include:

•

•

•

•

•

•

•

•

Table G. Touch Screen Interface with 12-bit Analog-to-Digital

Converter Pin Assignments

Timing and interface signals for digital LCD and TFT

displays

Full programmability for either non-interlaced or dualscan color and grayscale flat panel displays

Dedicated data path to SDRAM controller for

improved system performance

Pixel depths of 4, 8, 16, or 24 bits per pixel or 256

levels of grayscale

Hardware Cursor up to 64 x 64 pixels

256 x 18 Color Lookup Table

Hardware Blinking

8-bit interface to low-end panel

Table F. LCD Interface Pin Assignments

Pin Mnemonic

SPCLK

Pin Description

Pin Mnemonic

Yp, Ym

Touch screen ADC Y Axis

SXp, SXm

Touch screen ADC X Axis

Voltage Feedback

SYp, SYm

Touch screen ADC Y Axis

Voltage Feedback

64-Key Keypad Interface

The keypad circuitry scans an 8 x 8 array of 64 normally

open, single-pole switches. Any one or two keys

depressed will be de-bounced and decoded. An interrupt

is generated whenever a stable set of depressed keys is

detected. If the keypad is not utilized, the 16 column/row

pins may be used as general purpose I/O. The Keypad

interface:

•

Pixel Clock

P[17:0]

Pixel Data Bus [17:0]

HSYNC / LP

Horizontal

Synchronization / Line Pulse

VCSYNC / FP

Vertical or Composite

Synchronization / Frame Pulse

BLANK

Composite Blank

BRIGHT

Pulse Width Modulated Brightness

•

•

•

•

•

•

•

Support for 4-, 5-, 7-, or 8-wire analog resistive touch

screens.

Flexibility - unused lines may be used for temperature

sensing or other functions.

Touch screen interrupt function.

Table G. Touch Screen Interface with 12-bit Analog-to-Digital

Converter Pin Assignments

Pin Mnemonic

Xp, Xm

Pin Description

Touch screen ADC X Axis

Pin Mnemonic

Pin

Description

Alternative Usage

COL[7:0]

Key Matrix Column

Inputs

General Purpose I/O

ROW[7:0]

Key Matrix Row

Inputs

General Purpose I/O

Universal Asynchronous

Receiver/Transmitters (UARTs)

Three 16550-compatible UARTs are supplied. Two

provide asynchronous HDLC (High-level Data Link

Control) protocol support for full duplex transmit and

receive. The HDLC receiver handles framing, address

matching, CRC checking, control-octet transparency, and

optionally passes the CRC to the host at the end of the

packet. The HDLC transmitter handles framing, CRC

generation, and control-octet transparency. The host

must assemble the frame in memory before

transmission. The HDLC receiver and transmitter use the

UART FIFOs to buffer the data streams. A third IrDA®

compatible UART is also supplied.

•

8

Provides scanning, debounce, and decoding for a 64key switch array.

Scans an 8-row by 8-column matrix.

May decode 2 keys at once.

Generates an interrupt when a new stable key is

determined.

Also generates a 3-key reset interrupt.

Table H. 64-Key Keypad Interface Pin Assignments

Touch Screen Interface with 12-bit Analogto-digital Converter (ADC)

The touch screen interface performs all sampling,

averaging, ADC range checking, and control for a wide

variety of analog resistive touch screens. This controller

only interrupts the processor when a meaningful change

occurs. The touch screen hardware may be disabled and

the switch matrix and ADC controlled directly if desired.

Features include:

Pin Description

UART1 supports modem bit rates up to 115.2 Kbps,

supports HDLC and includes a 16 byte FIFO for

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

•

•

receive and a 16 byte FIFO for transmit. Interrupts are

generated on Rx, Tx and modem status change.

UART2 contains an IrDA encoder operating at either

the slow (up to 115 Kbps), medium (0.576 or 1.152

Mbps), or fast (4 Mbps) IR data rates. It also has a 16

byte FIFO for receive and a 16 byte FIFO for transmit.

UART3 supports HDLC and includes a 16 byte FIFO

for receive and a 16 byte FIFO for transmit. Interrupts

are generated on Rx and Tx.

•

•

•

•

Fetches endpoint descriptors and transfer descriptors

Accesses endpoint data from system memory

Accesses the HC communication area

Writes status and retire transfer descriptor

Table J. Triple Port USB Host Pin Assignments

Pin Mnemonic

Pin Name - Description

USBp[2:0]

USB Positive signals

USBm[2:0]

USB Negative Signals

Table I. Universal Asynchronous Receiver/Transmitters Pin

Assignments

Pin Mnemonic

Pin Name - Description

Two-wire Interface

The two-wire interface provides communication and

control for synchronous-serial-driven devices.

TXD0

UART1 Transmit

RXD0

UART1 Receive

CTSn

UART1 Clear To Send /

Transmit Enable

Table K. Two-Wire Port with EEPROM Support Pin Assignments

DSRn / DCDn

UART1 Data Set Ready /

Data Carrier Detect

Pin Mnemonic

DTRn

UART1 Data Terminal Ready

RTSn

UART1 Ready To Send

EGPIO[0] / RI

UART1 Ring Indicator

TXD1 / SIROUT

UART2 Transmit /

IrDA Output

RXD1 / SIRIN

UART2 Receive / IrDA Input

TXD2

UART3 Transmit

RXD2

UART3 Receive

EGPIO[3] / TENn

HDLC3 Transmit Enable

Triple-port USB Host

Alternative

Usage

EECLK

Two-wire Interface Clock

General

Purpose I/O

EEDATA

Two-wire Interface Data

General

Purpose I/O

Real-time Clock with Software Trim

The software trim feature on the real time clock (RTC)

provides software controlled digital compensation of the

32.768 kHz input clock. This compensation is accurate to

±1.24 sec/month.

Note:

The USB Open Host Controller Interface (Open HCI)

provides full-speed serial communications ports at a

baud rate of 12 Mbits/sec. Up to 127 USB devices

(printer, mouse, camera, keyboard, etc.) and USB hubs

can be connected to the USB host in the USB “tiered

star” topology.

Pin Name - Description

A real time clock must be connected to RTCXTALI or

the EP9312 device will not boot.

Table L. Real-Time Clock with Pin Assignments

Pin Mnemonic

Pin Name - Description

RTCXTALI

Real-Time Clock Oscillator Input

This includes the following features:

RTCXTALO

Real-Time Clock Oscillator Output

•

•

•

PLL and Clocking

Compliance with the USB 2.0 specification

Compliance with the Open HCI Rev 1.0 specification

Supports both low speed (1.5 Mbps) and full speed

(12 Mbps) USB device connections

• Root HUB integrated with 3 downstream USB ports

• Transceiver buffers integrated, over-current protection

on ports

• Supports power management

• Operates as a master on the bus

The Open HCI host controller initializes the master DMA

transfer with the AHB bus:

DS515F2

The Processor and the Peripheral Clocks operate from a

single 14.7456 MHz crystal.

The Real Time Clock operates from a 32.768 kHz

external oscillator.

Copyright 2010 Cirrus Logic (All Rights Reserved)

9

�EP9312

Universal Platform SOC Processor

Table M. PLL and Clocking Pin Assignments

Pin Mnemonic

Pin Name - Description

XTALI

Main Oscillator Input

XTALO

Main Oscillator Output

VDD_PLL

Main Oscillator Power

GND_PLL

Main Oscillator Ground

Timers

The Watchdog Timer ensures proper operation by

requiring periodic attention to prevent a reset-on-timeout.

Two 16-bit timers operate as free-running down counters

or as periodic timers for fixed-interval interrupts and have

a range of 0.03 ms to 4.27 seconds.

One 32-bit timer, plus a 6-bit prescale counter, has a

range of 0.03 μs to 73.3 hours.

One 40-bit debug timer, plus a 6-bit prescale counter, has

a range of 1.0 μs to 12.7 days.

Interrupt Controller

The interrupt controller allows up to 64 interrupts to

generate an Interrupt Request (IRQ) or Fast Interrupt

Request (FIQ) signal to the processor core. Thirty-two

hardware priority assignments are provided for assisting

IRQ vectoring, and two levels are provided for FIQ

vectoring. This allows time-critical interrupts to be

processed in the shortest time possible. Internal

interrupts may be programmed as active high or active

low level sensitive inputs. External interrupts may be

programmed as active-high level-sensitive, active-low

level-sensitive,

rising-edge-triggered,

falling-edgetriggered, or combined rising/falling-edge-triggered.

•

•

•

•

•

Supports 64 interrupts from a variety of sources (such

as UARTs, GPIO, and key matrix)

Routes interrupt sources to either the ARM920T’s

IRQ or FIQ (Fast IRQ) inputs

Four dedicated off-chip interrupt lines INT[3:0]

operate as level-sensitive interrupts

Any of the 16 GPIO lines maybe configured to

generate interrupts

Software-supported priority mask for all FIQs and

IRQs

Dual LED Drivers

Two pins are assigned specifically to drive external

LEDs.

Table O. Dual LED Pin Assignments

Pin Mnemonic

Pin Name Description

GRLED

Green LED

General Purpose I/O

REDLED

Red LED

General Purpose I/O

Alternative Usage

General Purpose Input/Output (GPIO)

The 16 EGPIO pins may each be configured individually

as an output, an input, or an interrupt input.

There are 23 pins that may alternatively be used as input,

output, but do not support interrupts. These pins are:

• Key Matrix ROW[7:0], COL[7:0]

• Ethernet MDIO

• Both LED Outputs

• Two-wire Clock and Data

• SLA [1:0]

6 pins may alternatively be used as inputs only:

• CTSn, DSRn / DCDn

• 4 Interrupt Lines

2 pins may alternatively be used as outputs only:

• RTSn

• ARSTn

Table P. General Purpose Input/Output Pin Assignment

Pin Mnemonic

EGPIO[15:0]

Pin Name - Description

Expanded General Purpose Input / Output

Pins with Interrupts

Reset and Power Management

The chip may be reset through the PRSTn pin or through

the open drain common reset pin, RSTOn.

Clocks are managed on a peripheral-by-peripheral basis

and may be turned off to conserve power.

The processor clock is dynamically adjustable from 0 to

200 MHz (184 MHz for industrial conditions).

Table Q. Reset and Power Management Pin Assignments

Table N. External Interrupt Controller Pin Assignment

Pin Mnemonic

INT[3:0]

10

Pin Name - Description

Pin Mnemonic

Pin Name - Description

PRSTn

Power On Reset

RSTOn

User Reset In/Out – Open Drain –

Preserves Real Time Clock value

External Interrupt 3-0

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Hardware Debug Interface

12-channel DMA Controller

The JTAG interface allows use of ARM’s Multi-ICE or

other in-circuit emulators.

The DMA module contains 12 separate DMA channels.

Ten of these may be used for peripheral-to-memory or

memory-to-peripheral access. Two of these are

dedicated to memory-to-memory transfers. Each DMA

channel is connected to the 16-bit DMA request bus.

Table R. Hardware Debug Interface

Pin Mnemonic

Pin Name - Description

TCK

JTAG Clock

TDI

JTAG Data In

TDO

JTAG Data Out

TMS

JTAG Test Mode Select

TRSTn

JTAG Port Reset

The request bus is a collection of requests, Serial Audio

and UARTs. Each DMA channel can be used

independently or dedicated to any request signal. For

each DMA channel, source and destination addressing

can be independently programmed to increment,

decrement, or stay at the same value. All DMA

addresses are physical, not virtual addresses.

Internal Boot ROM

The Internal 16 Kbyte ROM allows booting from FLASH

memory, SPI or UART. Consult the EP93xx User’s Guide

for operational details.

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

11

�EP9312

Universal Platform SOC Processor

Electrical Specifications

Absolute Maximum Ratings

(All grounds = 0 V, all voltages with respect to 0 V)

Parameter

Power Supplies

Total Power Dissipation

Symbol

Min

Max

Unit

RVDD

CVDD

VDD_PLL

VDD_ADC

-

3.96

2.16

2.16

3.96

V

V

V

V

-

2

W

(Note 1)

Input Current per Pin, DC (Except supply pins)

-

±10

mA

Output current per pin, DC

-

±50

mA

-0.3

RVDD+0.3

V

-40

+125

°C

Digital Input voltage

(Note 2)

Storage temperature

Note:

1. Includes all power generated by AC and/or DC output loading.

2. The power supply pins are at recommended maximum values.

WARNING: Operation beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Recommended Operating Conditions

(All grounds = 0 V, all voltages with respect to 0 V)

Parameter

Symbol

Min

Typ

Max

Unit

RVDD

CVDD

VDD_PLL

VDD_ADC

3.0

1.71

1.71

3.0

3.3

1.80

1.80

3.3

3.6

1.94

1.94

3.6

V

V

V

V

Operating Ambient Temperature - Commercial

TA

0

+25

+70

°C

Operating Ambient Temperature - Industrial

TA

-40

+25

+85

°C

FCLK

-

-

200

MHz

Processor Clock Speed - Industrial

FCLK

-

-

184

MHz

System Clock Speed - Commercial

HCLK

-

-

100

MHz

System Clock Speed - Industrial

HCLK

-

-

92

MHz

Power Supplies

Processor Clock Speed - Commercial

12

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

DC Characteristics

(TA = 0 to 70° C; CVDD = VDD_PLL = 1.8; RVDD = 3.3 V;

All grounds = 0 V; all voltages with respect to 0 V unless otherwise noted)

Parameter

High level output voltage

Iout = -4 mA

Low level output voltage

Iout = 4 mA

Symbol

Min

Max

Unit

Voh

0.85 × RVDD

-

V

Vol

-

0.15 × RVDD

V

(Note 3)

High level input voltage

(Note 4)

Vih

0.65 × RVDD

VDD + 0.3

V

Low level input voltage

(Note 4)

Vil

-0.3

0.35 × RVDD

V

High level leakage current

Vin = 3.3 V

(Note 4)

Iih

-

10

µA

Low level leakage current

Vin = 0

(Note 4)

Iil

-

-10

µA

Parameter

Min

Typ

Max

Unit

Power Supply Pins (Outputs Unloaded)

Power Supply Current:

CVDD / VDD_PLL Total

RVDD

-

190

45

240

80

mA

mA

Low-Power Mode Supply Current

CVDD / VDD_PLL Total

RVDD

-

2

1.0

3.5

2

mA

mA

Note:

DS515F2

3. For open drain pins, high level output voltage is dependent on the external load.

4. All inputs that do not include internal pull-ups or pull-downs, must be externally driven for proper operation (See Table S on

page 59). If an input is not driven, it should be tied to power or ground, depending on the particular function. If an I/O pin is not

driven and programmed as an input, it should be tied to power or ground through its own resistor.

Copyright 2010 Cirrus Logic (All Rights Reserved)

13

�EP9312

Universal Platform SOC Processor

Timings

Timing Diagram Conventions

This data sheet contains one or more timing diagrams. The following key explains the components used in these

diagrams. Any variations are clearly labelled when they occur. Therefore, no additional meaning should be attached

unless specifically stated.

Clock

High to Low

High/Low to High

Bus Change

Bus Valid

Undefined/Invalid

Valid Bus to Tristate

Bus/Signal Omission

Figure 1. Timing Diagram Drawing Key

Timing Conditions

Unless specified otherwise, the following conditions are true for all timing measurements.

• TA = 0 to 70° C

• CVDD = VDD_PLL = 1.8V

• RVDD = 3.3 V

• All grounds = 0 V

• Logic 0 = 0 V, Logic 1 = 3.3 V

• Output loading = 50 pF

• Timing reference levels = 1.5 V

• The Processor Bus Clock (HCLK) is programmable and is set by the user. The frequency is typically between

33 MHz and 100 MHz (92 MHz for industrial conditions).

14

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Memory Interface

Figure 2 through Figure 5 define the timings associated with all phases of the SDRAM. The following table contains the

values for the timings of each of the SDRAM modes.

Parameter

Symbol

Min

Typ

Max

Unit

SDCLK high time

tclk_high

-

(tHCLK) / 2

-

ns

SDCLK low time

tclk_low

-

(tHCLK) / 2

-

ns

tclkrf

-

2

4

ns

SDCLK rise/fall time

Signal delay from SDCLK rising edge time

td

-

-

8

ns

Signal hold from SDCLK rising edge time

th

1

-

-

ns

DQMn delay from SDCLK rising edge time

tDQd

-

-

8

ns

DQMn hold from SDCLK rising edge time

tDQh

1

-

-

ns

DA valid setup to SDCLK rising edge time

tDAs

2

-

-

ns

DA valid hold from SDCLK rising edge time

tDAh

3

-

-

ns

SDRAM Load Mode Register Cycle

tclk_low

tclkrf

tclk_high

SDCLK

td

th

SDCSn

RASn

CASn

SDWEn

DQMn

AD

OP-Code

DA

Figure 2. SDRAM Load Mode Register Cycle Timing Measurement

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

15

�EP9312

Universal Platform SOC Processor

SDRAM Burst Read Cycle

tclk_low

tclk_high

SDCLK

tclkrf

td

th

SDCSn

RASn

CASn

SDWEn

tDQh

tDQd

DQMn

CL = 2

tDQh

DQMn

CL = 3

AD

td

tDAs

DA

tDAh

n

n+1

n+2

n+3

CL = 2

tDAs

DA

CL = 3

tDAh

n

n+1

n+2

n+3

Figure 3. SDRAM Burst Read Cycle Timing Measurement

16

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

SDRAM Burst Write Cycle

tclk_high

tclk_low

SDCLK

tclkrf

td

th

th

SDCSn

RASn

CASn

SDWEn

DQMn

AD

DA

n

n +1

n+2

n+3

Figure 4. SDRAM Burst Write Cycle Timing Measurement

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

17

�EP9312

Universal Platform SOC Processor

SDRAM Auto Refresh Cycle

tclk_high

tclk_low

SDCLK

tclkrf

td

SDCSn

th

7

b

d

e

RASn

CASn

SDWEn

Note:

Chip select shown as bus to illustrate multiple devices being put into auto refresh in one access

Figure 5. SDRAM Auto Refresh Cycle Timing Measurement

18

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Static Memory Single Word Read Cycle

Parameter

Symbol

Min

Typ

Max

Unit

AD setup to CSn assert time

tADs

0

-

-

ns

AD hold from CSn deassert time

tADh

tHCLK

-

-

ns

RDn assert time

tRDpw

-

tHCLK × (WST1 + 2)

-

ns

CSn to RDn delay time

tRDd

-

-

3

ns

tDQMd

-

-

1

ns

DA setup to RDn deassert time

tDAs

tHCLK + 12

-

-

ns

DA hold from RDn deassert time

tDAh

0

-

-

ns

CSn assert to DQMn assert delay time

See “Timing Conditions” on page 14 for definition of HCLK.

tADs

tADh

AD

CSn

WRn

tRDd

tRDd

RDn

DQMn

tDQMd

tDAs

tDAh

DA

WAIT

Figure 6. Static Memory Single Word Read Cycle Timing Measurement

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

19

�EP9312

Universal Platform SOC Processor

Static Memory Single Word Write Cycle

Parameter

Symbol

Min

Typ

Max

Unit

AD setup to WRn assert time

tADs

tHCLK

-3

-

-

ns

AD hold from WRn deassert time

tADh

tHCLK × 2

-

-

ns

WRn deassert to CSn deassert time

tCSh

7

-

-

ns

CSn to WRn assert delay time

tWRd

-

-

2

ns

WRn assert time

tWRpw

-

tHCLK × (WST1 + 1)

-

ns

CSn to DQMn assert delay time

tDQMd

-

-

1

ns

WRn deassert to DA transition time

tDAh

tHCLK

-

-

ns

WRn assert to DA valid

tDAV

-

-

8

ns

tADs

tADh

AD

tCSh

CSn

tWRd

tWRpw

WRn

RDn

DQMn

tDQMd

tDAV

tDAh

DA

WAIT

Figure 7. Static Memory Single Word Write Cycle Timing Measurement

20

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Static Memory 32-bit Read on 8-bit External Bus

Parameter

Symbol

Min

Typ

Max

Unit

AD setup to CSn assert time

tADs

tHCLK

-

-

ns

CSn assert to Address transition time

tAD1

-

tHCLK × (WST1 + 1)

-

ns

Address assert time

tAD2

-

tHCLK × (WST1 + 1)

-

ns

AD transition to CSn deassert time

tAD3

-

tHCLK × (WST1 + 2)

-

ns

tADh

-

ns

tHCLK

-

tRDpwL

-

tHCLK × (4 × WST1 + 5)

-

ns

tRDd

-

-

3

ns

CSn assert to DQMn assert delay time

tDQMd

-

-

1

ns

DA setup to AD transition time

tDAs1

15

-

-

ns

DA setup to RDn deassert time

tDAs2

tHCLK + 12

-

-

ns

DA hold from AD transition time

tDAh1

0

-

-

ns

DA hold from RDn deassert time

tDAh2

0

-

-

ns

AD hold from CSn deassert time

RDn assert time

CSn to RDn delay time

tADs

tAD1

tAD2

tAD2

tADh

tAD3

AD

CSn

WRn

tRDd

tRDd

RDn

tDQMd

DQMn

tDAh1

tDAh1

tDAh11

tDAh2

DA

tDAs1

tDAs1

tDAs1

tDAs2

WAIT

Figure 8. Static Memory Multiple Word Read 8-bit Cycle Timing Measurement

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

21

�EP9312

Universal Platform SOC Processor

Static Memory 32-bit Write on 8-bit External Bus

Parameter

Symbol

Min

Typ

Max

Unit

AD setup to WRn assert time

tADs

tHCLK − 3

-

-

ns

WRn/DQMn deassert to AD transition time

tADd

-

-

tHCLK + 6

ns

AD hold from WRn deassert time

tADh

tHCLK × 2

-

-

ns

CSn hold from WRn deassert time

tCSh

7

-

-

ns

tWRd

2

ns

CSn to WRn assert delay time

-

-

WRn assert time

tWRpwL

-

tHCLK × (WST1 + 1)

-

ns

WRn deassert time

tWRpwH

-

tHCLK × 2

(tHCLK × 2) + 14

ns

tDQMd

-

-

1

ns

DQMn assert time

tDQMpwL

-

tHCLK × (WST1 + 1)

-

ns

DQMn deassert time

tDQMpwH

-

-

(tHCLK × 2) + 7

ns

WRn / DQMn deassert to DA transition time

tDAh

tHCLK

-

-

ns

WRn / DQMn assert to DA valid time

tDAV

-

-

8

ns

CSn to DQMn assert delay time

tADs

tADd

tADd

tADd

tADh

AD

CSn

tWRd

tWRpwL

tWRpwL

tCSh

tWRpwL

WRn

tWRpwH

tWRpwH

tWRpwH

RDn

tDQMd

tDQMpwL

tDQMpwL

tDQMpwL

DQMn

tDQMpwH

tDAV

tDQMpwH

tDAV

tDQMpwH

tDAV

tDAV

DA

tDAh

tDAh

tDAh

tDAh

WAIT

Figure 9. Static Memory Multiple Word Write 8-bit Cycle Timing Measurement

22

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Static Memory 32-bit Read on 16-bit External Bus

Parameter

Symbol

Min

Typ

Max

Unit

AD setup to CSn assert time

tADs

tHCLK

-

-

ns

CSn assert to AD transition time

tADd1

-

tHCLK × (WST1 + 1)

-

ns

AD transition to CSn deassert time

tADd2

-

tHCLK × (WST1 + 2)

-

ns

AD hold from CSn deassert time

tADh

tHCLK

-

-

ns

tRDpwL

-

tHCLK × ((2 × WST1) + 3)

-

ns

tRDd

-

-

3

ns

CSn assert to DQMn assert delay time

tDQMd

-

-

1

ns

DA setup to AD transition time

tDAs1

15

-

-

ns

DA to RDn deassert time

tDAs2

tHCLK + 12

-

-

ns

DA hold from AD transition time

tDAh1

0

-

-

ns

DA hold from RDn deassert time

tDAh2

0

-

-

ns

RDn assert time

CSn to RDn delay time

tADs

tADd1

tADd2

tADh

AD

CSn

WRn

tRDd

tRDh

tRDpwl

RDn

DQMn

tDQMh

tDQMd

tDAs1

tDAh1

tDAs2

tDAh2

DA

WAIT

Figure 10. Static Memory Multiple Word Read 16-bit Cycle Timing Measurement

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

23

�EP9312

Universal Platform SOC Processor

Static Memory 32-bit Write on 16-bit External Bus

Parameter

Symbol

Min

Typ

Max

Unit

AD setup to WRn assert time

tADs

tHCLK – 3

-

-

ns

WRn/DQMn deassert to AD transition time

tADd

-

-

tHCLK + 6

ns

AD hold from WRn deassert time

tADh

tHCLK × 2

-

-

ns

CSn hold from WRn deassert time

tCSh

7

-

-

ns

tWRd

CSn to WRn assert delay time

-

-

2

ns

WRn assert time

tWRpwL

-

tHCLK × (WST1 + 1)

-

ns

WRn deassert time

tWRpwH

-

-

(tHCLK × 2) + 14

ns

tDQMd

-

-

1

ns

DQMn assert time

tDQMpwL

-

tHCLK × (WST1 + 1)

-

ns

DQMn deassert time

tDQMpwH

-

-

(tHCLK × 2) + 7

ns

WRn / DQMn deassert to DA transition time

tDAh1

tHCLK

-

-

ns

WRn / DQMn assert to DA valid time

tDAV

-

-

8

ns

CSn to DQMn assert delay time

tADs

tADd

tADh

AD

CSn

tWRd

tWRpwL

WRn

tWRpwL

tCSh

tWRpwH

RDn

tDQMd

tDQpwL

DQMn

tDQpwL

tDQpwH

tDAV

tDAh

tDAV

tDAh

DA

WAIT

Figure 11. Static Memory Multiple Word Write 16-bit Cycle Timing Measurement

24

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Static Memory Burst Read Cycle

Parameter

Symbol

Min

Typ

Max

Unit

CSn assert to Address 1 transition time

tADd1

-

tHCLK × (WST1 + 1)

-

ns

Address assert time

tADd2

-

tHCLK × (WST2 + 1)

-

ns

AD transition to CSn deassert time

tADd3

-

tHCLK × (WST1 + 2)

-

ns

AD hold from CSn deassert time

tADh

tHCLK

-

-

ns

tRDd

-

-

3

ns

CSn to RDn delay time

CSn to DQMn assert delay time

tDQMd

-

-

1

ns

DA setup to AD transition time

tDAs1

15

-

-

ns

DA setup to CSn deassert time

tDAs2

tHCLK + 12

-

-

ns

DA hold from AD transition time

tDAh1

0

-

-

ns

DA hold from RDn deassert time

tDAh2

0

-

-

ns

Note:

These characteristics are valid when the Page Mode Enable (Burst Mode) bit is set. See the User's Guide for details.

tADs

tADd1

tADd2

tADd2

tADh

tADd3

AD

CSn

WRn

tRDd

RDn

DQMn

tDQMd

tDAh1

tDAh1

tDAh1

tDAh2

DA

tDAs1

tDAs1

tDAs1

tDAs2

WAIT

Figure 12. Static Memory Burst Read Cycle Timing Measurement

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

25

�EP9312

Universal Platform SOC Processor

Static Memory Burst Write Cycle

Parameter

Symbol

Min

AD setup to WRn assert time

tADs

tHCLK − 3

ns

AD hold from WRn deassert time

tADh

tHCLK × 2

ns

WRN/DQMn deassert to AD transition time

tADd

CSn hold from WRn deassert time

tCSh

CSn to WRn assert delay time

tWRd

CSn to DQMn assert delay time

tDQMd

DQMn assert time

tDQpwL

DQMn deassert time

tDQpwH

WRn assert time

tWRpwL

WRn deassert time

tWRpwH

WRn/DQMn deassert to DA transition time

tDAh

WRn/DQMn assert to DA valid time

tDAv

Note:

Typ

Max

Unit

tHCLK + 6

ns

7

ns

2

ns

1

ns

tHCLK × (WST1 + 1)

ns

(tHCLK × 2) + 14

ns

tHCLK × (WST1 + 11)

ns

(tHCLK × 2) + 7

ns

tHCLK

ns

8

ns

These characteristics are valid when the Page Mode Enable (Burst Mode) bit is set. See the User's Guide for details.

tADs

tADd

tADh

AD

CSn

tWRpwL

WRn

tCSh

tWRpwH

tWRd

RD

tDQMd

tDQpwL

DQMn

tDQpwH

tDAv

tDAh

DA

WAIT

Figure 13. Static Memory Burst Write Cycle Timing Measurement

26

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Static Memory Single Read Wait Cycle

Parameter

Symbol

Min

Typ

Max

Unit

CSn assert to WAIT time

tWAITd

-

-

tHCLK × (WST1-2)

ns

WAIT assert time

tWAITpw

tHCLK × 2

-

tHCLK × 510

ns

tCSnd

tHCLK × 3

-

tHCLK × 5

ns

WAIT to CSn deassert delay time

AD

CSn

WRn

RDn

DQMn

DA

WAIT

tWAITd

tWAITpw

tCSnd

Figure 14. Static Memory Single Read Wait Cycle Timing Measurement

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

27

�EP9312

Universal Platform SOC Processor

Static Memory Single Write Wait Cycle

Parameter

Symbol

Min

Typ

Max

Unit

tWRd

tHCLK × 2

-

tHCLK × 4

ns

CSn assert to WAIT time

tWAITd

-

-

tHCLK × (WST1-2)

ns

WAIT assert time

tWAITpw

tHCLK × 2

-

tHCLK × 510

ns

tCSnd

tHCLK × 3

-

tHCLK × 5

ns

WAIT to WRn deassert delay time

WAIT to CSn deassert delay time

AD

CSn

tWRd

WRn

RDn

DQMn

DA

tWAITd

tWAITpw

tCSnd

WAIT

Figure 15. Static Memory Single Write Wait Cycle Timing Measurement

28

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

Static Memory Turnaround Cycle

Parameter

CSnX deassert to CSnY assert time

Symbol

Min

Typ

Max

Unit

tBTcyc

-

tHCLK × (IDCY+1)

-

ns

Notes: 1. X and Y represent any two chip select numbers.

2. IDCY occurs on read-to-write and write-to-read.

3. IDCY is honored when going from a asynchronous device (CSx) to a synchronous device (/SDCSy).

tBTcyc

AD

CSnX

CSnY

WRn

RDn

DQMn

DA

WAIT

Figure 16. Static Memory Turnaround Cycle Timing Measurement

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

29

�EP9312

Universal Platform SOC Processor

IDE Interface

Register Transfers

Parameter

Symbol

Mode 0 Mode 1 Mode 2 Mode 3 Mode 4

(in ns) (in ns) (in ns) (in ns) (in ns)

Cycle time

(min)

(Notes 1, 4, 5)

t0

600

383

330

180

120

Address valid to DIORn / DIOWn setup

(min)

(Note 4)

t1

70

50

30

30

25

DIORn / DIOWn pulse width 8-bit

(min)

(Note 1, 4)

t2

290

290

290

80

70

DIORn / DIOWn recovery time

(min)

(Note 1, 4)

t2i

-

-

-

70

25

DIOWn data setup

(min)

(Note 4)

t3

60

45

30

30

20

DIOWn data hold

(min)

t4

0

0

0

0

0

DIORn data setup

(min)

t5

20

20

20

20

20

DIORn data hold

(min)

t6

0

0

0

0

0

DIORn data high impedance state

(max)

(Note 2, 4)

t6z

30

30

30

30

30

DIORn / DIOWn to address valid hold

(min)

(Note 4)

t9

20

15

10

10

10

Read Data Valid to IORDY

active (if IORDY initially low after tA)

(min)

(Note 4)

tRD

0

0

0

0

0

(Note 3, 4)

tA

35

35

35

35

35

(Note 4)

tB

1250

1250

1250

1250

1250

IORDY Setup time

IORDY Pulse Width

(max)

IORDY assertion to release

(max)

tC

5

5

5

5

5

(max)

tDDV

10

10

10

10

10

DIOWn assert to data valid

Note:

1. t0 is the minimum total cycle time, t2 is the minimum DIORn / DIOWn assertion time, and t2i is the minimum DIORn / DIOWn

negation time. A host implementation shall lengthen t2 and/or t2i to ensure that t0 is equal to or greater than the value

reported in the devices IDENTIFY DEVICE data. A device implementation shall support any legal host implementation.

2. This parameter specifies the time from the negation edge of DIORn to the time that the data bus is released by the device.

3. The delay from the activation of DIORn or DIOWn until the state of IORDY is first sampled. If IORDY is inactive then the host

shall wait until IORDY is active before the register transfer cycle is completed. If the device is not driving IORDY negated at

the tA after the activation of DIORn or DIOWn, then t5 shall be met and tRD is not applicable. If the device is driving IORDY

negated at the time tA after the activation of DIORn or DIOWn, then tRD shall be met and t5 is not applicable.

4. Timings based upon software control. See User’s Guide.

5. ATA / ATAPI standards prior to ATA / ATAPI-5 inadvertently specified an incorrect value for mode 2 time t0 by utilizing the

16-bit PIO value.

6. All IDE timing is based upon HCLK = 100 MHz.

30

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

ADDR valid

(Note 1)

t9

t1

t2

t2i

DIORn/

DIOWn

t0

tDDV

WRITE

DD(15:0)

(Note 2)

t3

t4

READ

DD(15:0)

(Note 2)

t5

t6

t6z

IORDY

(Note 3,3-1)

tA

IORDY

(Note 3,3-2)

tC

tRD

IORDY

(Note 3,3-3)

tB

Note:

tC

1. Device address consists of signals IDECS0n, IDECS1n and IDEDA (2:0)

2. Data consists of DD (7:0)

3. The negation of IORDY by the device is used to extend the register transfer cycle. The determination of whether the cycle is

to be extended is made by the host after tA from the assertion of DIORn or DIOWn. The assertion and negation or IORDY

are described in the following three cases:

3-1 Device never negates IORDY, devices keeps IORDY released: no wait is generated.

3-2 Device negates IORDY before tA, but causes IORDY to be asserted before tA. IORDY is released prior to negation

and may be asserted for no more than tC before release: no wait generated.

3-3 Device negates IORDY before tA. IORDY is released prior to negation and may be asserted for no more than tC

before release: wait generated. The cycle completes after IORDY is reasserted. For cycles where a wait is generated

and DIORn is asserted, the device shall place read data on DD (7:0) for tRD before asserting IORDY.

Figure 17. Register Transfer to/from Device

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

31

�EP9312

Universal Platform SOC Processor

PIO Data Transfers

Parameter

Symbol

Mode 0 Mode 1 Mode 2 Mode 3 Mode 4

(in ns)

(in ns)

(in ns)

(in ns)

(in ns)

Cycle time

(min)

(Note 1, 4)

t0

600

383

240

180

120

Address valid to DIORn / DIOWn setup

(min)

(Note 4)

t1

70

50

30

30

25

DIORn / DIOWn 16-bit

(min)

(Note 1, 4)

t2

165

125

100

80

70

DIORn / DIOWn recovery time

(min)

(Note 1, 4)

t2i

-

-

-

70

25

DIOWn data setup

(min)

(Note 4)

t3

60

45

30

30

20

DIOWn data hold

(min)

t4

0

0

0

0

0

DIORn data setup

(min)

t5

20

20

20

20

20

DIORn data hold

(min)

t6

0

0

0

0

0

DIORn data high impedance state

(max)

(Note 2, 4)

t6z

30

30

30

30

30

DIORn / DIOWn to address valid hold

(min)

(Note 4)

t9

20

15

10

10

10

Read Data Valid to IORDY

active (if IORDY initially low after tA)

(min)

(Note 4)

tRD

0

0

0

0

0

(Note 3, 4)

tA

35

35

35

35

35

(Note 4)

tB

1250

1250

1250

1250

1250

IORDY Setup time

IORDY Pulse Width

(max)

IORDY assertion to release

(max)

tC

5

5

5

5

5

(max)

tDDV

10

10

10

10

10

DIOWn assert to data valid

Note:

32

1. t0 is the minimum total cycle time, t2 is the minimum DIORn / DIOWn assertion time, and t2i is the minimum DIORn / DIOWn

negation time. A host implementation shall lengthen t2 and/or t2i to ensure that t0 is equal to or greater than the value

reported in the devices IDENTIFY DEVICE data. A device implementation shall support any legal host implementation.

2. This parameter specifies the time from the negation edge of DIORn to the time that the data bus is released by the device.

3. The delay from the activation of DIORn or DIOWn until the state of IORDY is first sampled. If IORDY is inactive then the host

shall wait until IORDY is active before the register transfer cycle is completed. If the device is not driving IORDY negated at

the tA after the activation of DIORn or DIOWn, then t5 shall be met and tRD is not applicable. If the device is driving IORDY

negated at the time tA after the activation of DIORn or DIOWn, then tRD shall be met and t5 is not applicable.

4. Timings based upon software control. See User’s Guide.

5. All IDE timing is based upon HCLK = 100 MHz.

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

ADDR valid

(Note 1)

t9

t1

t2

t2i

DIORn/

DIOWn

t0

tDDV

WRITE

DD(15:0)

(Note 2)

t3

t4

READ

DD(15:0)

(Note 2)

t5

t6

t6z

IORDY

(Note 3,3-1)

tA

IORDY

(Note 3,3-2)

tC

tRD

IORDY

(Note 3,3-3)

tB

Note:

tC

1. Device address consists of signals IDECS0n, IDECS1n and IDEDA (2:0)

2. Data consists of DD (15:0)

3. The negation of IORDY by the device is used to extend the register transfer cycle. The determination of whether the cycle is

to be extended is made by the host after tA from the assertion of DIORn or DIOWn. The assertion and negation or IORDY

are described in the following three cases:

3-1 Device never negates IORDY, devices keeps IORDY released: no wait is generated.

3-2 Device negates IORDY before tA, but causes IORDY to be asserted before tA. IORDY is released prior to negation

and may be asserted for no more than tC before release: no wait generated.

3-3 Device negates IORDY before tA. IORDY is released prior to negation and may be asserted for no more than tC

before release: wait generated. The cycle completes after IORDY is reasserted. For cycles where a wait is generated

and DIORn is asserted, the device shall place read data on DD (15:0) for tRD before asserting IORDY.

Figure 18. PIO Data Transfer to/from Device

DS515F2

Copyright 2010 Cirrus Logic (All Rights Reserved)

33

�EP9312

Universal Platform SOC Processor

Ultra DMA Data Transfer

Figure 19 through Figure 28 define the timings associated with all phases of Ultra DMA bursts. The following table

contains the values for the timings for each of the Ultra DMA modes.

Timing reference levels = 1.5 V

Parameter

Symbol

Mode 0

(in ns)

Mode 1

(in ns)

Mode 2

(in ns)

Mode 3

(in ns)

min

max

min

max

min

max

min

max

tCYCRD

112

-

73

-

54

-

39

-

Two-cycle time allowing for clock variations (from rising edge to next

rising edge or from falling edge to next falling edge of DSTROBE)

t2CYCRD

230

-

154

-

115

-

86

-

Cycle time allowing for asymmetry and clock variations

(from HSTROBE edge to HSTROBE edge)

tCYCWR

230

-

170

-

130

-

100

-

Two-cycle time allowing for clock variations (from rising edge to next

rising edge or from falling edge to next falling edge of HSTROBE)

t2CYCWR

460

-

340

-

260

-

200

-

tDS

15

-

10

-

7

-

7

-

tDH

8

-

8

-

8

-

8

-

tDVS

70

-

48

-

30

-

20

-

tDVH

6

-

6

-

6

-

6

-

tFS

0

230

0

200

0

170

0

130

Cycle time allowing for asymmetry and clock variations

(from DSTROBE edge to DSTROBE edge)

Data setup time at recipient (Read)

Data hold time at recipient (Read)

Data valid setup time at sender (Write)

(from data valid until STROBE edge)

(Note 2)

Data valid hold time at sender (Write)

(from STROBE edge until data may become invalid)

(Note 2)

First STROBE time (for device to first negate DSTROBE from STOP

during a data in burst)

Limited interlock time

(Note 3)

tLI

0

150

0

150

0

150

0

100

Interlock time with minimum

(Note 3)

tMLI

20

-

20

-

20

-

20

-

Unlimited interlock time

(Note 3)

tUI

0

-

0

-

0

-

0

-

tAZ

-

10

-

10

-

10

-

10

Minimum delay time required for output

tZAH

20

-

20

-

20

-

20

-

Drivers to assert or negate (from released)

tZAD

0

-

0

-

0

-

0

-

Envelope time (from DMACKn to STOP and HDMARDYn during data in

burst initiation and from DMACKn to STOP during data out burst initiation)

tENV

20

70

20

70

20

70

20

55

Ready-to-final-STROBE time (no STROBE edges shall be sent this long

after negation of DMARDYn)

tRFS

-

75

-

70

-

60

-

60

Ready-to-pause time

(that recipient shall wait to pause after negating DMARDYn)

tRP

160

-

125

-

100

-

100

-

tIORDYZ

-

20

-

20

-

20

-

20

tZIORDY

0

-

0

-

0

-

0

-

Setup and hold times for DMACKn (before assertion or negation)

tACK

20

-

20

-

20

-

20

-

Time from STROBE edge to negation of DMARQ or assertion of STOP

(when sender terminates a burst)

tSS

50

-

50

-

50

-

50

-

Maximum time allowed for output drivers to release

(from asserted or negated)

Maximum time before releasing IORDY

Minimum time before driving STROBE

Note:

34

(Note 4)

1. Timing parameters shall be measured at the connector of the sender or receiver to which the parameter applies.

2. The test load for tDVS and tDVH shall be a lumped capacitor load with no cable or receivers. Timing for tDVS and tDVH shall be

met for all capacitive loads from 15 to 40 pf where all signals have the same capacitive load value.

3. tUI, tMLI and tLI indicate sender-to-recipient or recipient-to-sender interlocks, i.e., either sender or recipient is waiting for the

other to respond with a signal before proceeding. tUI is an unlimited interlock that has no maximum time value. tMLI is a limited

time-out that has a defined minimum. tLI is a limited time-out that has a defined maximum.

4. tZIORDY may be greater than tENV since the device has a pull up on IORDYn giving it a known state when released.

5. All IDE timing is based upon HCLK = 100 MHz.

Copyright 2010 Cirrus Logic (All Rights Reserved)

DS515F2

�EP9312

Universal Platform SOC Processor

DMARQ

(device)

tUI

DMACKn

(host)

tFS

tACK

tENV

tZAD

tACK

tENV

tZAD

STOP

(host)

HDMARDYn

(host)

tZIORDY

DSTROBE

(device)

tAZ