CY7B952

SST™ SONET/SDH Serial Transceiver

SST™ SONET/SDH Serial Transceiver

Features

■

No output clock “drift” without data transitions

OC-3 Compliant with Bellcore and CCITT (ITU) specifications

on:

❐ Jitter Generation ( 0 °C

VCC 1.03 VCC 0.83

V

VCC 1.86 VCC 1.62

V

0.6

–

V

VCC

V

Three-Level Input Pins (MODE)

VIHH

Three-Level Input HIGH

VCC 0.75

VIMM

Three-Level Input MID

VCC/2 0.5 VCC/2 + 0.5

VILL

Three-Level Input LOW

V

0.0

0.75

V

Operating Current [5]

ICCS

Static Operating Current

–

38

mA

ICCR

Receiver Operating Current

–

50

mA

ICCT

Transmitter Operating Current

–

13

mA

ICCE

ECL Pair Operating Current

–

7.0

mA

ICC5

Additional Current at 51.84 MHz

–

7.0

mA

ICCO

Additional Current LFI = LOW

–

3

mA

Note

5. Total Receiver operating current (assuming that the Transmitter is not activated) can be found by adding ICCS + ICCR + x × ICCE; where x is 2 if the ROUT outputs

are not activated and 3 if they are activated. Total Transmitter operating current (assuming that the Receiver is not activated) can be found by adding ICCS + ICCT +

x × ICCE; where x is 1 if the TOUT outputs are not activated and 2 if they are activated. Total device power (assuming that the Transmitter and the Receiver are

activated) can be found by adding ICCS + ICCR + ICCT + x × ICCE; where x represents the number of ECL output pairs activated.

Document Number: 38-02018 Rev. *E

Page 8 of 16

[+] Feedback

�CY7B952

Capacitance

Parameter [6]

CIN

Description

Test Conditions

TA = 25 C, f0 = 1 MHz, VCC = 5.0 V

Input Capacitance

Max

Unit

10

pF

AC Test Loads and Waveforms

Figure 2. AC Test Loads and Waveforms

5V

R1

OUTPUT

R1=910

R2=510

CL < 30 pF

(Includes fixture and

probe capacitance)

VCC – 2

CL

CL

R2

(a) TTL AC Test Load

[7]

3.0V

3.0V

GND

RL

2.0V

(b) ECL AC Test Load

VIHE

2.0V

1.0V

< 1 ns

1.0V

< 1 ns

(c) TTL Input Test Waveform

VILE

[7]

VIHE

80%

80%

20%

20%

< 1 ns

RL =50

CL < 5 pF

(Includes fixture and

probe capacitance)

VILE

< 1 ns

(d) ECL Input Test Waveform

Notes

6. Tested initially and after any design or process changes that may affect these parameters.

7. Cypress uses constant current (ATE) load configurations and forcing functions. This figure is for reference only.

Document Number: 38-02018 Rev. *E

Page 9 of 16

[+] Feedback

�CY7B952

Switching Characteristics

Over the Operating Range

Parameter

fREF

fB

Description

Reference Frequency

Bit Time

[8]

Min

Max

Unit

MODE = LOW

6.41

6.55

MHz

MODE = HIGH

19.24

19.64

MHz

MODE = LOW

19.5

19.1

ns

MODE = HIGH

6.50

6.40

ns

tODC

Output Duty Cycle (TCLK, RCLK) [9]

48

52

%

tRF

Output Rise/Fall Time [9]

0.4

1.2

ns

tLOCK

PLL Lock Time (RIN transition density 25%) [10]

–

3

ms

tRPWH

REFCLK Pulse Width HIGH

10

–

ns

tRPWL

REFCLK Pulse Width LOW

10

–

ns

tDV

Data Valid

3

–

ns

tDH

Data Hold

1

–

ns

tPD

Propagation Delay (RIN to ROUT, TSER to TOUT) [11]

–

10

ns

Jitter

Generation

Jitter Generation of RX PLL

–

0.01

f3dB

3 dB Gain Bandwidth of RX PLL (Jitter Transfer

Bandwidth)

At 155 MHz

–

130

kHz

f3dB

3 dB Gain Bandwidth of RX PLL (Jitter Transfer

Bandwidth)

At 52 MHz

–

40

kHz

Gpeak

Maximum Peaking of RX PLL[12]

–

0.1

dB

UIrms

Notes

8. fB is calculated a 1/(fREF8).

9. Tested initially and after any design or process changes that may affect these parameters.

10. tLOCK is the time needed for transitioning from lock to REFCLK × 8 to lock to data.

11. The ECL switching threshold is the differential zero crossing (i.e., the place where + and – signals cross).

12. Maximum Peaking is measured using a maximum of 1.2 ns peak to peak duty cycle distortion for RINand applying sinusoidal jitter to the input signal at the maximum

amplitude of the jitter tolerance mask for each specific jitter frequency as specified by the Bellcore GR-253-Core issue 2, Dec 1995 - SONET Common Generic

Criteria for OC-3.

Document Number: 38-02018 Rev. *E

Page 10 of 16

[+] Feedback

�CY7B952

Switching Waveforms for the CY7B952 SONET/SDH Serial Transceiver

tRPWH

tRPWL

REFCLK

TSER

(RIN)

tPD

TOUT

(ROUT)

tODC

tODC

RCLK+

tDH

tDV

RSER

tB/2 tPE

tB/2 tPE

RIN

Document Number: 38-02018 Rev. *E

Page 11 of 16

[+] Feedback

�CY7B952

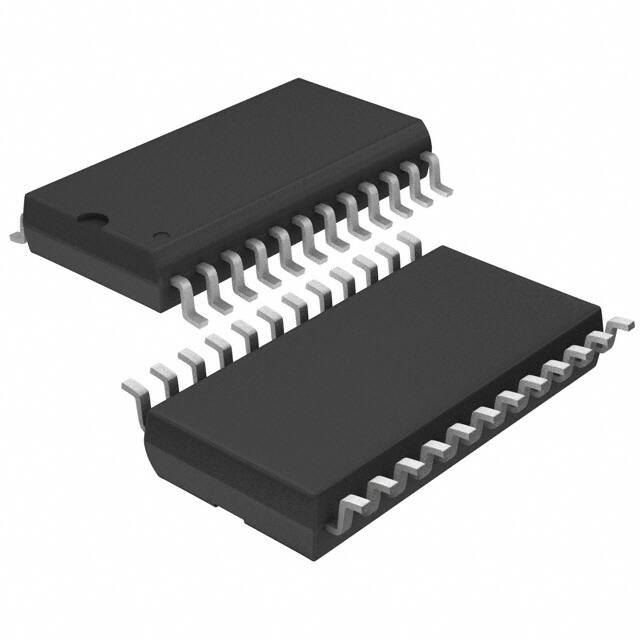

Ordering Information

Speed

(ns)

25

Package

Name

Ordering Code

Package Type

Operating

Range

CY7B952-SXC

S13

24-pin (300-Mil) Molded SOIC

Commercial

CY7B952-SXCT

S13

24-pin (300-Mil) Molded SOIC

Commercial

Ordering Code Definitions

CY 7B

952 -

S X C

X

X = blank or T

blank = Tube; T = Tape and Reel

Temperature Range: C = Commercial

Pb-free

Package Type: S = 24-pin SOIC

Base part number: 952 = Serial Transceiver

Marketing Code: 7B = HOTLink Transceiver/Receiver

Company ID: CY = Cypress

Document Number: 38-02018 Rev. *E

Page 12 of 16

[+] Feedback

�CY7B952

Package Diagram

Figure 3. 24-pin SOIC (0.615 × 0.300 × 0.0932 Inches) Package Outline, 51-85025

51-85025 *E

Document Number: 38-02018 Rev. *E

Page 13 of 16

[+] Feedback

�CY7B952

Acronyms

Acronym

Document Conventions

Description

AC

alternating current

CD

carrier detect

DC

direct current

ECL

emitter coupled logic

I/O

input/output

LFI

link fault indicator

PCB

printed circuit board

PECL

Units of Measure

Symbol

Unit of Measure

dB

decibel

°C

degree Celsius

kHz

kilohertz

MHz

megahertz

µA

microampere

positive emitter coupled logic

µF

microfarad

PLL

phase locked loop

mA

milliampere

SOIC

small-outline integrated circuit

mV

millivolt

TTL

transistor-transistor logic

ns

nanosecond

VCO

voltage controlled oscillator

ohm

%

percent

pF

picofarad

ppm

parts per million

V

volt

Document Number: 38-02018 Rev. *E

Page 14 of 16

[+] Feedback

�CY7B952

Document History Page

Document Title: CY7B952, SST™ SONET/SDH Serial Transceiver

Document Number: 38-02018

Rev.

ECN.

Issue Date

Orig. of

Change

**

105981

03/28/01

SZV

Change from Spec. number: 38-00502 to 38-02018

*A

122206

12/28/02

RBI

Add power up requirements to maximum ratings information.

Description of Change

*B

283371

See ECN

BCD

Removed Preliminary from the data sheet

*C

2896206

03/19/10

CGX

Removed obsolete part and added the following parts: CY7B952-SXC and

CY7B952-SXCT

Updated package diagram

*D

3092301

11/22/10

SAAC

Ordering Information update.

Added Ordering Code Definitions.

*E

3434099

11/09/2011

SAAC

Updated Package Diagram.

Added Acronyms and Units of Measure.

Updated in new template.

Document Number: 38-02018 Rev. *E

Page 15 of 16

[+] Feedback

�CY7B952

Sales, Solutions, and Legal Information

Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer’s representatives, and distributors. To find the office

closest to you, visit us at Cypress Locations.

Products

Automotive

Clocks & Buffers

Interface

Lighting & Power Control

PSoC Solutions

cypress.com/go/automotive

psoc.cypress.com/solutions

cypress.com/go/clocks

PSoC 1 | PSoC 3 | PSoC 5

cypress.com/go/interface

cypress.com/go/powerpsoc

cypress.com/go/plc

Memory

Optical & Image Sensing

cypress.com/go/memory

cypress.com/go/image

PSoC

cypress.com/go/psoc

Touch Sensing

cypress.com/go/touch

USB Controllers

Wireless/RF

cypress.com/go/USB

cypress.com/go/wireless

© Cypress Semiconductor Corporation, 2001-2011. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of

any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for

medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as

critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems

application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign),

United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of,

and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress

integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without

the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not

assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where

a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress’ product in a life-support systems application implies that the manufacturer

assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 38-02018 Rev. *E

Revised November 9, 2011

Page 16 of 16

SUNI is a trademark of PMC-Sierra, Incorporated. SST is a trademark of Cypress Semiconductor Corporation. All products and company names mentioned in this document may be the trademarks

of their respective holders.

[+] Feedback

�

很抱歉,暂时无法提供与“CY7B952-SXCT”相匹配的价格&库存,您可以联系我们找货

免费人工找货