CY7C1308DV25C-167BZCT 数据手册

PRELIMINARY

CY7C1308DV25C

9 Mbit DDR I SRAM 4-Word

Burst Architecture

Functional Description

Features

■

9 Mbit Density (256 Kbit x 36)

■

250 MHz Clock for High Bandwidth

■

4-Word Burst to Reduce Address Bus Frequency

■

Double Data Rate (DDR) Interfaces

(data transferred at 500 MHz at 250 MHz)

■

Two Input Clocks (K and K) for Precise DDR Timing—SRAM

uses rising edges only

■

Two Input Clocks (C and C) Account for Clock Skew and Flight

Time Mismatching

■

Separate Port Selects for Depth Expansion

■

Synchronous Internally Self-timed Writes

■

2.5V Core Power Supply with HSTL Inputs and Outputs

■

Variable Drive HSTL Output Buffers

■

Expanded HSTL Output Voltage (1.4V to 1.9V)

■

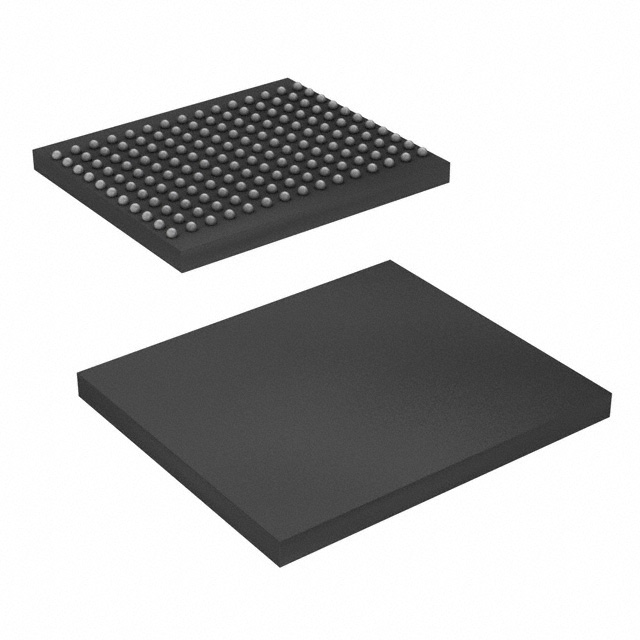

13 x 15 x 1.4 mm 1.0 mm pitch fBGA package, 165 ball (11 x

15 matrix)

■

JTAG 1149.1 Compatible Test Access Port

Configuration

The CY7C1308DV25C is a 2.5V Synchronous Pipelined SRAM

equipped with DDR I (Double Data Rate) architecture. The

DDR I architecture consists of an SRAM core with advanced

synchronous peripheral circuitry and a 2-bit burst counter.

Addresses for Read and Write are latched on alternate rising

edges of the input (K) clock. Write data is registered on the rising

edges of both K and K. Read data is driven on the rising edges

of C and C if provided, or on the rising edge of K and K if C/C are

not provided. Every Read or Write operation is associated with

four words that burst sequentially into or out of the device. The

burst counter takes in the least two significant bits of the external

address and bursts four 36-bit words. Depth expansion is

accomplished with Port Selects for each port. Port Selects allow

each port to operate independently.

Asynchronous inputs include impedance match (ZQ).

Synchronous data outputs (Q, sharing the same physical pins as

the data inputs D) are tightly matched to the two output echo

clocks CQ/CQ, eliminating the need for separately capturing

data from each individual DDR SRAM in the system design.

Output data clocks (C/C) are also provided for maximum system

clocking and data synchronization flexibility.

All synchronous inputs pass through input registers controlled by

the K or K input clocks. All data outputs pass through output

registers controlled by the C or C input clocks. Writes are

conducted with on-chip synchronous self timed write circuitry.

CY7C1308DV25C – 256K x 36

Logic Block Diagram

Burst

Logic

16

18

Write

Reg

Address

A(17:2) Register

Write Add. Decode

A(17:0)

LD

K

K

CLK

Gen.

Write

Reg

Write

Reg

Write

Reg

Read Add. Decode

A(1:0)

256K x 36 Array

36

Output

Logic

Control

C

C

Read Data Reg.

144

Vref

R/W

CQ

72

Reg.

Control

Logic

72

Reg.

36

Reg.

36

Cypress Semiconductor Corporation

Document #: 001-04310 Rev. *A

•

198 Champion Court

CQ

•

DQ[35:0]

San Jose, CA 95134-1709

•

408-943-2600

Revised August 04, 2009

[+] Feedback

�CY7C1308DV25C

PRELIMINARY

Selection Guide

Parameter

250 MHz

200 MHz

167 MHz

Unit

Maximum Operating Frequency

250

200

167

MHz

Maximum Operating Current

850

700

600

mA

Shaded areas contain advance information.

Pin Configuration

CY7C1308DV25C (256K × 36) – 11 × 15 FBGA

1

A

B

C

D

E

F

G

H

J

K

L

M

N

P

CQ

R

2

3

GND/144M NC/36M

4

5

6

7

8

R/W

NC

K

NC

LD

9

10

NC/18M GND/72M

11

CQ

NC

DQ27

DQ18

A

NC

K

NC

A

NC

NC

DQ8

NC

NC

NC

DQ29

DQ28

DQ19

VSS

VSS

A

VSS

A0

VSS

A1

VSS

VSS

VSS

NC

NC

DQ17

NC

DQ7

DQ16

NC

NC

DQ20

VDDQ

VSS

VSS

VSS

VDDQ

NC

DQ15

DQ6

NC

NC

NC

NC

DQ30

DQ21

VDDQ

VDD

VSS

VDD

VDDQ

NC

DQ31

VREF

NC

DQ22

VDDQ

DQ32

VDDQ

VDDQ

VDDQ

VDD

VDD

VDD

VSS

VSS

VSS

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

NC

NC

VDDQ

NC

NC

VREF

DQ13

DQ5

DQ14

ZQ

DQ4

NC

NC

DQ23

VDDQ

VDD

VSS

VDD

VDDQ

NC

DQ12

DQ3

NC

DQ33

DQ24

VDDQ

VSS

VSS

VSS

VDDQ

NC

NC

DQ2

NC

NC

NC

DQ35

DQ34

DQ25

VSS

VSS

VSS

A

VSS

A

VSS

A

VSS

VSS

NC

NC

DQ11

NC

DQ1

DQ10

NC

NC

DQ26

A

A

C

A

A

NC

DQ9

DQ0

TDO

TCK

A

A

A

C

A

A

A

TMS

TDI

Pin Definitions

Name

I/O

Description

DQ[35:0]

Input/Output

Synchronous

Data Input/Output Signals. Inputs are sampled on the rising edge of K and K clocks

during valid Write operations. These pins drive out the requested data during a Read

operation. Valid data is driven out on the rising edge of both the C and C clocks during

Read operations or K and K when in single clock mode. When Read access is deselected,

Q[35:0] are automatically tristated.

LD

Input

Synchronous

Synchronous Load. This input is brought LOW when a bus cycle sequence is to be

defined. This definition includes address and Read/Write direction. All transactions

operate on a burst of 4 data (two clock periods of bus activity).

A, A0, A1

Input

Synchronous

Address Inputs. These address inputs are multiplexed for both Read and Write operations. A0 and A1 are the inputs to the burst counter. These are incremented in a linear

fashion internally. Eighteen address inputs are needed to access the entire memory

array. All the address inputs are ignored when the part is deselected.

R/W

Input

Synchronous

Synchronous Read/Write Input. When LD is LOW, this input designates the access

type (Read when R/W is HIGH, Write when R/W is LOW) for loaded address. R/W must

meet the setup and hold times around edge of K.

Input Clock

Positive Output Clock Input. C is used in conjunction with C to clock out the Read data

from the device. C and C can be used together to deskew the flight times of various

devices on the board back to the controller. See Figure 1 on page 5 for further details.

C

Document #: 001-04310 Rev. *A

Page 2 of 18

[+] Feedback

�CY7C1308DV25C

PRELIMINARY

Pin Definitions

(continued)

Name

I/O

Description

C

Input Clock

Negative Output Clock Input. C is used in conjunction with C to clock out the Read data

from the device. C and C can be used together to deskew the flight times of various

devices on the board back to the controller. See Figure 1 on page 5 for further details.

K

Input Clock

Positive Input Clock Input. The rising edge of K is used to capture synchronous inputs

to the device and to drive out data through Q[35:0] when in single clock mode. All accesses

are initiated on the rising edge of K.

K

Input Clock

Negative Input Clock Input. K is used to capture synchronous inputs being presented

to the device and to drive out data through Q[35:0] when in single clock mode.

CQ

Echo Clock

CQ is Referenced with Respect to C. This is a free running clock and is synchronized

to the output clock (C) of the DDR I. In the single clock mode, CQ is generated with

respect to K. The timings for the echo clocks are shown in the AC timing table.

CQ

Echo Clock

CQ is Referenced with Respect to C. This is a free running clock and is synchronized

to the output clock (C) of the DDR I. In the single clock mode, CQ is generated with

respect to K. The timings for the echo clocks are shown in the AC timing table.

ZQ

Input

Output Impedance Matching Input. This input is used to tune the device outputs to the

system data bus impedance. CQ, CQ and Q[35:0] output impedance are set to 0.2 x RQ,

where RQ is a resistor connected between ZQ and ground. Alternately, this pin can be

connected directly to VDD, which enables the minimum impedance mode. This pin cannot

be connected directly to GND or left unconnected.

TDO

Output

TCK

Input

TCK pin for JTAG.

TDI

Input

TDI pin for JTAG.

TMS

Input

TMS pin for JTAG.

NC

N/A

Not Connected to the Die. Can be tied to any voltage level.

NC/18M

N/A

Address Expansion for 18M. This is not connected to the die.

NC/36M

N/A

Address Expansion for 36M. This is not connected to the die.

GND/72M

Input

Address Expansion for 72M. This should be tied LOW.

GND/144M

Input

Address Expansion for 144M. This should be tied LOW.

VREF

InputReference

VDD

Power Supply

VSS

Ground

VDDQ

Power Supply

TDO for JTAG.

Reference Voltage Input. Static input used to set the reference level for HSTL inputs

and outputs as well as AC measurement points.

Power supply inputs to the core of the device.

Ground for the device.

Power supply inputs for the outputs of the device.

Introduction

Functional Overview

The CY7C1308DV25C is a synchronous pipelined Burst SRAM

equipped with DDR interface.

Accesses are initiated on the positive input clock (K). All

synchronous input timing is referenced from the rising edge of

the input clocks (K and K) and all output timing is referenced to

the rising edge of output clocks (C and C or K and K when in

single clock mode).

All synchronous data inputs (D[35:0]) pass through input registers

controlled by the input clocks (K and K). All synchronous data

outputs (Q[35:0]) pass through output registers controlled by the

rising edge of the output clocks (C and C or K and K when in

single clock mode).

Document #: 001-04310 Rev. *A

All synchronous control (R/W, LD) inputs pass through input

registers controlled by the rising edge of the input clocks (K and

K).

Read Operations

The CY7C1308DV25C is organized internally as an array of

256K x 36. Accesses are completed in a burst of four sequential

36-bit data words. Read operations are initiated by asserting

R/W HIGH and LD LOW at the rising edge of the Positive Input

Clock (K). The address presented to Address inputs are stored

in the Read address register and the least two significant bits of

the address are presented to the burst counter. The burst

counter increments the address in a linear fashion. Following the

next K clock rise the corresponding 36-bit word of data from this

address location is driven onto the Q[35:0] using C as the output

timing reference. On the subsequent rising edge of C the next

36-bit data word from the address location generated by the

burst counter is driven onto the Q[35:0]. This process continues

Page 3 of 18

[+] Feedback

�PRELIMINARY

until all four 36-bit data words are driven out onto Q[35:0]. The

requested data is valid 3 ns from the rising edge of the output

clock (C or C, 250 MHz device). To maintain the internal logic,

each Read access must be allowed to complete. Each Read

access consists of four 36-bit data words and takes two clock

cycles to complete. Therefore, Read accesses to the device

cannot be initiated on two consecutive K clock rises. The internal

logic of the device ignores the second Read request. Read

accesses can be initiated on every other K clock rise. Doing so

pipelines the data flow such that data is transferred out of the

device on every rising edge of the output clocks (C and C or K

and K when in single clock mode).

When the read port is deselected, the CY7C1308DV25C first

completes the pending read transactions. Synchronous internal

circuitry automatically tristates the outputs following the next

rising edge of the positive output clock (C). This allows for a

seamless transition between devices without the insertion of wait

states in a depth expanded memory.

Write Operations

Write operations are initiated by asserting R/W LOW and LD

LOW at the rising edge of the positive input clock (K). The

address presented to Address inputs are stored in the Write

address register and the least two significant bits of the address

are presented to the burst counter. The burst counter increments

the address in a linear fashion. On the following K clock rise, the

data presented to D[35:0] is latched and stored into the 36-bit

Write Data register. On the subsequent rising edge of the

Negative Input Clock (K) the information presented to D[35:0] is

also stored into the Write Data Register.This process continues

for one more cycle until four 36-bit words (a total of 144 bits) of

data are stored in the SRAM. The 144 bits of data are then written

into the memory array at the specified location. Therefore, Write

accesses to the device can not be initiated on two consecutive

K clock rises. The internal logic of the device ignores the second

Write request. Write accesses can be initiated on every other

rising edge of the positive input clock (K). Doing so pipelines the

data flow such that 36-bits of data can be transferred into the

device on every rising edge of the input clocks (K and K).

When deselected, the Write port ignores all inputs after the

pending Write operations are completed.

Single Clock Mode

The CY7C1308DV25C can be used with a single clock that

controls both the input and output registers. In this mode, the

device recognizes only a single pair of input clocks (K and K) that

control both the input and output registers. This operation is

Document #: 001-04310 Rev. *A

CY7C1308DV25C

identical to the operation if the device had zero skew between

the K/K and C/C clocks. All timing parameters remain the same

in this mode. To use this mode of operation, the user must tie C

and C HIGH at power-on. This function is a strap option and not

alterable during device operation.

DDR Operation

The CY7C1308DV25C enables high performance operation

through high clock frequencies (achieved through pipelining) and

double data rate mode of operation. At slower frequencies, the

CY7C1308DV25C requires a single No Operation (NOP) cycle

when transitioning from a Read to a Write cycle. At higher

frequencies, a second NOP cycle may be required to prevent

bus contention.

If a Read occurs after a Write cycle, address and data for the

Write are stored in registers. The Write information must be

stored because the SRAM can not perform the last word Write

to the array without conflicting with the Read. The data stays in

this register until the next Write cycle occurs. On the first Write

cycle after the Read(s), the stored data from the earlier Write is

written into the SRAM array. This is called a Posted Write.

Depth Expansion

Depth expansion requires replicating the LD control signal for

each bank. All other control signals can be common between

banks as appropriate.

Echo Clocks

Echo clocks are provided on the DDR I to simplify data capture

on high-speed systems. Two echo clocks are generated by the

DDR I. CQ is referenced with respect to C and CQ is referenced

with respect to C. These are free-running clocks and are

synchronized to the output clock of the DDR I. In the single clock

mode, CQ is generated with respect to K and CQ is generated

with respect to K. The timings for the echo clocks are shown in

the AC Timing table.

Programmable Impedance

An external resistor, RQ must be connected between the ZQ pin

on the SRAM and VSS to allow the SRAM to adjust its output

driver impedance. The value of RQ must be 5X the value of the

intended line impedance driven by the SRAM, The allowable

range of RQ to guarantee impedance matching with a tolerance

of ±15% is between 175Ω and 350Ω, with VDDQ=1.5V. The

output impedance is adjusted every 1024 cycles to adjust for

drifts in supply voltage and temperature.

Page 4 of 18

[+] Feedback

�CY7C1308DV25C

PRELIMINARY

Figure 1. Application Example[1]

DQ

A

DQ

Addresses

Cycle Start#

R/W#

Return CLK

Source CLK

Return CLK#

Source CLK#

Echo Clock1/Echo Clock#1

Echo Clock2/Echo Clock#2

BUS

MASTER

(CPU

or

ASIC)

ZQ

CQ/CQ#

LD# R/W# C C# K K#

SRAM#1

R = 250ohms

ZQ

CQ/CQ#

LD# R/W# C C# K K#

SRAM#2

DQ

A

R = 250ohms

Vterm = 0.75V

R = 50ohms

Vterm = 0.75V

Truth Table[2, 3, 4, 5, 6, 7]

Operation

K

LD

R/W

DQ

DQ

Write Cycle:

Load address; wait one cycle; input

write data on 2 consecutive K and

K rising edges.

L-H

L

L[8]

D(A1)at

K(t+1)↑

D(A2) at

K(t+1)↑

D(A3) at

K(t+2) ↑

D(A4) at

K(t+2) ↑

Read Cycle:

Load address; wait one cycle; read

data on 2 consecutive C and C

rising edges.

L-H

L

H[9]

Q(A1) at

C(t+1)↑

Q(A2) at

C(t+1) ↑

Q(A3) at

C(t+2)↑

Q(A4) at

C(t+2) ↑

NOP: No Operation

L-H

H

X

High-Z

High-Z

High-Z)

High-Z

Stopped

X

X

Previous State Previous State Previous State Previous State

Standby: Clock Stopped

DQ

DQ

Linear Burst Address Table

First Address (External)

Second Address (Internal)

Third Address (Internal)

Fourth Address (Internal)

X..X00

X..X01

X..X10

X..X11

X..X01

X..X10

X..X11

X..X00

X..X10

X..X11

X..X00

X..X01

X..X11

X..X00

X..X01

X..X10

Notes

1. The above application shows 2 DDR I being used.

2. X = “Don't Care“, H = Logic HIGH, L = Logic LOW, ↑represents rising edge.

3. Device powers up deselected and the outputs are in a tristate condition.

4. “A1” represents address location latched by the devices when transaction was initiated. A2, A3, and A4 represents the internal address sequence in the burst.

5. “t” represents the cycle at which a Read/Write operation is started. t+1 and t+2 are the first and second clock cycles succeeding the “t” clock cycle.

6. Data inputs are registered at K and K rising edges. Data outputs are delivered on C and C rising edges, except when in single clock mode.

7. It is recommended that K = K and C = C when clock is stopped. This is not essential, but permits most rapid restart by overcoming transmission line charging

symmetrically.

8. This signal was HIGH on previous K clock rise. Initiating consecutive Write operations on consecutive K clock rises is not permitted. The device ignores the second

Write request.

9. This signal was LOW on previous K clock rise. Initiating consecutive Read operations on consecutive K clock rises is not permitted.The device ignores the second

Read request.

Document #: 001-04310 Rev. *A

Page 5 of 18

[+] Feedback

�CY7C1308DV25C

PRELIMINARY

Maximum Ratings

Current into Outputs (LOW)......................................... 20 mA

Exceeding maximum ratings may impair the useful life of the

device. These user guidelines are not tested

Storage Temperature ..................................... −65°C to +150°C

Ambient Temperature with

Power Applied.................................................. −55°C to +125°C

Supply Voltage on VDD Relative to GND .........−0.5V to +3.6V

DC Applied to Outputs in High-Z...........−0.5V to VDDQ + 0.5V

DC Input

Voltage[10]

Static Discharge Voltage........................................... >2001V

(per MIL-STD-883, Method 3015)

Latch Up Current ................................................... > 200 mA

Operating Range

Range

Ambient

Temperature (TA)

VDD[11]

VDDQ[11]

0°C to +70°C

2.5 ± 0.1V

1.4V to 1.9V

Com’l

................................−0.5V to VDDQ + 0.5V

Electrical Characteristics Over the Operating Range [12]

Parameter

Description

Test Conditions

Min

Typ

Max

Unit

VDD

Power Supply Voltage

2.4

2.5

2.6

V

VDDQ

I/O Supply Voltage

1.4

1.5

1.9

V

VOH

Output HIGH Voltage

Note 14

VDDQ/2–0.12

VDDQ/2+0.12

V

VOL

Output LOW Voltage

Note 15

VDDQ/2–0.12

VDDQ/2+0.12

V

VDDQ–0.2

VDDQ

V

VSS

0.2

V

VOH(LOW)

Output HIGH Voltage

IOH = –0.1 mA, Nominal Impedance

VOL(LOW)

Output LOW Voltage

IOL = 0.1 mA, Nominal Impedance

VIH

Input HIGH Voltage[10]

VIL

Input LOW Voltage[10, 13]

IX

Input Load Current

IOZ

Output Leakage Current

Voltage[16]

VREF

Input Reference

IDD

VDD Operating Supply

ISB1

Automatic Power-Down

VREF+0.1

VDDQ+0.3

V

–0.3

VREF – 0.1

V

GND ≤ VI ≤ VDDQ

–5

5

μA

GND ≤ VI ≤ VDDQ, Output Disabled

–5

5

μA

0.95

V

VDD = Max., IOUT = 0 mA, 167 MHz

f = fMAX = 1/tCYC

200 MHz

Typical Value = 0.75V

0.68

0.75

600

mA

700

mA

250 MHz

850

mA

Max. VDD, Both Ports

167 MHz

Deselected, VIN ≥ VIH or 200 MHz

VIN ≤ VIL f = fMAX = 1/tCYC,

250 MHz

Inputs Static

250

mA

300

mA

350

mA

Shaded areas contain advance information.

AC Input Requirements

Min

Typ

Max

Unit

VIH

Parameter

Input High (Logic 1) Voltage

Description

Test Conditions

VREF + 0.2

–

–

V

VIL

Input Low (Logic 0) Voltage

–

–

VREF – 0.2

V

Notes

10. Overshoot: VIH(AC) < VDDQ + 0.85V (Pulse width less than tCYC/2). Undershoot: VIL(AC) > –1.5V (Pulse width less than tCYC/2).

11. Power-up: Assumes a linear ramp from 0V to VDD(min.) within 200 ms. During this time VIH < VDD and VDDQ < VDD.

12. All voltage referenced to ground.

13. This spec is for all inputs except C and C Clock. For C and C Clock, VIL(Max.) = VREF – 0.2V.

14. Output are impedance controlled. IOH = –(VDDQ/2)/(RQ/5) for values of 175Ω