CY7C199C

256K (32K x 8) Static RAM

Features

General Description

• Fast access time: 12 ns, 15 ns, 20 ns, and 25 ns

• Wide voltage range: 5.0V ± 10% (4.5V to 5.5V)

• CMOS for optimum speed/power

• TTL–compatible Inputs and Outputs

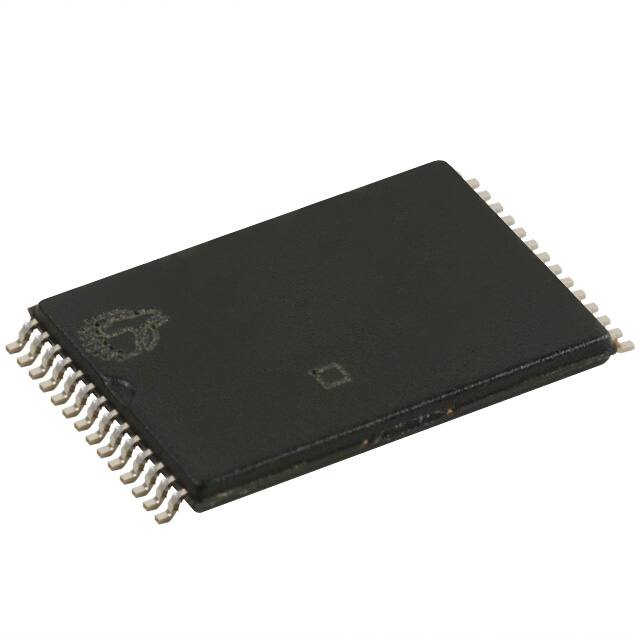

• Available in 28 DIP, 28 SOJ, and 28 TSOP I packages

• Also available in Lead-Free 28 DIP

The CY7C199C is a high-performance CMOS Asynchronous

SRAM organized as 32K by 8 bits that supports an

asynchronous memory interface. The device features an

automatic power-down feature that significantly reduces

power consumption when deselected.

See the Truth Table in this data sheet for a complete

description of read and write modes.

The CY7C199C is available in 28 DIP, 28 SOJ, and 28 TSOP I

package(s).

• 2.0V Data Retention

• Low CMOS standby power

• Automated Power-down when deselected

Logic Block Diagram

RAM Array

Sense Amps

Row Decoder

Input Buffer

I/Ox

CE

Column Decoder

WE

Power

Down

Circuit

OE

A

X

X

Product Portfolio

Maximum Access Time

12 ns

15 ns

20 ns

25 ns

Unit

12

15

20

25

ns

Maximum Operating Current

85

80

75

75

mA

Maximum CMOS Standby Current

(low power)

500

500

500

500

µA

Note:

1. For best-practices recommendations, please refer to the Cypress application note System Design Guidelines on www.cypress.com.

Cypress Semiconductor Corporation

Document #: 38-05408 Rev. *B

•

3901 North First Street

•

San Jose, CA 95134

•

408-943-2600

Revised November 05, 2004

�CY7C199C

Pin Layout and Specifications

28 DIP (6.9 x 35.6 x 3.5 mm) – P21

OE

A1

A2

A3

A4

WE

VCC

A5

A6

A7

A8

A9

A10

A11

1

2

3

4

5

6

7

8

9

10

11

12

13

14

A5

1

28

VCC

A6

2

27

WE

A7

3

26

A4

A8

4

25

A3

A9

5

24

A2

A10

6

23

A1

A11

7

22

OE

A12

8

21

A0

A13

9

20

CE

A14

10

19

I/O7

I/O0

11

18

I/O6

I/O1

12

17

I/O5

I/O2

13

16

I/O4

VSS

14

15

I/O3

28 TSOP I (8 x 13.4 mm) – Z28

28

27

26

25

24

23

22

21

20

19

18

17

16

15

A0

CE

I/O7

I/O6

I/O5

I/O4

I/O3

VSS

I/O2

I/O1

I/O0

A14

A13

A12

28 SOJ – V21

Document #: 38-05408 Rev. *B

A5

1

28

VCC

A6

2

27

WE

A7

3

26

A4

A8

4

25

A3

A9

5

24

A2

A10

6

23

A1

A11

7

22

OE

A12

8

21

A0

A13

9

20

CE

A14

10

19

I/O7

I/O0

11

18

I/O6

I/O1

12

17

I/O5

I/O2

13

16

I/O4

VSS

14

15

I/O3

Page 2 of 13

�CY7C199C

Pin Description

Pin

Type

Description

DIP

SOJ

TSOP I

1, 2, 3, 4, 5, 6, 7,

8, 9, 10, 21, 23,

24, 25, 26

1, 2, 3, 4, 5, 6, 7,

8, 9, 10, 21, 23,

24, 25, 26

2, 3, 4, 5, 8, 9,

10, 11, 12, 13,

14, 15, 16, 17,

28

20

20

27

11, 12, 13, 15,

16, 17, 18, 19

11, 12, 13, 15,

16, 17, 18, 19

18, 19, 20, 22,

23, 24, 25, 26

Output Enable

22

22

1

Power (5.0V)

28

28

7

Supply

Ground

14

14

21

Control

Write Enable

27

27

6

AX

Input

Address Inputs

CE

Control

Chip Enable

I/OX

Input or

Output

Data Input/Outputs

OE

Control

VCC

Supply

VSS

WE

Truth Table

Document #: 38-05408 Rev. *B

Page 3 of 13

�CY7C199C

Maximum Ratings (Above which the useful life may be impaired. For user guidelines, not tested.)

Parameter

Description

Value

Unit

TSTG

Storage Temperature

–65 to +150

°C

TAMB

Ambient Temperature with Power Applied (i.e., case temperature)

–55 to +125

°C

VCC

Core Supply Voltage Relative to VSS

–0.5 to +7.0

V

VIN, VOUT

DC Voltage Applied to any Pin Relative to VSS

–0.5 to VCC + 0.5

V

IOUT

Output Short-Circuit Current

20

VESD

Static Discharge Voltage (per MIL-STD-883, Method 3015)

> 2001

V

ILU

Latch-up Current

> 200

mA

mA

Operating Range

Range

Ambient Temperature (TA)

Voltage Range (VCC)

0°C to 70°C

5.0V ± 10%

–40°C to 85°C

5.0V ± 10%

Commercial

Industrial

DC Electrical Characteristics Over the Operating Range (–12, –15)[2]

12 ns

Parameter

Description

Condition

15 ns

Power

Min.

Max.

Min.

Max.

Unit

VIH

Input HIGH Voltage

–

2.2

VCC +

0.3

2.2

VCC +

0.3

V

VIL

Input LOW Voltage

–

–0.5

0.8

–0.5

0.8

V

VOH

Output HIGH Voltage VCC = Min., IOH = –4.0 mA

–

2.4

–

2.4

–

V

VOL

Output LOW Voltage VCC = Min., IOL = 8.0 mA

–

–

0.4

–

0.4

V

ICC

VCC Operating Supply VCC = Max., IOUT = 0 mA, f = FMAX =

Current

1/tRC

Automatic CE

Max. VCC, CE ≥ VIH, VIN ≥ VIH or VIN

Power-down Current ≤ VIL, f = FMAX

TTL Inputs

–

–

85

–

80

mA

–

–

30

–

30

mA

L

–

10

–

10

mA

Automatic CE

Max. VCC, CE ≥ VCC – 0.3V, VIN ≥ VCC

Power-down Current – 0.3V, or VIN ≤ 0.3V, f = 0

CMOS Inputs

–

–

10

–

10

mA

L

–

500

–

500

µA

ISB1

ISB2

IOZ

Output Leakage

Current

GND ≤ Vi ≤ VCC, Output Disabled

–

–5

+5

–5

+5

µA

IIX

Input Load Current

GND ≤ Vi ≤ VCC

–

–5

+5

–5

+5

µA

DC Electrical Characteristics Over the Operating Range (–20, –25)[2]

20 ns

Parameter

Description

Condition

Power

25 ns

Min. Max. Min. Max.

Unit

VIH

Input HIGH Voltage

–

2.2

VCC

+ 0.3

2.2

VCC

+ 0.3

V

VIL

Input LOW Voltage

–

–0.5

0.8

–0.5

0.8

V

VOH

Output HIGH Voltage VCC = Min., IOH = –4.0 mA

–

2.4

–

2.4

–

V

VOL

Output LOW Voltage VCC = Min., IOL = 8.0 mA

–

–

0.4

–

0.4

V

ICC

VCC Operating Supply VCC = Max., IOUT = 0 mA, f = FMAX =

Current

1/tRC

Automatic CE

Max. VCC, CE ≥ VIH, VIN ≥ VIH or VIN

Power-down Current ≤ VIL, f = FMAX

TTL Inputs

–

–

75

–

75

mA

–

–

30

–

30

mA

L

–

10

–

10

mA

ISB1

Note:

2. VIL (min) = –2.0V for pulse durations of less than 20 ns.

Document #: 38-05408 Rev. *B

Page 4 of 13

�CY7C199C

DC Electrical Characteristics Over the Operating Range (–20, –25)[2] (continued)

20 ns

Parameter

Description

Condition

Power

Automatic CE

Max. VCC, CE ≥ VCC – 0.3V, VIN ≥ VCC

Power-down Current – 0.3V, or VIN ≤ 0.3V, f = 0

CMOS Inputs

ISB2

25 ns

Min. Max. Min. Max.

Unit

–

–

10

–

10

mA

L

–

500

–

500

µA

IOZ

Output Leakage

Current

GND ≤ Vi ≤ VCC, Output Disabled

–

–5

+5

–5

+5

µA

IIX

Input Load Current

GND ≤ Vi ≤ VCC

–

–5

+5

–5

+5

µA

Capacitance[3]

Max.

Parameter

Description

CIN

Input Capacitance

COUT

Output Capacitance

Conditions

ALL – PACKAGES

Unit

TA = 25°C, f = 1 MHz,

VCC = 5.0V

8

pF

8

AC Test Loads

Output Loads

Output Loads

for t HZOE , tHZCE & tHZW E

R1

R3

VCC

VCC

Output

C1

R2

C2

(A)*

(B)*

Thevenin Equivalent

Output

R th

R4

All Input Pulses

VCC

VT

VSS

90%

90%

10%

10%

Rise Time

1 V/ns

Fall Time

1 V/ns

* including scope and jig capacitance

AC Test Conditions

Parameter

Description

Nom.

Unit

pF

C1

Capacitor 1

30

C2

Capacitor 2

5

R1

Resistor 1

480

R2

Resistor 2

255

R3

Resistor 3

480

R4

Resistor 4

255

RTH

Resistor Thevenin

167

VTH

Voltage Thevenin

1.73

Ω

V

Note:

3. Tested initially and after any design or process change that may affect these parameters.

Document #: 38-05408 Rev. *B

Page 5 of 13

�CY7C199C

Thermal Resistance[4]

Parameter

ΘJA

ΘJC

Description

Conditions

Thermal Resistance Still Air, soldered on a

(Junction to Ambient) 3 × 4.5 square inch,

Thermal Resistance two–layer printed

circuit board

(Junction to Case)

TSOP I

SOJ

DIP

Unit

88.6

79

TBD

°C/W

21.94

41.42

TBD

AC Electrical Characteristics[5, 6, 7]

12 ns

Parameter

Description

15 ns

20 ns

25 ns

Min

Max

Min

Max

Min

Max

Min

Max

Unit

tRC

Read Cycle Time

12

–

15

–

20

–

25

–

ns

tAA

Address to Data Valid

–

12

–

15

–

20

–

25

ns

tOHA

Data Hold from Address

Change

3

–

3

–

3

–

3

–

ns

tACE

CE to Data Valid

–

12

–

15

–

20

–

25

ns

tDOE

OE to Data Valid

–

5

–

7

–

9

–

9

ns

tLZOE

OE to Low Z

0

–

0

–

0

–

0

–

ns

tHZOE

OE to High Z

–

5

–

7

–

9

–

9

ns

tLZCE

CE to Low Z

3

–

3

–

3

–

3

–

ns

tHZCE

CE to High Z

–

5

–

7

–

9

–

9

ns

tPU

CE to Power-up

0

–

0

–

0

–

0

–

ns

tPD

CE to Power-down

–

12

–

15

–

20

–

20

ns

tWC

Write Cycle Time

12

–

15

–

20

–

25

–

ns

tSCE

CE to Write End

9

–

10

–

15

–

15

–

ns

tAW

Address Set-up to Write End

9

–

10

–

15

–

15

–

ns

tHA

Address Hold from Write End

0

–

0

–

0

–

0

–

ns

tSA

Address Set-up to Write Start

0

–

0

–

0

–

0

–

ns

tPWE

WE Pulse Width

8

–

9

–

15

–

15

–

ns

tSD

Data Set-up to Write End

8

–

9

–

10

–

10

–

ns

tHD

Data Hold from Write End

0

–

0

–

0

–

0

–

ns

tHZWE

WE LOW to High Z

–

7

–

7

–

10

–

10

ns

tLZWE

WE HIGH to Low Z

3

–

3

–

3

–

3

–

ns

Data Retention Characteristics[8]

ALL

Parameter

Description

VDR

VCC for Data Retention

ICCDR

Data Retention Current

tCDR

Chip Deselect to Data

Retention Time

tR

Operation Recovery Time

Condition

VCC = VDR=2.0V, CE ≥ VCC – 0.3V, VIN ≥ VCC

– 0.3V or VIN ≤ 0.3V

Min

Max

Unit

2.0

–

V

–

150

mA

0

–

ns

200

–

µs

Notes:

4. Test Conditions assume a transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V.

5. At any given temperature and voltage condition, tHZCE is less than tLZCE, tHZOE is less than tLZOE, and tHZWE is less than tLZWE for any given device.

6. The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. CE and WE must be LOW to initiate a write, and the transition of any

of these signals can terminate the write. The input data set–up and hold timing should be referenced to the leading edge of the signal that terminates the write.

7. tHZOE, tHZCE, tHZWE are specified as in part (b) of the A/C Test Loads. Transitions are measured ± 200 mV from steady state voltage.

8. L-version only.

Document #: 38-05408 Rev. *B

Page 6 of 13

�CY7C199C

Timing Waveforms

Data Retention Waveform

VCC

DATA RETENTION MODE

tCDR

tR

CE

Read Cycle No. 1[9, 10]

tRC

Address

tAA

tOHA

Data Out

Previous Data Valid

Data Valid

Read Cycle No. 2[11, 12]

tRC

Address

CE

tHZCE

tACE

OE

tDOE

tHZOE

tLZOE

High Z

Data Out

VCC

Current

ICC

ISB

High Z

Data Valid

tLZCE

tPU

tPD

50%

50%

Notes:

9. Device is continuously selected. OE = VIL = CE.

10. WE is HIGH for Read Cycle.

11. This cycle is OE Controlled and WE is HIGH read cycle.

12. Address valid prior to or coincident with CE transition LOW.

Document #: 38-05408 Rev. *B

Page 7 of 13

�CY7C199C

Timing Waveforms (continued)

Write Cycle No. 1 (WE Controlled)[13, 14, 15]

tWC

Address

tSCE

CE

tAW

tHA

tPWE

tSA

WE

OE

tHZOE

Data In/Out

tSD

Undefined

tHD

Data-In Valid

see footnotes

Write Cycle No. 2 (CE Controlled)[14, 16, 17]

tWC

Address

tSCE

CE

tSA

tHA

tAW

WE

tSD

Data In/Out

High Z

Data-In Valid

tHD

High Z

Notes:

13. This cycle is WE controlled, OE is HIGH during write.

14. Data In/Out is high impedance if OE = VIH.

15. During this period the I/Os are in output state and input signals should not be applied.

16. This cycle is CE controlled.

17. If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high-impedance state.

Document #: 38-05408 Rev. *B

Page 8 of 13

�CY7C199C

Timing Waveforms (continued)

Write Cycle No. 3 (WE Controlled, OE Low)[18]

t WC

Address

tSCE

CE

tAW

tHA

tPWE

tSA

WE

tSD

Data

In/Out

Undefined

tHD

Undefined

See Footnotes

Data-In Valid

see footnotes

tHZWE

tLZWE

Note:

18. The cycle is WE controlled, OE LOW. The minimum write cycle time is the sum of tHZWE and tSD.

Document #: 38-05408 Rev. *B

Page 9 of 13

�CY7C199C

Ordering Information

Package

Name

Power

Option

Operating

Range

28 SOJ

Standard

Commercial

V21

28 SOJ (Pb-Free)

Standard

Commercial

Z28

28 TSOP I (8 x 13.4 mm)

Standard

Commercial

Speed

Ordering Code

12 ns

CY7C199C–12VC

V21

12 ns

CY7C199C–12VXC

12 ns

CY7C199C–12ZC

Package Type

12 ns

CY7C199C–12ZXC

Z28

28 TSOP I (8 x 13.4 mm) (Pb-Free)

Standard

Commercial

12 ns

CY7C199C–12VI

V21

28 SOJ

Standard

Industrial

12 ns

CY7C199C–12VXI

V21

28 SOJ (Pb-Free)

Standard

Industrial

15 ns

CY7C199C–15PC

P21

28 DIP (6.9 x 35.6 x 3.5 mm)

Standard

Commercial

15 ns

CY7C199C–15PXC

P21

28 DIP (6.9 x 35.6 x 3.5 mm) (Pb-Free)

Standard

Commercial

15 ns

CY7C199C–15VC

V21

28 SOJ

Standard

Commercial

15 ns

CY7C199C–15VXC

V21

28 SOJ (Pb-Free)

Standard

Commercial

15 ns

CY7C199C–15ZC

Z28

28 TSOP I (8 x 13.4 mm)

Standard

Commercial

15 ns

CY7C199C–15ZXC

Z28

28 TSOP I (8 x 13.4 mm) (Pb-Free)

Standard

Commercial

15 ns

CY7C199C–15VI

V21

28 SOJ

Standard

Industrial

15 ns

CY7C199C–15VXI

V21

28 SOJ (Pb-Free)

Standard

Industrial

15 ns

CY7C199CL–15VC

V21

28 SOJ

Low Power

Commercial

15 ns

CY7C199CL–15VXC

V21

28 SOJ (Pb-Free)

Low Power

Commercial

15 ns

CY7C199CL–15ZC

Z28

28 TSOP I (8 x 13.4 mm)

Low Power

Commercial

15 ns

CY7C199CL–15ZXC

Z28

28 TSOP I (8 x 13.4 mm) (Pb-Free)

Low Power

Commercial

15 ns

CY7C199CL–15VI

V21

28 SOJ

Low Power

Industrial

15 ns

CY7C199CL–15VXI

V21

28 SOJ (Pb-Free)

Low Power

Industrial

20 ns

CY7C199C–20VC

V21

28 SOJ

Standard

Commercial

20 ns

CY7C199C–20VXC

V21

28 SOJ (Pb-Free)

Standard

Commercial

20 ns

CY7C199C–20ZI

Z28

28 TSOP I (8 x 13.4 mm)

Standard

Industrial

20 ns

CY7C199C–20ZXI

Z28

28 TSOP I (8 x 13.4 mm) (Pb-Free)

Standard

Industrial

25 ns

CY7C199C–25PC

P21

28 DIP (6.9 x 35.6 x 3.5 mm)

Standard

Commercial

25 ns

CY7C199C–25PXC

P21

28 DIP (6.9 x 35.6 x 3.5 mm) (Pb-Free)

Standard

Commercial

Document #: 38-05408 Rev. *B

Page 10 of 13

�CY7C199C

Package Diagram

28-Lead Thin Small Outline Package Type 1 (8 x 13.4 mm) Z28

51-85071-*G

Document #: 38-05408 Rev. *B

Page 11 of 13

�CY7C199C

Package Diagram (continued)

28-Lead (300-Mil) Molded SOJ V21

MIN.

MAX.

DIMENSIONS IN INCHES

PIN 1 ID

14

DETAIL

A

EXTERNAL LEAD DESIGN

1

0.291

0.300

15

0.330

0.350

0.026

0.032

0.013

0.019

28

0.014

0.020

OPTION 1

0.697

0.713

OPTION 2

SEATING PLANE

0.120

0.140

A

0.050

TYP.

0.007

0.013

0.004

0.262

0.272

0.025 MIN.

51-85031-*B

28-Lead (300-Mil) PDIP P21

SEE LEAD END OPTION

14

1

DIMENSIONS IN INCHES [MM] MIN.

MAX.

REFERENCE JEDEC MO-095

0.260[6.60]

0.295[7.49]

15

28

PACKAGE WEIGHT: 2.15 gms

0.030[0.76]

0.080[2.03]

SEATING PLANE

1.345[34.16]

1.385[35.18]

0.290[7.36]

0.325[8.25]

0.120[3.05]

0.140[3.55]

0.140[3.55]

0.190[4.82]

0.115[2.92]

0.160[4.06]

0.015[0.38]

0.060[1.52]

0.090[2.28]

0.110[2.79]

0.009[0.23]

0.012[0.30]

0.055[1.39]

0.065[1.65]

0.015[0.38]

0.020[0.50]

3° MIN.

0.310[7.87]

0.385[9.78]

SEE LEAD END OPTION

LEAD END OPTION

51-85014-*D

(LEAD #1, 14, 15 & 28)

All product and company names mentioned in this document may be the trademarks of their respective holders.

Document #: 38-05408 Rev. *B

Page 12 of 13

© Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

�CY7C199C

Document History Page

Document Title: CY7C199C 256K (32K x 8) Static RAM

Document Number: 38-05408

REV.

ECN No.

Issue

Date

Orig. of

Change

Description of Change

**

129233

09/11/03

HGK

New Data Sheet

*A

129697

09/15/03

KKV

Minor change:

Move Product Portfolio from page 4 to page 1

Move Truth table from page 9 to page 3

*B

341574

See ECN

PCI

Added Lead-Free part to Ordering info on Page #10

Document #: 38-05408 Rev. *B

Page 13 of 13

�