The following document contains information on Cypress products. The document has the series

name, product name, and ordering part numbering with the prefix “MB”. However, Cypress will

offer these products to new and existing customers with the series name, product name, and

ordering part number with the prefix “CY”.

How to Check the Ordering Part Number

1. Go to www.cypress.com/pcn.

2. Enter the keyword (for example, ordering part number) in the SEARCH PCNS field and click

Apply.

3. Click the corresponding title from the search results.

4. Download the Affected Parts List file, which has details of all changes

For More Information

Please contact your local sales office for additional information about Cypress products and

solutions.

About Cypress

Cypress is the leader in advanced embedded system solutions for the world's most innovative

automotive, industrial, smart home appliances, consumer electronics and medical products.

Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable,

high-performance memories help engineers design differentiated products and get them to market

first. Cypress is committed to providing customers with the best support and development

resources on the planet enabling them to disrupt markets by creating new product categories in

record time. To learn more, go to www.cypress.com.

�MB91460M Series

FR60 32-bit Microcontroller

MB91460M series is a line of general-purpose 32-bit RISC microcontrollers designed for embedded control applications which require

high-speed real-time processing, such as consumer devices and on-board vehicle systems. This series uses the FR60 CPU, which

is compatible with the FR family of CPUs.

This series contains the LIN-USART, CAN controllers, MediaLB(512Fs)*, and I2S.

*: This product is licensed by SMSC Europe in conditions where it is used in the MediaLB system compliant with the MediaLB

specification of the SMSC Europe.

Features

FR60 CPU core

■

32-bit RISC, load/store architecture, five-stage pipeline

■

16-bit fixed-length instructions (basic instructions)

■

Instruction execution speed: 1 instruction per cycle

■

Instructions including memory-to-memory transfer, bit

manipulation, and barrel shift instructions: Instructions suitable

for embedded applications

■

Function entry/exit instructions and register data multi-load

store instructions : Instructions supporting C language

■

Register interlock function: Facilitating assembly-language

coding

■

Built-in multiplier with instruction-level support

❐ Signed 32-bit multiplication: 5 cycles

❐ Signed 16-bit multiplication: 3 cycles

■

Interrupts (save PC/PS) : 6 cycles (16 priority levels)

■

Harvard architecture enabling program access and data

access to be performed simultaneously

■

Instructions compatible with the FR family

Internal peripheral resources

■

Bit search module (for REALOS)

❐ Function to search from the MSB (most significant bit) for the

position of the first “0”, “1”, or changed bit in a word

■

LIN-USART (full duplex double buffer): 9 channels

❐ Clock synchronous/asynchronous selectable

❐ Sync-break detection

❐ Internal dedicated baud rate generator

❐ 4 channel is equipped with 16 stages of transmission and

reception FIFO buffers.

■

I2C bus interface (supports 400 kbps): 8 channels

❐ Master/slave transmission and reception

❐ Arbitration function, clock synchronization function

■

CAN controller (C-CAN): 2 channels

❐ Maximum transfer speed: 1 Mbps

❐ 32 transmission/reception message buffers

■

MediaLB

❐ Supports 512Fs

❐ 15 channels

❐ Contains local channel buffers: 32 bit × 2 k.

❐ Contains a 32 bit × 2 k FIFO buffer for between MediaLB and

I2S.

■

I2S : 10 channels

■

General-purpose ports : Maximum 175 ports

■

16-bit PPG timer : 8 channels

■

DMAC (DMA Controller)

❐ Maximum of 5 channels able to operate simultaneously.

(External to external : 1 channel)

❐ 3 transfer sources (external pin/internal peripheral/software)

❐ Activation source can be selected using software.

❐ Addressing mode specifies full 32-bit addresses

(increment/decrement/fixed)

❐ Transfer mode (demand transfer/burst transfer/step

transfer/block transfer)

❐ Fly-by transfer support (between external I/O and memory)

❐ Transfer data size selectable from 8/16/32-bit

❐ Multi-byte transfer enabled (by software)

❐ DMAC descriptor in I/O areas (200H to 240H, 1000H to

1024H)

■

16-bit reload timer: 5 channels

■

16-bit free-run timer: 4 channels (1 channel each for ICU and

OCU)

■

Input capture: 4 channels (operates in conjunction with the

free-run timer)

■

Output compare: 4 channels (operates in conjunction with the

free-run timer)

■

Watchdog timer

■

Real-time clock

■

Low-power consumption modes : Sleep/stop mode function

■

Low voltage detection circuit

■

Clock modulator

■

Sub-clock calibration

❐ Corrects the real-time clock timer when operating with the

32 kHz or CR oscillator

■

■

A/D converter (successive approximation type)

❐ 10-bit resolution: 12 channels

❐ Conversion time: minimum 3 s

External interrupt inputs : 16 channels

2

❐ 4 channels shared with CAN RX or I C pins

Cypress Semiconductor Corporation

Document Number: 002-04615 Rev. *A

•

198 Champion Court

•

San Jose, CA 95134-1709

•

408-943-2600

Revised May 18, 2016

�MB91460M Series

■

■

Main oscillator stabilization timer

❐ Generates an interrupt in sub-clock mode after the

stabilization wait time has elapsed on the 23-bit stabilization

wait time counter

Sub-oscillator stabilization timer

❐ Generates an interrupt in main clock mode after the

stabilization wait time has elapsed on the 15-bit stabilization

wait time counter

Document Number: 002-04615 Rev. *A

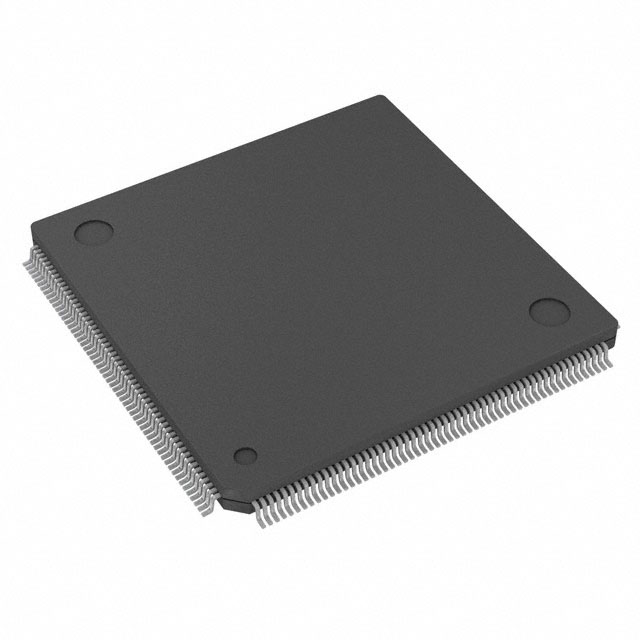

Package and technology

■

Package : QFP-216

■

CMOS 0.18 m technology

■

Power supply range 3 V to 5 V (1.8 V internal logic provided by

a step-down voltage converter)

■

Operating temperature range: between − 40°C and + 105°C

Page 2 of 128

�MB91460M Series

Contents

Product Lineup ................................................................ 4

Pin Assignment ................................................................ 5

Pin Description ................................................................. 6

I/O Circuit Types .....................................................................19

Handling Devices ............................................................ 24

Notes On Debugger ........................................................ 28

Block Diagram ................................................................ 29

Features .................................................................... 30

Internal architecture ................................................... 30

Programming model .................................................. 31

Registers ................................................................... 32

Embedded Program/Data Memory (Flash) ................... 35

Flash features ............................................................ 35

Operation modes ....................................................... 35

Flash access in CPU mode ....................................... 36

Parallel Flash programming mode ............................ 39

Memory Space ................................................................ 41

Memory Map .................................................................... 42

Document Number: 002-04615 Rev. *A

I/O Map ............................................................................. 43

Interrupt Vector Table .................................................... 80

Recommended Settings ................................................. 85

PLL and Clockgear settings ...................................... 85

Clock Modulator settings ........................................... 86

Electrical Characteristics ............................................... 90

Absolute maximum ratings ....................................... 90

Recommended operating conditions ......................... 92

DC characteristics ..................................................... 93

A/D converter characteristics .................................... 96

FLASH memory program/erase characteristics ...... 100

AC characteristics ................................................... 101

Ordering Information .................................................... 124

Package Dimension ...................................................... 125

Main Changes ............................................................... 126

Document History ......................................................... 127

Page 3 of 128

�MB91460M Series

1. Product Lineup

Feature

MB91F467MA

MB91V460 (Reference)

Core frequency

80 MHz

80 MHz

Resource frequency

20 MHz

40 MHz

External bus frequency

40 MHz

40 MHz

Watchdog timer

Yes

Yes

Bit Search

Yes

Yes

Reset input pin

Yes

Yes

Low power consumption mode

Yes

Yes

DMA

5 channels

5 channels

Flash

1 Mbyte

SRAM

Yes

No

D-RAM

48 Kbytes

64 Kbytes

I/D-RAM

16 Kbytes

64 Kbytes

Direct map cache

8 Kbytes

16 Kbytes

I-Cache

4 Kbytes

4 Kbytes

Boot-ROM

4 Kbytes

4 Kbytes

RTC

1 channel

1 channel

Free-run timer

4 channels

8 channels

ICU

4 channels

8 channels

OCU

4 channels

8 channels

Reload timer

5 channels

8 channels

PPG

8 channels

16 channels

C_CAN

2 channels (32 msg + 64 msg)

6 channels (128 msg)

LIN-USART

5 channels + 4 channels FIFO

4 channels + 4 channels FIFO + 8 channels

8 channels

4 channels

512Fs

No

10 channels

No

24 bit address / 16 bit data

32 bit address / 32 bit data

External Interrupts

16 channels

16 channels

A/D converter

12 channels

32 channels

DSU4

Yes

Yes

EDSU

Yes

Yes

Flash security

I2C

MediaLB

I2S

External bus

Document Number: 002-04615 Rev. *A

Page 4 of 128

�MB91460M Series

2. Pin Assignment

VCC5

P24_2/INT2

P17_3/PPG3

P17_2/PPG2

P17_1/PPG1

P17_0/PPG0

P14_3/ICU3/TIN3/TRG3

P14_2/ICU2/TIN2/TRG2

P14_1/ICU1/TIN1/TRG1

P14_0/ICU0/TIN0/TRG0

P22_3/INT15

P22_2/INT13

P22_1/INT14

P22_0/INT12

P23_6/INT11

P23_4/INT10

P40_5/SCL6

P40_4/SDA6

P40_3/SCL5

P40_2/SDA5

P40_1/SCL4

P40_0/SDA4

P24_7/SCL3/INT7

P24_6/SDA3/INT6

VCC5

VSS

P15_3/OCU3/TOT3

P15_2/OCU2/TOT2

P15_1/OCU1/TOT1

P15_0/OCU0/TOT0

P18_2/SCK6

P18_1/SOT6

P18_0/SIN6

P19_6/SCK5

P19_5/SOT5

P19_4/SIN5

P19_2/SCK4

P19_1/SOT4

P19_0/SIN4

VCC5

VSS

P20_6/SCK3/FRCK3

P20_5/SOT3

P20_4/SIN3

P20_2/SCK2/FRCK2

P20_1/SOT2

P20_0/SIN2

P21_6/SCK1/FRCK1

P21_5/SOT1

P21_4/SIN1

P21_2/SCK0/FRCK0

P21_1/SOT0

P21_0/SIN0

VCC5

(TOP VIEW)

(2)

(3)

216

215

214

213

212

211

210

209

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

(1)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

MB91F467MA

LQFP-216

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

VSS

TRSTX

INITX

MD0

MD1

MD2

MD3

MD4

P23_3/TX1

P23_2/RX1/INT9

P23_1/TX0

P23_0/RX0/INT8

P24_1/INT1

P24_0/INT0

P22_5/SCL0

P22_4/SDA0/INT14

P40_7/SCL7

P40_6/SDA7

AVRH

AVCC3

AVSS/AVRL

P28_3/AN11

P28_2/AN10

P28_1/AN9

P28_0/AN8

P29_7/AN7

P29_6/AN6

P29_5/AN5

P29_4/AN4

P29_3/AN3

P29_2/AN2

P29_1/AN1

P29_0/AN0

VSS

WDRESETX

P35_2/SCK8

P35_1/SOT8

P35_0/SIN8

P17_7/PPG7

P17_6/PPG6

P17_5/PPG5

P17_4/PPG4

P16_7/ATGX

P38_1/SD9

P38_0/SD8

P39_7/SD7

P39_6/SD6

P39_5/SD5

P39_4/SD4

P39_3/SD3

P39_2/SD2

P39_1/SD1

P39_0/SD0

VCC3

VSS

P01_0/D16

P01_1/D17

P01_2/D18

P01_3/D19

P01_4/D20

P01_5/D21

P01_6/D22

P01_7/D23

P00_0/D24

P00_1/D25

P00_2/D26

P00_3/D27

P00_4/D28

P00_5/D29

P00_6/D30

P00_7/D31

VCC3

VSS

P07_0/A00

P07_1/A01

P07_2/A02

P07_3/A03

P07_4/A04

P07_5/A05

P07_6/A06

P07_7/A07

P06_0/A08

P06_1/A09

P06_2/A10

P06_3/A11

P06_4/A12

P06_5/A13

P06_6/A14

P06_7/A15

VCC3

VSS

P05_0/A16

P05_1/A17

P05_2/A18

P05_3/A19

P05_4/A20

P05_5/A21

P05_6/A22

P05_7/A23

P18_6/SCK7

P18_5/SOT7

P18_4/SIN7

P36_5/MLBDAT

P36_6/MLBSIG

P36_7/MLBCLK

P36_2/WS0

P36_3/SCK0

VSS

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

VSS

INT3/P24_3

INT15/SDA1/P22_6

SCL1/P22_7

SDA2/INT4/P24_4

SCL2/INT5/P24_5

ICS2/P16_6

ICS1/P16_5

ICS0/P16_4

ICD3/P16_3

ICD2/P16_2

ICD1/P16_1

ICD0/P16_0

BREAK/P15_7

ICLK/P15_6

SHUTDOWN

DREQ0/P13_0

DACKX0/P13_1

DEOP0/DEOTX0/P13_2

VCC3

VSS

C_2

CS6X/P09_6

CS5X/P09_5

CS4X/P09_4

CS3X/P09_3

CS2X/P09_2

CS1X/P09_1

CS0X/P09_0

IORDX/P11_0

IOWRX/P11_1

RDY/P08_7

BRQ/P08_6

BGRNTX/P08_5

RDX/P08_4

WR1X/P08_1

WR0X/P08_0

MCLKE/P10_6

MCLKI/P10_5

MCLKO/P10_4

WEX/P10_3

BAAX/P10_2

ASX/P10_1

SYSCLK/P10_0

VCC3

VCC3

C_1

VSS

X0

X1

VSS

X0A

X1A

VCC3

(LQQ216)

The 5 V/3 V block is the area (1) to (3) in the figure.

This area is available for both 5 V and 3 V.However, when 5 V is used in at least one place, 5 V must be used for the

area (3).

Document Number: 002-04615 Rev. *A

Page 5 of 128

�MB91460M Series

3. Pin Description

Pin no.

2

Pin name

P24_3

INT3

I/O

I/O circuit

type*

I/O

D

P22_6

3

SDA1

P22_7

SCL1

I/O

C

6

INT4

I/O

C

8

9

10

11

12

13

14

15

16

Serial data input/output pin of I2C 1.

General-purpose input/output ports

Serial clock input/output pin of I2C 1.

General-purpose input/output ports

I/O

C

Request input pin of external interrupt ch.4.

SDA2

Serial data input/output pin of I2C 2.

P24_5

General-purpose input/output ports

INT5

I/O

C

P16_6

ICS2

P16_5

ICS1

P16_4

ICS0

P16_3

ICD3

P16_2

ICD2

P16_1

ICD1

P16_0

ICD0

P15_7

BREAK

P15_6

ICLK

SHUTDOWN

Request input pin of external interrupt ch.5.

Serial clock input/output pin of I2C 2.

SCL2

7

Request input pin of external interrupt ch.3.

Request input pin of external interrupt ch.15. Exclusive from P22_3.

P24_4

5

General-purpose input/output ports

General-purpose input/output ports

INT15

4

Function

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

I

O

J

General-purpose input/output ports. Enabled when MD4 = “0”.

Status output pin of DSU4. Enabled when MD4 = “1”.

General-purpose input/output ports.Enabled when MD4 = “0”.

Status output pin of DSU4. Enabled when MD4 = “1”.

General-purpose input/output ports. Enabled when MD4 = “0”.

Status output pin of DSU4. Enabled when MD4 = “1”.

General-purpose input/output ports. Enabled when MD4 = “0”.

Data input/output pin of DSU4. Enabled when MD4 = “1”.

General-purpose input/output ports. Enabled when MD4 = “0”.

Data input/output pin of DSU4. Enabled when MD4 = “1”.

General-purpose input/output ports. Enabled when MD4 = “0”.

Data input/output pin of DSU4. Enabled when MD4 = “1”.

General-purpose input/output ports. Enabled when MD4 = “0”.

Data input/output pin of DSU4. Enabled when MD4 = “1”.

General-purpose input/output ports. Enabled when MD4 = “0”.

BREAK input pin of DSU4. Enabled when MD4 = “1”.

General-purpose input/output ports. Enabled when MD4 = “0”.

Clock output pin of DSU4. Enabled when MD4 = “1”.

Shutdown output, H active.

(Continued)

Document Number: 002-04615 Rev. *A

Page 6 of 128

�MB91460M Series

Pin no.

17

18

Pin name

P13_0

DREQ0

P13_1

DACKX0

I/O

I/O circuit

type*

I/O

H

I/O

H

P13_2

19

DEOTX0

24

25

26

27

28

29

30

31

P09_6

CS6X

P09_5

CS5X

P09_4

CS4X

P09_3

CS3X

P09_2

CS2X

P09_1

CS1X

P09_0

CS0X

P11_0

IORDX

P11_1

IOWRX

I/O

H

RDY

Input pin for DMA transfer request.

General-purpose input/output ports.

Output pin for DMA transfer request acknowledge.

Input pin for DMA transfer stop request.

Output pin for DMA transfer end.

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

P08_7

32

General-purpose input/output ports.

General-purpose input/output ports.

DEOP0

23

Function

General-purpose input/output ports.

Output pin of external bus chip select area 6.

General-purpose input/output ports.

Output pin of external bus chip select area 5.

General-purpose input/output ports.

Output pin of external bus chip select area 4.

General-purpose input/output ports.

Output pin of external bus chip select area 3.

General-purpose input/output ports.

Output pin of external bus chip select area 2.

General-purpose input/output ports.

Output pin of external bus chip select area 1.

General-purpose input/output ports.

Output pin of external bus chip select area 0.

General-purpose input/output ports.

Output pin for DMA fly-by transfer from I/O to memory.

General-purpose input/output ports.

Output pin for DMA fly-by transfer from memory to I/O.

General-purpose input/output ports.

I/O

H

External bus ready input pin (when RDY is enabled to a corresponding CS

area).

(Continued)

Document Number: 002-04615 Rev. *A

Page 7 of 128

�MB91460M Series

Pin no.

Pin name

I/O

I/O circuit

type*

I/O

H

P08_6

33

BRQ

General-purpose input/output ports.

P08_5

34

35

36

37

38

39

40

41

42

43

44

BGRNTX

P08_4

RDX

P08_1

WR1X

P08_0

WR0X

P10_6

MCLKE

P10_5

MCLKI

P10_4

MCLKO

P10_3

WEX

P10_2

BAAX

P10_1

ASX

P10_0

SYSCLK

Function

External bus open request input pin (when sharing is enabled to a

corresponding CS area) .

General-purpose input/output ports.

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

External bus release acceptance output pin (when sharing is enabled to a

corresponding CS area)

General-purpose input/output ports.

Output pin for external bus read strobe.

General-purpose input/output ports.

Output pin for external bus write strobe.

General-purpose input/output ports.

Output pin for external bus write strobe.

General-purpose input/output ports.

Output pin for external bus memory clock enabled.

General-purpose input/output ports.

Input pin for external bus memory clock.

General-purpose input/output ports.

Output pin for external bus memory clock.

General-purpose input/output ports.

Output pin for external bus write strobe.

General-purpose input/output ports.

Output pin for external bus burst access.

General-purpose input/output ports.

Output pin for external bus address strobe.

General-purpose input/output ports.

Output pin for external bus clock.

49

X0

—

G

Main oscillation pin

50

X1

—

G

Main oscillation pin

52

X0A

—

G

Sub oscillation pin

53

X1A

—

G

Sub oscillation pin

I/O

H

56

P01_0

D16

General-purpose input/output ports.

I/O pin for 16-bit external data bus.

(Continued)

Document Number: 002-04615 Rev. *A

Page 8 of 128

�MB91460M Series

Pin no.

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

74

75

Pin name

P01_1

D17

P01_2

D18

P01_3

D19

P01_4

D20

P01_5

D21

P01_6

D22

P01_7

D23

P00_0

D24

P00_1

D25

P00_2

D26

P00_3

D27

P00_4

D28

P00_5

D29

P00_6

D30

P00_7

D31

P07_0

A00

P07_1

A01

I/O

I/O circuit

type*

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

Function

General-purpose input/output ports.

I/O pin for 17-bit external data bus.

General-purpose input/output ports.

I/O pin for 18-bit external data bus.

General-purpose input/output ports.

I/O pin for 19-bit external data bus.

General-purpose input/output ports.

I/O pin for 20-bit external data bus.

General-purpose input/output ports.

I/O pin for 21-bit external data bus.

General-purpose input/output ports.

I/O pin for 22-bit external data bus.

General-purpose input/output ports.

I/O pin for 23-bit external data bus.

General-purpose input/output ports.

I/O pin for 24-bit external data bus.

General-purpose input/output ports.

I/O pin for 25-bit external data bus.

General-purpose input/output ports.

I/O pin for 26-bit external data bus.

General-purpose input/output ports.

I/O pin for 27-bit external data bus.

General-purpose input/output ports.

I/O pin for 28-bit external data bus.

General-purpose input/output ports.

I/O pin for 29-bit external data bus.

General-purpose input/output ports.

I/O pin for 30-bit external data bus.

General-purpose input/output ports.

I/O pin for 31-bit external data bus.

General-purpose input/output ports.

I/O pin for 0-bit external address bus.

General-purpose input/output ports.

I/O pin for 1-bit external address bus.

(Continued)

Document Number: 002-04615 Rev. *A

Page 9 of 128

�MB91460M Series

Pin no.

76

77

78

79

80

81

82

83

84

85

86

87

88

89

92

93

94

Pin name

P07_2

A02

P07_3

A03

P07_4

A04

P07_5

A05

P07_6

A06

P07_7

A07

P06_0

A08

P06_1

A09

P06_2

A10

P06_3

A11

P06_4

A12

P06_5

A13

P06_6

A14

P06_7

A15

P05_0

A16

P05_1

A17

P05_2

A18

I/O

I/O circuit

type*

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

Function

General-purpose input/output ports.

I/O pin for 2-bit external address bus.

General-purpose input/output ports.

I/O pin for 3-bit external address bus.

General-purpose input/output ports.

I/O pin for 4-bit external address bus.

General-purpose input/output ports.

I/O pin for 5-bit external address bus.

General-purpose input/output ports.

I/O pin for 6-bit external address bus.

General-purpose input/output ports.

I/O pin for 7-bit external address bus.

General-purpose input/output ports.

I/O pin for 8-bit external address bus.

General-purpose input/output ports.

I/O pin for 9-bit external address bus.

General-purpose input/output ports.

I/O pin for 10-bit external address bus.

General-purpose input/output ports.

I/O pin for 11-bit external address bus.

General-purpose input/output ports.

I/O pin for 12-bit external address bus.

General-purpose input/output ports.

I/O pin for 13-bit external address bus.

General-purpose input/output ports.

I/O pin for 14-bit external address bus.

General-purpose input/output ports.

I/O pin for 15-bit external address bus.

General-purpose input/output ports.

I/O pin for 16-bit external address bus.

General-purpose input/output ports.

I/O pin for 17-bit external address bus.

General-purpose input/output ports.

I/O pin for 18-bit external address bus.

(Continued)

Document Number: 002-04615 Rev. *A

Page 10 of 128

�MB91460M Series

Pin no.

95

96

97

98

99

100

101

102

103

104

105

106

107

110

111

112

113

Pin name

P05_3

A19

P05_4

A20

P05_5

A21

P05_6

A22

P05_7

A23

P18_6

SCK7

P18_5

SOT7

P18_4

SIN7

P36_5

MLBDAT

P36_6

MLBSIG

P36_7

MLBCLK

P36_2

WS0

P36_3

SCK0

P39_0

SD0

P39_1

SD1

P39_2

SD2

P39_3

SD3

I/O

I/O circuit

type*

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

L

I/O

L

I/O

L

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

Function

General-purpose input/output ports.

I/O pin for 19-bit external address bus.

General-purpose input/output ports.

I/O pin for 20-bit external address bus.

General-purpose input/output ports.

I/O pin for 21-bit external address bus.

General-purpose input/output ports.

I/O pin for 22-bit external address bus.

General-purpose input/output ports.

I/O pin for 23-bit external address bus.

General-purpose input/output ports.

Clock input/output pin of LIN-USART 7.

General-purpose input/output ports.

Serial data output pin of LIN-USART 7

General-purpose input/output ports.

Serial data input pin of LIN-USART 7

General-purpose input/output ports.

Data input/output pin for MediaLB.

General-purpose input/output ports.

Data input/output pin for MediaLB.

General-purpose input/output ports.

Clock input pin for MediaLB.

General-purpose input/output ports.

Input/output pin of L/R judgement signal for I2S.

General-purpose input/output ports.

Clock input/output pin for I2S.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.0.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.1.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.2.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.3.

(Continued)

Document Number: 002-04615 Rev. *A

Page 11 of 128

�MB91460M Series

Pin no.

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

130

Pin name

P39_4

SD4

P39_5

SD5

P39_6

SD6

P39_7

SD7

P38_0

SD8

P38_1

SD9

P16_7

ATGX

P17_4

PPG4

P17_5

PPG5

P17_6

PPG6

P17_7

PPG7

P35_0

SIN8

P35_1

SOT8

P35_2

SCK8

WDRESETX

P29_0

AN0

I/O

I/O circuit

type*

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

I/O

H

O

J

I/O

F

Function

General-purpose input/output ports.

Sound data input/output pin for I2S ch.4.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.5.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.6.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.7.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.8.

General-purpose input/output ports.

Sound data input/output pin for I2S ch.9.

General-purpose input/output ports.

A/D converter external trigger input.

General-purpose input/output ports.

Waveform output pin of programmable pulse generator PPG 4.

General-purpose input/output ports.

Waveform output pin of programmable pulse generator PPG 5.

General-purpose input/output ports.

Waveform output pin of programmable pulse generator PPG 6.

General-purpose input/output ports.

Waveform output pin of programmable pulse generator PPG 7.

General-purpose input/output ports.

Serial data input of LIN-USART 8.

General-purpose input/output ports.

Serial data output of LIN-USART 8.

General-purpose input/output ports.

Clock input/output of LIN-USART 8.

Watchdog reset output, L Active.

General-purpose input/output ports.

Analog input ch.0 for A/D converter.

(Continued)

Document Number: 002-04615 Rev. *A

Page 12 of 128

�MB91460M Series

Pin no.

131

132

133

134

135

136

137

138

139

140

141

145

146

Pin name

P29_1

AN1

P29_2

AN2

P29_3

AN3

P29_4

AN4

P29_5

AN5

P29_6

AN6

P29_7

AN7

P28_0

AN8

P28_1

AN9

P28_2

AN10

P28_3

AN11

P40_6

SDA7

P40_7

SCL7

I/O

I/O circuit

type*

I/O

F

I/O

F

I/O

F

I/O

F

I/O

F

I/O

F

I/O

F

I/O

F

I/O

F

I/O

F

I/O

F

I/O

C

I/O

C

P22_4

147

SDA0

149

P22_5

SCL0

P24_0

INT0

General-purpose input/output ports.

Analog input ch.1 for A/D converter.

General-purpose input/output ports.

Analog input ch.2 for A/D converter.

General-purpose input/output ports.

Analog input ch.3 for A/D converter.

General-purpose input/output ports.

Analog input ch.4 for A/D converter.

General-purpose input/output ports.

Analog input ch.5 for A/D converter.

General-purpose input/output ports.

Analog input ch.6 for A/D converter.

General-purpose input/output ports.

Analog input ch.7 for A/D converter.

General-purpose input/output ports.

Analog input ch.8 for A/D converter.

General-purpose input/output ports.

Analog input ch.9 for A/D converter.

General-purpose input/output ports.

Analog input ch.10 for A/D converter.

General-purpose input/output ports.

Analog input ch.11 for A/D converter.

General-purpose input/output ports.

Serial data input/output pin of I2C 7.

General-purpose input/output ports.

Serial clock input/output pin of I2C 7.

General-purpose input/output ports.

I/O

C

INT14

148

Function

Serial data input/output pin of I2C 0.

Request input pin of external interrupt ch.14. Exclusive from P22_1.

I/O

C

I/O

D

General-purpose input/output ports.

Serial clock input/output pin of I2C 0.

General-purpose input/output ports.

Request input pin of external interrupt ch.0.

(Continued)

Document Number: 002-04615 Rev. *A

Page 13 of 128

�MB91460M Series

Pin no.

150

Pin name

P24_1

INT1

I/O

I/O circuit

type*

I/O

D

P23_0

151

RX0

P23_1

TX0

I/O

D

RX1

I/O

D

P23_3

TX1

Reception input pin of CAN 0.

General-purpose input/output ports.

Transmission output pin of CAN 0.

General-purpose input/output ports.

I/O

D

INT9

154

Request input pin of external interrupt ch.1.

Request input pin of external interrupt ch.8.

P23_2

153

General-purpose input/output ports.

General-purpose input/output ports.

INT8

152

Function

Reception input pin of CAN 1.

Request input pin of external interrupt ch.9.

I/O

D

General-purpose input/output ports.

Transmission output pin of CAN 1.

155

MD4

I

A

Mode pin 4

156

MD3

I

A

Mode pin 3

157

MD2

I

K

Mode pin 2

158

MD1

I

K

Mode pin 1

159

MD0

I

K

Mode pin 0

160

INITX

I

B

MCU reset input pin, L active doesn't change.

161

TRSTX

I

E

Tool reset input pin, L active doesn't change.

I/O

D

I/O

D

164

165

P21_0

SIN0

P21_1

SOT0

P21_2

166

SCK0

167

168

SIN1

P21_5

SOT1

I/O

D

SCK1

I/O

D

I/O

D

P20_0

SIN2

Serial data output pin of LIN-USART 0.

Clock input/output pin of LIN-USART 0.

General-purpose input/output ports.

Serial data input pin of LIN-USART 1 .

General-purpose input/output ports.

Serial data output pin of LIN-USART 1.

General-purpose input/output ports.

I/O

D

FRCK1

170

General-purpose input/output ports.

Clock input pin of Free-run timer FRT0.

P21_6

169

Serial data input pin of LIN-USART 0.

General-purpose input/output ports.

FRCK0

P21_4

General-purpose input/output ports.

Clock input/output pin of LIN-USART 1.

Clock input pin of Free-run timer FRT1.

I/O

D

General-purpose input/output ports.

Serial data input pin of LIN-USART 2 .

(Continued)

Document Number: 002-04615 Rev. *A

Page 14 of 128

�MB91460M Series

Pin no.

171

Pin name

P20_1

SOT2

I/O

I/O circuit

type*

I/O

D

P20_2

172

SCK2

174

P20_4

SIN3

P20_5

SOT3

I/O

D

SCK3

I/O

D

I/O

D

179

180

181

182

183

184

185

186

P19_0

SIN4

P19_1

SOT4

P19_2

SCK4

P19_4

SIN5

P19_5

SOT5

P19_6

SCK5

P18_0

SIN6

P18_1

SOT6

P18_2

SCK6

I/O

D

OCU0

General-purpose input/output ports.

Serial data input pin of LIN-USART 3 .

General-purpose input/output ports.

Serial data output pin of LIN-USART 3.

Clock input/output pin of LIN-USART 3.

Clock input pin of Free-run timer FRT3.

I/O

D

I/O

D

I/O

D

I/O

D

I/O

D

I/O

D

I/O

D

I/O

D

I/O

D

P15_0

187

Clock input/output pin of LIN-USART 2.

General-purpose input/output ports.

FRCK3

178

Serial data output pin of LIN-USART 2.

Clock input pin of Free-run timer FRT2.

P20_6

175

General-purpose input/output ports.

General-purpose input/output ports.

FRCK2

173

Function

General-purpose input/output ports.

Serial data input pin of LIN-USART 4 .

General-purpose input/output ports.

Serial data output pin of LIN-USART 4.

General-purpose input/output ports.

Clock input/output pin of LIN-USART 4.

General-purpose input/output ports.

Serial data input pin of LIN-USART 5 .

General-purpose input/output ports.

Serial data output pin of LIN-USART 5.

General-purpose input/output ports.

Clock input/output pin of LIN-USART 5.

General-purpose input/output ports.

Serial data input pin of LIN-USART 6 .

General-purpose input/output ports.

Serial data output pin of LIN-USART 6.

General-purpose input/output ports.

Clock input/output pin of LIN-USART 6.

General-purpose input/output ports.

I/O

TOT0

D

Waveform output pin of output compare OCU 0.

Output pin of reload timer RLT 0.

(Continued)

Document Number: 002-04615 Rev. *A

Page 15 of 128

�MB91460M Series

Pin no.

Pin name

I/O

I/O circuit

type*

P15_1

188

189

190

OCU1

General-purpose input/output ports.

I/O

D

Output pin of reload timer RLT 1.

P15_2

General-purpose input/output ports.

OCU2

I/O

D

TOT2

Output pin of reload timer RLT 2.

General-purpose input/output ports.

OCU3

I/O

D

INT6

196

197

198

199

200

201

202

203

204

Waveform output pin of output compare OCU 3.

Output pin of reload timer RLT 3.

General-purpose input/output ports.

I/O

D

Request input pin of external interrupt ch.6.

SDA3

Serial data input/output pin of I2C 3.

P24_7

General-purpose input/output ports.

INT7

I/O

D

P40_0

SDA4

P40_1

SCL4

P40_2

SDA5

P40_3

SCL5

P40_4

SDA6

P40_5

SCL6

P23_4

INT10

P23_6

INT11

P22_0

INT12

P22_1

INT14

Request input pin of external interrupt ch.7.

Serial clock input/output pin of I2C 3.

SCL3

195

Waveform output pin of output compare OCU 2.

P15_3

P24_6

194

Waveform output pin of output compare OCU 1.

TOT1

TOT3

193

Function

I/O

C

I/O

C

I/O

C

I/O

C

I/O

C

I/O

C

I/O

D

I/O

D

I/O

D

I/O

D

General-purpose input/output ports.

Serial data input/output pin of I2C 4.

General-purpose input/output ports.

Serial clock input/output pin of I2C 4.

General-purpose input/output ports.

Serial data input/output pin of I2C 5.

General-purpose input/output ports.

Serial clock input/output pin of I2C 5.

General-purpose input/output ports.

Serial data input/output pin of I2C 6.

General-purpose input/output ports.

Serial clock input/output pin of I2C 6.

General-purpose input/output ports.

Request input pin of external interrupt ch.10.

General-purpose input/output ports.

Request input pin of external interrupt ch.11.

General-purpose input/output ports.

Request input pin of external interrupt ch.12.

General-purpose input/output ports.

Request input pin of external interrupt ch.14. Exclusive from P22_4.

(Continued)

Document Number: 002-04615 Rev. *A

Page 16 of 128

�MB91460M Series

(Continued)

Pin no.

205

206

Pin name

P22_2

INT13

P22_3

INT15

I/O

I/O circuit

type*

I/O

D

I/O

D

P14_0

207

208

209

210

ICU0

TIN0

212

213

214

215

General-purpose input/output ports.

Request input pin of external interrupt ch.13.

General-purpose input/output ports.

Request input pin of external interrupt ch.15. Exclusive from P22_6.

General-purpose input/output ports.

I/O

D

Data sample input pin of Input capture ICU 0.

Event input pin of reload timer RLT 0.

TRG0

Event input pin of programmable pulse generator PPG 0.

P14_1

General-purpose input/output ports.

ICU1

TIN1

I/O

D

Data sample input pin of Input capture ICU 1.

Event input pin of reload timer RLT 1.

TRG1

Event input pin of programmable pulse generator PPG 1.

P14_2

General-purpose input/output ports.

ICU2

TIN2

I/O

D

Data sample input pin of input capture ICU 2.

Event input pin of reload timer RLT 2.

TRG2

Event input pin of programmable pulse generator PPG 2.

P14_3

General-purpose input/output ports.

ICU3

TIN3

I/O

D

TRG3

211

Function

P17_0

PPG0

P17_1

PPG1

P17_2

PPG2

P17_3

PPG3

P24_2

INT2

Data sample input pin of input capture ICU 3.

Event input pin of reload timer RLT 3.

Event input pin of programmable pulse generator PPG 3.

I/O

D

I/O

D

I/O

D

I/O

D

I/O

D

General-purpose input/output ports.

Waveform output pin of programmable pulse generator PPG 0.

General-purpose input/output ports.

Waveform output pin of programmable pulse generator PPG 1.

General-purpose input/output ports.

Waveform output pin of programmable pulse generator PPG 2.

General-purpose input/output ports.

Waveform output pin of programmable pulse generator PPG 3.

General-purpose input/output ports.

Request input pin of external interrupt ch.2.

* : For information about the I/O circuit type, refer to “4. I/O Circuit Types”.

Document Number: 002-04615 Rev. *A

Page 17 of 128

�MB91460M Series

[Power supply/Ground pins]

Pin no.

Pin name

1, 21, 48, 51, 55, 73, 91,

108, 129, 162, 176, 191

VSS

20, 45, 46, 54, 72, 90,

109

VCC3

Power supply pins for external data bus and internal regulator.

163, 177, 192, 216

VCC5

Power supply pins

143

AVCC3

142

AVSS/AVRL

144

AVRH

Reference power supply pin for A/D converter

47

C_1

Capacitor connection pin for internal regulator.

22

C_2

Capacitor connection pin for internal regulator.

Document Number: 002-04615 Rev. *A

I/O

Function

Ground pins

Supply

Power supply pin for A/D converter

Analog ground pin, reference power supply pin for

A/D converter.

Page 18 of 128

�MB91460M Series

4. I/O Circuit Types

Type

Circuit

5.0 V

Remarks

Input

• 5.0 V CMOS level hysteresis input

• With Pull-down

A

N-ch

B

• 5.0 V CMOS level hysteresis input

• With Pull-up

P-ch

5.0 V

Input

Pull-up control

P-ch

5.0 V

C

P-ch

Output drive P-ch

N-ch

Output drive N-ch

N-ch

Pull- down control

CMOS level input

• 5.0 V CMOS level output

IOL = 3 mA, IOH = − 3 mA

• 5.0 V CMOS level input

• 5.0 V CMOS level hysteresis input

• 5.0 V Automotive level input

With standby control

With Pull-up/down control

• Pseudo open drain when using I2C

Standby control

CMOS level hysteresis

input

Standby control

Automotive level input

Standby control

(Continued)

Document Number: 002-04615 Rev. *A

Page 19 of 128

�MB91460M Series

Type

Circuit

Remarks

Pull-up control

P-ch

5.0 V

D

P-ch

Output drive P-ch

N-ch

Output drive N-ch

N-ch

Pull- down control

• 5.0 V CMOS level output

IOL = 4 mA, IOH = − 4 mA

• 5.0 V CMOS level input

• 5.0 V CMOS level hysteresis input

• 5.0 V Automotive level input

With standby control

With Pull-up/down control

CMOS level input

Standby control

CMOS level Hysteresis

input

Standby control

Automotive level input

Standby control

E

P-ch

Pull-up control

5.0 V

3.3 V CMOS level hysteresis input

Withstand voltage 5 V

5.0 V pull-up function (When DSU4 is unused)

Input

(Continued)

Document Number: 002-04615 Rev. *A

Page 20 of 128

�MB91460M Series

Type

Circuit

Remarks

Pull-up control

P-ch

3.3 V

P-ch

Output drive P-ch

N-ch

Output drive N-ch

F

N-ch

Pull- down control

• 3.3 V CMOS level output

IOL = 4 mA, IOH = − 4 mA

• 3.3 V CMOS level input

• 3.3 V CMOS level hysteresis input

With standby control

• Analog input for A/D converter

CMOS level input

Standby control

CMOS level

hysteresis input

Standby control

Analog input

3.3 V

Input

3.3 V Oscillation cell

Feedback resistor 1 MΩ

With standby control

G

Standby control

(Continued)

Document Number: 002-04615 Rev. *A

Page 21 of 128

�MB91460M Series

Type

Circuit

Remarks

Pull-up control

P-ch

3.3 V

P-ch

Output drive P-ch

N-ch

Output drive N-ch

H

Pull- down control

N-ch

• 3.3 V CMOS level output

IOL = 4 mA, IOH = − 4 mA

• 3.3 V CMOS level input

• 3.3 V CMOS level hysteresis input

With standby control

With Pull-up/down control

CMOS level input

Standby control

CMOS level

hysteresis input

Standby control

3.3 V

P-ch

N-ch

I

Output drive P-ch

Output drive N-ch

• 3.3 V CMOS level output

IOL = 8 mA, IOH = − 8 mA

• 3.3 V CMOS level hysteresis input

With standby control

CMOS level

hysteresis input

Standby control

3.3 V

J

P-ch

N-ch

Document Number: 002-04615 Rev. *A

Output drive P-ch

3.3 V CMOS level output

IOL = 4 mA, IOH = − 4 mA

Output drive N-ch

Page 22 of 128

�MB91460M Series

Type

K

Circuit

5.0 V

Input

Remarks

5.0 V CMOS level hysteresis input

Pull-up control

P-ch

3.3 V

L

P-ch

Output drive P-ch

N-ch

Output drive N-ch

N-ch

Pull- down control

• 3.3 V CMOS level output

IOL = 6 mA, IOH = − 6 mA

• 3.3 V CMOS level input

• 3.3 V CMOS level hysteresis input

• 3.3 V MediaLB level hysteresis input

With standby control

With Pull-up/down control

CMOS level input

Standby control

CMOS level

hysteresis input

Standby control

Dedicated MediaLB input

Standby control

Document Number: 002-04615 Rev. *A

Page 23 of 128

�MB91460M Series

5. Handling Devices

Preventing Latch-up

Latch-up may occur in a CMOS IC if a voltage higher than VCC or less than VSS is applied to an input or output pin or if a voltage

exceeding the rating is applied between VCC and VSS pins.

If latch-up occurs, the power supply current increases rapidly, sometimes resulting in thermal breakdown of the device. Therefore, be

very careful not to apply voltages in excess of the absolute maximum ratings.

Handling of unused input pins

If unused input pins are left open, abnormal operation may result. Any unused input pins should be connected to pull-up or pull-down

resistor (2 KΩ or more) or enable internal pull up or pull down resistors before setting the global port enable bit.

Unused input and output pins need to leave open at the output state, or treat the same as for the input pin when they are at the input

state.

Power supply pins

The MB91460M series has multiple of VCC and VSS pins.

The device is designed such that pins necessary to be at the same potential are interconnected internally to prevent malfunctions

such as latch-up. However, all of these pins must be connected externally to the power supply or ground in order to minimize undesired

electromagnetic radiation, prevent strobe signal malfunctions due to the rise in ground level, and conform to the total output current

rating.

Moreover, connect the current supply source with the VCC and VSS pins of this device at the low impedance.

It is also recommended that a ceramic capacitor of around 0.1 μF be connected as a bypass capacitor between the VCC and VSS

pins at a location close to the device.

This series has a built-in regulator. Connect a bypass capacitor of 4.7 μF to C_1 and C_2 pins for the regulator.

Crystal oscillator circuit

Noise in proximity to the X0 (X0A) and X1 (X1A) pins can cause the device to operate abnormally. Printed circuit boards should be

designed so that the X0 (X0A) and X1 (X1A) pins, and crystal oscillator (or ceramic oscillator), as well as bypass capacitors connected

to ground, are placed as close together as possible. When the signal wires for transmitting from X0 and X1 pins are pulled along, use

the circuit with them shielded on board. Be careful especially when a pin next to X0 pin is used.

It is recommended that the printed circuit board layout be designed such that the X0 and X1 pins or X0A and X1A pins are surrounded

by ground plane for the stable operation. Sub clock is also needed when dual clock product is used as single clock product.

Please request the oscillator manufacturer to evaluate the oscillational characteristics of the crystal and this device.

Treatment of NC and OPEN pins

Pins marked as NC and OPEN must be left open-circuit.

Mode pins (MD0 to MD4)

These pins should be connected directly to Vcc or Vss. To prevent the device from entering test mode accidentally due to noise,

minimize the lengths of the patterns between each mode pin and Vcc or Vss on the printed circuit board as possible and connect them

with low impedance.

Especially, MD3 must be directly connected to Vss with 0 Ω.

Operation at Start-up

Be sure to execute the setting initialized reset (INIT) with INITX pin immediately after start-up.

Hold the “L” level input to the INITX pin during the stabilization wait time immediately after the power on to ensure the stabilization

wait time as required by the oscillator circuit (the stabilization wait time is initialized to the minimum value when INIT is asserted to

reset using the INITX pin).

Note on oscillator input at power-on

At power-on, ensure that the clock is input until the oscillator stabilization wait time has elapsed.

Notes on operating in PLL clock mode

If the oscillator is disconnected or the clock input stops when the PLL clock is selected, the microcontroller may continue to operate

at the free-running frequency of the self-oscillating circuit of the PLL. However, this self-running operation cannot be guaranteed.

Document Number: 002-04615 Rev. *A

Page 24 of 128

�MB91460M Series

Notes on using external clock

When using an external clock, simultaneously supply the clock signal to the X1 (X1A) pin and a clock signal with the reverse phase

to X0(X0A).

However, the external clock must not be used while the microcontroller is in stop mode (oscillator stop mode). The X1 pin outputs the

H level and stops in STOP mode.

Setting external bus

This model guarantees the maximum frequency of 40 MHz for the external clock operation.

Setting the base clock frequency to the maximum operation frequency without changing the initial value of DIVR1 (external bus base

clock division setting register) sets the external bus frequency that is not guaranteed.

Before changing the base clock frequency, set SYSCLK not to exceed the maximum guaranteed frequency.

The AC ratings cannot be guaranteed if a pull-up resistor is connected to the pin serving as an external bus pin.

Clock control

Input the “L” signal to INIT to assure the clock oscillation stabilization wait time.

Immediately after power-on or when returning from shutdown by INITX input, keep the "L" level input to the INITX pin for oscillation

stabilization wait time (8ms) in order to secure stabilization wait for the built-in regulator or oscillation stabilization wait time for the

oscillation circuit.

Switching multiplexed ports

Use PFR (port function register) to switch between the use as a PORT and the multiplexed port.

Low power consumption mode

■

For the standby mode, enable the synchronous standby mode (TBCR.SYNCS="1") to use and be sure to follow the sequence below.

LDI

#value_of_standby, R0

;

value_of_standby is write data of STCR.

LDI

#_STCR, R12

;

_STCR is address (481H) of STCR.

STB

R0, @R12

;

Write to standby control register (STCR)

LDUB

@12, R0

;

Read STCR for synchronous standby

LDUB

@12, R0

;

Dummy re-read of STCR

NOP

;

NOP x 5 for arrangement of timing

NOP

NOP

NOP

NOP

In addition, set I flag, ILM and ICR to diverge to the interruption handler which triggers the return after returning to the standby mode.

■

Do not do the following when the monitor debugger is used.

• Break point setting for the above instruction lines

• Step execution for above instruction lines

Power-on sequence for dual-power-supply model

Notes on the power-on and power-off sequences

Power-on sequence : (1) VCC5 (2) VCC3 (3) AVRH, AVCC

Power-off sequence : (1) AVRH, AVCC (2) VCC3 (3) VCC5

Follow the above sequence.

Turn on VCC3 before applying power supply to the analog power supply AVCC3 and AVRH, or the analog signal.

AVRH must not exceed voltage of AVCC3.

Multiplexed pin for analog input

Input voltage must not exceed AVCC3 when the multiplexed pin serving for the analog input is used as a general-purpose port.

Recommended operating condition

VCC3 = AVCC3 = AVRH : Recommended condition

Document Number: 002-04615 Rev. *A

Page 25 of 128

�MB91460M Series

Notes on PS register

As the PS register is processed in advance by some instructions, when the debugger is being used, the exception handling described

below may result in execution breaking in an interrupt handling routine or the displayed values of the flags in the PS register being

updated.

As the microcontroller is designed to carry out reprocessing correctly upon returning from such an EIT event, the operation before

and after the EIT always proceeds according to specification.

■

The following behavior may occur if any of the following occurs in the instruction immediately after a DIV0U/DIV0S instruction:

• a user interrupt is accepted;

• single-step execution is performed;

• or execution breaks due to a data event or from the emulator menu.

1. D0 and D1 flags are updated in advance.

2. An EIT handling routine (user interrupt or emulator) is executed.

3. Upon returning from the EIT, the DIV0U/DIV0S instruction is executed and the D0 and D1 flags are updated to the same values

as those in 1).

■

The following behavior occurs when an ORCCR, STILM, MOV Ri or PS instruction is executed to enable a user interrupt while that

interrupt is in the active state.

4. The PS register is updated in advance.

5. An EIT handling routine (user interrupt) is executed.

6. Upon returning from the EIT, the above instructions are executed and the PS register is updated to the same value as in 4.

Watchdog timer

The watchdog timer built in this model monitors a program and resets the CPU if the reset defer function is not executed within a

certain period of time or the program runs out of control. Once the function of the watchdog timer is enabled, the watchdog timer keeps

on operating program until it resets the CPU.

As an exception, the watchdog timer defers a reset automatically under the condition in which the CPU stops executing the program.

For those conditions to which this exception applies, see “Chapter 20 Watch dog timer in Hardware manual”.

Frequency fluctuation

This chip which contains PLL can switch divide-by-two external clock to PLL output fast clock. The clock gear function which is built

in this model prevents consumption power from increasing rapidly at this time.

Serial communication

There is a possibility to receive wrong data due to noise or other causes on the serial communication. Therefore, design a printed

circuit board so as to avoid noise.

Consider receiving of wrong data when designing the system. For example, apply a checksum to detect an error. If an error is detected,

retransmit the data.

Write to registers which include a status flag (1)

Be careful not to accidentally clear a status flag, when writing into registers which include a status flag (especially the interrupt request

flag).

Take notice that a flag of a status bit is not cleared and the control bit is set to the expected value at writing.

When overwriting the control bit structured by multiple bits simultaneously, it is not possible to use the bit manipulation instruction. As

a result, it is necessary to access data with usual byte/half word/word when writing to both a control bit and a status flag simultaneously.

At this time, be careful not to accidentally clear other bits (bits in a status flag).

Almost all registers shown below include multiple control bits and status flags.

• TBCR

• OSCR

• TCCS0, TCCS1

• ICS01

• TMCSR0, TMCSR1, TMCSR2, TMCSR3

• PCN0, PCN1, PCN2, PCN3, PCN4, PCN5

• ADCSL0, ADCSL1

Note: It is not necessary to take special care when overwriting a single bit by the bit manipulation instruction.

Document Number: 002-04615 Rev. *A

Page 26 of 128

�MB91460M Series

Write to registers which include a status flag (2)

Take notice that actual access will be delayed when writing into registers which include a status flag (especially the interrupt request

flag).

This is because data is written via multiple busses.

For example, when the program exits the interrupt routine after clearing the interrupt request flag, the interrupt flag may be cleared

after accepting the RETI instructions. In this case, the interrupts may be accepted again because some of the interrupt requests are

left at the time of returning from the interrupt routine.

To adjust any discord between this register address and instruction execution, read synchronous registers (RBSYNC, CBSYNC0/1,

and MBSYNC) along with the area where written registers exist.

Adjustment at every writing makes a bus data band width narrow. Therefore, we recommend to adjust only if necessary. For example,

when continuous writing is executed, adjustment at the last writing will be enough.

The table below shows the correspondence between a target area and a synchronous register.

Register name

Target area

RBSYNC

0x0000-0x01FF, 0x0280-0x037D, 0x0400-0x063F, 0x0C00-0x0FFF (Peripheral function on R-bus)

CBSYNC0/1

MBSYNC

0xC000-0xFFFF (CAN on D-bus)

0x6000-0x6FFF (MediaLB, I2S and FIFO buffer on F-bus)

Document Number: 002-04615 Rev. *A

Page 27 of 128

�MB91460M Series

6. Notes On Debugger

Execution of the RETI Command

If an interrupt occurs frequently during step execution, the corresponding interrupt handling routine is executed repeatedly after step

execution. As the result of that, the main routine and low-interrupt-level programs will not be executed.

Do not perform the step execution of RETI instruction to prevent this issue.

Disable the corresponding interrupt and execute debugger when the corresponding interrupt routine no longer needs debugging.

Operand break

Do not set the access to the areas containing the address of system stack pointer as a target of data event break.

Flash security

DSU4 will not be available due to security issues when Flash security is used.

Shutdown mode

It is impossible to execute debugger in the shutdown mode.

Document Number: 002-04615 Rev. *A

Page 28 of 128

�MB91460M Series

7. Block Diagram

MB91F467MA

TRSTX

BREAK

ICS0 to ICS2

ICD0 to ICD3

FR60 CPU

DSU

EDSU/MPU

core

Bit search

32

I-bus

Direct Mapped

Cachannelse

8 Kbytes

D-bus

32

RAM 48 Kbytes

16 Kbytes (0wait)

32 Kbytes (1wait)

RX0/RX1

TX0/TX1

I - Cache

SYSCLK

ASX

RDX

WR0X

WR1X

32 to 16

4 Kbytes

Flash

CAN 2channels

32msg+64msg

BUS adaptor

1 Mbyte

RAM

External BUS I/F

BUS

16 Kbytes

BOOT ROM

4 Kbytes

F-bus

convertor

32

32

32

MediaLB

R-bus

DREQ0

DACKX0

DEOP0

IOWRX

IORDX

DMAC

5 channels

MediaLB

HB-bus

Interrupt

Controller

32

HB

decoder

PB-bus

32

TRQ0 to TRQ3

PPG0 to PPG7

PPG

8 channels

TIN0 to TIN3

TOT0 to TOT3

Reload Timer

5 channels

FRCK0 to FRCK3

FIFO buffer

WS0

SCK0

SD0 to SD9

BRQ

BGRNTX

CS0X to CS6X

A23 to A00

BUS I/F

MLBCLK

MLBSIG

MLBDAT

MCLKE

MCLKI

MCLKO

WEX

BAAX

ICU0 to ICU3

I2S 10 channels

Free Run Timer

4 channels

Input Capture

4 channels

D31 to D16

16

A/D Convertor

12 channels

AN0 to AN11

ATGX

External Interrupt

16 channels

INT0 to INT15

General Purpose

Port

GPxx_x

LIN-USART

9 channels

SIN0 to SIN8

SOT0 to SOT8

SCK0 to SCK8

I2C

8 channels

SDA0 to SDA7

SCL0 to SCL7

Real Time Clock

OCU0 to OCU3

Output Compare

4 channels

Clock Controller

X0

Clock Controller

for MediaLB

Document Number: 002-04615 Rev. *A

Page 29 of 128

�MB91460M Series

■ CPU and Control Unit

The FR family CPU is a high performance core that is designed based on the RISC architecture with advanced instructions for

embedded applications.

7.1 Features

• Adoption of RISC architecture

Basic instruction: 1 instruction per cycle

• General-purpose registers: 32-bit × 16 registers

• 4 Gbytes linear memory space

• Multiplier installed

32-bit × 32-bit multiplication: 5 cycles

16-bit × 16-bit multiplication: 3 cycles

• Enhanced interrupt processing function

Quick response speed (6 cycles)

Multiple-interrupt support

Level mask function (16 levels)

• Enhanced instructions for I/O operation

Memory-to-memory transfer instruction

Bit processing instruction

Basic instruction word length: 16 bits

• Low-power consumption

Sleep mode/stop mode

7.2 Internal architecture

• The FR family CPU uses the Harvard architecture in which the instruction bus and data bus are independent of each other.

• A 32-bit 16-bit buffer is connected to the 32-bit bus (D-bus) to provide an interface between the CPU and peripheral resources.

• A Harvard Princeton bus converter is connected to both the I-bus and D-bus to provide an interface between the CPU and

the bus controller.

Document Number: 002-04615 Rev. *A

Page 30 of 128

�MB91460M Series

7.3 Programming model

7.3.1 Basic programming model

32 bits

Initial value

R0

XXXX XXXXH

R1

...

General-purpose registers

...

...

...

...

...

...

...

R12

R13

AC

...

R14

FP

XXXX XXXXH

R15

SP

0000 0000H

Program counter

PC

Program status

RS

Table base register

TBR

Return pointer

RP

System stack pointer

SSP

User stack pointer

USP

Multiply & divide registers

MDH

ILM

SCR

CCR

MDL

Document Number: 002-04615 Rev. *A

Page 31 of 128

�MB91460M Series

7.4 Registers

7.4.1 General-purpose register

32 bits

Initial value

R0

XXXX XXXXH

R1

...

...

...

...

...

...

...

...

R12

R13

AC

...

R14

FP

XXXX XXXXH

R15

SP

0000 0000H

Registers R0 to R15 are general-purpose registers. These registers can be used as accumulators for computation operations and as

pointers for memory access.

Of the 16 registers, enhanced commands are provided for the following registers to enable their use for particular applications.

R13 : Virtual accumulator

R14 : Frame pointer

R15 : Stack pointer

Initial values at reset are undefined for R0 to R14. The value for R15 is 00000000H (SSP value).

7.4.2 PS (Program Status)

This register holds the program status, and is divided into three parts, ILM, SCR, and CCR.

All undefined bits (-) in the diagram are reserved bits. The read values are always “0”. Write access to these bits is invalid.

Bit position → bit 31

bit 20

bit 16

ILM

Document Number: 002-04615 Rev. *A

bit 10 bit 8 bit 7

SCR

bit 0

CCR

Page 32 of 128

�MB91460M Series

7.4.3 CCR (Condition Code Register)

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

SV

S

I

N

Z

V

C

Initial value

- 000XXXXB

SV : Supervisor flag

S : Stack flag

I

: Interrupt enable flag

N : Negative enable flag

Z

: Zero flag

V : Overflow flag

C : Carry flag

7.4.4 SCR (System Condition Register)

bit 10 bit 9

D1

D0

bit 8

T

Initial value

XX0B

Flag for step division (D1, D0)

This flag stores interim data during execution of step division.

Step trace trap flag (T)

This flag indicates whether the step trace trap is enabled or disabled.

The step trace trap function is used by emulators. When an emulator is in use, it cannot be used in execution of user programs.

7.4.5 ILM (Interrupt Level Mask register)

bit 20 bit 19 bit 18 bit 17 bit 16

Initial value

ILM4 ILM3 ILM2 ILM1 ILM0

01111B

This register stores interrupt level mask values, and the values stored in ILM4 to ILM0 are used for level masking.

The register is initialized to value “01111B” at reset.

7.4.6 PC (Program Counter)

bit 31

bit 0

Initial value

XXXXXXXXH

The program counter indicates the address of the instruction that is being executed.

The initial value at reset is undefined.

Document Number: 002-04615 Rev. *A

Page 33 of 128

�MB91460M Series

7.4.7 TBR (Table Base Register)

bit 31

bit 0

Initial value

000FFC00H

The table base register stores the starting address of the vector table used in EIT processing.

The initial value at reset is 000FFC00H.

7.4.8 RP (Return Pointer)

bit 31

bit 0

Initial value

XXXXXXXXH

The return pointer stores the address for return from subroutines.

During execution of a CALL instruction, the PC value is transferred to this RP register.

During execution of a RET instruction, the contents of the RP register are transferred to PC.

The initial value at reset is undefined.

7.4.9 USP (User Stack Pointer)

bit 31

bit 0

Initial value

XXXXXXXXH

The user stack pointer, when the S flag is “1”, this register functions as the R15 register.

• The USP register can also be explicitly specified.

The initial value at reset is undefined.

• This register cannot be used with RETI instructions.

7.4.10 Multiply & divide registers

bit 31

MDH

MDL

bit 0

Initial value

XXXXXXXXH

XXXXXXXXH

These registers are for multiplication and division, and are 32 bits each in length.

The initial value at reset is undefined.

Document Number: 002-04615 Rev. *A

Page 34 of 128

�MB91460M Series

8. Embedded Program/Data Memory (Flash)

8.1 Flash features

•

•

•

•

MB91F467MA: 1088 Kbytes (16 × 64 Kbytes + 8 × 8 Kbytes = 8.7 Mbits)

Programmable wait state for read/write access

Flash and Boot security with security vector at 0014:8000H to 0014:800FH

Basic specification: Same as MBM29LV400TC (except size and part of sector configuration)

8.2 Operation modes

1. 64-bit CPU mode

• CPU reads and executes programs in word (32-bit) length units.

• Flash writing is not possible.

• Actual Flash Memory access is performed in d-word (64-bit) length units.

2. 32-bit CPU mode :

• Actual Flash Memory access is performed in word (32-bit) length units.

3. 16-bit CPU mode :

• CPU reads and writes in half-word (16-bit) length units.

• Program execution from the Flash is not possible.

• Actual Flash Memory access is performed in half-word (16-bit) length units.

Document Number: 002-04615 Rev. *A

Page 35 of 128

�MB91460M Series

8.3 Flash access in CPU mode

8.3.1 Flash configuration

Flash memory map MB91F467MA

Address

0014:FFFFH

0014:C000H

SA6 (8kB)

SA7 (8kB)

0014:BFFFH

0014:8000H

SA4 (8kB)

SA5 (8kB)

0014:7FFFH

0014:4000H

SA2 (8kB)

SA3 (8kB)

0014:3FFFH

0014:0000H

SA0 (8kB)

SA1 (8kB)

0013:FFFFH

0012:0000H

SA22 (64kB)

SA23 (64kB)

0011:FFFFH

0010:0000H

SA20 (64kB)

SA21 (64kB)

000F:FFFFH

000E:0000H

SA18 (64kB)

SA19 (64kB)

ROMS5

000D:FFFFH

000C:0000H

SA16 (64kB)

SA17 (64kB)

ROMS4

000B:FFFFH

000A:0000H

SA14 (64kB)

SA15 (64kB)

ROMS3

0009:FFFFH

0008:0000H

SA12 (64kB)

SA13 (64kB)

ROMS2

0007:FFFFH

0006:0000H

SA10 (64kB)

SA11 (64kB)

ROMS1

0005:FFFFH

0004:0000H

SA8 (64kB)

SA9 (64kB)

ROMS0

ROMS7

ROMS6

addr+0

16bit read/write

addr+1

addr+2

dat[31:16]

32bit read/write

64bit read

Document Number: 002-04615 Rev. *A

addr+3

addr+4

dat[15:0]

addr+5

addr+6

dat[31:16]

dat[31:0]

addr+7

dat[15:0]

dat[31:0]

dat[63:0]

Page 36 of 128

�MB91460M Series

8.3.2 Flash access timing settings in CPU mode

The following tables list all settings for a given maximum Core Frequency (through the setting of CLKB or maximum clock modulation)

for Flash read and write access.

Flash read timing settings (synchronous read)

Core clock (CLKB)

ATD

ALEH

EQ

WEXH

WTC

to 24 MHz

0

0

0

-

1

to 48 MHz

0

0

1

-

2

to 80 MHz

1

1

3

-

4

Remark

Flash write timing settings (synchronous write)

Core clock (CLKB)

ATD

ALEH

EQ

WEXH

WTC

to 32 MHz

1

-

-

0

4

to 48 MHz

1

-

-

0

5