Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as “Cypress” document as this is the

company that originally developed the product. Please note that Infineon will continue

to offer the product to new and existing customers as part of the Infineon product

portfolio.

Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product

portfolio does not lead to any changes to this document. Future revisions will occur

when appropriate, and any changes will be set out on the document history page.

Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the

ordering part numbers listed in the datasheet for ordering.

www.infineon.com

�CY91F469GA/CY91F469GB

FR60 CY91460G Series

32-bit Microcontroller Datasheet

FR60 CY91460G Series 32-bit Microcontroller Datasheet

CY91460G series is a line of general-purpose 32-bit RISC microcontrollers designed for embedded control applications which

require high-speed real-time processing, such as consumer devices and on-board vehicle systems. This series uses the FR60 CPU,

which is compatible with the FR family of CPUs.

This series contains the LIN-USART and CAN controllers.

Features

FR60 CPU Core

■

32-bit RISC, load/store architecture, five-stage pipeline

■

16-bit fixed-length instructions (basic instructions)

■

Instruction execution speed: 1 instruction per cycle

■

Instructions including memory-to-memory transfer, bit manipulation, and barrel shift instructions: Instructions suitable for

embedded applications

■

Function entry/exit instructions and register data multi-load

store instructions: Instructions supporting C language

■

Register interlock function: Facilitating assembly-language

coding

■

Built-in multiplier with instruction-level support

Signed 32-bit multiplication: 5 cycles

Signed 16-bit multiplication: 3 cycles

■

Interrupts (save PC/PS): 6 cycles (16 priority levels)

■

Harvard architecture enabling program access and data

access to be performed simultaneously

■

Instructions compatible with the FR family

Internal Peripheral Resources

■

General-purpose ports : Maximum 205 ports

■

I2C bus interface (supports 400 kbps): 4 channel

■

DMAC (DMA Controller)

■

Master/slave transmission and reception

■

Arbitration function, clock synchronization function

■

CAN controller (C-CAN): 6 channels

Activation source can be selected using software

■

Maximum transfer speed: 1 Mbps

Addressing mode specifies full 32-bit addresses

(increment/decrement/fixed)

■

128 transmission/reception message buffers

■

Sound generator: 1 channelTone frequency: PWM frequency

divide-by-two (reload value + 1)

■

Alarm comparator: 2 channelsMonitor external voltage

Generate an interrupt in case of voltage lower/higher than the

defined thresholds (reference voltage)

Multi-byte transfer enabled (by software)

■

16-bit PPG timer: 16 channels

DMAC descriptor in I/O areas (200H to 240H, 1000H to 1024H)

■

16-bit PFM timer: 1 channel

■

16-bit reload timer: 8 channels

■

16-bit free-run timer: 8 channels (1 channel each for ICU and

OCU)

■

Input capture: 8 channels (operates in conjunction with the

free-run timer)

■

Output compare: 8 channels (operates in conjunction with the

free-run timer)

■

Up/Down counter: 4 channels (4*8-bit or 2*16-bit)

■

Watchdog timer

■

Real-time clock

■

Low-power consumption modes: Sleep/stop mode function

■

Low voltage detection circuit

Maximum of 5 channels able to operate simultaneously

(including 2 external channels)

3 transfer sources (external pin/internal peripheral/software)

Transfer mode (demand transfer/burst transfer/step

transfer/block transfer)

Fly-by transfer support (between external I/O and memory)

Transfer data size selectable from 8/16/32-bit

■

A/D converter (successive approximation type)

10-bit resolution: 32 channels

Conversion time: minimum 1 μs

■

External interrupt inputs : 16 channels

12 channels shared with CAN RX, I2C SDA or I2C SCL pins

■

Bit search module (for REALOS)

Function to search from the MSB (most significant bit) for the

position of the first “0”, “1”, or changed bit in a word

■

LIN-USART (full duplex double buffer): 8 channels, 4 channels

with FIFO

Clock synchronous/asynchronous selectable

Sync-break detection

Internal dedicated baud rate generator

Cypress Semiconductor Corporation

Document Number: 002-04606 Rev. *C

•

198 Champion Court

•

San Jose, CA 95134-1709

•

408-943-2600

Revised July 22, 2019

�CY91F469GA/CY91F469GB

■

Clock supervisor

Monitors the sub-clock (32 kHz) and the main clock (4 MHz) ,

and switches to a recovery clock (CR oscillator, etc.) when the

oscillations stop.

■

Main oscillator stabilization timer

Generates an interrupt in sub-clock mode after the stabilization

wait time has elapsed on the 23-bit stabilization wait time

counter

■

Clock modulator

■

■

Clock monitor

■

Sub-clock calibration

Corrects the real-time clock timer when operating with the 32

kHz or CR oscillator

Sub-oscillator stabilization timer

Generates an interrupt in main clock mode after the stabilization wait time has elapsed on the 15-bit stabilization wait time

counter

■

Power supply range 3 V to 5 V (1.8 V internal logic provided by

a step-down voltage converter)

■

Operating temperature range: between − 40°C and + 125°C

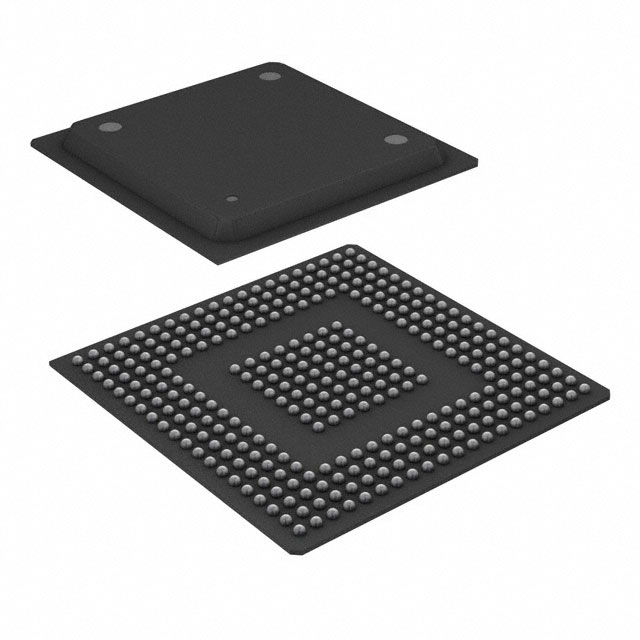

Package and Technology

■

Package: 320-pin plastic BGA (BGA-320)

■

CMOS 0.18 μm technology

Document Number: 002-04606 Rev. *C

Page 2 of 146

�CY91F469GA/CY91F469GB

Contents

1.

Product Lineup............................................................. 4

2.

2.1

Pin Assignment ............................................................ 6

CY91F469Gx ................................................................. 6

3.

3.1

3.2

Pin Description............................................................. 7

CY91F469Gx ................................................................. 7

Power Supply/Ground Pins.......................................... 21

4.

I/O Circuit Types......................................................... 22

5.

5.1

5.2

5.3

5.4

5.5

5.6

5.7

5.8

5.9

Handling Devices .......................................................

Preventing Latch-up.....................................................

Handling of Unused Input Pins ....................................

Power Supply Pins.......................................................

Crystal Oscillator Circuit...............................................

Notes on using External Clock.....................................

Mode Pins (MD_x) .......................................................

Notes on Operating in PLL Clock Mode.......................

Pull-up Control .............................................................

Notes on PS Register ..................................................

29

29

29

29

29

29

30

30

30

30

6.

6.1

6.2

6.3

Notes on Debugger....................................................

Execution of the RETI Command ................................

Break Function.............................................................

Operand Break.............................................................

31

31

31

31

7.

7.1

Block Diagram............................................................ 32

CY91F469Gx ............................................................... 32

8.

8.1

8.2

8.3

8.4

CPU and Control Unit ................................................

Features.......................................................................

Internal Architecture.....................................................

Programming Model.....................................................

Registers......................................................................

33

33

33

34

35

9.

9.1

9.2

9.3

9.4

Embedded Program/Data Memory (Flash) ..............

Flash Features .............................................................

Operation Modes .........................................................

Flash Access in CPU Mode .........................................

Parallel Flash Programming Mode...............................

38

38

38

39

42

Document Number: 002-04606 Rev. *C

9.5

9.6

Power on Sequence in Parallel Programming Mode .... 44

Flash Security ............................................................... 45

10.

Memory Space ............................................................ 48

11. Memory Maps .............................................................. 49

11.1 CY91F469Gx ................................................................ 49

12. I/O Map ......................................................................... 50

12.1 CY91F469Gx ................................................................ 50

12.2 Flash Memory and External Bus Area .......................... 81

13.

Interrupt Vector Table ................................................. 83

14. Recommended Settings ............................................. 88

14.1 PLL and Clock Gear Settings........................................ 88

14.2 Clock Modulator Settings .............................................. 89

15.

15.1

15.2

15.3

15.4

15.5

15.6

15.7

Electrical Characteristics ........................................... 95

Absolute Maximum Ratings .......................................... 95

Recommended Operating Conditions........................... 98

DC Characteristics ........................................................ 99

A/D Converter Characteristics .................................... 102

Alarm Comparator Characteristics.............................. 106

Flash Memory Program/Erase Characteristics ........... 107

AC Characteristics ...................................................... 107

16.

Ordering Information ................................................ 141

17.

Package Dimension .................................................. 142

18.

Revision History........................................................ 143

19. Main Changes in This Edition.................................. 144

Document History Page ............................................... 145

Sales, Solutions, and Legal Information .................... 146

Worldwide Sales and Design Support ..................... 146

Products .................................................................. 146

PSoC® Solutions .................................................... 146

Cypress Developer Community ............................... 146

Technical Support ................................................... 146

Page 3 of 146

�CY91F469GA/CY91F469GB

1. Product Lineup

Feature

CY91V460A

(Evaluation Device)

CY91F469Gx

Max. core frequency (CLKB)

80MHz

100MHz at 1.9V main regulator output voltage [1]

88MHz at 1.8V main regulator output voltage

Max. resource frequency (CLKP)

40MHz

50MHz

Max. external bus freq. (CLKT)

40MHz

50MHz

Max. CAN frequency (CLKCAN)

20MHz

50MHz

0.35μm

0.18μm

Emulation SRAM 32bit read data

2112 KByte

Satellite Flash memory

no

no

Flash Protection

no

yes

Flash CRC calculation

no

yes

64 KByte

64 KByte

Max. FlexRay frequency (SCLK)

Technology

Flash memory

D-RAM

ID-RAM

64 KByte

32 KByte

Flash-cache (F-cache)

16 KByte

16 KBytes

External bus cache (I-cache)

4 KBytes

4 KBytes

Boot-ROM / BI-ROM

MMU/MPU

DMA

4 KByte fixed

MPU (16 ch)

[1]

4 KByte

MPU (8 ch) [2]

5 ch

5 ch

MAC (μDSP)

no

no

Watchdog timer

yes

yes

yes (disengageable)

yes

yes

yes

Watchdog timer (RC osc. based)

Bit Search

RTC

1 ch

1 ch

Free Running Timer

8 ch

8 ch

ICU

8 ch

8 ch

OCU

8 ch

8 ch

Reload Timer

8 ch

8 ch

PPG 16-bit

16 ch

16 ch

PFM 16-bit

1 ch

1 ch

Sound Generator

1 ch

1 ch

4 ch (8-bit) / 2 ch (16-bit)

4 ch (8-bit) / 2 ch (16-bit)

SMC

Up/Down Counter (8/16-bit)

6 ch

-

LCD controller (40x4)

1ch

-

Document Number: 002-04606 Rev. *C

Page 4 of 146

�CY91F469GA/CY91F469GB

Feature

C_CAN

CY91V460A

(Evaluation Device)

CY91F469Gx

6 ch (128msg)

6 ch (128msg)

4 ch + 4 ch FIFO + 8 ch

4 ch + 4 ch FIFO

4 ch

4 ch

yes (32bit addr, 32bit data, 8 chip selects)

yes (28bit addr, 32bit data, 8 chip selects)

External Interrupts

16 ch

16 ch

NMI Interrupts

1 ch

General IO ports

288

205

ADC (10 bit)

32 ch

32 ch

Alarm Comparator

2 ch

2 ch

Reset input (INITX)

yes

yes

LIN-USART

I2C (400k)

FR external bus

Hardware Standby Input (HSTX)

yes

no

Clock Modulator

yes

yes

Low power mode

yes

yes

Supply Supervisor

(low voltage detection

yes

yes

Clock Supervisor

yes

yes

Main clock oscillator

4MHz

4MHz

Sub clock oscillator

32kHz

32kHz

RC Oscillator

100kHz

100kHz / 2MHz

PLL

x 20

x 25

DSU4

yes

EDSU

JTAG Boundary Scan

yes (32 BP)

no

[2]

yes (16 BP) [2]

no

yes

3V / 5V

3V / 5V

Regulator

yes

yes

Power Consumption

n.a.

2

■ if tSCYCI = (2*k + 1)*tCLKP, then m = k + 1, where k is an integer > 1

Notes:

■

The above values are AC characteristics for CLK synchronous mode.

■ tCLKP

is the cycle time of the peripheral clock.

Document Number: 002-04606 Rev. *C

Page 109 of 146

�CY91F469GA/CY91F469GB

Figure 4. Internal Clock Mode (Master Mode)

tSCYCI

SCKn

for ESCR:SCES = 0

VOH

VOL

VOL

VOH

SCKn

for ESCR:SCES = 1

VOH

VOL

tSLOVI

tOVSHI

VOH

VOL

SOTn

tIVSHI

tSHIXI

VIH

VIL

SINn

VIH

VIL

Figure 5. External Clock Mode (Slave Mode)

tSLSHE

SCKn

for ESCR:SCES = 0

VOH

SCKn

for ESCR:SCES = 1

VOL

tSHSLE

VOH

VOL

VOL

VOH

VOH

VOL

VOH

VOL

tRE

tFE

tSLOVE

SOTn

VOH

VOL

tIVSHE

SINn

Document Number: 002-04606 Rev. *C

VIH

VIL

tSHIXE

VIH

VIL

Page 110 of 146

�CY91F469GA/CY91F469GB

15.7.4 I2C AC Timings at VDD5 = 3.0 to 5.5 V

■

Conditions during AC measurements

All AC tests were measured under the following conditions:

❐ -IOdrive = 3 mA

❐ -VDD5 = 3.0 V to 5.5 V, Iload = 3 mA

❐ -VSS5 = 0 V

❐ -Ta = − 40 °C to + 125 °C

❐ -Cl = 50 pF

❐ -VOL = 0.3 ⋅ VDD5

❐ -VOH = 0.7 ⋅ VDD5

❐ -EPILR = 0, PILR = 0 (CMOS Hysteresis 0.3 ⋅ VDD5/0.7 ⋅ VDD5)

15.7.4.1

Fast Mode:

(VDD5 = 3.5 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = −40 °C to + 125 °C)

Parameter

Symbol

Pin Name

fSCL

Value

Unit

Min

Max

SCLn

0

400

kHz

tHD;STA

SCLn, SDAn

0.6

−

μs

LOW period of the SCL clock

tLOW

SCLn

1.3

−

μs

HIGH period of the SCL clock

tHIGH

SCLn

0.6

−

μs

tSU;STA

SCLn, SDAn

0.6

−

μs

tHD;DAT

SCLn, SDAn

0

0.9

μs

SCL clock frequency

Hold time (repeated) START

condition. After this period, the first clock

pulse is generated

Setup time for a repeated START condition

2C-bus

Data hold time for I

devices

tSU;DAT

SCLn SDAn

100

−

ns

Rise time of both SDA and SCL signals

tr

SCLn, SDAn

20 + 0.1Cb

300

ns

Fall time of both SDA and SCL signals

tf

SCLn, SDAn

20 + 0.1Cb

300

ns

tSU;STO

SCLn, SDAn

0.6

−

μs

tBUF

SCLn, SDAn

1.3

−

μs

Capacitive load for each bus line

Cb

SCLn, SDAn

−

400

pF

Pulse width of spike suppressed by input

filter

tSP

SCLn, SDAn

0

(1..1.5) ⋅

tCLKP

ns

Data setup time

Setup time for STOP condition

Bus free time between a STOP and START

condition

Remark

[1]

1. The noise filter will suppress single spikes with a pulse width of 0ns and between (1 to 1.5) cycles of peripheral clock, depending on the phase

relationship between I2C signals (SDA, SCL) and peripheral clock.

Note: tCLKP is the cycle time of the peripheral clock.

Document Number: 002-04606 Rev. *C

Page 111 of 146

�Document Number: 002-04606 Rev. *C

SCL

SDA

tHD;STA

tf

S

tr

tHD;DAT

tLOW

tHIGH

tSU;DAT

tSU;STA

Sr

tHD;STA

tSP

tr

P

tSU;ST0

tBUF

S

tf

CY91F469GA/CY91F469GB

Page 112 of 146

�CY91F469GA/CY91F469GB

15.7.5 Free-Run Timer Clock

(VDD5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Input pulse width

Symbol

Pin Name

Condition

tTIWH

tTIWL

CKn

−

Value

Min

Max

4tCLKP

−

Unit

ns

Note: tCLKP is the cycle time of the peripheral clock.

CKn

VIH

VIH

VIL

VIL

tTIWH

tTIWL

15.7.6 Trigger Input Timing

(VDD5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

Condition

tINP

ICUn

tATGX

ATGX

Input capture input trigger

A/D converter trigger

Value

Unit

Min

Max

−

5tCLKP

−

ns

−

5tCLKP

−

ns

Note: tCLKP is the cycle time of the peripheral clock.

tATGX, tINP

ICUn,

ATGX

Document Number: 002-04606 Rev. *C

Page 113 of 146

�CY91F469GA/CY91F469GB

15.7.7 External Bus AC Timings at VDD35 = 4.5 to 5.5 V

■

Conditions during AC measurements

All AC tests were measured under the following conditions:

❐ -IOdrive = 5 mA

❐ -VDD35 = 4.5 V to 5.5 V, Iload = 5 mA

❐ -VSS5 = 0 V

❐ -Ta = − 40 °C to + 125 °C

❐ -Cl = 50 pF

❐ -VOL = 0.2 ⋅ VDD35

❐ -VOH = 0.8 ⋅ VDD35

❐ -EPILR = 0, PILR = 1 (Automotive Level = worst case)

15.7.7.1

Basic Timing

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK

SYSCLK ↓ to CSXn delay time

SYSCLK ↑ to CSXn delay time

(Addr → CS delay)

SYSCLK ↓ to ASX delay time

SYSCLK ↓ to BAAX delay time

SYSCLK ↓ to Address valid delay time

Symbol

tCLCH

tCHCL

Pin Name

SYSCLK

tCLASH

tCLBAL

tCLBAH

tCLAV

Max

1/2 ⋅ tCLKT − 4

1/2 ⋅ tCLKT + 5

ns

1/2 ⋅ tCLKT − 5

1/2 ⋅ tCLKT + 4

ns

−

9

ns

8

ns

−2

8

ns

SYSCLK

ASX

−

8

ns

−

7

ns

SYSCLK

BAAX

−

5

ns

−2

−

ns

SYSCLK

A27 to A0

−

10

ns

SYSCLK

CSXn

tCHCSL

tCLASL

Unit

Min

−

tCLCSL

tCLCSH

Value

Note: tCLKT is the cycle time of the external bus clock.

Document Number: 002-04606 Rev. *C

Page 114 of 146

�CY91F469GA/CY91F469GB

tCLCH

tCHCL

tCYC

SYSCLK

tCLCSL

tCLCSH

CSXn

tCHCSL

delayed CSXn

tCLASH

tCLASL

ASX

tCLAV

ADDRESS

tCLBAH

tCLBAL

BAAX

Document Number: 002-04606 Rev. *C

Page 115 of 146

�CY91F469GA/CY91F469GB

15.7.7.2

Synchronous/Asynchronous Read Access with External MCLKI Input

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

tCHRL

Value

Unit

Min

Max

SYSCLK

RDX

−2

7

ns

tCHRH

MCLKI

RDX

10

20

ns

Data valid to RDX ↑ setup time

tDSRH

RDX

D31 to D0

20

−

ns

RDX ↑ to Data valid hold time (external MCLKI

input)

tRHDX

RDX

D31 to D0

0

−

ns

Data valid to MCLKI ↑ setup time

tDSCH

MCLKI

D31 to D0

1

−

ns

MCLKI ↑ to Data valid hold time

tCHDX

MCLKI

D31 to D0

3

−

ns

SYSCLK ↓ to WRXn (as byte enable) delay

time

tCLWRL

−

9

ns

SYSCLK ↑ /MCLKI ↑ to RDX delay time

SYSCLK

WRXn

tCLWRH

tCLCSL

SYSCLK ↓ to CSXn delay time

SYSCLK

CSXn

tCLCSH

−1

−

ns

−

9

ns

−

8

ns

SYSCLK

MCLKI

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tDSCH

tRHDX

tCHDX

DATA IN

Document Number: 002-04606 Rev. *C

Page 116 of 146

�CY91F469GA/CY91F469GB

15.7.7.3

Synchronous/Asynchronous Read Access with Internal MCLKO --> MCLKI Feedback

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↑ to RDX delay time

Symbol

Pin Name

tCHRL

SYSCLK

RDX

tCHRH

Value

Unit

Min

Max

−2

7

ns

−2

4

ns

Data valid to RDX setup time

tDSRH

RDX

D31 to D0

19

−

ns

RDX ↑ to Data valid hold time (internal

MCLKO → MCLKI / /MCLKI feedback)

tRHDX

RDX

D31 to D0

0

−

ns

−

9

ns

−1

−

ns

−

9

ns

−

8

ns

tCLWRL

SYSCLK ↓ to WRXn (as byte enable) delay

time

SYSCLK

WRXn

tCLWRH

tCLCSL

SYSCLK ↓ to CSXn delay time

SYSCLK

CSXn

tCLCSH

SYSCLK

tCLCSL

tCLCSH

CSXn

tCLWRL

tCLWRH

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tRHDX

DATA IN

Document Number: 002-04606 Rev. *C

Page 117 of 146

�CY91F469GA/CY91F469GB

15.7.7.4

Synchronous Write Access - Byte Control Type

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↓ to WEX delay time

Symbol

Pin Name

tCLWL

SYSCLK

WEX

tCLWH

Value

Unit

Min

Max

−

8

ns

−2

−

ns

Data valid to WEX ↓ setup time

tDSWL

WEX

D31 to D0

−5

−

ns

WEX ↑ to Data valid hold time

tWHDH

WEX

D31 to D0

tCLKT − 10

−

ns

−

9

ns

−1

−

ns

−

9

ns

−

8

ns

SYSCLK ↓ to WRXn (as byte enable) delay time

SYSCLK ↓ to CSXn delay time

tCLWRL

SYSCLK

WRXn

tCLWRH

tCLCSL

SYSCLK

CSXn

tCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCLWH

tCLWL

WEX

tDSWL

tWHDH

DATA OUT

Document Number: 002-04606 Rev. *C

Page 118 of 146

�CY91F469GA/CY91F469GB

15.7.7.5

Synchronous Write Access - No Byte Control Type

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↓ to WRXn delay time

Symbol

Pin Name

tCLWRL

SYSCLK

WRXn

tCLWRH

Value

Unit

Min

Max

−

9

ns

−1

−

ns

Data valid to WRXn ↓ setup time

tDSWRL

WRXn

D31 to D0

−6

−

ns

WRXn ↑ to Data valid hold time

tWRHDH

WRXn

D31 to D0

tCLKT − 10

−

ns

−

9

ns

−

8

ns

SYSCLK ↓ to CSXn delay time

tCLCSL

SYSCLK

CSXn

tCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

tDSWRL

tWRHDH

DATA OUT

Document Number: 002-04606 Rev. *C

Page 119 of 146

�CY91F469GA/CY91F469GB

15.7.7.6

Asynchronous Write Access - Byte Control Type

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

WEX ↓ to WEX ↑ pulse width

tWLWH

Data valid to WEX ↓ setup time

WEX ↑ to Data valid hold time

WEX to WRXn delay time

WEX to CSXn delay time

Value

Unit

Min

Max

WEX

tCLKT − 6

−

ns

tDSWL

WEX

D31 to D0

1/2 ⋅ tCLKT − 9

−

ns

tWHDH

WEX

D31 to D0

1/2 ⋅ tCLKT − 7

−

ns

tWRLWL

WEX

WRXn

tWHWRH

tCLWL

WEX

CSXn

tWHCH

−

1/2 ⋅ tCLKT + 2

ns

1/2 ⋅ tCLKT − 1

−

ns

−

1/2 ⋅ tCLKT − 1

ns

1/2 ⋅ tCLKT + 1

−

ns

CSXn

tWHCH

tCLWL

WRXn

(as byte enable)

tWHWRH

tWRLWL

tWLWH

WEX

tDSWL

tWHDH

DATA OUT

Document Number: 002-04606 Rev. *C

Page 120 of 146

�CY91F469GA/CY91F469GB

15.7.7.7

Asynchronous Write Access - No Byte Control Type

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

WRXn ↓ to WRXn ↑ pulse width

tWRLWRH

Data valid to WRXn ↓ setup time

WRXn ↑ to Data valid hold time

WRXn to CSXn delay time

Value

Unit

Min

Max

WRXn

tCLKT − 6

−

ns

tDSWRL

WRXn

D31 to D0

1/2 ⋅ tCLKT − 9

−

ns

tWRHDH

WRXn

D31 to D0

1/2 ⋅ tCLKT − 7

−

ns

−

1/2 ⋅ tCLKT − 1

ns

1/2 ⋅ tCLKT + 1

−

ns

tCLWRL

WRXn

CSXn

tWRHCH

CSXn

tWRHCH

tCLWRL

tWRLWRH

WRXn

tDSWRL

tWRHDH

DATA OUT

Document Number: 002-04606 Rev. *C

Page 121 of 146

�CY91F469GA/CY91F469GB

15.7.7.8

RDY Waitcycle Insertion

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

RDY setup time

tRDYS

RDY hold time

tRDYH

Value

Unit

Min

Max

SYSCLK

RDY

19

−

ns

SYSCLK

RDY

0

−

ns

SYSCLK

tRDYS

tRDYH

RDY

15.7.7.9

Bus Hold Timing

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↓ to BGRNTX delay time

Symbol

Pin Name

tCLBGL

tCLBGH

Bus HIZ to BGRNTX ↓

tAXBGL

BGRNTX ↑ to Bus drive

tBGHAV

Value

Unit

Min

Max

SYSCLK

BGRNTX

−

5

ns

−

5

ns

BGRNTX

MCLK*

A0 to An

RDX, ASX

WRXn,WEX

CSXn,BAAX

tCLKT + 2

−

ns

tCLKT + 1

−

ns

Note: BRQ must be kept High until the bus is granted (this is acknowledged by the falling edge of BGRNTX). It must be kept High as

long as the bus shall be hold. After releasing the bus (BRQ set to Low) this is acknowledged by the rising edge of BGRNTX.

SYSCLK

BRQ

tCLBGL

tCLBGH

BGRNTX

tAXBGL

tBGHAV

ADDR,RDX,WRX,

WEX,CSXn,ASX,

MCLKE,MCLKI,

MCLKO,BAAX

Document Number: 002-04606 Rev. *C

Page 122 of 146

�CY91F469GA/CY91F469GB

15.7.7.10 Clock Relationships

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK to MCLKO

Symbol

Pin Name

tCSHMH

tCSLML

MCLKO ↓ to MCLKE (in sleep mode)

tCLML

tCLMH

Value

Unit

Min

Max

SYSCLK

MCLKO

1

5

ns

0

2

ns

MCLKO

MCLKE

−

5

ns

−3

−

ns

SYSCLK

tCSHMH

tCSLML

MCLKO

tCLML

tCLMH

MCLKE (sleep)

Document Number: 002-04606 Rev. *C

Page 123 of 146

�CY91F469GA/CY91F469GB

15.7.7.11 DMA Transfer

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↓ to DACKX delay time

SYSCLK ↓ to DEOP delay time

Symbol

Pin Name

tCLDAL

tCLDAH

tCLDEL

Value

Unit

Min

Max

SYSCLK

DACKXn

−

8

ns

−

8

ns

SYSCLK

DEOPn

−

7

ns

−

9

ns

tCHDAL

SYSCLK

DACKXn

−1

8

ns

SYSCLK ↑ to DEOP delay time

(ADDR → delayed CS)

tCHDEL

SYSCLK

DEOPn

−1

8

ns

DREQ setup time

tDRQS

SYSCLK

DREQn

19

−

ns

DREQ hold time

tDRQH

SYSCLK

DREQn

0

−

ns

DEOTXn setup time

tDTXS

SYSCLK

DEOTXn

20

−

ns

DEOTXn hold time

tDTXH

SYSCLK

DEOTXn

0

−

ns

SYSCLK ↑ to DACKX delay time

(ADDR → delayed CS)

tCLDEH

Note: DREQ and DEOTX must be applied for at least 5 ⋅ tCLKT to ensure that they are really sampled and evaluated.Under best

case conditions (DMA not busy) only setup and hold times are required.

Document Number: 002-04606 Rev. *C

Page 124 of 146

�CY91F469GA/CY91F469GB

SYSCLK

tCLDAL

tCLDAH

tCLDEL

tCLDEH

DACKX

DEOP

tCHDAL

delayed DACKX

tCHDEL

delayed DEOP

tDRQS

tDRQH

tDTXS

tDTXH

DREQ

DEOTX

Document Number: 002-04606 Rev. *C

Page 125 of 146

�CY91F469GA/CY91F469GB

15.7.7.12 DMA Flyby Transfer

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C

to + 125 °C)

Parameter

SYSCLK ↑ to IORDX delay time

Symbol

Pin Name

tCHIRL

tCHIRH

tCHIWL

SYSCLK ↑ to IOWRX delay time

tCHIWH

Value

Unit

Min

Max

SYSCLK

IORDX

−2

8

ns

0

4

ns

SYSCLK

IOWRX

−2

8

ns

−1

3

ns

SYSCLK

tCHIRH

tCHIRL

IORDX

tCHIWH

tCHIWL

IOWRX

Document Number: 002-04606 Rev. *C

Page 126 of 146

�CY91F469GA/CY91F469GB

15.7.8 External Bus AC Timings at VDD35 = 3.0 to 4.5 V

■

Conditions during AC measurements

All AC tests were measured under the following conditions:

❐ -IOdrive = 5 mA

❐ -VDD35 = 3.0 V to 4.5 V, Iload = 3 mA

❐ -VSS5 = 0 V

❐ -Ta = − 40 °C to + 125 °C

❐ -Cl = 50 pF

❐ -VOL = 0.2 ⋅ VDD35

❐ -VOH = 0.8 ⋅ VDD35

❐ -EPILR = 0, PILR = 1 (Automotive Level = worst case)

15.7.8.1

Basic Timing

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK

SYSCLK ↓ to CSXn delay time

SYSCLK ↑ to CSXn delay time

(Addr → CS delay)

SYSCLK ↓ to ASX delay time

SYSCLK ↓ to BAAX delay time

SYSCLK ↓ to Address valid delay time

Document Number: 002-04606 Rev. *C

Symbol

tCLCH

tCHCL

Pin Name

SYSCLK

tCLASH

tCLBAL

tCLBAH

tCLAV

Max

1/2 ⋅ tCLKT − 1

1/2 ⋅ tCLKT + 3

ns

1/2 ⋅ tCLKT − 3

1/2 ⋅ tCLKT + 1

ns

−

9

ns

7

ns

−1

4

ns

SYSCLK

ASX

−

5

ns

−

6

ns

SYSCLK

BAAX

−

6

ns

0

−

ns

SYSCLK

A27 to A0

−

13

ns

SYSCLK

CSXn

tCHCSL

tCLASL

Unit

Min

−

tCLCSL

tCLCSH

Value

Page 127 of 146

�CY91F469GA/CY91F469GB

tCLCH

tCHCL

tCYC

SYSCLK

tCLCSL

tCLCSH

CSXn

tCHCSL

delayed CSXn

tCLASH

tCLASL

ASX

tCLAV

ADDRESS

tCLBAH

tCLBAL

BAAX

Document Number: 002-04606 Rev. *C

Page 128 of 146

�CY91F469GA/CY91F469GB

15.7.8.2

Synchronous/Asynchronous Read Access With External MCLKI Input

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

tCHRL

Value

Unit

Min

Max

SYSCLK

RDX

−1

3

ns

tCHRH

MCLKI

RDX

11

25

ns

Data valid to RDX ↑ setup time

tDSRH

RDX

D31 to D0

25

−

ns

RDX ↑ to Data valid hold time (external MCLKI

input)

tRHDX

RDX

D31 to D0

0

−

ns

Data valid to MCLKI ↑ setup time

tDSCH

MCLKI

D31 to D0

1

−

ns

MCLKI ↑ to Data valid hold time

tCHDX

MCLKI

D31 to D0

3

−

ns

SYSCLK ↓ to WRXn (as byte enable) delay

time

tCLWRL

−

5

ns

−1

−

ns

−

5

ns

−

6

ns

SYSCLK ↑/MCLKI ↑ to RDX delay time

SYSCLK

WRXn

tCLWRH

tCLCSL

SYSCLK ↓ to CSXn delay time

SYSCLK

CSXn

tCLCSH

SYSCLK

MCLKI

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tDSCH

tRHDX

tCHDX

DATA IN

Document Number: 002-04606 Rev. *C

Page 129 of 146

�CY91F469GA/CY91F469GB

15.7.8.3

Synchronous/Asynchronous Read Access with Internal MCLKO --> MCLKI Feedback

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↑ to RDX delay time

Symbol

Pin Name

tCHRL

SYSCLK

RDX

tCHRH

Value

Unit

Min

Max

−1

3

ns

−2

4

ns

Data valid to RDX ↑ setup time

tDSRH

RDX

D31 to D0

25

−

ns

RDX ↑ to Data valid hold time

(internal MCLKO → MCLKI /

/MCLKI feedback)

tRHDX

RDX

D31 to D0

0

−

ns

−

5

ns

tCLWRL

SYSCLK ↓ to WRXn

(as byte enable) delay time

tCLWRH

tCLCSL

SYSCLK ↓ to CSXn delay time

tCLCSH

SYSCLK

WRXn

SYSCLK

CSXn

−1

−

ns

−

5

ns

−

6

ns

SYSCLK

tCLCSL

tCLCSH

CSXn

tCLWRL

tCLWRH

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tRHDX

DATA IN

Document Number: 002-04606 Rev. *C

Page 130 of 146

�CY91F469GA/CY91F469GB

15.7.8.4

Synchronous Write Access - Byte Control Type

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↓ to WEX delay time

Symbol

Pin Name

tCLWL

SYSCLK

WEX

tCLWH

Value

Unit

Min

Max

−

5

ns

−1

−

ns

Data valid to WEX ↓ setup time

tDSWL

WEX

D31 to D0

− 11

−

ns

WEX ↑ to Data valid hold time

tWHDH

WEX

D31 to D0

tCLKT − 13

−

ns

SYSCLK ↓ to WRXn (as byte enable) delay

time

tCLWRL

−

5

ns

−1

−

ns

−

5

ns

−

6

ns

SYSCLK ↓ to CSXn delay time

SYSCLK

WRXn

tCLWRH

tCLCSL

SYSCLK

CSXn

tCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCLWH

tCLWL

WEX

tDSWL

tWHDH

DATA OUT

Document Number: 002-04606 Rev. *C

Page 131 of 146

�CY91F469GA/CY91F469GB

15.7.8.5

Synchronous Write Access - No Byte Control Type

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↓ to WRXn delay time

Symbol

Pin Name

tCLWRL

SYSCLK

WRXn

tCLWRH

Value

Unit

Min

Max

−

5

ns

−1

−

ns

Data valid to WRXn ↓ setup time

tDSWRL

WRXn

D31 to D0

− 11

−

ns

WRXn ↑ to Data valid hold time

tWRHDH

WRXn

D31 to D0

tCLKT − 13

−

ns

−

5

ns

−

6

ns

SYSCLK ↓ to CSXn delay time

tCLCSL

SYSCLK

CSXn

tCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

tDSWRL

tWRHDH

DATA OUT

Document Number: 002-04606 Rev. *C

Page 132 of 146

�CY91F469GA/CY91F469GB

15.7.8.6

Asynchronous Write Access - Byte Control Type

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

WEX ↓ to WEX ↑ pulse width

tWLWH

Data valid to WEX ↓ setup time

WEX ↑ to Data valid hold time

WEX to WRXn delay time

WEX to CSXn delay time

Value

Unit

Min

Max

WEX

tCLKT − 4

−

ns

tDSWL

WEX

D31 to D0

1/2 ⋅ tCLKT − 12

−

ns

tWHDH

WEX

D31 to D0

1/2 ⋅ tCLKT − 11

−

ns

tWRLWL

WEX

WRXn

tWHWRH

tCLWL

WEX

CSXn

tWHCH

−

1/2 ⋅ tCLKT + 1

ns

1/2 ⋅ tCLKT − 1

−

ns

−

1/2 ⋅ tCLKT − 1

ns

1/2 ⋅ tCLKT + 1

−

ns

CSXn

tWHCH

tCLWL

WRXn

(as byte enable)

tWHWRH

tWRLWL

tWLWH

WEX

tDSWL

tWHDH

DATA OUT

Document Number: 002-04606 Rev. *C

Page 133 of 146

�CY91F469GA/CY91F469GB

15.7.8.7

Asynchronous Write Access - No Byte Control Type

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

WRXn ↓ to WRXn ↑ pulse width

tWRLWRH

Data valid to WRXn ↓ setup time

WRXn ↑ to Data valid hold time

WRXn to CSXn delay time

Value

Unit

Min

Max

WRXn

tCLKT − 3

−

ns

tDSWRL

WRXn

D31 to D0

1/2 ⋅ tCLKT − 12

−

ns

tWRHDH

WRXn

D31 to D0

1/2 ⋅ tCLKT − 11

−

ns

−

1/2 ⋅ tCLKT − 1

ns

1/2 ⋅ tCLKT + 1

−

ns

tCLWRL

WRXn

CSXn

tWRHCH

CSXn

tWRHCH

tCLWRL

tWRLWRH

WRXn

tDSWRL

tWRHDH

DATA OUT

Document Number: 002-04606 Rev. *C

Page 134 of 146

�CY91F469GA/CY91F469GB

15.7.8.8

RDY Waitcycle Insertion

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

Symbol

Pin Name

RDY setup time

tRDYS

RDY hold time

tRDYH

Value

Unit

Min

Max

SYSCLK

RDY

24

−

ns

SYSCLK

RDY

0

−

ns

SYSCLK

tRDYS

tRDYH

RDY

Document Number: 002-04606 Rev. *C

Page 135 of 146

�CY91F469GA/CY91F469GB

15.7.8.9

Bus Hold Timing

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↓ to BGRNTX delay time

Symbol

Pin Name

tCLBGL

tCLBGH

Bus HIZ to BGRNTX ↓

tAXBGL

BGRNTX ↑ to Bus drive

tBGHAV

Value

Unit

Min

Max

SYSCLK

BGRNTX

−

5

ns

−

6

ns

BGRNTX

MCLK*

A0 to An

RDX, ASX

WRXn,WEX

CSXn,BAAX

tCLKT + 2

−

ns

tCLKT − 2

−

ns

Note: BRQ must be kept High until the bus is granted (this is acknowledged by the falling edge of BGRNTX). It must be kept High as

long as the bus shall be hold.After releasing the bus (BRQ set to Low) this is acknowledged by the rising edge of BGRNTX.

SYSCLK

BRQ

tCLBGL

tCLBGH

BGRNTX

tAXBGL

tBGHAV

ADDR,RDX,WRX,

WEX,CSXn,ASX,

MCLKE,MCLKI,

MCLKO,BAAX

Document Number: 002-04606 Rev. *C

Page 136 of 146

�CY91F469GA/CY91F469GB

15.7.8.10 Clock Relationships

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK to MCLKO

Symbol

Pin Name

tCSHMH

tCSLML

MCLKO ↓ to MCLKE (in sleep mode)

tCLML

tCLMH

Value

Unit

Min

Max

SYSCLK

MCLKO

1

5

ns

0

2

ns

MCLKO

MCLKE

−

4

ns

−3

−

ns

SYSCLK

tCSHMH

tCSLML

MCLKO

tCLML

tCLMH

MCLKE (sleep)

Document Number: 002-04606 Rev. *C

Page 137 of 146

�CY91F469GA/CY91F469GB

15.7.8.11 DMA Transfer

(VDD35 = 3.0 V to 4.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↓ to DACKX delay time

SYSCLK ↓ to DEOP delay time

Symbol

Pin Name

tCLDAL

SYSCLK

DACKXn

tCLDAH

tCLDEL

SYSCLK

DEOPn

Value

Unit

Min

Max

−

9

ns

−

7

ns

−

8

ns

−

7

ns

tCHDAL

SYSCLK

DACKXn

0

8

ns

SYSCLK ↑ to DEOP delay time

(ADDR → delayed CS)

tCHDEL

SYSCLK

DEOPn

−1

8

ns

DREQ setup time

tDRQS

SYSCLK

DREQn

25

−

ns

DREQ hold time

tDRQH

SYSCLK

DREQn

0

−

ns

DEOTXn setup time

tDTXS

SYSCLK

DEOTXn

26

−

ns

DEOTXn hold time

tDTXH

SYSCLK

DEOTXn

0

−

ns

SYSCLK ↑ to DACKX delay time

(ADDR → delayed CS)

tCLDEH

Note: DREQ and DEOTX must be applied for at least 5 ⋅ tCLKT to ensure that they are really sampled and evaluated.Under best case

conditions (DMA not busy) only setup and hold times are required.

Document Number: 002-04606 Rev. *C

Page 138 of 146

�CY91F469GA/CY91F469GB

SYSCLK

tCLDAL

tCLDAH

tCLDEL

tCLDEH

DACKX

DEOP

tCHDAL

delayed DACKX

tCHDEL

delayed DEOP

tDRQS

tDRQH

tDTXS

tDTXH

DREQ

DEOTX

Document Number: 002-04606 Rev. *C

Page 139 of 146

�CY91F469GA/CY91F469GB

15.7.8.12 DMA Flyby Transfer

(VDD35 = 4.5 V to 5.5 V, Vss5 = AVss5 = 0 V, TA = − 40 °C to + 125 °C)

Parameter

SYSCLK ↑ to IORDX delay time

Symbol

Pin Name

tCHIRL

SYSCLK

IORDX

tCHIRH

tCHIWL

SYSCLK ↑ to IOWRX delay time

tCHIWH

SYSCLK

IOWRX

Value

Unit

Min

Max

−1

6

ns

−2

3

ns

0

5

ns

−2

3

ns

SYSCLK

tCHIRH

tCHIRL

IORDX

tCHIWH

tCHIWL

IOWRX

Document Number: 002-04606 Rev. *C

Page 140 of 146

�CY91F469GA/CY91F469GB

16. Ordering Information

Part number

CY91F469GBPB-GS-UJE1

Document Number: 002-04606 Rev. *C

Package

Remarks

320-pin plastic BGA

(BYA320)

Page 141 of 146

�CY91F469GA/CY91F469GB

17. Package Dimension

D

D2

D1

A

eD

0.20 C

2X

eE

E2 E

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

7

SE

E1

Y W V U T R

PIN A1

CORNER

P N M L K

J

H G F

8

320xφb

0.20 C

TOP VIEW

E D C B A

SD

B

6

2X

7

0.30

C A B

0.15 C

BOTTOM VIEW

0.20 C

A1

0.15 C

DETAIL A

A

C

SIDE VIEW

DETAIL A

NOTES

DIMENSIONS

SYMBOL

MIN.

NOM.

A

A1

2.46

4. "e" REPRESENTS THE SOLDER BALL GRID PITCH.

27.00 BSC

E

27.00 BSC

D1

24.00 BSC

E 1

24.00 BSC

MD

20

ME

20

n

5. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION.

n IS THE NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX

SIZE MD X ME.

6. DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER

IN A PLANE PARALLEL TO DATUM C.

320

0.60

2. DIMENSIONS AND TOLERANCES METHODS PER ASME Y14.5-2009 .

THIS OUTLINE CONFORMS TO JEP95, SECTION 4.5.

3. BALL POSITION DESIGNATION PER JEP95, SECTION 3, SPP-010.

0.35

D

Φb

MAX.

1. ALL DIMENSIONS ARE IN MILLIMETERS.

0.75

eD

1.27 BSC

eE

1.27 BSC

SD / SE

0.635

0.90

7. "SD" AND "SE" ARE MEASURED WITH RESPECT TO DATUMS A AND B AND

DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

WHEN THERE IS AN ODD NUMBER

OF SOLDER BALLS IN THE OUTER ROW,

"SD" OR "SE" =0.

WHEN THERE IS AN

EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW,

"SD" = eD/2 AND "SE" = eE/2.

8. A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK.

METALLIZED MARK INDENTATION OR OTHER MEANS.

9. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

10. JEDEC SPECIFICATION NO. REF: N/A.

PACKAGE OUTLINE, 320 BALL FBGA

27.00X27.00X2.46 MM BYA320 REV**

002-16414 **

Document Number: 002-04606 Rev. *C

Page 142 of 146

�CY91F469GA/CY91F469GB

18. Revision History

Spansion Publication Number: DS07-16608-1E

Version

Date

2.0

2008-01-08

Initial version

2.1

2008-01-11

I/O circuit type J2: Feedback resistor = approx. 2 * 5 MΩ.

2.2

2008-02-01

Pins 257 to 320 are GND.

2.3

2008-02-04

Various changes after proofread by FJ

2.4

2008-02-15

Corrected product lineup table: No NMI function,

updated disclaimer at the end

2.5

2008-02-22

Corrected naming and size of Flash-cache (F-cache)

2008-04-29

Flash Operation modes: Added note about the

"flash access mode switching" incl. address in Boot ROM

Flash parallel programming: wait times added

2008-08-18

Product Lineup: corrected typos

Pin Description: corrected CAN RX (is input only)

IO Circuit Type: corrected typos

Handling Devices: updated the "Notes on PS register"

Interrupt Vector Table: corrected the footnotes

Electrical Characteristics: removed the note that analog input/output

pins cannot accept +B signal input.

DC characteristics: updated PullUp/Down resistance values,

corrected the table footnotes,

splitted ILV into external and internal LV detection

ADC Characteristics: Corrected the items about nonlinearity error

FLASH memory parallel programming mode: added section "Poweron

Sequence in parallel programming mode"

FLASH memory program/erase characteristics: word programming time

is for 16- and 32-bit

Ordering information: updated the part numbers

All pages: Kilobytes are now written with “K”

2.7

2008-08-19

DC characteristics: updated the current consumption values ICC, ICCH

3.0

2009-01-09

DC characteristics: corrected the current consumption values ICC, ICCH

Added Ta=125C characteristics

2.6

Remark

Document Number: 002-04606 Rev. *C

Page 143 of 146

�CY91F469GA/CY91F469GB

19. Main Changes in This Edition

Page

Section

Change Results

33

Block Diagram

Corrected alarm comparator input pin name.

ALARM1 → ALARM_1

100

Electrical Characteristics

15.3. DC characteristics

Corrected output "L" voltage condition.

IOH → IOL

103

15.4. A/D converter characteristics

Corrected the explanation for “Zero reading voltage” and “Full scale reading voltage” in the table.

Unit:

LSB → V

Value:

AVRL - 1.5 → AVRL - 1.5 LSB

AVRL + 0.5 → AVRL + 0.5 LSB

AVRL + 2.5 → AVRL + 2.5 LSB

AVRH - 3.5 → AVRH - 3.5 LSB

AVRH - 1.5 → AVRH - 1.5 LSB

AVRH + 0.5 → AVRH + 0.5 LSB

109

15.7. AC characteristics

15.7.3 LIN-USART Timings at

VDD5 = 3.0 to 5.5 V

Corrected “• All AC tests were measured under the

following conditions:“.

Ta:

125 ⋅ °C → 125 °C

111

112

Rev.*B

-

Corrected the figures in "Internal clock mode

(master mode)" and "External clock mode (slave mode)".

VOH → VIH, VOL → VIL

15.7.4 I2C AC Timings at

VDD5 = 3.0 to 5.5 V

Corrected the explanation for “Rise time of both SDA and SCL signals”

and “Fall time of both SDA and SCL signals” in the table.

0.1Cb → 0.1Cb

-

-

Marketing Part Numbers changed from an MB prefix to a CY prefix.

6

141

142

2.Pin Assignment

16.Ordering Information

17.Package Dimension

Package description modified to JEDEC description.

141

16.Ordering Information

Revised Marketing Part Numbers as follows:

Before)

MB91F469GBPB-GSE1

After)

CY91F469GBPB-GS-UJE1

Deleted the following Marketing part number as follows:

MB91F469GAPB-GS

MB91F469GBPB-GS

NOTE: Please see “Document History” for later revised information.

Document Number: 002-04606 Rev. *C

Page 144 of 146

�CY91F469GA/CY91F469GB

Document History Page

Document Title: CY91F469GA/CY91F469GB, FR60 CY91460G Series 32-bit Microcontroller Datasheet

Document Number: 002-04606

Revision

ECN

Submission

Date

**

–

05/25/2009

Migrated to Cypress and assigned document number 002-04606.

No change to document contents.

*A

5218210

04/20/2016

Updated to Cypress template.

*B

6314327

09/19/2018

Updated Document Title to read as “CY91F469GA/CY91F469GB, FR60 CY91460G Series

32-bit Microcontroller Datasheet”.

Replaced “MB91F469GA” with “CY91F469GA” in all instances across the document.

Replaced “MB91F469GB” with “CY91F469GB” in all instances across the document.

Replaced “MB91460G Series” with “CY91460G Series” in all instances across the

document.

Marketing Part Numbers changed from an MB prefix to a CY prefix.

2.Pin Assignments

16.Package Dimension

17.Ordering Information

For details, please see 19. Main Changes in this Edition

*C

6633872

07/22/2019

Updated to new template.

Document Number: 002-04606 Rev. *C

Description of Change

Page 145 of 146

�CY91F469GA/CY91F469GB

Sales, Solutions, and Legal Information

Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer’s representatives, and distributors. To find the office

closest to you, visit us at Cypress Locations.

PSoC® Solutions

Products

Arm® Cortex® Microcontrollers

Automotive

cypress.com/arm

cypress.com/automotive

Clocks & Buffers

Interface

cypress.com/clocks

cypress.com/interface

Internet of Things

Memory

cypress.com/iot

cypress.com/memory

Microcontrollers

cypress.com/mcu

PSoC

cypress.com/psoc

Power Management ICs

Cypress Developer Community

Community | Projects | Video | Blogs | Training | Components

Technical Support

cypress.com/support

cypress.com/pmic

Touch Sensing

cypress.com/touch

USB Controllers

Wireless Connectivity

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

cypress.com/usb

cypress.com/wireless

© Cypress Semiconductor Corporation 2009–2019. This document is the property of Cypress Semiconductor Corporation and its subsidiaries (“Cypress”). This document, including any software or

firmware included or referenced in this document (“Software”), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress

reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property

rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants

you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce

the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or

indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress’s patents that are infringed by the Software (as provided by

Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the

Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE

OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing

device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress shall have no liability arising out of any security breach, such

as unauthorized access to or use of a Cypress product. CYPRESS DOES NOT REPRESENT, WARRANT, OR GUARANTEE THAT CYPRESS PRODUCTS, OR SYSTEMS CREATED USING

CYPRESS PRODUCTS, WILL BE FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION (collectively, “Security

Breach”). Cypress disclaims any liability relating to any Security Breach, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any Security Breach. In

addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted

by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or

circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the

responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. “High-Risk Device”

means any device or system whose failure could cause personal injury, death, or property damage. Examples of High-Risk Devices are weapons, nuclear installations, surgical implants, and other

medical devices. “Critical Component” means any component of a High-Risk Device whose failure to perform can be reasonably expected to cause, directly or indirectly, the failure of the High-Risk

Device, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any use of

a Cypress product as a Critical Component in a High-Risk Device. You shall indemnify and hold Cypress, its directors, officers, employees, agents, affiliates, distributors, and assigns harmless from

and against all claims, costs, damages, and expenses, arising out of any claim, including claims for product liability, personal injury or death, or property damage arising from any use of a Cypress

product as a Critical Component in a High-Risk Device. Cypress products are not intended or authorized for use as a Critical Component in any High-Risk Device except to the limited extent that (i)

Cypress’s published data sheet for the product explicitly states Cypress has qualified the product for use in a specific High-Risk Device, or (ii) Cypress has given you advance written authorization to

use the product as a Critical Component in the specific High-Risk Device and you have signed a separate indemnification agreement.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in

the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-04606 Rev. *C

Revised July 22, 2019

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

Page 146 of 146

�