Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as “Cypress” document as this is the

company that originally developed the product. Please note that Infineon will continue

to offer the product to new and existing customers as part of the Infineon product

portfolio.

Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product

portfolio does not lead to any changes to this document. Future revisions will occur

when appropriate, and any changes will be set out on the document history page.

Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the

ordering part numbers listed in the datasheet for ordering.

www.infineon.com

�S6BP401A

Power Management IC

for Automotive ADAS Platform

Quad Buck 2.1 MHz DC/DC Converter and Dual LDO with Watchdog Timer

S6BP401A is a power management IC, consists of quad buck 2.1 MHz DC/DC converter with built-in switching FETs, dual Low

Drop-out regulator (LDOs) and a digital windowed watchdog timer. Having the switching FETs built-in, S6BP401A realizes high

power conversion efficiency and high switching frequency up to 2.4 MHz. The internal FETs are capable to handle up to 3 A load. As

S6BP401A employs the current mode architecture, it has fast load transient response. Built-in output voltage setting resistors and

compensation circuits reduce BOM cost and component area.

Features

Block Diagram

◼ Quad Buck DC/DC Converter (DD1 to DD4)

VIN

Input Range: 4.5 V to 5.5 V

Frequency

External clock mode: 1.8 MHz to 2.4 MHz

Internal clock mode: 2.0 MHz to 2.2 MHz

Built-in Switching FETs up to 3 A

Built-in Output Voltage Setting Resistors

Built-in Compensation Circuits

Switching

S6BP401A : PMIC

1.20 V to 1.575 V / 2 A

5V

1.00 V to 1.275 V / 3 A

DC/DC converter

◼ Dual LDO (LD1, LD2)

1.20 V to 2.575 V / 2 A

VIN

Input Voltage Range: 2.97 V to 5.5 V

Built-in Output Voltage Setting resistors

3.3 V to 3.4 V / 1 A

◼ Power Good Monitor Output for each DC/DC Converters,

3.3 V to 3.4 V / 0.2 A

LDO

LDOs

1.20 V to 2.875 V / 0.5 A

◼ Built-in Windowed Watchdog Timer (WDT)

◼ Under Voltage Lockout (UVLO)

5

Power Good

◼ Thermal Shutdown (TSD)

Watch Dog

◼ Over Current Protection (OCP)

◼ Over Voltage Protection (OVP)

◼ Independent Enabling for each DC/DC Converters and LDOs

◼ Load-independent Soft-Start

◼ Built-in Discharge Resistors

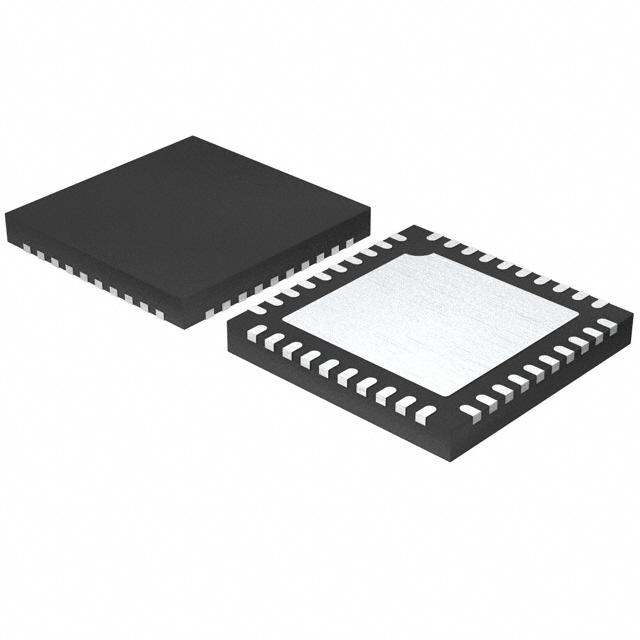

◼ Small 6 mm × 6 mm QFN-40 Package

◼ AEC-Q100 compliant (Grade-1)

Applications

◼ Automotive Applications

◼ Advanced Driver Assistance Systems (ADAS)

◼ Camera Systems such as Security Camera

◼ Industrial Applications

Cypress Semiconductor Corporation

Document Number: 002-03341 Rev.*I

•

198 Champion Court

•

San Jose, CA 95134-1709

•

408-943-2600

Revised January 16, 2020

�S6BP401A

More Information

Cypress provides a wealth of data at www.cypress.com/pmic to help you to select the right PMIC device for your design, and to help

you to quickly and effectively integrate the device into your design. Following is an abbreviated list for S6BP401A:

◼ Overview: Automotive PMIC Portfolio, Automotive PMIC

Roadmap

◼ Product Selector:

S6BP401A:

6 ch Automotive PMIC for ADAS

◼ Application Notes: Cypress offers S6BP401A application

notes. Recommended application notes for getting started

with S6BP401A are:

AN98649: How to Design a Power Management System

AN201006: Thermal Considerations and Parameters

Document Number: 002-03341 Rev.*I

◼ Evaluation Kit Operation Manual:

S6SBP401AM2SA1001:

ADAS platform

Power block for automotive

◼ Related Products:

S6BP201A,

S6BP202A, S6BP203A:

1 ch Buck-Boost Automotive PMIC

S6BP501A, S6BP502A:

3 ch Automotive PMIC for Instrument Cluster

Page 2 of 41

�S6BP401A

Contents

Features................................................................................................................................................................................... 1

Applications ............................................................................................................................................................................ 1

Block Diagram......................................................................................................................................................................... 1

More Information .................................................................................................................................................................... 2

1.

Typical Application ........................................................................................................................................................ 4

2.

Pin Configuration ........................................................................................................................................................... 5

3.

Pin Functions ................................................................................................................................................................. 6

4.

Preset Output Voltage.................................................................................................................................................... 7

5.

Architecture Block Diagram .......................................................................................................................................... 9

6.

Absolute Maximum Ratings ........................................................................................................................................ 11

7.

Recommended Operating Conditions ........................................................................................................................ 12

8.

Electrical Characteristics ............................................................................................................................................ 13

9.

Operating Mode List..................................................................................................................................................... 18

10. Function ........................................................................................................................................................................ 19

10.1 Turning ON and OFF Sequence .................................................................................................................................. 19

10.2 Over Current Protection............................................................................................................................................... 21

10.3 Over Voltage Protection .............................................................................................................................................. 21

10.4 Thermal Shutdown (TSD) ............................................................................................................................................ 22

10.5 Under Voltage Lockout (UVLO) ................................................................................................................................... 22

10.6 Soft-Start Operation..................................................................................................................................................... 22

10.7 Discharge Operation.................................................................................................................................................... 23

10.8 Power Good Monitor and Reset Function.................................................................................................................... 24

10.9 Watchdog Timer .......................................................................................................................................................... 26

10.10 Internal Linear Regulator Output (VREG) .................................................................................................................... 29

11. Application Circuit Example........................................................................................................................................ 30

12. Reference Data ............................................................................................................................................................. 32

13. Ordering Information ................................................................................................................................................... 35

14. Package Dimensions ................................................................................................................................................... 36

15. Major Changes ............................................................................................................................................................. 37

Document History ................................................................................................................................................................. 38

Document Number: 002-03341 Rev.*I

Page 3 of 41

�S6BP401A

1. Typical Application

Figure 1-1 Typical Application

Document Number: 002-03341 Rev.*I

Page 4 of 41

�S6BP401A

2. Pin Configuration

LDO2

PVCCL2

PVCCL1

LDO1

VCC

PG1

VREG

PG2

CP1

GND

(Corner Pad)

PGL2

Figure 2-1 Pin Configuration

40

39

38

37

36

35

34

33

32

31

CP4

(Corner Pad)

PG4

1

30

FB1

FB4

2

29

PVCC1

PVCC4

3

28

LX1

LX4

4

27

PGND1

PGND4

5

26

PGND2

PGND3

6

25

PGND2

LX3

7

24

LX2

PVCC3

8

23

LX2

FB3

9

22

PVCC2

PG3

10

21

PVCC2

Document Number: 002-03341 Rev.*I

11

12

13

14

15

16

17

18

19

20

WDI

RST

ENL2

ENL1

EN4

EN3

EN2

EN1

FB2

CP2

EP (Exposed Pad)

SYNC

(Corner Pad)

Top View

CP3

(Corner Pad)

Page 5 of 41

�S6BP401A

3. Pin Functions

Table 3-1 Pin Functions

Functional

Block

DD1

DD2

DD3

DD4

LD1

LD2

WDT

Pin Number

Pin Name

I/O

19

EN1

I

Enable input terminal of DD1.

Pin Setting When

Not Being Used

Ground

30

FB1

I

Output voltage feedback terminal of DD1.

Ground

33

PG1

O

Power good output terminal of DD1.

Ground

29

PVCC1

-

Power supply terminal of DD1.

VCC

Leave pin open

Description

28

LX1

O

Inductor connect terminal of DD1.

27

PGND1

-

Power ground terminal of DD1.

Ground

18

EN2

I

Enable input terminal of DD2.

Ground

20

FB2

I

Output voltage feedback terminal of DD2.

Ground

31

PG2

O

Power good output terminal of DD2.

Ground

21, 22

PVCC2

-

Power supply terminal of DD2.

VCC

23, 24

LX2

O

Inductor connect terminal of DD2.

Leave pin open

25, 26

PGND2

-

Power ground terminal of DD2.

Ground

17

EN3

I

Enable input terminal of DD3.

Ground

9

FB3

I

Output voltage feedback terminal of DD3.

Ground

10

PG3

O

Power good output terminal of DD3.

Ground

8

PVCC3

-

Power supply terminal of DD3.

VCC

Leave pin open

7

LX3

O

Inductor connect terminal of DD3.

6

PGND3

-

Power ground terminal of DD3.

Ground

16

EN4

I

Enable input terminal of DD4.

Ground

2

FB4

I

Output voltage feedback terminal of DD4.

Ground

1

PG4

O

Power good output terminal of DD4.

Ground

3

PVCC4

-

Power supply terminal of DD4.

VCC

4

LX4

O

Inductor connect terminal of DD4.

Leave pin open

5

PGND4

-

Power ground terminal of DD4.

Ground

15

ENL1

I

Enable input terminal of LD1.

Ground

36

PVCCL1

-

Power supply terminal of LD1.

VCC

35

LDO1

O

Output terminal of LD1.

Leave pin open

14

ENL2

I

Enable input of LD2.

Ground

40

PGL2

O

Power good output terminal of LD2.

Ground

37

PVCCL2

-

Power supply terminal of LD2.

VCC

38

LDO2

O

Output terminal of LD2.

Leave pin open

12

WDI

I

Trigger input terminal of WDT.

Ground

13

RST

O

Reset input terminal of WDT.

Ground

Ground

SYNC

11

SYNC

I

External clock input terminal.

-

34

VCC

-

−

-

32

VREG

O

Power supply terminal for analog controller.

Internal 1.8 V supply voltage capacitor terminal. Do NOT

supply or load this terminal externally.

-

39

GND

-

Ground terminal for analog controller.

−

-

EP

EP

-

Exposed pad. Connect to ground plane.

−

-

CP1, CP2,

CP3, CP4

-

Corner pad for reinforcing attachment to a board.

Connect to ground plane.

−

Document Number: 002-03341 Rev.*I

CP

−

Page 6 of 41

�S6BP401A

4. Preset Output Voltage

Table 4-1 Preset Output Voltage (Buck DC/DC Converter)

Channel

DD1

DD2

DD3

DD4

Preset Output

Voltage [V]

1.200

1.225

1.250

1.275

1.300

1.325

1.500

1.525

1.550

1.575

1.000

1.025

1.050

1.075

1.100

1.125

1.150

1.175

1.200

1.225

1.250

1.275

1.200

1.225

1.250

1.275

1.500

1.525

1.550

1.575

1.800

1.825

1.850

1.875

2.500

2.525

2.550

2.575

3.300

3.325

3.350

3.375

3.400

Soft-start Time

[ms]

1.200

1.225

1.250

1.275

1.300

1.325

1.500

1.525

1.550

1.575

1.000

1.025

1.050

1.075

1.100

1.125

1.150

1.175

1.200

1.225

1.250

1.275

1.200

1.225

1.250

1.275

1.500

1.525

1.550

1.575

1.800

1.825

1.850

1.875

2.500

2.525

2.550

2.575

3.300

3.325

3.350

3.375

3.400

Maximum Output

Current [mA]

Under Voltage

Threshold [%]

Over Voltage

Threshold [%]

2000

94.0

106.0

3000

94.0

106.0

2000

95.2

106.0

1000

95.5

106.0

Notes:

−

Soft-start time values are at fOSC = 2.1 MHz

−

See 8. Electrical Characteristics for the minimum or maximum values of output voltage, under voltage threshold and over

voltage threshold.

Document Number: 002-03341 Rev.*I

Page 7 of 41

�S6BP401A

Table 4-2 Preset Output Voltage (LDO)

Channel

LD1

LD2

Preset Output

Voltage [V]

Soft-start Time

[ms]

3.300

3.300

3.325

3.325

3.350

3.350

3.375

3.375

3.400

3.400

1.200

1.200

1.225

1.225

1.250

1.250

1.275

1.275

1.800

1.800

1.825

1.825

1.850

1.850

1.875

1.875

2.800

2.800

2.825

2.825

2.850

2.850

2.875

2.875

Maximum Output

Current [mA]

Under Voltage

Threshold [%]

Over Voltage

Threshold [%]

200

94.0

106.0

500

94.0

106.0

Notes:

−

Soft-start time values are at fOSC = 2.1 MHz

−

See 8. Electrical Characteristics for the minimum or maximum values of output voltage, under voltage threshold and over

voltage threshold.

Document Number: 002-03341 Rev.*I

Page 8 of 41

�S6BP401A

5. Architecture Block Diagram

Figure 5-1 Architechture Block Diagram

>

FB1

PVCC1

Discharge

PWM

Comparator

Low Priority

en1

Voltage

Reference

PWM

AntiLogic

Shoot

Control Through

Error

Amplifier

Slope

Compensation

Power Good

Monitor

LX1

Current

Sense

PGND1

pg1

Peak Current

Comparator

ss1

clk

>

FB2

PVCC2

Discharge

en2

Voltage

Reference

PVCC2

PWM

Comparator

Low Priority

PWM

AntiLogic

Shoot

Control Through

Error

Amplifier

Slope

Compensation

Power Good

Monitor

LX2

LX2

Current

Sense

PGND2

PGND2

pg2

Peak Current

Comparator

ss2

clk

>

FB3

PVCC3

Discharge

PWM

Comparator

Low Priority

en3

Voltage

Reference

PWM

AntiLogic

Shoot

Control Through

Error

Amplifier

Slope

Compensation

Power Good

Monitor

LX3

Current

Sense

PGND3

pg3

Peak Current

Comparator

ss3

clk

>

FB4

PVCC4

Discharge

PWM

Comparator

Low Priority

en4

Voltage

Reference

Power Good

Monitor

pg4

ss4

PWM

AntiLogic

Shoot

Control Through

Error

Amplifier

Slope

Compensation

LX4

Current

Sense

PGND4

Peak Current

Comparator

clk

Document Number: 002-03341 Rev.*I

Page 9 of 41

�S6BP401A

>

Low Priority

PVCCL1

Voltage

Reference

LDO1

Power Good

Monitor

Discharge

pgl1

ssl1

enl1

>

Low Priority

PVCCL2

Voltage

Reference

LDO2

Power Good

Monitor

Discharge

pgl2

ssl2

enl2

>

>

PG1

Thermal

Shutdown

PG2

VCC

Under Voltage

Lockout

PG3

EN1

en1

EN2

en2

PG4

PGL2

EN3

en3

pg1

pg2

pg3

pg4

pgl2

Control

Logic

EN4

en4

ENL1

enl1

ENL2

enl2

>

RST

Watchdog

Timer

clk

pgl1

WDI

ss1

ss2

ss3

Soft-Start

Control

ss4

ssl1

enl2

clk

VCC

VCC

VREG

SYNC

Linear

Regulator

Power Good

Monitor

Oscillator

with Synchronization

clk

GND

Document Number: 002-03341 Rev.*I

Page 10 of 41

�S6BP401A

6. Absolute Maximum Ratings

Table 6-1 Absolute Maximum Ratings

Parameter

Symbol

VVCC

Power supply voltage

VPVCC

VPVCCL

VEN

VWDI

Input voltage

VSYNC

VFB

VPG

VRST

Condition

VCC

PVCC1, PVCC2, PVCC3, PVCC4

PVCCL1, PVCCL2

EN1, EN2, EN3, EN4, ENL1, ENL2

WDI

SYNC

FB1, FB2, FB3, FB4

PG1, PG2, PG3, PG4, PGL2

Min

-0.3

Rating

Max

+6.9

Unit

V

-0.3

-0.3

+6.9

+6.9

V

V

-0.3

-0.3

+6.9

+6.9

V

V

-0.3

-0.3

+6.9

+6.9

V

V

-0.3

+6.9

V

RST

-0.3

+6.9

V

LX voltage

LX1, LX2, LX3, LX4

VLX

-0.3

+6.9

V

PVCC1 -VCC, PVCC2-VCC,

VPVCC-VCC

-0.3

+0.3

V

PVCC3-VCC, PVCC4-VCC

PGND1-GND, PGND2-GND,

VPGND-GND

-0.3

+0.3

V

PGND3-GND, PGND4-GND

PVCC1-LX1, PVCC2-LX2,

Voltage difference

VPVCC-LX

-0.3

+6.9

V

PVCC3-LX3, PVCC4-LX4

VCC-EN1, VCC-EN2, VCC-EN3,

VCC-EN4, VCC-EN1L, VCC-EN2L,

VVCC-INPUT

-0.3

+6.9

V

VCC-WDI, VCC-SYNC, VCC-FB1,

VCC-FB2, VCC-FB3, VCC-FB4

TA ≤ + 25 °C,

Power dissipation

PD

6940

mW

Thermal resistance (θJA): 18 °C /W (*1)

Junction temperature

TJ

-40

+150

°C

Storage temperature

TSTG

-55

+150

°C

*1: When the IC is mounted on 76.2 mm × 114.3 mm four-layer epoxy board. IC is mounted on a four-layer epoxy board, which

terminal bias, and the IC’s thermal pad is connected to the epoxy board.

WARNING

1. Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or

temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

Maximum Power dissipation PD

[mW]

Figure 6-1 Maximum Power Dissipation - Operating Ambient Temperature Characteristics

8000

7000

6000

5000

4000

3000

2000

1000

0

-60 -40 -20

0

20 40 60 80 100 120 140

Ambient Temperature TA [°C]

Document Number: 002-03341 Rev.*I

Page 11 of 41

�S6BP401A

7. Recommended Operating Conditions

Table 7-1 Recommended Operating Conditions

Parameter

Power supply voltage

Input voltage

Symbol

Min

Value

Typ

Max

Unit

VVCC

VPVCC

VCC

PVCC1, PVCC2, PVCC3, PVCC4

+4.5

-

+5.0

VVCC

+5.5

-

V

V

VPVCCL

VEN

PVCCL1, PVCCL2

EN1, EN2, EN3, EN4, ENL1, ENL2

WDI

+2.97

0

+5.0

-

VVCC

VVCC

V

V

0

0

-

VVCC

VVCC

V

V

0

0

-

VVCC

+5.5

V

V

0

-

+5.5

V

-40

+25

+125

°C

VWDI

VSYNC

VFB

VPG

VRST

Operating ambient

temperature

Condition

TA

SYNC

FB1, FB2, FB3, FB4

PG1, PG2, PG3, PG4, PGL2

RST

-

WARNING:

1. The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of

the device's electrical characteristics are warranted when the device is operated under these conditions.

2.

Any use of semiconductor devices will be under their recommended operating condition.

3.

Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device

failure.

4.

No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you

are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

Document Number: 002-03341 Rev.*I

Page 12 of 41

�S6BP401A

8. Electrical Characteristics

VVCC = VPVCC = 5.0 V, VPVCCL = 5.0 V, TA = TJ = -40 to +125 °C, unless otherwise noted. Typical values are at TA = +25 °C.

Table 8-1 Electrical Characteristics

Parameter

Symbol

Condition

Min

Value

Typ

Max

Unit

-

1

10

µA

3.80

0.27

3.95

0.30

4.10

0.33

V

V

Supply Current

VCC pin,

VEN1 = VEN2 = VEN3 = VEN4 = VENL1 =

VENL2 = 0 V

UVLO: Under Voltage Lockout (VCC)

Threshold voltage

VUVLOF

VVCC falling, UVLO stop voltage

Shutdown current

Hysteresis

IVCCS

VUVHYS

-

TSD: Thermal Shutdown

Shutdown temperature

TTSD

Hysteresis

TTSDHYS

Temperature rising

-

165 (*1)

-

°C

-

-

10 (*1)

-

°C

Enable Inputs (EN1, EN2, EN3, EN4, ENL1, ENL2)

Input high voltage

VIHEN

-

2.0

-

VVCC

V

Input low voltage

-

0

-

0.4

V

33

50

100

µA

50

100

150

kΩ

1.74

1.80

1.86

V

5

-

-

mA

1.86

1.81

1.67

1.62

1.92

1.87

1.73

1.68

1.98

1.93

1.79

1.74

V

V

V

V

2.0

2.1

2.2

MHz

2.0

0

33

50

1.8

-

50

100

2.1

fSYNC

VVCC

0.4

100

150

2.4

-

V

V

µA

kΩ

MHz

MHz

Input current

Pull down resistance

VILEN

IIHEN

RPDEN

VEN = 5.0 V

-

Internal Linear Regulator Output (VREG)

Output voltage

VVREG

VVCC = 5.0 V

Maximum output

IVREG

VVCC = 5.0 V

current

VVREGOVR VVREG rising, Power fail

Over voltage lockout

threshold

VVREGOVF VVREG falling, Power good

VVREGUVR VVREG rising, Power good

Under voltage lockout

threshold

VVREGUVF VVREG falling, Power fail

Oscillator

Switching frequency

fOSC

Synchronization Input (SYNC)

Input high voltage

VIHSYNC

Input Low voltage

VILSYNC

Input current

IIHSYNC

VEN = 5.0 V

Pull down resistance

RPDSYNC

Input frequency

fSYNC

Switching frequency

fOSC

-

Document Number: 002-03341 Rev.*I

Page 13 of 41

�S6BP401A

Parameter

Symbol

Condition

Power Good Monitor (PG1, PG2, PGL2)

Over voltage

Ratio of power fail threshold to VOUT1, VOUT2,

VPGOV

threshold

VOUTL2 rising

Over voltage

VPGOVHYS

hysteresis

Under voltage

Ratio of power fail threshold to VOUT1, VOUT2,

VPGUV

threshold

VOUT3 falling

Under voltage

VPGUVHYS

hysteresis

Leakage current

ILEAKPG

VPG = 5.0 V

Output low voltage

VOLPG

IPG = 3 mA

Propagation time

TPPG

5 % outside of the threshold, Power fail

Power-on reset time

TRPG

Power good

Power Good Monitor (PG3)

Over voltage

VPGOV

Ratio of power fail threshold to VOUT3 rising

threshold

Over voltage

VPGOVHYS

hysteresis

Under voltage

VPGUV

Ratio of power fail threshold to VOUT3 falling

threshold

Under voltage

VPGUVHYS

hysteresis

Leakage current

ILEAKPG

VPG = 5.0 V

Output low voltage

VOLPG

IPG = 3 mA

Propagation time

TPPG

5 % outside of the threshold, Power fail

Power-on reset time

TRPG

Power good

Power Good Monitor (PG4)

Over voltage

VPGOV

Ratio of power fail threshold to VOUT4 rising

threshold

Over voltage

VPGOVHYS

hysteresis

Under voltage

VPGUV

Ratio of power fail threshold to VOUT4 falling

threshold

Under voltage

VPGUVHYS

hysteresis

Leakage current

ILEAKPG

VPG = 5.0 V

Output low voltage

VOLPG

IPG = 3 mA

Propagation time

TPPG

5 % outside of the threshold, Power fail

Power-on reset time

TRPG

Power good

Reset (RST)

Over voltage

VRSOV

Ratio of power fail threshold to VOUTL1 rising

threshold

Over voltage

VRSOVHYS

hysteresis

Under voltage

VRSUV

Ratio of power fail threshold to VOUTL1 falling

threshold

Under voltage

VRSUVHYS

hysteresis

Leakage current

ILEAKRST

VRST = 5.0 V

Output low voltage

VOLRST

IPG = 3 mA

Propagation time

TPRST

5 % outside of the threshold, Power fail

Power-on reset time

TRD

Power good

Document Number: 002-03341 Rev.*I

Min

Value

Typ

Max

Unit

104.5

106.0

107.5

%

0.5

1.0

1.5

%

92.5

94.0

95.5

%

0.5

1.0

1.5

%

8

0.15

4 (*1)

10

1

0.30

8 (*1)

12

µA

V

µs

ms

104.5

106.0

107.5

%

0.5

1.0

1.5

%

93.7

95.2

96.7

%

0.5

1.0

1.5

%

8

0.15

4 (*1)

10

1

0.30

8 (*1)

12

µA

V

µs

ms

104.5

106.0

107.5

%

0.5

1.0

1.5

%

94.0

95.5

97.0

%

0.5

1.0

1.5

%

8

0.15

4 (*1)

10

1

0.30

8 (*1)

12

µA

V

µs

ms

104.5

106.0

107.5

%

0.5

1.0

1.5

%

92.5

94.0

95.5

%

0.5

1.0

1.5

%

25.6

0.15

4 (*1)

32.0

1

0.30

8 (*1)

38.4

µA

V

µs

ms

Page 14 of 41

�S6BP401A

Parameter

Symbol

Watchdog Timer (WDI)

Watchdog sampling

TSAM

time

Ignore window time

TIW

Open window time

TOW

Long open window

TLOW

time

Closed window time

TCW

Window watchdog

TWD

trigger time

Input high voltage

VIHWDI

Input low voltage

VILWDI

Input current

IIHWDI

Pull down resistance

RPDWDI

DD1: Buck DC/DC Converter

Output voltage

VOUT1

accuracy

DC regulation

VREG1

FB1 input resistance

RFB1

RONHS1

Switching FET

ON resistance

RONLS1

Switching FET

ILEAK1

leakage current

Maximum output

IOUT1

current

LX1 peak current limit

ILIMIT1

Over voltage

VOVP1

protection threshold

Over voltage

VOVPHYS1

protection hysteresis

FB1 discharge

RDIS1

resistance

Soft-start time

TCOESS1

coefficient

DD2: Buck DC/DC Converter

Output voltage

VOUT2

accuracy

DC regulation

VREG2

FB2 input resistance

Switching FET

ON resistance

Switching FET

leakage current

Maximum output

current

LX2 peak current limit

Over voltage

protection threshold

Over voltage

protection hysteresis

FB2 discharge

resistance

Soft-start time

coefficient

RFB2

RONHS2

RONLS2

Condition

Min

Value

Typ

Max

Unit

-

0.40

0.50

0.60

ms

-

25.6

25.6

32.0

32.0

38.4

38.4

ms

ms

-

102.4

128.0

153.6

ms

-

25.6

32.0

38.4

ms

-

38.4

48

51.2

ms

-

2.0

0

33

50

50

100

VVCC

0.4

100

150

V

V

µA

kΩ

-1.8

0

+1.8

%

-15 (*1)

0

+5 (*1)

mV

95

-

190

100

65

285

190

125

kΩ

mΩ

mΩ

-

1

10

µA

2 (*1)

-

-

A

2.5 (*1)

-

-

A

125.0

130.0

135.0

%

-

2.0

5.0

8.0

%

-

160

400

640

Ω

0.9

1.0

1.1

ms/V

-1.8

0

+1.8

%

-15 (*1)

0

+5 (*1)

mV

95

-

190

85

55

285

165

105

kΩ

mΩ

mΩ

-

1

10

µA

3 (*1)

-

-

A

3.5 (*1)

-

-

A

125.0

130.0

135.0

%

VWDI = 5.0 V

VVCC = 5.0 V,

IOUT1 = 10 mA

VVCC = VPVCC1 = 4.5 to 5.5 V,

IOUT1 = 0 to 2.0 A

VFB1 = 2.0 V

ILX1 = 20 mA (PVCC1 to LX1)

ILX1 = -20 mA (LX1 to PGND1)

IPVCC1 = 5.0 V

L = 1.5 µH

L = 1.5 µH

VOUT1 rising, Switching termination

threshold

TSS1 = VOUT1 x TCOESS1

VVCC = 5.0 V,

IOUT2 = 10 mA

VVCC = VPVCC2 = 4.5 to 5.5 V

IOUT2 = 0 to 3.0 A

VFB2 = 2.0 V

ILX2 = 20 mA (PVCC2 to LX2)

ILX2 = -20 mA (LX2 to PGND2)

ILEAK2

IPVCC2 = 5.0 V

IOUT2

L = 1.5 µH

ILIMIT2

L = 1.5 µH

VOUT2 rising, Switching termination

threshold

VOVP2

VOVPHYS2

-

2.0

5.0

8.0

%

RDIS2

-

160

400

640

Ω

0.9

1.0

1.1

ms/V

TCOESS2

Document Number: 002-03341 Rev.*I

TSS2 = VOUT2 x TCOESS2

Page 15 of 41

�S6BP401A

Parameter

DD3: Buck DC/DC Converter

Output voltage

VOUT3

accuracy

DC regulation

VREG3

FB3 input resistance

RFB3

RONHS3

Switching FET

ON resistance

RONLS3

Switching FET

ILEAK3

leakage current

Maximum output

IOUT3

current

LX3 peak current limit

ILIMIT3

Over voltage

VOVP3

protection threshold

Over voltage

VOVPHYS3

protection hysteresis

FB3 discharge

RDIS3

resistance

Soft-start time

TCOESS3

coefficient

DD4: Buck DC/DC Converter

Output voltage

VOUT4

accuracy

DC regulation

VREG4

FB4 input resistance

Switching FET

ON resistance

Switching FET

leakage current

Maximum output

current

LX4 peak current limit

Over voltage

protection threshold

Over voltage

protection hysteresis

FB4 discharge

resistance

Soft-start time

coefficient

RFB4

RONHS4

RONLS4

Min

Value

Typ

Max

Unit

-1.8

0

+1.8

%

-15 (*1)

0

+5 (*1)

mV

95

-

190

100

65

285

190

125

kΩ

mΩ

mΩ

-

1

10

µA

2 (*1)

-

-

A

2.5 (*1)

-

-

A

125.0

130.0

135.0

%

-

2.0

5.0

8.0

%

-

160

400

640

Ω

0.9

1.0

1.1

ms/V

-1.8

0

+1.8

%

-15 (*1)

0

+5 (*1)

mV

95

-

190

100

65

285

190

125

kΩ

mΩ

mΩ

-

1

10

µA

1 (*1)

-

-

A

1.5 (*1)

-

-

A

125.0

130.0

135.0

%

Condition

Symbol

VVCC = 5.0 V,

IOUT3 = 10 mA

VVCC = VPVCC3 = 4.5 to 5.5 V,

IOUT3 = 0 to 2.0 A

VFB3 = 2.0 V

ILX3 = 20 mA (PVCC3 to LX3)

ILX3 = -20 mA (LX3 to PGND3)

IPVCC3 = 5.0 V

L = 1.5 µH

L = 1.5 µH

VOUT3 rising, Switching termination

threshold

TSS3 = VOUT3 × TCOESS3

VVCC = 5.0 V,

IOUT4 = 10 mA

VVCC = VPVCC4 = 4.5 to 5.5 V,

IOUT4 = 0 to 1.0 A

VFB4 = 2.0 V

ILX4 = 20 mA (PVCC4 to LX4)

ILX4 = -20 mA (LX4 to PGND4)

ILEAK4

IPVCC4 = 5.0 V

IOUT4

L = 1.5 µH

ILIMIT4

L = 1.5 µH

VOUT4 rising, Switching termination

threshold

VOVP4

VOVPHYS4

-

2.0

5.0

8.0

%

RDIS4

-

160

400

640

Ω

0.9

1.0

1.1

ms/V

TCOESS4

Document Number: 002-03341 Rev.*I

TSS4 = VOUT4 × TCOESS4

Page 16 of 41

�S6BP401A

Parameter

LD1: LDO Regulator

Output voltage

accuracy

DC regulation

Output FET

leakage current

Maximum output

current

Output current limit

LDO1 discharge

resistance

Soft-start time

coefficient

LD2: LDO Regulator

Output voltage

accuracy

DC regulation

Output FET

leakage current

Maximum output

current

Output current limit

Symbol

VOUTL1

VREGL1

ILEAKL1

IOUTL1

ILIMITL1

Condition

VVCC = 5.0 V,

IOUTL1 = 10 mA

VVCC = 4.5 to 5.5 V, VPVCCL1 = 2.97 to VVCC

IOUTL1 = 0 to IOUTL1

IPVCCL1 = 5.0 V

VPVCCL1 - VOUTL1 ≥ 1.6 V

0.17 V ≤ VPVCCL1 - VOUTL1 < 1.6 V

VPVCCL1 - VOUTL1 ≥ 1.6 V

0.17 V ≤ VPVCCL1 - VOUTL1 < 1.6 V

RDISL1

TCOESSL1

VOUTL2

VREGL2

ILEAKL2

IOUTL2

ILIMITL2

TSSL1 = VOUTL1 × TCOESSL1

VVCC = 5.0 V,

IOUTL2 = 10 mA

VVCC = 4.5 to 5.5 V, VPVCCL2 = 2.97 to VVCC

IOUTL2 = 0 to IOUTL2

IPVCCL2 = 5.0 V

VPVCCL2 - VOUTL2 ≥ 1.6 V

0.17 V ≤ VPVCCL2 - VOUTL2 < 1.6 V

VPVCCL2 - VOUTL2 ≥ 1.6 V

0.17 V ≤ VPVCCL2 - VOUTL2 < 1.6 V

Min

Value

Typ

Max

Unit

-1.8

0

+1.8

%

-15 (*1)

0

+5 (*1)

mV

-

1

10

µA

200 (*1)

100 (*1)

210 (*1)

105 (*1)

-

-

mA

mA

mA

mA

160

400

640

Ω

0.9

1.0

1.1

ms/V

-1.8

0

+1.8

%

-15 (*1)

0

+5 (*1)

mV

-

1

10

µA

500 (*1)

400 (*1)

525 (*1)

420 (*1)

-

-

mA

mA

mA

mA

400

640

Ω

1.0

1.1

ms/V

LDO2 discharge

RDISL2

160

resistance

Soft-start time

TCOESSL2 TSSL2 = VOUTL2 × TCOESSL2

0.9

coefficient

*1: The electrical characteristic is ensured by statistical characterization and indirect tests.

Document Number: 002-03341 Rev.*I

Page 17 of 41

�S6BP401A

9. Operating Mode List

Table 9-1 shows the operation list of S6BP401A.

Table 9-1 Operation Mode List

Condition

Operating Block

TJ

SYNC

ENL1

< TTSD

L or H

L

EN1/

EN2/

EN3/

EN4/

ENL2

L

OFF

OFF

< TTSD

L or H

L

H

ON

ON

< TTSD

L or H

H

L

ON

< TTSD

L or H

H

H

ON

< TTSD

clock

L

L

< TTSD

clock

L

< TTSD

clock

H

< TTSD

clock

H

H

ON

ON

ON

ON

ON

ON

≥ TTSD

L or H

L

L

OFF

OFF

OFF

OFF

OFF

OFF

≥ TTSD

L or H

L

H

ON

ON

OFF

OFF

OFF

OFF

≥ TTSD

L or H

H

L

ON

ON

OFF

OFF

OFF

OFF

≥ TTSD

L or H

H

H

ON

ON

OFF

OFF

OFF

OFF

≥ TTSD

clock

L

L

OFF

OFF

OFF

OFF

OFF

OFF

≥ TTSD

clock

L

H

ON

ON

OFF

OFF

OFF

OFF

≥ TTSD

clock

H

L

ON

ON

OFF

OFF

OFF

OFF

≥ TTSD

clock

H

H

ON

ON

OFF

OFF

OFF

OFF

Document Number: 002-03341 Rev.*I

Freq.

Sync.

LD1

OFF

OFF

OFF

DD1/

DD2/

DD3/

DD4/

LD2

OFF

OFF

OFF

OFF

ON

ON

ON

OFF

ON

OFF

ON

ON

OFF

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

H

ON

ON

OFF

ON

OFF

ON

L

ON

ON

ON

ON

ON

OFF

Chip

Control

WatchVREG LDO dog Trigger

Monitor

Page 18 of 41

�S6BP401A

10. Function

10.1 Turning ON and OFF Sequence

When all of the enable input terminals (EN1, EN2, EN3, EN4, ENL1 and ENL2) are “Low”, the device is in shutdown state. When

any one or more than one of them go “High,” the device is initialized, then the internal linear regulator (VREG) starts generating 1.8

V internal supply voltage. After that, each DC/DC converters and LDOs state is transitioned to the state which can be started.

In order for the device to start, the VCC terminal voltage must be higher than the under-voltage lockout threshold (VUVLOF + VUVHYS).

Figure 10-1 depicts the turning-on and off sequence where the enable signals are connected to VCC. Figure 10-2 depicts that where

the enable signals are respectively controlled after the IC is powered.

Figure 10-1 Turning ON and OFF Sequence (where EN1 and ENL1 are Connected to VCC)

VVCC

VUVLOF

VUVLOF + VUVHYS

VEN1

VENL1

VVREG

VOUT1

VPGUV+VPGUVHYS

10%

TYP:40.5ms(*1)

VRSUV+VRSUVHYS

VOUTL1

10%

TYP:0.92ms(*1)

VRST

Initialization

(TYP:1ms)

TRD

Time

*1: Given that the system employs the same external parts with those specified in “11. Application Circuit Example”.

Document Number: 002-03341 Rev.*I

Page 19 of 41

�S6BP401A

Figure 10-2 Turning ON and OFF Sequence (where EN1 and ENL1 are Respectively Controlled)

VVCC

VUVLOF + VUVHYS

VEN1

VENL1

VVREG

VPGUV+VPGUVHYS

VOUT1

10%

TYP:40.5ms(*1)

VRSUV+VRSUVHYS

VOUTL1

10%

TYP:0.92ms(*1)

VRST

Initialization

(TYP:1ms)

TRD

Initialization

(TYP:1ms)

Time

*1: Given that the system employs the same external parts with those specified in “11. Application Circuit Example”.

Document Number: 002-03341 Rev.*I

Page 20 of 41

�S6BP401A

10.2 Over Current Protection

The over current protection of the DC/DC converters detects the inductor peak current with on-resistance of Internal high side

switching FET. If the DC/DC converter is over current state, the corresponding output voltage is decreased. If the device returns

from over current state, the output voltage is target voltage.

Each LDOs equips foldback current limiter in order to prevent the IC itself from being damaged or destroyed. The curve of output

current and output voltage in over current state is shown in the Figure 10-3.

Figure 10-3 LDO Foldback Over Current Protection Characteristic

Voltage

VOUTL1

VOUTL2

Current

ISL1

ISL2

IOUTL1

IOUTL2

ILIMITL1

ILIMITL2

10.3 Over Voltage Protection

The over voltage protection of the DC/DC converters detects the output voltage. If the DC/DC converter is over voltage state, the

corresponding channel stops switching and inductor connecting terminal (LX1, LX2, LX3, LX4) is held at high impedance. If the

device returns from over voltage state, the channel returns switching automatically.

Figure 10-4 Over Voltage Protection Timing Chart

VEN1,VEN2,

VEN3,VEN4

VOVPHYS1, VOVPHYS2,

VOVPHYS3, VOVPHYS4

VOVP1, VOVP2,

VOVP3, VOVP4

VPGOV

VOUT1,VOUT2,

VOUT3,VOUT4

VPGOVHYS

TRPG

TPPG

TRPG

VPG1,VPG2,

VPG3,VPG4

LX1, LX2,

LX3, LX4

Hi-Z

Discharge

ON

Switching

Hi-Z

Switching

OFF

Time

Document Number: 002-03341 Rev.*I

Page 21 of 41

�S6BP401A

10.4 Thermal Shutdown (TSD)

If the junction temperature reaches +165 °C, all DC/DC converters and LDOs stop outputting voltage. Then the discharge operation

is carried out to discharge the output capacitor (The discharge operation continues until the state of the thermal shutdown released.)

When the junction temperature drops below +155 °C, the soft-starters activate regulators and start generating voltage gradually if

the enable is "High."

Figure 10-5 Thermal Shutdown Timing Chart

165 deg.

TJ

155 deg.

VEN1

VOUT1

Soft-Start

Soft-Start

Time

10.5 Under Voltage Lockout (UVLO)

If the VCC terminal voltage (VVCC) drops below the lower UVLO threshold (VUVLOF), all DC/DC converters (DD1, DD2, DD3, DD4),

LDOs (LD1, LD2), windowed watchdog timer (WDT) and the internal linear regulator (VREG) stop working. When the VCC terminal

voltage (VVCC) is raised higher than the higher UVLO threshold (VUVLOF + VUVHYS), the device returns automatically.

10.6 Soft-Start Operation

S6BP401A equips load-independent soft-start function in order to prevent the DC/DC converters and LDOs from having rush current

at the start-up. The soft-start timing is shown in the Figure 10-6, and is given by the following equation;

𝑇𝑆𝑆 = 𝑉𝑂𝑈𝑇 × 𝑇𝐶𝑂𝐸𝑆𝑆 , where

TSS [ms] :

Soft-start time

VOUT [V] :

Output voltage (VOUT1, VOUT2, VOUT3, VOUT4, VOUTL1, VOUTL2)

TCOESS [ms/V] :

Soft-start time coefficient (TCOESS1, TCOESS2, TCOESS3, TCOESS4, TCOESSL1, TCOESSL2)

Document Number: 002-03341 Rev.*I

Page 22 of 41

�S6BP401A

Figure 10-6 Soft-Start Operation Timing Chart

VEN

VOUT(3)

VOUT(2)

VOUT(1)

VOUT

TSS=VOUT(1)×TCOESS

TSS=VOUT(2)×TCOESS

TSS=VOUT(3)×TCOESS

Time

10.7 Discharge Operation

When an enable signal goes “Low”, the corresponding output capacitor is discharged by the internal discharge resistor and the

output voltage is decreased gradually. Note that the discharge time is not consistent: it depends on the output load current.

As for a DC/DC converter, the output capacitor is discharged from FB1, FB2, FB3 and FB4 terminal to PGND1, PGND2, PGND3

and PGND4 terminal respectively. As for a LDO, the output capacitor is dis-charged from LDO1, LDO2 terminal to GND terminal.

The discharge time required to decrease the output voltage by 90 % without any explicit load given by the following equation;

𝑇𝐷𝐼𝑆 = 2.3 × 𝑅𝐷𝐼𝑆 × 𝐶𝑂𝑈𝑇 , where

TDIS [ms] :

Discharge time

RDIS [kΩ] :

Discharge resistance (RDIS1, RDIS2, RDIS3, RDIS4, RDISL1, RDISL2)

COUT [µF] :

Output capacitor

Figure 10-7 Discharge Diagram (DC/DC Converter)

PVCC1,PVCC2,

PVCC3,PVCC4

Power

Supply

FB1,FB2,

FB3,FB4

Error Amp.

RDIS1,

RDIS2,

RDIS3,

RDIS4

LX1,LX2,

LX3,LX4

PWM

Control

PGND1,PGND2,

PGND3,PGND4

enable

Document Number: 002-03341 Rev.*I

Page 23 of 41

�S6BP401A

Figure 10-8 Discharge Diagram (LDO)

PVCCL1,PVCCL2

Power

Supply

LDO1,LDO2

RDISL1,

RDISL2

enable

10.8 Power Good Monitor and Reset Function

Each DC/DC converters and LDOs has power good function to indicate whether the output voltage is in the expected range. The

Table 10-1 describes the power good pin names and their functions of each DC/DC converters and LDOs. The Figure 10-9 and

Figure 10-10 depict power-good timing chart.

Table 10-1 Power Good Monitor and Reset Function Pin List

Channel Pin Name

DD1

DD2

DD3

DD4

Description

PG1

Enabling DD1 is followed by rising of the DD1 output voltage (VOUT1). Once VOUT1 reaches within the power

good range (VPGUV + VPGUVHYS < VOUT1 < VPGOV – VPGOVHYS), the power good monitor output (PG1 terminal)

changes its state from “Low” to “Open” after a power-on-reset time (TRPG). When VOUT1 is out of the power

good range (VOUT1 ≤ VPGUV or VOUT1 ≥ VPGOV), PG1 terminal changes its state from “Open” to “Low” after the

propagation delay (TPPG). The glitch within TPPG does not affect the power good monitor output.

PG2

Enabling DD2 is followed by rising of the DD2 output voltage (V OUT2). Once VOUT2 reaches within the power

good range (VPGUV + VPGUVHYS < VOUT2 < VPGOV – VPGOVHYS), the power good monitor output (PG2 terminal)

changes its state from “Low” to “Open” after a power-on-reset time (TRPG). When VOUT2 is out of the power

good range (VOUT2 ≤ VPGUV or VOUT2 ≥ VPGOV), PG2 terminal changes its state from “Open” to “Low” after the

propagation delay (TPPG). The glitch within TPPG does not affect the power good monitor output.

PG3

Enabling DD3 is followed by rising of the DD3 output voltage (V OUT3). Once VOUT3 reaches within the power

good range (VPGUV + VPGUVHYS < VOUT3 < VPGOV – VPGOVHYS), the power good monitor output (PG3 terminal)

changes its state from “Low” to “Open” after a power-on-reset time (TRPG). When VOUT3 is out of the power

good range (VOUT3 ≤ VPGUV or VOUT3 ≥ VPGOV), PG3 terminal changes its state from “Open” to “Low” after the

propagation delay (TPPG). The glitch within TPPG does not affect the power good monitor output.

PG4

Enabling DD4 is followed by rising of the DD4 output voltage (V OUT4). Once VOUT4 reaches within the power

good range (VPGUV + VPGUVHYS < VOUT4 < VPGOV – VPGOVHYS), the power good monitor output (PG4 terminal)

changes its state from “Low” to “Open” after a power-on-reset time (TRPG). When VOUT4 is out of the power

good range (VOUT4 ≤ VPGUV or VOUT4 ≥ VPGOV), PG4 terminal changes its state from “Open” to “Low” after the

propagation delay (TPPG). The glitch within TPPG does not affect the power good monitor output.

Document Number: 002-03341 Rev.*I

Page 24 of 41

�S6BP401A

Channel Pin Name

LD1

LD2

Description

RST

Enabling LD1 is followed by rising of the LD1 output voltage (VOUTL1). Once VOUTL1 reaches within the power

good range (VRSUV + VRSUVHYS < VOUTL1 < VRSOV - VRSOVHYS), the RST terminal changes its state from “Low”

to “Open” after a power-on-reset time (TRD). When VOUTL1 is out of the power good range (VOUTL1 ≤ VRSUV or

VOUTL1 ≥ VRSOV), RST terminal changes “Open” to “Low” after the propagation delay (T PRST). The glitch within

TPRST does not affect the power good monitor output.

PGL2

Enabling LD2 is followed by rising of the LD2 output voltage (VOUTL2). Once VOUTL2 reaches within the power

good range (VPGUV + VPGUVHYS < VOUTL2 < VPGOV – VPGOVHYS), the power good monitor output (PGL2

terminal) changes its state from “Low” to “Open” through the power-on-reset time (TRPG). When VOUTL2 is out

of the power good range (VOUTL2 ≤ VPGUV or VOUTL2 ≥ VPGOV), PGL2 terminal changes “Open” to “Low” after

the propagation delay (TPPG). The glitch within TPPG does not affect the power good monitor output.

Figure 10-9 Power-Good Monitor Output Timing Chart (PG1, PG2, PG3, PG4, PGL2)

VEN1,VEN2,

VEN3,VEN4,

VENL2

VOUT1,VOUT2,

VOUT3,VOUT4,

VOUTL2

VPGOVHYS

VPGOV

VPGUV

VPGUVHYS

Not reset

VPG1,VPG2,

VPG3,VPG4,

VPGL2

TRPG

< TPPG

< TPPG

TPPG

TRPG

TPPG

TRPG

Time

Figure 10-10 Power-Good Monitor Output Timing Chart (RST)

VENL1

VRSOVHYS

VRSOV

VOUTL1

VRSUV

VRSUVHYS

Not reset

VRST

TRD

Document Number: 002-03341 Rev.*I

< TPRST

< TPRST

TPRST

TRD

TPRST

TRD

Time

Page 25 of 41

�S6BP401A

10.9 Watchdog Timer

S6BP401A employs a digital windowed watchdog timer. The digital windowed watchdog timer starts monitoring trigger signal, when

the LD1 output voltage (VOUTL1) reaches the power good level after enabling LD1.

Figure 10-11 shows the state diagram of the digital watchdog timer. There are six states in the diagram. In the normal operation, the

state is expected to move back and forth between “CW” and “OW”,

At first, as described in the section 10.8, enabling LD1 brings “RESET” state, and the “RESET” state is kept for the “Reset Time

(TRD)” outputting “Low” from RST terminal.

In the second, after TRD in the “RESET” state, the state will transition to “Ignore Window (IW)”, and let RST terminal be “Open”. The

“IW” state will be elapsed in the “Ignore Window Time (T IW.)”

In the third, after elapsing, the state will transition to “Long Open Window (LOW)” state, and let RST terminal be “Open.” In this state,

a trigger signal is expected to be input: if an input trigger arrives, the state will immediately transition to the “Closed Window (CW)”

state. Without an input trigger in the “Long Open Window Time (TLOW,)” the state will be elapsed and will transition to “RESET” state.

In the “CW” state, a trigger signal is expected NOT to be input: if an input trigger arrives, the state will immediately transition to the

“RESET” state. Without an input trigger in the “Closed Window Time (T CW,)” the state will be elapsed and will transition to “Open

Window (OW)” state.

In the “OW” state, a trigger signal is expected to be input: if an input trigger arrives, the state will immediately transition to the

“Closed Window (CW)” state. Without an input trigger in the “Open Window Time (T OW,)” the state will be elapsed and will transition

to “RESET” state.

Figure 10-14 shows that to avoid wrong triggering due to glitch noise two “High” samples followed by two “Low” samples to input

WDI pin are decoded as a trigger.

In any states above, a power failure of LD1 will cause a transition to “OFF” state, and output “Low” from RST terminal until LD1 goes

well.

Figure 10-11 Watchdog Timer State Diagram

OFF

RST=Low

LD1 power good

LD1

power

fail

Reset

RST=Low

TRD timeout

No Trigger

(TLOW timeout)

LD1

power

fail

Trigger

No Trigger

(TOW timeout)

Trigger

IW

RST=open T timeout

IW

Long OW

RST=open Trigger

LD1 power fail

Document Number: 002-03341 Rev.*I

OW

RST=open

CW

RST=open

LD1 power fail

No Trigger

(TCW timeout)

LD1 power fail

Page 26 of 41

�S6BP401A

Figure 10-12 Window Watchdog Timing Chart (WDI)

VRSUVHYS

VOUTL1

TWD

Ignore

VWDI

State

OFF

Reset

Long

OW

IW

No

Trigger

No

No

Trigger

Trigger (Wrong)

CW

CW

OW

OW

Reset

VRSUV

Wrong

Trigger

IW

Long

OW

CW

Reset

IW

Long

Reset

OW

IW

VRST

TRD

TIW