S70GL02GP

2 Gbit, 3V Page Mode

S70GL-P MirrorBit® Flash

General Description

The Cypress S70GL02GP 2 Gbit Mirrorbit Flash device is fabricated on 90-nm process technology. This device offers a fast page

access time of 25 ns with a corresponding random access time of 110 ns. It features a Write Buffer that allows a maximum of 32

words/64 bytes to be programmed in one operation, resulting in faster effective programming time than standard single byte/word

programming algorithms. This makes the device an ideal product for today’s embedded applications that require higher density,

better performance and lower power consumption.

This document contains information for the S70GL02GP device, which is a dual die stack of two S29GL01GP die. For detailed

specifications, refer to the discrete die datasheet provided in Table 1.

Table 1. Affected Documents/Related Documents

Title

Publication Number

S29GL01GP, S29GL512P, S29GL256P, S29GL128P

1 Gbit, 512, 256, 128 Mbit, 3 V, Page Flash with 90 nm MirrorBit

Process Technology

002-00886

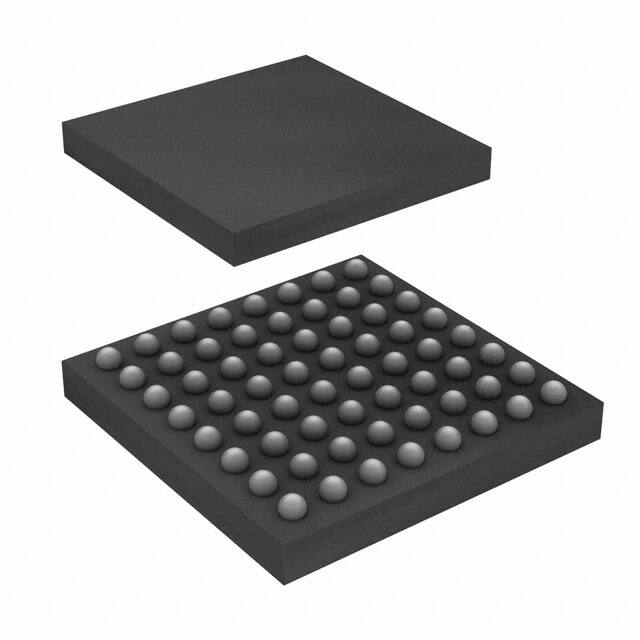

Distinctive Characteristics

Two 1024 Mbit (S29GL01GP) in a single 64-ball FortifiedBGA package (see S29GL01P datasheet for full

specifications)

Single 3V read/program/erase (3.0V - 3.6V)

90 nm MirrorBit process technology

8-word/16-byte page read buffer

32-word/64-byte write buffer reduces overall programming

time for multiple-word writes

Secured Silicon Sector region

– 128-word/256-byte sector for permanent, secure

identification through an 8-word/16-byte random Electronic

Serial Number

– Can be programmed and locked at the factory or by the

customer

Uniform 64Kword/128KByte Sector Architecture

– S70GL02GP: two thousand forty-eight sectors

100,000 erase cycles per sector typical

20-year data retention typical

Offered Packages

– 64-ball Fortified BGA

Cypress Semiconductor Corporation

Document Number: 002-01338 Rev. *D

•

Suspend and Resume commands for Program and Erase

operations

Write operation status bits indicate program and erase

operation completion

Unlock Bypass Program command to reduce programming

time

Support for Common Flash Interface (CFI)

Persistent and Password methods of Advanced Sector

Protection

WP#/ACC input

– Accelerates programming time (when VACC is applied) for

greater throughput during system production

– Protects first or last sector of each die, regardless of sector

protection settings

Hardware reset input (RESET#) resets device

Ready/Busy# output (RY/BY#) detects program or erase

cycle completion

198 Champion Court

•

San Jose, CA 95134-1709

•

408-943-2600

Revised March 16, 2016

�S70GL02GP

Performance Characteristics

Max. Read Access Times (ns)(Note 1)

Parameter

2 Gb

Random Access Time (tACC)

110

Page Access Time (tPACC)

25

CE# Access Time (tCE)

110

OE# Access Time (tOE)

25

Notes

1. Access times are dependent on VCC and VIO operating ranges. See Ordering Information on page 4 for further details.

2. Contact a sales representative for availability.

Current Consumption (typical values)

Random Access Read

30 mA

8-Word Page Read

1 mA

Program/Erase

50 mA

Standby

2 µA

Program & Erase Times (typical values)

Single Word Programming

60 µs

Effective Write Buffer Programming (VCC) Per Word

15 µs

Effective Write Buffer Programming (VACC) Per Word

15 µs

Sector Erase Time (64 Kword Sector)

0.5 s

Document Number: 002-01338 Rev. *D

Page 2 of 11

�S70GL02GP

Contents

1.

1.1

Ordering Information ................................................... 4

Recommended Combinations........................................ 4

3.

Memory Map .................................................................. 8

4.

Autoselect ..................................................................... 8

2.

2.1

2.2

Input/Output Description and Logic Symbol............. 5

Special Handling Instructions for BGA Package............ 6

LSE064—64 ball Fortified Ball Grid Array, 13 ´ 11 mm . 7

5.

Erase And Programming Performance....................... 8

6.

BGA Package Capacitance .......................................... 9

7.

Revision History.......................................................... 10

Document Number: 002-01338 Rev. *D

Page 3 of 11

�S70GL02GP

1.

Ordering Information

The ordering part number is formed by a valid combination of the following:

S70GL02GP

11

F

F

C

R1

0

PACKING TYPE

0 = Tray (standard; see (Note 3)

2 = 7” Tape and Reel

3 = 13” Tape and Reel

MODEL NUMBER (VIO range, protection when WP# =VIL)

R1 = VIO = VCC = 3.0 to 3.6V, highest address sector protected

R2 = VIO = VCC = 3.0 to 3.6V, lowest address sector protected

TEMPERATURE RANGE

I = Industrial (–40 °C to +85 °C)

C = Commercial (0 °C to +85 °C)

PACKAGE MATERIALS SET

A = Pb (Note 1)

F = Pb-free

PACKAGE TYPE

F = Fortified Ball Grid Array, 1.0 mm pitch package

SPEED OPTION

11 = 110 ns

DEVICE NUMBER/DESCRIPTION

S70GL02GP

3.0V-only, 2048 Megabit (128 M x 16-Bit/256 M x 8-Bit) Page-Mode Flash Memory

Manufactured on 90 nm MirrorBit process technology

1.1

Recommended Combinations

Recommended Combinations table below list various configurations planned to be available in volume. The table below will be

updated as new combinations are released. Check with your local sales representative to confirm availability of specific

configuration not listed or to check on newly released combinations.

S29GL-P Recommended Combinations (Note 1)

Base OPN

S70GL02GP

Package and

Temperature

Speed (ns)

110

FFC, FAC (Note 2)

Model Number

R1, R2

Packing Type

Ordering Part Number

(x = Packing Type)

0, 2, 3 (Note 3)

S70GL02GP11FFCR1x

S70GL02GP11FFCR2x

S70GL02GP11FACR1x

S70GL02GP11FACR2x

Notes

1. Contact a local sales representative for availability.

2. BGA package marking omits leading “S29” and packing type designator from ordering part number.

3. Packing Type “0” is standard option.

Document Number: 002-01338 Rev. *D

Page 4 of 11

�S70GL02GP

2.

Input/Output Description and Logic Symbol

Table 1 identifies the input and output package connections provided on the device.

Table 1. Input/Output Description

Symbol

Type

A26–A0

Input

Description

DQ14–DQ0

I/O

Data input/output.

DQ15/A-1

I/O

DQ15: Data input/output in word mode.

A-1: LSB address input in byte mode.

CE#

Input

Address lines for GL02GP

Chip Enable.

OE#

Input

Output Enable.

WE#

Input

Write Enable.

VCC

Supply

Device Power Supply.

VIO

Supply

Versatile IO Input.

VSS

Supply

Ground.

RY/BY#

Output

Ready/Busy. Indicates whether an Embedded Algorithm is in progress or complete. At VIL, the

device is actively erasing or programming. At High Z, the device is in ready.

BYTE#

Input

Selects data bus width. At VIL, the device is in byte configuration and data I/O pins DQ0-DQ7 are

active. At VIH, the device is in word configuration and data I/O pins DQ0-DQ15 are active.

RESET#

Input

Hardware Reset. Low = device resets and returns to reading array data.

WP#/ACC

Input

Write Protect/Acceleration Input. At VIL, disables program and erase functions in the outermost

sectors. At VHH, accelerates programming; automatically places device in unlock bypass mode.

Should be at VIH for all other conditions.

NC

No Connect

Not connected internally.

Document Number: 002-01338 Rev. *D

Page 5 of 11

�S70GL02GP

2.1

Special Handling Instructions for BGA Package

Special handling is required for Flash Memory products in BGA packages.

Flash memory devices in BGA packages may be damaged if exposed to ultrasonic cleaning methods. The package and/or data

integrity may be compromised if the package body is exposed to temperatures above 150°C for prolonged periods of time.

Figure 2.1 64-ball Fortified Ball Grid Array

64-ball Fortified BGA

Top View, Balls Facing Down

A8

B8

C8

D8

E8

F8

G8

H8

NC

A22

A23

VIO

VSS

A24

A25

NC

A7

B7

C7

D7

E7

F7

G7

H7

A13

A12

A14

A15

A16

BYTE#

DQ15/A-1

VSS

A6

B6

C6

D6

E6

F6

G6

H6

A9

A8

A10

A11

DQ7

DQ14

DQ13

DQ6

A5

B5

C5

D5

E5

F5

G5

H5

WE#

RESET#

A21

A19

DQ5

DQ12

VCC

DQ4

A4

B4

C4

D4

E4

F4

G4

H4

A18

A20

DQ2

DQ10

DQ11

DQ3

RY/BY# WP#/ACC

A3

B3

C3

D3

E3

F3

G3

H3

A7

A17

A6

A5

DQ0

DQ8

DQ9

DQ1

A2

B2

C2

D2

E2

F2

G2

H2

A3

A4

A2

A1

A0

CE#

OE#

VSS

A1

B1

C1

D1

E1

F1

G1

H1

NC

A26

NC

NC

NC

VIO

NC

NC

Document Number: 002-01338 Rev. *D

Page 6 of 11

�S70GL02GP

2.2

LSE064—64 ball Fortified Ball Grid Array, 13 11 mm

Figure 2.2 LSE064—64-ball Fortified Ball Grid Array (FBGA), 13 x 11 mm

NOTES:

PACKAGE

LSE 064

JEDEC

N/A

DxE

13.00 mm x 11.00 mm

PACKAGE

SYMBOL

MIN

NOM

MAX

A

---

---

1.40

A1

0.40

---

---

A2

0.79

---

0.91

D

13.00 BSC.

BALL POSITION DESIGNATION PER JEP95,

SECTION 4.3, SPP-010.

4.

e REPRESENTS THE SOLDER BALL GRID PITCH.

5.

SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D"

DIRECTION.

BODY THICKNESS

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE

"E" DIRECTION.

BODY SIZE

BODY SIZE

7.00 BSC.

MATRIX FOOTPRINT

E1

7.00 BSC.

MD

8

MATRIX SIZE D DIRECTION

ME

8

MATRIX SIZE E DIRECTION

MATRIX FOOTPRINT

64

0.60

ALL DIMENSIONS ARE IN MILLIMETERS.

3.

PROFILE

11.00 BSC.

0.50

2.

BALL HEIGHT

E

n

DIMENSIONING AND TOLERANCING METHODS PER

ASME Y14.5M-1994.

NOTE

D1

Øb

1.

n IS THE NUMBER OF POPULTED SOLDER BALL POSITIONS

FOR MATRIX SIZE MD X ME.

6

DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL

DIAMETER IN A PLANE PARALLEL TO DATUM C.

7

SD AND SE ARE MEASURED WITH RESPECT TO DATUMS

A AND B AND DEFINE THE POSITION OF THE CENTER

SOLDER BALL IN THE OUTER ROW.

BALL COUNT

0.70

eE

1.00 BSC.

BALL PITCH

eD

1.00 BSC

BALL PITCH

SD / SE

0.50 BSC.

---

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN

THE OUTER ROW SD OR SE = 0.000.

BALL DIAMETER

SOLDER BALL PLACEMENT

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN

THE OUTER ROW, SD OR SE = e/2

8.

"+" INDICATES THE THEORETICAL CENTER OF

DEPOPULATED BALLS.

9

A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK

MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

DEPOPULATED SOLDER BALLS

3611 \ 16-038.15 \ 11.13.6

Document Number: 002-01338 Rev. *D

Page 7 of 11

�S70GL02GP

3. Memory Map

The S70GL02GP consist of uniform 64 Kword (128 Kb) sectors organized as shown in Table 2.

Table 2. S70GL02GP Sector & Memory Address Map

Uniform Sector Size Sector Count

64 Kword/128 Kb

Sector Range

Address Range (16-bit)

Notes

SA00

0000000h–000FFFFh

Sector Starting Address

2048

:

:

SA2047

7FF0000H–7FFFFFFh

Sector Ending Address

Note

This table has been condensed to show sector-related information for an entire device on a single page. Sectors and their address ranges that are not explicitly listed

(such as SA001-SA2046) have sector starting and ending addresses that form the same pattern as all other sectors of that size. For example, all 128 Kb sectors have the

pattern xxx0000h-xxxFFFFh.

4. Autoselect

Table 3 provides the device identification codes for the S70GL02GP. For more information on the autoselect function, refer to the

S29GL01P datasheet.

Table 3. Autoselect Addresses in System

Description

Address

Read Data (word/byte mode)

Manufacturer ID

(Base) + 00h

xx01h/1h

Device ID, Word 1

(Base) + 01h

227Eh/7Eh

Device ID, Word 2

(Base) + 0Eh

2248h/48h

Device ID, Word 3

(Base) + 0Fh

2201h/01h

Secure Device Verify

(Base) + 03h

For S70GL02GPH: XX19h/19h = Not Factory Locked. XX99h/99h = Factory Locked.

For S70GL02GPL: XX09h/09h = Not Factory Locked. XX89h/89h = Factory Locked.

Sector Protect Verify

(SA) + 02h

xx01h/01h = Locked, xx00h/00h = Unlocked

5. Erase And Programming Performance

Table 4. Erase And Programming Performance

Parameter

Typ (Note 1)

Sector Erase Time

Chip Erase Time

S70GL02GP

Max (Note 2)

Unit

0.5

3.5

sec

1024

4096

sec

Total Write Buffer Time, for 64 bytes

480

µs

Total Accelerated Write Buffer Programming Time,

for 64 bytes

432

µs

Chip Program Time

1968

sec

S70GL02GP

Comments

Excludes 00h programming

prior to erasure (Note 3)

Excludes system level

overhead (Note 4)

Notes

1. Typical program and erase times assume the following conditions: 25°C, 3.6 V VCC, 10,000 cycles, checkerboard pattern.

2. Under worst case conditions of -40°C, VCC = 3.0 V, 100,000 cycles.

3. In the pre-programming step of the Embedded Erase algorithm, all bits are programmed to 00h before erasure.

4. System-level overhead is the time required to execute the two- or four-bus-cycle sequence for the program command.

Document Number: 002-01338 Rev. *D

Page 8 of 11

�S70GL02GP

6. BGA Package Capacitance

Parameter Symbol

Parameter Description

Test Setup

Typ

Max

Unit

CIN

Input Capacitance

VIN = 0

12

20

pF

COUT

Output Capacitance

VOUT = 0

20

24

pF

CIN2

Control Pin Capacitance

VIN = 0

16

20

pF

RESET#, WP#/ACC

Separated Control Pin

VIN = 0

84

90

pF

CE#

Separated Control Pin

VIN = 0

44

50

pF

Notes

1. Sampled, not 100% tested.

2. Test conditions TA = 25°C, f = 1.0 MHz.

Document Number: 002-01338 Rev. *D

Page 9 of 11

�S70GL02GP

7. Revision History

Document History Page

Document Title: S70GL02GP, 2 Gbit, 3V Page Mode S70GL-P MirrorBit® Flash

Document Number: 002-01338

Rev.

ECN No.

Orig. of

Change

Submission

Date

**

RYSU

12/04/2006

Initial release

Description of Change

*A

RYSU

05/19/2008

Global:

Changed data sheet designation

Added Product Life-cycle notice

Removed Table of Figures and Table of Tables

Ordering Information:

Changed sample OPN

Added Commercial temperature range

Changed configuration in “Device Number/description”

Modified “Recommended Combination” table

removed TSOP package option

Erase And Program Performance:

Chip Program Time - removed comment

Common Flash Memory Interface:

Removed section (see publication S29GL-P_00 for details)

*B

RYSU

02/23/2010

Global:

Updated available model options.

Corrected Chip Program Time.

*C

4950184

RYSU

10/06/2015

Updated to Cypress template

*D

5177489

RYSU

03/16/2016

Updated General Description and Distinctive Characteristics.

Document Number: 002-01338 Rev. *D

Page 10 of 11

�S70GL02GP

Sales, Solutions, and Legal Information

Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer’s representatives, and distributors. To find the office

closest to you, visit us at Cypress Locations.

PSoC® Solutions

Products

®

®

ARM Cortex Microcontrollers

Automotive

cypress.com/arm

cypress.com/automotive

Clocks & Buffers

Interface

Lighting & Power Control

Memory

cypress.com/clocks

cypress.com/interface

cypress.com/powerpsoc

cypress.com/memory

PSoC

cypress.com/psoc

Touch Sensing

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community

Community | Forums | Blogs | Video | Training

Technical Support

cypress.com/support

cypress.com/touch

USB Controllers

Wireless/RF

cypress.com/psoc

cypress.com/usb

cypress.com/wireless

© Cypress Semiconductor Corporation 2006-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document,

including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries

worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other

intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress

hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify

and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either

directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right

to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum

extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software

is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED

WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not

assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or

programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application

made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of

weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or

hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any

component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole

or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify

and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress

products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United

States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-01338 Rev. *D

Revised March 16, 2016

Page 11 of 11

�