STK14C88-NF35U

32Kx8 AutoStore nvSRAM with extended temperature

FEATURES

DESCRIPTION

• 35 ns Read Access & R/W Cycle Time

The Simtek STK14C88-NF35U is a 256Kb fast static

RAM with a non-volatile Quantum Trap storage element included with each memory cell.

• Unlimited Read/Write Endurance

• Automatic Non-volatile STORE on Power Loss

The SRAM provides the fast access & cycle times,

ease of use and unlimited read & write endurance of

a normal SRAM.

• Non-Volatile STORE Under Hardware or

Software Control

• Automatic RECALL to SRAM on Power Up

Data transfers automatically to the non-volatile storage cells when power loss is detected (the STORE

operation). On power up, data is automatically

restored to the SRAM (the RECALL operation). Both

STORE and RECALL operations are also available

under software control.

• Unlimited RECALL Cycles

• 100k STORE Cycles

• 10-Year Non-volatile Data Retention

• Single 5V +10% Power Supply

• -55°C to 125°C Operating Range

The Simtek nvSRAM is the first monolithic non-volatile memory to offer unlimited writes and reads. It is

the highest performance, most reliable non-volatile

memory available.

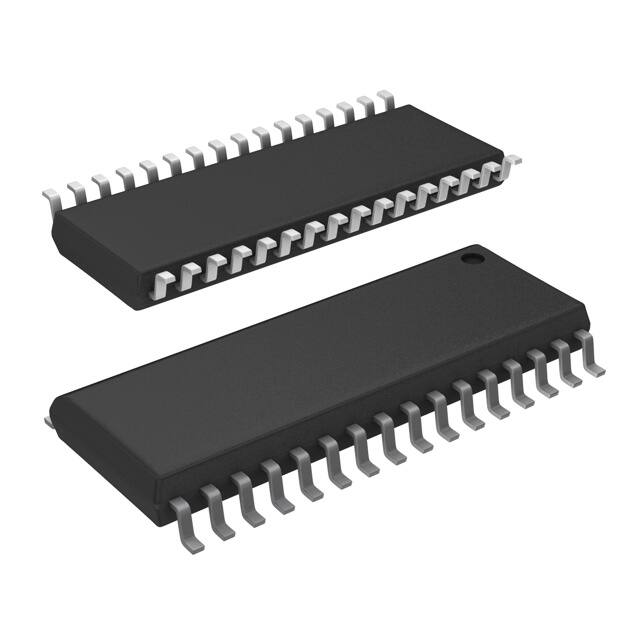

• 32-Pin 300 mil SOIC (RoHS-Compliant)

BLOCK DIAGRAM

VCCX

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

INPUT BUFFERS

A5

A6

A7

A8

A9

A11

A12

A13

A14

ROW DECODER

Quantum Trap

512 x 512

VCAP

POWER

CONTROL

STORE

STATIC RAM

ARRAY

512 x 512

RECALL

STORE/

RECALL

CONTROL

SOFTWARE

DETECT

COLUMN I/O

HSB

A0 - A13

COLUMN DEC

A0 A1 A2 A3 A4 A10

G

E

W

This product conforms to specifications per the

terms of Simtek standard warranty. The product

has completed Simtek internal qualification testing

and has reached production status.

1

Document Control #ML0066 Rev 2.0

Feb, 2008

�STK14C88-NF35U

PIN CONFIGURATIONS

VCAP

1

32

VCC

A14

2

31

HSB

A12

A7

3

30

4

A6

A5

A4

A3

5

29

28

W

A13

A8

6

27

A9

7

26

A11

8

25

NC

A2

9

24

G

NC

10

23

A10

A1

A0

11

22

12

21

E

DQ7

DQ0

13

20

DQ1

DQ2

VSS

14

19

15

18

16

17

(TOP)

DQ6

DQ5

DQ4

DQ3

32-Pin 300 mil SOIC

PIN DESCRIPTIONS

Pin Name

I/O

Description

A14-A0

Input

Address: The 15 address inputs select one of 32,768 bytes in the nvSRAM array

DQ7-DQ0

I/O

Data: Bi-directional 8-bit data bus for accessing the nvSRAM

E

Input

Chip Enable: The active low E input selects the device

W

Input

Write Enable: The active low W enables data on the DQ pins to be written to the address

location latched by the falling edge of E

G

Input

Output Enable: The active low G input enables the data output buffers during read cycles.

De-asserting G high caused the DQ pins to tri-state.

VCC

Power Supply

Power: 5.0V, +10%

HSB

I/O

Hardware Store Busy: When low this output indicates a Store is in progress. When pulled

low external to the chip, it will initiate a nonvolatile STORE operation. A weak pull up resistor

keeps this pin high if not connected. (Connection Optional).

VCAP

Power Supply

AutoStore Capacitor: Supplies power to nvSRAM during power loss to store data from

SRAM to nonvolatile storage elements.

VSS

Power Supply

Ground

Document Control #ML0066 Rev 2.0

Feb, 2008

2

�STK14C88-NF35U

ABSOLUTE MAXIMUM RATINGSa

Voltage on Input Relative to Ground . . . . . . . . . . . . . –0.5V to 7.0V

Voltage on Input Relative to VSS . . . . . . . . . .–0.6V to (VCC + 0.5V)

Voltage on DQ0-7 or HSB . . . . . . . . . . . . . . . .–0.5V to (VCC + 0.5V)

Temperature under Bias. . . . . . . . . . . . . . . . . . . . . .–55°C to 125°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .–65°C to 150°C

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1W

DC Output Current (1 output at a time, 1s duration) . . . . . . . 15mA

Note a: Stresses greater than those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device. This is a

stress rating only, and functional operation of the device at conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

(VCC = 5.0V ± 10%)e

DC CHARACTERISTICS

STK14C88-NF35U

SYMBOL

PARAMETER

UNITS

MIN

NOTES

MAX

ICC1b

Average VCC Current

90

mA

tAVAV = 35ns

ICC2c

Average VCC Current during STORE

3

mA

All Inputs Don’t Care, VCC = max

ICC3b

Average VCC Current at tAVAV = 200ns

5V, 25°C, Typical

15

mA

W ≥ (V CC – 0.2V)

All Others Cycling, CMOS Levels

ICC4c

Average VCAP Current during AutoStore Cycle

2

mA

All Inputs Don’t Care

ISB1d

Average VCC Current

(Standby, Cycling TTL Input Levels)

30

mA

tAVAV = 35ns, E ≥ VIH

ISB2d

VCC Standby Current

(Standby, Stable CMOS Input Levels)

3

mA

E ≥ (V CC – 0.2V)

All Others VIN ≤ 0.2V or ≥ (VCC – 0.2V)

IILK

Input Leakage Current

±1

μA

VCC = max

VIN = VSS to VCC

IOLK

Off-State Output Leakage Current

±5

μA

VCC = max

VIN = VSS to VCC, E or G ≥ VIH

VIH

Input Logic “1” Voltage

2.2

VCC + .5

V

All Inputs

VIL

Input Logic “0” Voltage

VSS – .5

0.8

V

All Inputs

VOH

Output Logic “1” Voltage

V

IOUT = – 4mA (except HSB)

VOL

Output Logic “0” Voltage

0.4

V

IOUT = 8mA (except HSB)

VBL

Logic “0” Voltage on HSB Output

0.4

V

IOUT = 3mA

TA

Operating Temperature

125

°C

Note b:

Note c:

Note d:

Note e:

2.4

55

ICC1 and ICC3 are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded.

ICC2 and ICC4 are the average currents required for the duration of the respective STORE cycles (tSTORE ) .

E ≥ VIH will not produce standby current levels until any nonvolatile cycle in progress has timed out.

VCC reference levels throughout this datasheet refer to system VCC if that is where the power supply connection is made, or VCAP if the IC VCC

is connected to ground.

AC TEST CONDITIONS

5.0V

Input Pulse Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to 3V

Input Rise and Fall Times. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 5ns

Input and Output Timing Reference Levels . . . . . . . . . . . . . . . 1.5V

Output Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Figure 1

CAPACITANCEf

SYMBOL

(TA = 25°C, f = 1.0MHz)

PARAMETER

MAX

UNITS

CONDITIONS

CIN

Input Capacitance

5

pF

ΔV = 0 to 3V

COUT

Output Capacitance

7

pF

ΔV = 0 to 3V

Note f:

OUTPUT

255 Ohms

30 pF

INCLUDING

SCOPE AND

FIXTURE

Figure 1: AC Output Loading

These parameters are guaranteed but not tested.

Document Control #ML0066 Rev 2.0

Feb, 2008

480 Ohms

3

�STK14C88-NF35U

(VCC = 5.0V ± 10%)e

SRAM READ CYCLES #1 & #2

SYMBOLS

STK14C88-NF35U

NO.

PARAMETER

#1, #2

UNITS

Alt.

MIN

MAX

1

tELQV

tACS

Chip Enable Access Time

2

tAVAVg, tELEHg

tRC

Read Cycle Time

35

3

tAVQVh

tAA

Address Access Time

35

ns

4

tGLQV

tOE

Output Enable to Data Valid

15

ns

5

tAXQXh

tOH

Output Hold after Address Change

5

6

tELQX

tLZ

Address Change or Chip Enable to Output Active

5

7

tEHQZi

tHZ

Address Change or Chip Disable to Output Inactive

8

tGLQX

tOLZ

Output Enable to Output Active

35

9

tGHQZi

tOHZ

Output Disable to Output Inactive

10

tELICCHf

tPA

Chip Enable to Power Active

11

tEHICCLf

tPS

Chip Disable to Power Standby

ns

ns

13

0

13

ns

35

ns

0

ns

SRAM READ CYCLE #1: Address Controlledg, h

2

tAVAV

ADDRESS

3

tAVQV

DQ (DATA OUT)

DATA VALID

SRAM READ CYCLE #2: E and G Controlledg

ADDR ESS

2

E

27

t E LE H

1

tEL Q V

6

29

t EHAX

11

t EHI CC L

t ELQ X

7

t EHQ Z

3

t AV QV

G

8

tG L Q X

9

t GH Q Z

4

t G L QV

DQ (D ATA OUT)

DAT A VAL ID

10

t ELI CC H

AC T IVE

I CC

ST AND BY

Document Control #ML0066 Rev 2.0

Feb, 2008

4

ns

ns

Note g: W and HSB must be high during SRAM READ cycles.

Note h: I/O state assumes E and G < VIL and W > VIH; device is continuously selected.

Note i: Measured ± 200mV from steady state output voltage.

5

tAXQX

ns

ns

�STK14C88-NF35U

(VCC = 5.0V ± 10%)e

SRAM WRITE CYCLES #1 & #2

SYMBOLS

STK14C88-NF35U

NO.

PARAMETER

#1

#2

Alt.

UNITS

MIN

MAX

12

tAVAV

tAVAV

tWC

Write Cycle Time

35

ns

13

tWLWH

tWLEH

tWP

Write Pulse Width

25

ns

14

tELWH

tELEH

tCW

Chip Enable to End of Write

25

ns

15

tDVWH

tDVEH

tDW

Data Set-up to End of Write

12

ns

16

tWHDX

tEHDX

tDH

Data Hold after End of Write

0

ns

17

tAVWH

tAVEH

tAW

Address Set-up to End of Write

25

ns

18

tAVWL

tAVEL

tAS

Address Set-up to Start of Write

0

ns

19

tWHAX

tEHAX

tWR

Address Hold after End of Write

0

20

t WLQZ i, j

tWZ

Write Enable to Output Disable

21

tWHQX

tOW

Output Active after End of Write

5

Note j: If W is low when E goes low, the outputs remain in the high-impedance state.

Note k: E or W must be ≥ VIH during address transitions.

Note l: HSB must be high during SRAM WRITE cycles.

SRAM WRITE CYCLE #1: W Controlledk, l

12

tAVAV

ADDRESS

19

tWHAX

14

tELWH

E

17

tAVWH

18

tAVWL

13

tWLWH

W

15

tDVWH

DATA IN

DATA OUT

16

tWHDX

DATA VALID

20

tWLQZ

21

tWHQX

HIGH IMPEDANCE

PREVIOUS DATA

SRAM WRITE CYCLE #2: E Controlledk, l

12

tAVAV

ADDRESS

18

tAVEL

14

tELEH

19

tEHAX

E

17

tAVEH

13

tWLEH

W

15

tDVEH

DATA IN

DATA OUT

Document Control #ML0066 Rev 2.0

Feb, 2008

16

tEHDX

DATA VALID

HIGH IMPEDANCE

5

ns

13

ns

ns

�STK14C88-NF35U

HARDWARE MODE SELECTION

E

W

HSB

A13 - A0 (hex)

H

X

H

X

L

H

H

L

L

H

X

X

L

X

MODE

I/O

POWER

Not Selected

Output High Z

Standby

X

Read SRAM

Output Data

Active

X

Write SRAM

Input Data

Active

Nonvolatile STORE

Output High Z

lCC2

NOTES

t

m

Note m: HSB STORE operation occurs only if an SRAM WRITE has been done since the last nonvolatile cycle. After the STORE (if any) completes,

the part will go into standby mode, inhibiting all operations until HSB rises.

(VCC = 5.0V ± 10%)e

HARDWARE STORE CYCLE

SYMBOLS

STK14C88-NF35U

NO.

PARAMETER

Standard

Alternate

UNITS

MIN

22

tSTORE

tHLHZ

STORE Cycle Duration

23

tDELAY

tHLQZ

Time Allowed to Complete SRAM Cycle

24

tRECOVER

tHHQX

Hardware STORE High to Inhibit Off

25

tHLHX

Hardware STORE Pulse Width

26

tHLBL

Hardware STORE Low to STORE Busy

NOTES

MAX

10

ms

μs

1

700

15

ns

n, o

ns

300

ns

Note n: E and G low and W high for output behavior.

Note o: tRECOVER is only applicable after tSTORE is complete.

HARDWARE STORE CYCLE

25

tHLHX

HSB (IN)

24

tRECOVER

22

tSTORE

26

tHLBL

HSB (OUT)

HIGH IMPEDANCE

HIGH IMPEDANCE

23

tDELAY

DQ (DATA OUT)

DATA VALID

DATA VALID

Document Control #ML0066 Rev 2.0

Feb, 2008

6

�STK14C88-NF35U

(VCC = 5.0V ± 10%)e

AutoStore™/POWER-UP RECALL

SYMBOLS

STK14C88-NF35U

NO.

PARAMETER

Standard

27

tRESTORE

28

tSTORE

UNITS

Alternate

tHLHZ

MIN

Power-up RECALL Duration

550

μs

p

STORE Cycle Duration

10

ms

n, q

29

tVSBL

30

tDELAY

31

VSWITCH

Low Voltage Trigger Level

32

VRESET

Low Voltage Reset Level

Low Voltage Trigger (VSWITCH) to HSB Low

tBLQZ

NOTES

MAX

Time Allowed to Complete SRAM Cycle

300

1

4.0

ns

l

μs

n

4.5

V

3.6

V

Note p: tRESTORE starts from the time VCC rises above VSWITCH.

Note q: HSB is asserted low for 1μs when VCAP drops through VSWITCH. If an SRAM WRITE has not taken place since the last nonvolatile cycle, HSB

will be released and no STORE will take place.

AutoStore™/POWER-UP RECALL

VCC

31

VSWITCH

32

VRESET

AutoStore

POWER-UP RECALL

29

tVSBL

27

tRESTORE

28

tSTORE

HSB

30

tDELAY

W

DQ (DATA OUT)

POWER-UP

RECALL

BROWN OUT

NO STORE

(NO SRAM WRITES)

BROWN OUT

AutoStore

BROWN OUT

AutoStore

NO RECALL

(VCC DID NOT GO

BELOW VRESET)

NO RECALL

(VCC DID NOT GO

BELOW VRESET)

RECALL WHEN

VCC RETURNS

ABOVE VSWITCH

Document Control #ML0066 Rev 2.0

Feb, 2008

7

�STK14C88-NF35U

SOFTWARE STORE/RECALL MODE SELECTION

E

L

L

W

A13 - A0 (hex)

MODE

I/O

POWER

NOTES

H

0E38

31C7

03E0

3C1F

303F

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Output Data

Output Data

Output Data

Output Data

Output Data

Active

n, r, s, t

0FC0

Nonvolatile STORE

Output High Z

lCC2

0E38

31C7

03E0

3C1F

303F

0C63

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Nonvolatile RECALL

Output Data

Output Data

Output Data

Output Data

Output Data

Output High Z

Active

H

(VCC = 5.0V ± 10%)e

SOFTWARE-CONTROLLED STORE/RECALL CYCLEv

SYMBOLS

STK14C88-NF35U

NO.

PARAMETER

Standard

n, r, s, t

UNITS

Alternate

MIN

NOTES

MAX

33

tAVAV

tRC

STORE/RECALL Initiation Cycle Time

35

ns

n

34

tAVEL

tAS

Address Set-up Time

0

ns

u,v

35

tELEH

tCW

Clock Pulse Width

25

ns

u,v

36

tELAX

Address Hold Time

20

ns

u, v

37

tRECALL

RECALL Duration

20

Note r:

μs

The six consecutive addresses must be in the order listed. W must be high during all six consecutive E or G controlled cycles to enable a nonvolatile cycle.

Note s: While there are 15 addresses on the STK14C88-NF35U, only the lower 14 are used to control software modes.

Note t: I/O state assumes G < VIL. Activation of nonvolatile cycles does not depend on state of G.

Note u: The software sequence is clocked on the falling edge of E controlled READs without involving G (double clocking will abort the sequence). See

application note: MA0002 http://www.simtek.com/attachments/appNote02.pdf.

Note v: The six consecutive addresses must be read in the order listed in the Software STORE/RECALL Mode Selection Table: (0E38, 31C7, 03E0,

3C1F, 303F, 0FC0) for a STORE cycle or (0E38, 31C7, 03E0, 3C1F, 303F, 0C63) for a RECALL cycle. W must be high during all six consecutive cycles.

SOFTWARE STORE/RECALL CYCLE: E CONTROLLEDv

33

33

tAVAV

ADDRESS

tAVAV

ADDRESS #1

34

tAVEL

ADDRESS #6

35

tELEH

E

36

tELAX

28

tSTORE

DQ (DATA

DATA VALID

DATA VALID

Document Control #ML0066 Rev 2.0

Feb, 2008

8

37

/ tRECALL

HIGH IMPEDANCE

�STK14C88-NF35U

nvSRAM OPERATION

The STK14C88-NF35U has two separate modes of

operation: SRAM mode and nonvolatile mode. In

SRAM mode, the memory operates as a standard

fast static RAM. In nonvolatile mode, data is transferred from SRAM to nonvolatile elements (the

STORE operation) or from nonvolatile elements to

SRAM (the RECALL operation). In this mode SRAM

functions are disabled.

NOISE CONSIDERATIONS

The STK14C88-NF35U is a high-speed memory

and so must have a high-frequency bypass capacitor of approximately 0.1μF connected between VCAP

and VSS, using leads and traces that are as short as

possible. As with all high-speed CMOS ICs, normal

careful routing of power, ground and signals will help

prevent noise problems.

SRAM READ

The STK14C88-NF35U performs a READ cycle

whenever E and G are low and W and HSB are

high. The address specified on pins A0-14 determines

which of the 32,768 data bytes will be accessed.

When the READ is initiated by an address transition,

the outputs will be valid after a delay of tAVQV (READ

cycle #1). If the READ is initiated by E or G, the outputs will be valid at tELQV or at tGLQV, whichever is later

(READ cycle #2). The data outputs will repeatedly

respond to address changes within the tAVQV access

time without the need for transitions on any control

input pins, and will remain valid until another address

change or until E or G is brought high, or W or HSB is

brought low.

SRAM WRITE

A WRITE cycle is performed whenever E and W are

low and HSB is high. The address inputs must be

stable prior to entering the WRITE cycle and must

remain stable until either E or W goes high at the

end of the cycle. The data on the common I/O pins

DQ0-7 will be written into the memory if it is valid tDVWH

before the end of a W controlled WRITE or tDVEH

before the end of an E controlled WRITE.

It is recommended that G be kept high during the

entire WRITE cycle to avoid data bus contention on

common I/O lines. If G is left low, internal circuitry

will turn off the output buffers tWLQZ after W goes low.

Document Control #ML0066 Rev 2.0

Feb, 2008

9

POWER-UP RECALL

During power up, or after any low-power condition

(VCAP < VRESET), an internal RECALL request will be

latched. When VCAP once again exceeds the sense

voltage of VSWITCH, a RECALL cycle will automatically

be initiated and will take tRESTORE to complete.

If the STK14C88-NF35U is in a WRITE state at the

end of power-up RECALL, the SRAM data will be corrupted. To help avoid this situation, a 10K Ohm

resistor should be connected either between W and

system VCC or between E and system VCC.

SOFTWARE NONVOLATILE STORE

The STK14C88-NF35U software STORE cycle is initiated by executing sequential E controlled READ

cycles from six specific address locations. During

the STORE cycle an erase of the previous nonvolatile data is first performed, followed by a program of

the nonvolatile elements. The program operation

copies the SRAM data into nonvolatile memory.

Once a STORE cycle is initiated, further input and

output are disabled until the cycle is completed.

Because a sequence of READs from specific

addresses is used for STORE initiation, it is important that no other READ or WRITE accesses intervene in the sequence, or the sequence will be

aborted and no STORE or RECALL will take place.

To initiate the software STORE cycle, the following

READ sequence must be performed:

1.

2.

3.

4.

5.

6.

Read address

Read address

Read address

Read address

Read address

Read address

0E38 (hex)

31C7 (hex)

03E0 (hex)

3C1F (hex)

303F (hex)

0FC0 (hex)

Valid READ

Valid READ

Valid READ

Valid READ

Valid READ

Initiate STORE cycle

The software sequence must be clocked with E controlled READs.

Once the sixth address in the sequence has been

entered, the STORE cycle will commence and the

chip will be disabled. It is important that READ cycles

and not WRITE cycles be used in the sequence,

although it is not necessary that G be low for the

sequence to be valid. After the tSTORE cycle time has

been fulfilled, the SRAM will again be activated for

READ and WRITE operation.

�STK14C88-NF35U

A software RECALL cycle is initiated with a sequence

of READ operations in a manner similar to the software STORE initiation. To initiate the RECALL cycle,

the following sequence of E controlled READ operations must be performed:

Read address

Read address

Read address

Read address

Read address

Read address

0E38 (hex)

31C7 (hex)

03E0 (hex)

3C1F (hex)

303F (hex)

0C63 (hex)

Valid READ

Valid READ

Valid READ

Valid READ

Valid READ

Initiate RECALL cycle

Internally, RECALL is a two-step procedure. First, the

SRAM data is cleared, and second, the nonvolatile

information is transferred into the SRAM cells. After

the tRECALL cycle time the SRAM will once again be

ready for READ and WRITE operations. The RECALL

operation in no way alters the data in the nonvolatile

elements. The nonvolatile data can be recalled an

unlimited number of times.

AutoStore MODE

The STK14C88-NF35U can be powered in one of

three modes.

During normal AutoStore operation, the STK14C88NF35U will draw current from VCC to charge a capacitor connected to the VCAP pin. This stored charge

will be used by the chip to perform a single STORE

operation. After power up, when the voltage on the

VCAP pin drops below VSWITCH, the part will automatically disconnect the VCAP pin from VCC and initiate a

STORE operation.

If the power supply drops faster than 20 μs/volt

before VCC reaches VSWITCH, then a 2.2 ohm resistor

should be inserted between the VCC pin on the IC

and the system supply to avoid momentary excess

of current between Vcc and Vcap.

AutoStore INHIBIT MODE

If an automatic STORE on power loss is not

required, then Vcc can be tied to ground and system

power applied to VCAP (Figure 3). This is the

AutoStore Inhibit mode, in which the AutoStore function is disabled. If the STK14C88-NF35U is operated in this configuration, references to Vcc should

be changed to VCAP throughout this data sheet. In

this mode, STORE operations may be triggered

through software control. It is not permissible to

change between these three options “on the fly.”

1

32

31

31

30

30

0.1μF

Bypass

68μF

6v, ±20%

+

32

10kΩ

10kΩ∗

1

In order to prevent unneeded STORE operations,

automatic STOREs as well as those initiated by

externally driving HSB low will be ignored unless at

least one WRITE operation has taken place since the

most recent STORE or RECALL cycle. Softwareinitiated STORE cycles are performed regardless of

whether a WRITE operation has taken place.

0.1μF

Bypass

Figure 2 shows the proper connection of capacitors

for automatic store operation. A charge storage

In system power mode, both VCC and VCAP are connected to the + 5V power supply without the 68μF

capacitor. In this mode the AutoStore function of the

STK14C88-NF35U will operate on the stored system charge as power goes down. The user must,

however, guarantee that VCC does not drop below

3.6V during the 10ms STORE cycle.

10kΩ∗

1.

2.

3.

4.

5.

6.

capacitor having a capacity of between 68μF and

220μF (± 20%) rated at 6V should be provided.

10kΩ

SOFTWARE NONVOLATILE RECALL

16

17

16

Figure 2: AutoStore Mode

Figure 3: AutoStore Inhibit Mode

*If HSB is not used, it should be left unconnected.

Document Control #ML0066 Rev 2.0

Feb, 2008

17

10

�STK14C88-NF35U

HSB OPERATION

The STK14C88-NF35U provides the HSB pin for

controlling and acknowledging the STORE operations. The HSB pin can be used to request a hardware STORE cycle. When the HSB pin is driven low,

the STK14C88-NF35U will conditionally initiate a

STORE operation after tDELAY; an actual STORE cycle

will only begin if a WRITE to the SRAM took place

since the last STORE or RECALL cycle. The HSB pin

has a very resistive pullup and is internally driven

low to indicate a busy condition while the STORE

(initiated by any means) is in progress. Pull up this

pin with an external 10K ohm resistor to VCAP if HSB

is used as a driver.

SRAM READ and WRITE operations that are in

progress when HSB is driven low by any means are

given time to complete before the STORE operation

is initiated. After HSB goes low, the STK14C88NF35U will continue SRAM operations for tDELAY. During tDELAY, multiple SRAM READ operations may take

place. If a WRITE is in progress when HSB is pulled

low it will be allowed a time, tDELAY, to complete. However, any SRAM WRITE cycles requested after HSB

goes low will be inhibited until HSB returns high.

The VCAP pins from the other STK14C88-NF35U

parts can be tied together and share a single capacitor. The capacitor size must be scaled by the number of devices connected to it. It is essential that all

parts have written to the SRAM for this STORE to

execute properly.

During any STORE operation, regardless of how it

was initiated, the STK14C88-NF35U will continue to

drive the HSB pin low, releasing it only when the

STORE is complete. Upon completion of the STORE

operation the STK14C88-NF35U will remain disabled until the HSB pin returns high.

If HSB is not used, it should be left unconnected.

BEST PRACTICES

nvSRAM products have been used effectively for

over 15 years. While ease-of-use is one of the product’s main system values, experience gained working with hundreds of applications has resulted in the

following suggestions as best practices:

• The non-volatile cells in an nvSRAM are programmed on the test floor during final test and

quality assurance. Incoming inspection routines

at customer or contract manufacturer’s sites will

sometimes reprogram these values. Final NV pat-

Document Control #ML0066 Rev 2.0

Feb, 2008

11

terns are typically repeating patterns of AA, 55,

00, FF, A5, or 5A. End product’s firmware should

not assume an NV array is in a set programmed

state. Routines that check memory content values to determine first time system configuration,

cold or warm boot status, etc. should always program a unique NV pattern (e.g., complex 4-byte

pattern of 46 E6 49 53 hex or more random

bytes) as part of the final system manufacturing

test to ensure these system routines work consistently.

• Power up boot firmware routines should rewrite

the nvSRAM into the desired state (autostore

enabled, etc.). While the nvSRAM is shipped in a

preset state, best practice is to again rewrite the

nvSRAM into the desired state as a safeguard

against events that might flip the bit inadvertently

(program bugs, incoming inspection routines,

etc.).

• The Vcap value specified in this datasheet

includes a minimum and a maximum value size.

Best practice is to meet this requirement and not

exceed the max Vcap value because the nvSRAM

internal algorithm calculates Vcap charge time

based on this max Vcap value. Customers that

want to use a larger Vcap value to make sure

there is extra store charge and store time should

discuss their Vcap size selection with Simtek to

understand any impact on the Vcap voltage level

at the end of a tRECALL period.

�STK14C88-NF35U

PREVENTING STORES

Average Active Current (mA)

100

The STORE function can be disabled on the fly by

holding HSB high with a driver capable of sourcing

30mA at a VOH of at least 2.2V, as it will have to overpower the internal pull-down device that drives HSB

low for 20μs at the onset of a STORE. When the

STK14C88-NF35U is connected for AutoStore operation (system VCC connected to chip VCC and a 68μF

capacitor on VCAP) and VCC crosses VSWITCH on the

way down, the STK14C88-NF35U will attempt to

pull HSB low; if HSB doesn’t actually get below VIL,

the part will stop trying to pull HSB low and abort the

STORE attempt.

60

40

TTL

20

CMOS

0

HARDWARE PROTECT

50

The STK14C88-NF35U offers hardware protection

against inadvertent STORE operation and SRAM

WRITEs during low-voltage conditions. When VCAP <

VSWITCH, all externally initiated STORE operations and

SRAM WRITEs will be inhibited.

LOW AVERAGE ACTIVE POWER

The STK14C88-NF35U draws significantly less current when it is cycled at times longer than 50ns. Figure 4 shows the relationship between ICC and READ

cycle time. Worst-case current consumption is

shown for both CMOS and TTL input levels (commercial temperature range, VCC = 5.5V, 100% duty cycle

on chip enable). Figure 5 shows the same relationship for WRITE cycles. If the chip enable duty cycle

is less than 100%, only standby current is drawn

when the chip is disabled. The overall average current drawn by the STK14C88-NF35U depends on

the following items: 1) CMOS vs. TTL input levels;

2) the duty cycle of chip enable; 3) the overall cycle

rate for accesses; 4) the ratio of READs to WRITEs;

5) the operating temperature; 6) the Vcc level; and

7) I/O loading.

12

100

150

Cycle Time (ns)

200

Figure 4: Icc (max) Reads

100

Average Active Current (mA)

AutoStore can be completely disabled by tying VCC

to ground and applying + 5V to VCAP. This is the

AutoStore Inhibit mode; in this mode STOREs are only

initiated by explicit request using either the software

sequence or the HSB pin.

Document Control #ML0066 Rev 2.0

Feb, 2008

80

80

60

TTL

40

CMOS

20

0

50

100

150

Cycle Time (ns)

Figure 5: Icc (max) Writes

200

�STK14C88-NF35U

Commercial and Industrial Ordering Information

STK14C88 - N F 35 U TR

Packaging Option

Blank = Tube

TR = Tape and Reel

Temperature Range

U = –55°C to 125°C (production testing)

Access Time

35 = 35ns

Lead Finish

F = 100% Sn (Matte Tin)

Package

N = Plastic 32-pin 300 mil SOIC

Ordering Information

Part Number

STK14C88-NF35UTR

Description

5V 32Kx8 AutoStore nvSRAM SOP32-300

Document Control #ML0066 Rev 2.0

Feb, 2008

13

Access Times

35 ns access time

Temperature

-55ºC to 125 ºC

�STK14C88-NF35U

Package Diagrams

32 Lead 300 mil SOIC Gull Wing

0.292 7.42

0.300 7.60

(

)

0.405 10.29

0.419 10.64

(

)

Pin 1

Index

.050 (1.27)

0.810 20.57

0.822 20.88

(

0.026 0.66

0.032 0.81

(

BSC

)

)

0.090 2.29

0.100 2.54

( )

0.086

0.090

0.12

0.22

( )

0.004 0.10

0.010 0.25

( )

0.014 0.36

0.020 0.51

0.006

0.013

0

0.15

( 0.32

)

8

0.021

0.041

DIM = INCHES

DIM = mm

Document Control #ML0066 Rev 2.0

Feb, 2008

14

MIN

MAX

MIN

( MAX

)

0.53

( 1.04

)

o

o

2.18

)

( 2.29

�STK14C88-NF35U

Document Revision History

Revision

2.0

Date

February 2008

Summary

New Document

SIMTEK STK14C88-NF35U Datasheet, February 2008

Copyright 2008, Simtek Corporation. All rights reserved.

This datasheet may only be printed for the expressed use of Simtek Customers. No part of the datasheet may be reproduced in any other

form or means without the express written permission from Simtek Corporation. The information contained in this publication is believed to be

accurate, but changes may be made without notice. Simtek does not assume responsibility for, or grant or imply any warranty, including

MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE regarding this information, the product or its use. Nothing herein constitutes a license, grant or transfer of any rights to any Simtek patent, copyright, trademark, or other proprietary right.

Document Control #ML0066 Rev 2.0

Feb, 2008

15

�