19-5480; Rev 8/10

DS1553

64kB, Nonvolatile, Year-2000-Compliant

Timekeeping RAM

www.maxim-ic.com

GENERAL DESCRIPTION

FEATURES

The DS1553 is a full-function, year-2000compliant (Y2KC) real-time clock/calendar (RTC)

with an RTC alarm, watchdog timer, power-on

reset, battery monitor, and 8k x 8 nonvolatile static

RAM. User access to all registers within the

DS1553 is accomplished with a byte-wide

interface as shown in Figure 1. The RTC registers

contain century, year, month, date, day, hours,

minutes, and seconds data in 24-hour BCD format.

Corrections for day of month and leap year are

made automatically.

Integrated NV SRAM, RTC, Crystal, Power-Fail

Control Circuit, and Lithium Energy Source

Clock Registers are Accessed Identically to the

Static RAM; These Registers are Resident in the

16 Top RAM Locations

Totally Nonvolatile with Over 10 Years of

Operation in the Absence of Power

Precision Power-On Reset

Programmable Watchdog Timer and RTC Alarm

BCD-Coded Year, Month, Date, Day, Hours,

Minutes, and Seconds with Automatic Leap Year

Compensation Valid Up to the Year 2100

Battery Voltage Level Indicator Flag

Power-Fail Write Protection Allows for 10%

VCC Power-Supply Tolerance

Lithium Energy Source is Electrically

Disconnected to Retain Freshness Until Power is

Applied for the First Time

Pin Configurations appear at end of data sheet.

ORDERING INFORMATION

PART

DS1553-85+

DS1553-100+

DS1553W-120+

DS1553W-150+

DS1553P-85+

DS1553P-100+

DS1553WP-120+

DS1553WP-150+

DS9034PCX+

VOLTAGE (V)

5.0

5.0

3.3

3.3

5.0

5.0

3.3

3.3

3

TEMP RANGE

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

PIN-PACKAGE

28 EDIP (0.740)

28 EDIP (0.740)

28 EDIP (0.740)

28 EDIP (0.740)

34 PowerCap*

34 PowerCap*

34 PowerCap*

34 PowerCap*

—

TOP MARK**

DS1553+85

DS1553+100

DS1553W+120

DS1553W+150

DS1553P+85

DS1553P+100

DS1553WP+120

DS1553WP+150

DS9034PCX

+Denotes a lead(Pb)-free/RoHS-compliant package.

*PowerCap required, must be ordered separately

**A “+” symbol anywhere on the top mark indicates a lead(Pb)-free package.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata.

1 of 20

�DS1553 64kB, Nonvolatile, Year-2000-Compliant Timekeeping RAM

PIN DESCRIPTION

EDIP

1

2

3

4

5

6

7

8

9

10

21

23

24

25

11

12

13

15

16

17

18

19

20

22

26

27

28

—

PIN

PowerCap

2

30

25

24

23

22

21

20

19

18

28

29

27

26

16

15

14

13

12

11

10

9

8

7

1

6

5

17

2, 3, 31–34

NAME

RST

A12

A7

A6

A5

A4

A3

A2

A1

A0

A10

A11

A9

A8

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

CE

OE

IRQ/FT

WE

VCC

GND

N.C

FUNCTION

Active-Low Power-On Reset Output (Open Drain)

Address Inputs

Data Input/Outputs

Active-Low Chip Enable

Active-Low Output Enable

Active-Low Interrupt/Frequency Test Output (Open Drain)

Active-Low Write Enable

Power-Supply Input

Ground

No Connection

2 of 20

�DS1553 64kB, Nonvolatile, Year-2000-Compliant Timekeeping RAM

DETAILED DESCRIPTION

The RTC registers in the DS1553 are double-buffered into an internal and external set. The user has direct

access to the external set. Clock/calendar updates to the external set of registers can be disabled and

enabled to allow the user to access static data. Assuming the internal oscillator is turned on, the internal

set of registers is continuously updated. This occurs regardless of external registers settings to guarantee

that accurate RTC information is always maintained.

The DS1553 has interrupt ( IRQ /FT) and reset ( RST ) outputs that can be used to control CPU activity.

The IRQ /FT interrupt output can be used to generate an external interrupt when the RTC register values

match user-programmed alarm values. The interrupt is always available while the device is powered from

the system supply, and it can be programmed to occur when in the battery-backed state to serve as a

system wakeup. Either the IRQ /FT or RST outputs can also be used as a CPU watchdog timer. CPU

activity is monitored and an interrupt or reset output is activated if the correct activity is not detected

within programmed limits. The DS1553 power-on reset can be used to detect a system power-down or

failure and can hold the CPU in a safe reset state until normal power returns and stabilizes. The RST

output is used for this function.

The DS1553 also contains its own power-fail circuitry, which automatically deselects the device when the

VCC supply enters an out-of-tolerance condition. This feature provides a high degree of data security

during unpredictable system operation brought on by low VCC levels.

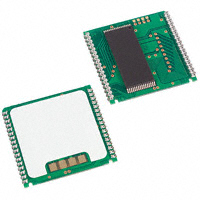

PACKAGES

The DS1553 is available in a 28-pin DIP and a 34-pin PowerCap module. The 28-pin DIP module

integrates the crystal, lithium energy source, and silicon in one package. The 34-pin PowerCap module

board is designed with contacts for connection to a separate PowerCap (DS9034PCX) that contains the

crystal and battery. This design allows the PowerCap to be mounted on top of the DS1553P after

completion of the surface-mount process. Mounting the PowerCap after the surface-mount process

prevents damage to the crystal and battery due to the high temperatures required for solder reflow. The

PowerCap is keyed to prevent reverse insertion. The PowerCap module board and PowerCap are ordered

separately and shipped in separate containers. The part number for the PowerCap is DS9034PCX.

Figure 1. Block Diagram

3 of 20

�DS1553 64kB, Nonvolatile, Year-2000-Compliant Timekeeping RAM

Table 1. Operating Modes

CE

OE

WE

DQ0–DQ7

MODE

POWER

VIH

X

X

High-Z

Deselect

Standby

VIL

X

VIL

DIN

Write

Active

VIL

VIL

VIH

DOUT

Read

Active

VIL

VIH

VIH

High-Z

Read

Active

VSO < VCC

很抱歉,暂时无法提供与“DS1553WP-150”相匹配的价格&库存,您可以联系我们找货

免费人工找货