DS21600/DS21602/DS21604

3.3V/5V Clock Rate Adapter

www.maxim-ic.com

GENERAL DESCRIPTION

FEATURES

The DS21600/DS21602/DS21604 are multiple-rate

clock adapters that convert between E-carrier and Tcarrier clocks rates. A T1 or E1 clock output,

CLKOUT1, is available, along with a higher multiple

rate clock output, CLKOUT2. CLKOUT1 and

CLKOUT2 are frequency locked to the clock input

CLKIN. The clock outputs, along with frame-sync

output, can be phase-aligned to a frame-sync input.

The devices are fully compatible with the LXP600A,

LXP602, and LXP604, and operate from either a 5V

or 3.3V supply. All operation modes include a

standard 8kHz output.

Direct Drop-In Replacement for LXP600ASE,

LXP602SE, and LXP604SE

Converts E-Carrier Clock Rates to T-Carrier

Clock Rates

Converts T-Carrier Clock Rates to E-Carrier

Clock Rates

3.3V or 5V Supply

Low Jitter Output

Multiple Output Clocks Synchronized to

Input Clock

8kHz Frequency-Locked Output for All

Operation Modes

No External Components Required

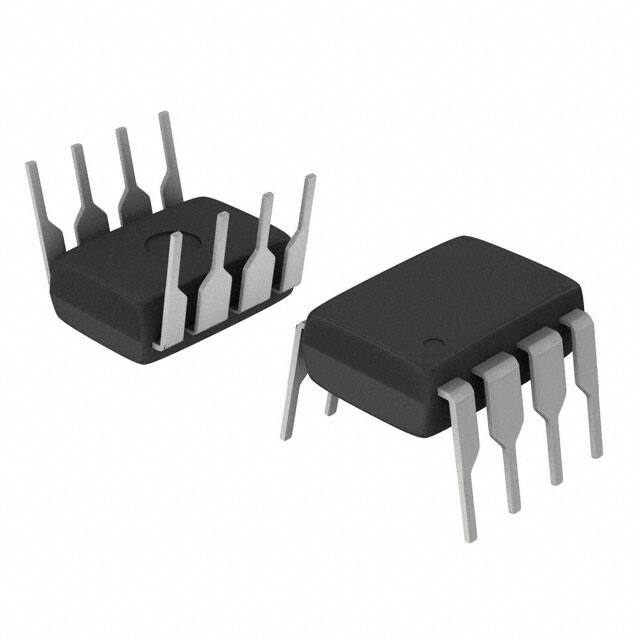

16-Pin SO and 8-Pin DIP

Industrial Temperature Range: -40°C to

+85°C

The DS21600/DS21602/DS21604 are available in

16-pin SO, and are rated for industrial temperatures.

ORDERING INFORMATION

PART

DS21600SN

DS21600SN+

DS21600N

DS21600N+

DS21602SN

DS21602SN+

DS21602N

DS21602N+

DS21604SN

DS21604SN+

DS21604N

DS21604N+

TEMP RANGE

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

PIN-PACKAGE

16 SO

16 SO

8 DIP

8 DIP

16 SO

16 SO

8 DIP

8 DIP

16 SO

16 SO

8 DIP

8 DIP

PIN CONFIGURATION

TOP VIEW

Dallas

Semiconductor

DS21600/2/4

+ Denotes a lead(Pb)-free/RoHS-compliant device.

FREQUENCY CONVERSIONS (MHz)

PART

DS21600

DS21602

DS21604

CLKIN

1.544

2.048

1.544

2.048

1.544

4.096

CLKOUT1

2.048

1.544

2.048

1.544

4.096

1.544

SO

CLKOUT2

6.144

6.176

8.192

6.176

8.192

6.176

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata.

1 of 12

REV: 011606

�TABLE OF CONTENTS

1.

PIN DESCRIPTION ................................................................................................ 3

1.1

2.

PIN NAME CROSS-REFERENCE TO LXP60X ......................................................................... 3

FUNCTIONAL DESCRIPTION ............................................................................... 4

2.1

2.2

3.

MODE SELECT ..................................................................................................................... 4

FRAME-SYNC INPUT............................................................................................................. 4

OUTPUT JITTER.................................................................................................... 4

3.1

JITTER TRANSFER................................................................................................................ 5

4.

OPERATING PARAMETERS................................................................................. 7

5.

PACKAGE INFORMATION.................................................................................. 11

6.

REVISION HISTORY............................................................................................ 12

LIST OF FIGURES

Figure 1-1. Block Diagram ........................................................................................................................3

Figure 3-1. Nominal Jitter Transer for 2.048MHz to 1.544MHz Conversion.............................................5

Figure 3-2. Nominal Jitter Transfer for 1.544MHz to 2.048MHz Conversion ............................................6

Figure 4-1. DS21600/DS21602 High-to-Low Frequency Conversion Frame-Sync Alignment .................8

Figure 4-2. DS21604 High-To-Low Frequency Conversion Frame-Sync Alignment ................................9

Figure 4-3. DS21600 Low-to-High Frequency Conversion Frame-Sync Alignment .................................9

Figure 4-4. DS21602 Low-to-High Frequency Conversion Frame-Sync Alignment ...............................10

Figure 4-5. DS21604 Low-to-High Frequency Conversion Frame-Sync Alignment ...............................10

LIST OF TABLES

Table 1-A. Pin Description ........................................................................................................................3

Table 1-B. Pin Name Cross-Reference to LXP60x...................................................................................3

Table 2-A. Frequency Conversions (MHz) ...............................................................................................4

Table 3-A. Output Jitter Specifications .....................................................................................................4

2 of 12

�1. PIN DESCRIPTION

Table 1-A. Pin Description

PIN

DIP

—

SO

1, 3, 6, 8, 10,

11, 13, 15

NAME

TYPE

N.C.

—

1

2

SYNCOUT

Output

2

4

CLKOUT2

Output

3

5

CLKIN

Input

4

7

CLKOUT1

Output

5

9

Vss

Supply

6

12

SEL

Input

7

14

SYNCIN

Input

8

16

VDD

Supply

FUNCTION

No Connect

Synchronization Output. An 8kHz output that can be

synchronized to the clock outputs.

Clock Output 2. T1 or E1 carrier clock output referenced to

CLKIN.

Clock Input. Reference Clock Input. CLKOUT1 and CLKOUT2

will be referenced to this clock.

Clock Output 1. T1 or E1 carrier clock output referenced to

CLKIN.

Ground

Clock Mode Select. Conversion mode select.

Synchronization Input. Used to synchronize the clock outputs

and SYNCOUT to CLKIN and SYNCIN. SYNCIN should be tied

high or low when not in use.

Positive Supply, 3.3V or 5V ±5%

1.1 Pin Name Cross-Reference to LXP60X

Table 1-B. Pin Name Cross-Reference to LXP60x

DS21600/DS21602

/DS21604

SYNCOUT

CLKOUT2

CLKIN

CLKOUT1

VSS

SEL

SYNCIN

N.C.

VDD

LXP600ALXP602/L

XP604

FSO

HFO

CLKI

CLKO

GND

SEL

FSI

N.C.

VCC

FUNCTION

Synchronization Pulse Output

Clock 2 Output

Clock Input

Clock 1 Output

Ground

Clock Mode Select

Synchronization Pulse Input

No Connect

Positive Supply

Figure 1-1. Block Diagram

CLKOUT2

CLKIN

ANALOG

PLL

FEEDBACK

CIRCUIT

OUTPUT

DIVIDER

CLKOUT1

Dallas Semiconductor

DS21600/DS21602/DS21604

SEL

FRAME SYNC

GENERATOR

SYNCIN

3 of 12

SYNCOUT

�2. FUNCTIONAL DESCRIPTION

A clock input at CLKIN is converted to an alternate clock rate available on CLKOUT1. A higher multiple-rate clock

also is available on CLKOUT2. Additionally, an 8kHz clock locked to CLKIN is always available at the SYNCOUT

pin. The SEL pin controls clock-rate conversion selection.

2.1

Mode Select

The SEL pin is used to select the operating frequencies. Table 2-A shows the SEL state for the various operating

modes of the DS21600, DS21602, and DS21604.

Table 2-A. Frequency Conversions (MHz)

PART

DS21600

DS21602

DS21604

2.2

SEL

0

1

0

1

0

1

CLKIN

1.544

2.048

1.544

2.048

1.544

4.096

CLKOUT1

2.048

1.544

2.048

1.544

4.096

1.544

CLKOUT2

6.144

6.176

8.192

6.176

8.192

6.176

Frame-Sync Input

In all cases, CLKOUT1 and CLKOUT2 are frequency-locked to CLKIN. CLKOUT1, CLKOUT2, and SYNCOUT

are phased-locked to SYNCIN when SYNCIN is asserted. The signal applied to SYNCIN can be 8kHz or some

integer subrate such as 1kHz, 2kHz, or 4kHz. Phase synchronization occurs within a maximum of 50ms when

SYNCIN is 8kHz.

3. OUTPUT JITTER

Table 3-A shows the output jitter specifications for 2.048MHz (or 4.096MHz) to 1.544MHz conversions (SEL = 1)

and 1.544MHz to 2.048MHz (or 4.096MHz) conversions (SEL = 0).

Table 3-A. Output Jitter Specifications

CLKIN

(MHz)

CLKOUT1

(MHz)

1.544

2.048

2.048 or

4.096

1.544

FREQUENCY

BAND

20Hz–100kHz

18kHz–100kHz

No bandlimiting

10Hz–40kHz

8kHz–40kHz

SPECIFICATION

VALUE

TYP

MAX

UNITS

G.823

G.823

TR62411

TR62411

TR62411

1.500

0.200

0.050

0.025

0.025

0.018

0.012

0.010

0.005

0.006

0.035

0.025

0.020

0.010

0.012

UIP-P

UIP-P

UIP-P

UIP-P

UIP-P

4 of 12

�3.1

Jitter Transfer

Figure 3-1 and Figure 3-2 show jitter transfer for 2.048MHz-to-1.544MHz conversions and vice versa.

Figure 3-1. Nominal Jitter Transfer for 2.048MHz-to-1.544MHz Conversion

JITTER GAIN (ns/ns)

2

1.8

1.6

1.4

1.2

1

0.8

0.6

0.4

0.2

0

0

10

20

30

40

50

60

70

80

JITTER FREQUENCY (kHz)

NOTE: THE TYPICAL PEAK JITTER GAIN OF THE DS21600/DS21602/DS21604 IS ABOUT 1.6 FOR CONVERSION FROM T1

TO E1. THE TYPICAL PEAK-JITTER GAIN OF THE LEVEL ONE DEVICE IS ABOUT 1.1. HOWEVER, THE JITTER GAIN FOR

THE DS21600/DS21602/DS21604 PEAKS IN THE 4kHz TO 8kHz RANGE, WHEREAS THE PEAK JITTER GAIN FOR THE

LXP6XX DEVICES SPANS A GREATER FREQUENCY RANGE (20kHz TO 40kHz).

5 of 12

�Figure 3-2. Nominal Jitter Transfer for 1.544MHz-to-2.048MHz Conversion

2.00

JITTER GAIN (ns/ns)

1.80

1.60

1.40

1.20

1.00

0.80

0.60

0.40

0.20

0.00

0

5

10

15

20

25

30

35

40

JITTER FREQUENCY (kHz)

NOTE: THE TYPICAL PEAK JITTER GAIN OF THE DS21600/DS21602/DS21604 IS ABOUT 1.6 FOR CONVERSION

FROM T1 TO E1. THE TYPICAL PEAK-JITTER GAIN OF THE LEVEL ONE DEVICE IS ABOUT 1.1. HOWEVER, THE

JITTER GAIN FOR THE DS21600/DS21602/DS21604 PEAKS IN THE 4kHz TO 8kHz RANGE, WHEREAS THE PEAK

JITTER GAIN FOR THE LXP6XX DEVICES SPANS A GREATER FREQUENCY RANGE (20kHz TO 40kHz).

6 of 12

�4. OPERATING PARAMETERS

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to Ground…………………………………………………………..-1.0V to +6.0V

Operating Temperature Range for DS21600SN, DS21602SN, DS21604SN……………………….-40°C to +85°C

Storage Temperature Range…………………………………………………………………………….-55°C to +125°C

Soldering Temperature..…………………………………………………….See IPC/JEDEC J-STD-020 Specification

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications

is not implied. Exposure to absolute maximum rating conditions for extended periods can affect device reliability.

RECOMMENDED DC OPERATING CONDITIONS

(TA = -40°C to +85°C)

PARAMETER

Logic 1

Logic 0

Supply Voltage

SYMBOL

VIH

VIL

VDD

CONDITIONS

(Note 1)

(Note 1)

3.3V

5V

MIN

2.0

-0.3

3.135

4.75

TYP

MIN

TYP

3.3

5

MAX

5.5

+0.8

3.465

5.25

UNITS

V

V

MAX

14

+1.0

1.0

UNITS

mA

A

A

mA

mA

V

DC CHARACTERISTICS

(VDD = 3.3V/5V 5%, TA = -40°C to +85°C.)

PARAMETER

Supply Current

Input Leakage

Output Leakage

Output Current (2.4V)

Output Current (0.4V)

SYMBOL

IDD

IIL

ILO

IOH

IOL

CONDITIONS

(Note 2)

(Note 3)

-1.0

-1.0

+4.0

7 of 12

�AC TIMING

(Figure 4-1, Figure 4-2, Figure 4-3, Figure 4-4, and Figure 4-5)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Capture Range on CLKIN

(Note 1)

±10,000

ppm

Lock Range on CLKIN

(Note 1)

±10,000

ppm

CLKIN Duty Cycle

SYNCIN Setup to CLKIN Rising

SYNCIN Hold After CLKIN Rising

tSU

tHI

(Note 1)

(Note 1)

(Note 1)

35

46

30

SYNCIN Pulse Width

tPW

(Note 1)

76

CLKOUT1 Delay from CLKIN Rising

tD

-15

-15

CLKOUT1 Duty Cycle

SYNCOUT Delay from CLKOUT2

CD

tDF

3.3V (Note 1)

5V (Note 1)

(Note 1)

(Note 1)

SYNCOUT Pulse Width

tSPW

(Note 1)

CLKOUT1 Delay from CLKOUT2

Rising

tDH

3.3V (Note 1)

Rise/Fall Time on CLKIN, SYNCIN

tRF

Rise/Fall Time on CLKOUT1,

SYNCOUT, CLKOUT2 (Note 4)

tRF

Guaranteed by design.

Note 2:

100pF load on all outputs.

Note 3:

0V < VIN < VDD.

Note 4:

100pF load on CLKOUT1, SYNCOUT, CLKOUT2.

0

0

50

-5

CLKIN

period

+41

+22

30

CLKOUT

1 period

-15

3.3V (Note 1)

5V (Note 1)

3.3V (Note 1)

5V (Note 1)

Note 1:

65

0

+15

Figure 4-1. DS21600/DS21602 High-to-Low Frequency Conversion Frame-Sync

Alignment

SYNCIN

CLKOUT1

(1.544MHz)

SYNCOUT

tSU

tPW

tHI

tD

tDH

tSPW

tDF

CLKOUT2

(6.176MHz)

8 of 12

ns

ns

%

ns

ns

60

40

75

40

CLKIN

(2.048MHz)

%

ns

ns

ns

ns

ns

�Figure 4-2. DS21604 High-To-Low Frequency Conversion Frame-Sync Alignment

CLKIN

(4.096MHz)

tSU

tHI

SYNCIN

tPW

CLKOUT1

(1.544MHz)

tD

tDH

SYNCOUT

tSPW

tDF

CLKOUT2

(6.176MHz)

Figure 4-3. DS21600 Low-to-High Frequency Conversion Frame-Sync Alignment

CLKIN

(1.544MHz)

tSU

SYNCIN

CLKOUT1

(2.048MHz)

SYNCOUT

tHI

tPW

tD

tDH

tSPW

tDF

CLKOUT2

(6.144MHz)

9 of 12

�Figure 4-4. DS21602 Low-to-High Frequency Conversion Frame-Sync Alignment

CLKIN

(1.544MHz)

tHI

tSU

SYNCIN

tPW

tD

CLKOUT1

(2.048MHz)

tDH

tSP

SYNCOUT

tDF

CLKOUT2

(8.192MHz)

Figure 4-5. DS21604 Low-to-High Frequency Conversion Frame-Sync Alignment

CLKIN

(1.544MHz)

tHI

tSU

SYNCIN

tPW

tDH

CLKOUT1

(4.096MHz)

tD

SYNCOUT

TSPW

tDF

CLKOUT2

(8.192MHz

)

10 of 12

�5. PACKAGE INFORMATION

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

PACKAGE TYPE

PACKAGE CODE

DOCUMENT NO.

16 SO

W16+11

21-0042

8 PDIP

P8+8

21-0043

11 of 12

�6. REVISION HISTORY

REVISION

082100

083100

090100

011101

092801

032002

032803

113004

112105

011606

DESCRIPTION

Preliminary release.

Added package specifications.

Correct operating voltage range.

Added mechanical drawing for DIP package.

Added jitter specifications and pin list for all packages; added timing

diagrams.

Updated jitter specifications.

Added 3.3V operation specifications.

Added the spec for soldering temperature in the Absolute Maximum Ratings

section.

Changed timing specs in DC Characteristics and AC Timing tables to

guaranteed by design.

Added lead-free packages to Ordering Information on page 1.

12 of 12

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No

circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2006 Maxim Integrated Products

The Maxim logo is a registered trademark of Maxim Integrated Products, Inc. The Dallas logo is a registered trademark of Dallas Semiconductor Corporation.

12 of 12

�