080807

LE

AVAILAB

DS2430A

256 位 1-Wire EEPROM

特性

256 位电可擦除、可编程只读存储器

(EEPROM) 和 64 位一次性可编程应用寄存

器

唯一的、工厂光刻并经过检测的 64 位注册

码 (8 位家族码 + 48 位序列号 + 8 位 CRC

校验码),保证绝对、唯一的识别

内置多点控制器可保证器件兼容于其它

MicroLAN 总线产品

EEPROM 按页组织,每页 32 个字节,可随

机存取

将控制、寻址、数据和电源集于一个数据

引脚

可直接与微控制器的一个端口连接,通信

速度为 16.3kbps

8 位家族码表明需要读取的是 DS2430A

当读取探头首次作用一个电压时,将发出

在线检测应答

采用低成本 TO-92 或 6 引脚 TSOC 表面贴

封装

在-40°C 至+85°C 温度范围、2.8V 至 6.0V

电压范围内可进行读、写操作

定购信息

DS2430A

DS2430AP

DS2430A/T&R

DS2430AP/T&R

DS2430A+

DS2430AP+

DS2430A+T&R

DS2430AP+T&R

DS2430AX

DS2430AX-S

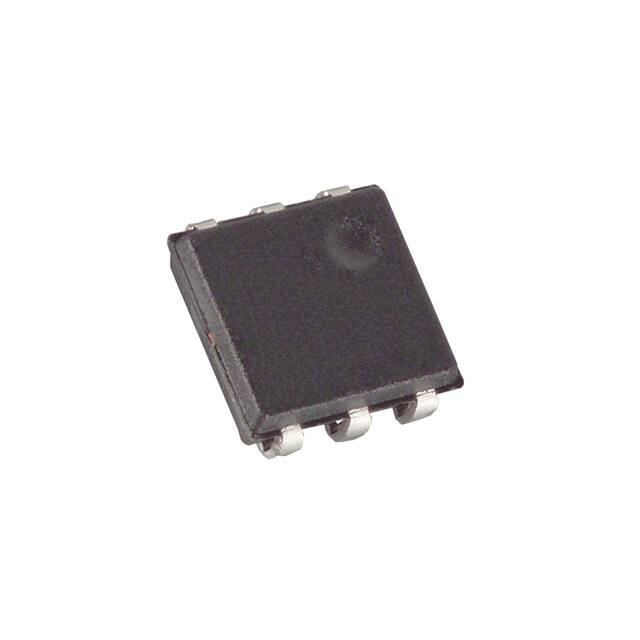

TSOC 封装

引脚排列

TO-92 封装

6 引脚 TSOC 封装

TO-92 封装,卷带包装

TSOC 封装,卷带包装

TO-92 封装

6 引脚 TSOC 封装

TO-92 封装,卷带包装

TSOC 封装,卷带包装

倒装芯片, 10k 卷带包装

倒装芯片, 2.5k 卷带包装

TO-92

DALLAS

DS2430A

1

6

2

5

3

4

顶视图

3.7mm x 4.0mm x 1.5mm

侧视图

参见机械尺寸部分

4

3

2430A

rrd#xx

1 2 3

1

2

倒装芯片,顶视图及

光刻标记,触点不可

见。

“rrd” = 版本/日期

#xx = 批号

封装图请参考 56G7016-001 。

1 2 3

底视图

底视图

参见机械尺寸部分

注:TO-92 封装的引脚在卷带内的排列间隔大

约为 100mil (2.54mm) ,详细信息请参考图56G0006-003。

引脚说明

引脚 1

引脚 2

引脚 3

引脚 4

引脚 5

引脚 6

TO-92

地

数据

浮空

––––

––––

––––

TSOC

地

数据

浮空

浮空

浮空

浮空

倒装片

地

数据

浮空

浮空

––––

––––

+表示无铅封装。

本文是英文数据资料的译文,文中可能存在翻译上的不准确或错误。如需进一步确认,请在您的设计中参考英文资料。

有关价格、供货及订购信息,请联络Maxim亚洲销售中心:10800 852 1249 (北中国区),10800 152 1249 (南中国区),

或访问Maxim的中文网站:china.maximintegrated.com。

�DS2430A

说明

DS2430A 256 位 1-Wire EEPROM用于识别和保存产品的相关信息,识别码和这些相关信息可以通

过最少的接口(例如,微控制器的一个端口)进行访问。DS2430A内部包含由工厂激光刻制的 64

位注册码、256 位用户可编程EEPROM和 64 位一次性可编程应用寄存器。其中 64 位注册码由唯

一的 48 位序列号、8 位CRC校验码和 8 位家族码 (14h)组成。DS2430A读写操作所需要的电源可

从 1-Wire®传输线获取。数据传输按照 1-Wire总线协议进行,只需要一根数据线和一根地线。激

光刻制在每个DS2430A中的 48 位序列号是绝对唯一的,可作为器件的ID。采用紧凑的TO-92 和

TSOC封装,能够采用标准的器件装配设备安装到印制电路板上或进行引线。典型应用包括:储

存校准系数、板卡识别以及产品升级的状态信息等。

概述

图 1 中的框图说明了 DS2430A 的主控部分和存储单元之间的关系。DS2430A 有四个主要的数据

部件:1)64 位光刻 ROM,2)256 位数据 EEPROM 和暂存器,3)64 位一次性编成应用寄存器

和暂存器,4)8 位状态存储器。1-Wire 协议分层结构见图 2。总线主机必须首先提供四个 ROM

操作命令中的一个:1)Read ROM, 2) Match ROM, 3)Search ROM, 4)Skip ROM。图 8 说明了

协议对这些 ROM 操作命令的要求。成功地执行了 ROM 操作命令后,就可以进行存储器操作,主

机可以发出四条存储器操作命令中的任何一个。图 6 说明了有关这些存储器操作命令的协议。所

有数据读写都是最低有效位在前。

激光刻制的 64 位 ROM

每个DS2430A都有一个 64 位的唯一ROM代码。前 8 位是 1-Wire家族代码 (14h),然后是 48 位的

唯一序列号,最后 8 位是前 56 位的CRC检验码(图 3)。1-Wire CRC校验码由一个包含移位寄存

器和异或门的多项式发生器产生,如图 4 所示。生成多项式为X8 + X5 + X4 + 1。关于Dallas 1-Wire

循环冗余校验的更多信息请参见应用笔记 27。移位寄存器初值为零。然后,从家族代码的最低有

效位开始,每次移入一位。当家族代码第 8 位移入后,再移入序列号。当序列号第 48 位也移入

后,留在移位寄存器中的就是CRC值。移入八位CRC校验码后,移位寄存器应该全部归零。

1-Wire 和 iButton 是Dallas Semiconductor的注册商标。

2 of 16

�DS2430A

DS2430A 的内部框图

图1

3 of 16

�DS2430A

1-Wire 协议的层次结构

64 位光刻 ROM

MSB

图2

图3

8-Bit CRC Code

1-Wire CRC 产生器

LSB MSB

48-Bit Serial Number

8-Bit Family Code (14h)

LSB MSB

LSB

图4

Polynomial = X8 + X5 + X4 + 1

4 of 16

�DS2430A

存储器

DS2430A 的存储器由三个独立部分组成,分别为数据存储器、应用寄存器和状态寄存器(见图

5)。每个数据存储器和应用寄存器都有其对应的暂存单元,称为暂存器,当向该器件写入数据

时,暂存器可作为缓冲器使用。数据存储器可在需要时反复读写,而应用寄存器只能编程一次。

一旦对应用寄存器进行编程,它将自动进入写保护状态。状态寄存器用于指示应用寄存器是否已

被锁定或是否可用于存储数据。在应用寄存器被编程之前,读出的状态寄存器值是 FFh。当把暂

存器的数据写入到应用寄存器时,状态寄存器的两个最低有效位将被清零,此后读出的状态寄存

器结果是 FCh 。

DS2430A 的存储器映射图

图5

存储器功能命令

图 6 所示的存储器功能流程图描述了访问 DS2430A 的不同存储器时需要遵循的协议。本文将在后

面举例说明。

Write Scratchpad [0Fh]

发出 Write Scratchpad 命令后,主机必须紧接着发出一个字节的地址,随后将需要送入数据存储器

的数据写入暂存器。DS2430A 每收到一个字节后地址会自动加 1。当地址为 1Fh 的暂存器也收到

了数据字节以后,地址计数器将返回到 00h,可继续写入下一个字节,直到主机发出复位脉冲。

Read Scratchpad [AAh]

该命令用于在将暂存器数据拷贝到 EEPROM 存储器之前对数据进行验证。主机发出 Read

Scratchpad 命令后,要紧接着发出一个字节的地址,表明读取数据的起始地址。主机每读取一个

字节,DS2430A 地址将自动加 1。读取地址为 1Fh 的数据后,地址计数器将返回到 00h,可继续

读取下一个字节,直到主机发出复位脉冲。

5 of 16

�DS2430A

存储器功能流程图 图 6

Copy Scratchpad [55h]

存入暂存器的数据经过确认后,主机便可发出 Copy Scratchpad 命令和确认字节 A5h,把数据从暂

存器写入 EEPROM 存储器。该命令总是把暂存器的全部数据拷贝到 EEPROM。如果只想改变

EEPROM 中几个字节的数据,在发出 Write Scratchpad 和 Copy Scratchpad 命令之前,暂存器中应

该包含了最新的 EEPROM 数据。发出该命令后,数据线要保持逻辑高电平状态至少 10ms。

Read Memory [F0h]

Read Memory 命令用于读取 EEPROM 数据存储器中的部分或全部数据,或把数据存储器中的全部

内容拷贝到暂存器为仅改变 EEPROM 部分字节做准备。当把数据从数据存储器拷贝到暂存器并

进行读取时,主机必须发出 Read Memory 命令和一个字节的数据读取起始地址。主机每读取一个

字节的数据,DS2430A 的地址自动加 1。读取地址 1Fh 的数据后,地址计数器将返回到 00h,以

便继续读取下一个字节,直到主机发出复位脉冲。如果只希望将数据存储器中的全部数据拷贝到

暂存器中,而不必读取数据,主机可以在发出命令字节后,立即发送复位脉冲。

6 of 16

�DS2430A

存储器功能流程图

图 6(续)

Write Application Register [99h]

该命令与 Write Scratchpad 命令基本相同,只是它是向 64 位应用寄存器的暂存器写入数据。在发

出命令代码后,主机必须提供一个字节的地址,随后发送要写入的数据。DS2430A 每收到一个字

节后地址会自动加 1。当地址为 07h 的暂存器收到数据后,地址计数器将返回到 00h,可继续写入

下一个字节,直到主机发出复位脉冲。只要应用寄存器未被锁定,就可以使用 Write Application

Register 命令。如果向已经锁定的应用寄存器发出该命令,写入寄存器暂存器的数据将会丢失。

Read Status Register [66h]

状态寄存器的主要作用是向主机指示应用寄存器是否已编程并锁定。在主机发出读状态寄存器命

令后,在接收状态信息之前必须发出确认字节 00h。如果应用寄存器已被编程并锁定,8 位状态寄

存器中的 2 个最低有效位为 0,而其余各位全部为 1。主机可以在任何时候通过发出复位脉冲结束

读状态命令。

7 of 16

�DS2430A

存储器功能流程图 图 6(续)

Read Application Register [C3h]

该命令用来读取应用寄存器或寄存器暂存器。只要应用寄存器未锁定,将接收来自寄存器暂存器

的数据。当应用寄存器锁定时,DS2430A 将从应用寄存器传送数据,使得寄存器暂存器的内容无

法读取。状态寄存器的内容确定通过该命令接收到的数据来自何处。发出 Read Application

Register 命令后,主机必须提供一个字节的数据读取起始地址。主机每读取一个字节,DS2430A

地址将自动加 1。读取地址 07h 的数据后,地址计数器将返回到 00h,以便继续读取下一个字节,

直到主机发送复位脉冲。

Copy & Lock Application Register [5Ah]

当存储到寄存器暂存单元的数据确认后,主机便可发出 Copy & Lock Application Register 命令和

确认字节 A5h,把数据从寄存器暂存器全部写入到应用寄存器并对应用寄存器进行写保护。主机

也可以通过发送复位脉冲(而不是确认字节)取消该命令。在确认字节发出后,应用寄存器中将

包含寄存器暂存器的数据。随后对应用寄存器进行的写访问将被拒绝。注意:Copy & Lock

Application Register 命令只能执行一次。

8 of 16

�DS2430A

1-Wire 总线系统

1-Wire 总线系统是由一个单总线主机和一个或多个从器件组成。在任何情况下,DS2430A 都是作

为从器件。总线主机通常是一个微控制器。对 1-Wire 总线系统的讨论分为 3 个部分:硬件配置、

处理流程和 1-Wire 信令 (信号类型和时序)。1-Wire 协议根据特定时隙总线的状态工作,这些特定

时隙始于总线主机发出的同步脉冲的下降沿。

硬件配置

1-Wire 总线系统只有一条数据线。因此,在适当时间驱动总线上的每个器件十分重要。为使上述

操作易于实现,总线上的每个器件需要具有漏极开路或三态输出。图 7 所示是 DS2430A 的内部开

漏输出等效电路。多节点总线由一个 1-Wire 总线和多个从器件组成,DS2430A 的标准传输速率

为 16.3kbps,需要图 7 所示的上拉电阻。1-Wire 总线的空闲状态为高电平。如果由于某种原因需

要暂停工作,稍后还要恢复工作的话,必须将总线置于空闲状态。否则,如果总线置为低电平的

时间超过 120µs,总线上的器件将被复位。

硬件配置

图7

RPU

RPU

注意:根据不同的 1-Wire通信速率和总线特征,上拉电阻的阻值应在 1.5kΩ 到 5kΩ范围内选择。

只向一个器件进行写操作时,选择 2.2kΩ 的上拉电阻、VPUP 不低于 4.0V就足够了;当对多个

DS2430A进行写操作时或VPUP电压较低时,在器件将数据从暂存器拷贝到EEPROM时,需要一个

低阻值的上拉电阻接到VPUP。

9 of 16

�DS2430A

ROM 功能流程图

图8

10 of 16

�DS2430A

处理流程

通过 1-Wire 端口访问 DS2430A 的操作流程如下:

初始化

ROM 功能命令

存储器功能命令

传输/数据

初始化

1-Wire 总线上的所有数据处理均从初始化开始。该初始化过程由主机发送的复位脉冲和从器件发

送的在线应答脉冲组成。

在线应答脉冲用于通知主机 DS2430A 已挂接在总线上,并已准备就绪。有关这方面的详细内容,

请参阅“1-Wire 信令”部分。

ROM 功能命令

一旦主机检测到在线应答脉冲,就可以发出四条 ROM 功能命令中的一个。所有 ROM 功能命令的

字长均是 8 位。下面是这些 ROM 命令的简要介绍 (参考图 8 所示的流程图)。

Read ROM [33h]

主机用该命令来读取 DS2430A 的 8 位家族码、唯一的 48 位序列号和 8 位 CRC 码。该命令适用于

总线上只有一个从器件的情况。如果总线上挂接有多个从器件,那么当所有从器件都试图在同一

时刻传送数据时,就会发生数据冲突 (开漏输出将产生“线与”结果),将会导致主机读取的家族

码和 48 位序列号与 CRC 不匹配。

Match ROM [55h]

发出 Match ROM 命令后紧跟着要发出 64 位 ROM 码,总线主机利用该命令访问多点总线上某个

特定的 DS2430A。只有内部 ROM 码与主机发出的 64 位 ROM 码匹配的 DS2430A 才会响应随后

的存储器功能命令,而其他与 64 位 ROM 码不匹配的所有从器件将等待复位脉冲。总线上有一个

或多个从器件时都可使用该命令。

Skip ROM [CCh]

在单点总线系统中,主线主机可使用该命令在不提供从器件 64 位 ROM 码的情况下直接执行存储

功能,从而节省时间。如果总线上挂接有多个从器件,Skip ROM 命令后发出读命令将会导致总

线冲突,因为会有多个从器件同时发送数据 (开漏下拉将产生一个“线与”结果)。

Search ROM [F0h]

当一个系统初始化时,总线主机可能不知道在 1-Wire 总线上挂接有多少个器件,也不知道各个器

件的 64 位 ROM 码。总线主机利用 Search ROM 命令通过采用排除法可以确认总线上所有从机器

件的 64 位 ROM 码。Search ROM 是以下三个步骤的简单重复,这三个步骤是:读一位、读该位

的补码、写入一位所希望的数值。总线主机对 ROM 的每一位都执行这三个步骤。经过一个完整

循环后,总线主机就可得到某个器件的 ROM 码。继续进行类似的过程可获悉其他从器件的 ROM

码。有关 Search ROM 的深入讨论,请参考应用笔记 187,其中还给出了一个实例。

11 of 16

�DS2430A

1-Wire 信令

DS2406 需要严格的协议来保证数据的完整性。该协议包括通过一条总线传送的四种信令:复位脉

冲和在线应答的复位过程、写 0 时隙、写 1 时隙、读数据时隙。除应答脉冲外,所有信号都由总

线主机发出。通过DS2430A进行通信时所需要的初始化时序如图 9 所示。复位脉冲后的在线应答

脉冲表明DS2430A已准备好接收ROM命令。总线主机发送 (TX) 一个复位脉冲 (tRSTL,最短时间为

480µs),然后总线主机释放总线并进入接收 (RX)模式,这时 1-Wire总线通过上拉电阻被拉至高电

平。当在数据引脚检测到上升沿后,DS2430A将在等待 (tPDH,15µs至 60µs)后发送在线应答脉冲

(tPDL,60µs至 240µs)。

复位和应答脉冲的初始化时序

图9

为了避免 1-Wire总线上的其它器件屏蔽中断信号,tRSTL + tR应始终小于 960µs。

读/写时隙

读、写时隙的定义如图 10 所示。主机通过拉低数据线来启动所有时隙。数据线的下降沿通过触发

内部延迟电路使 DS2430A 与主机同步。在写时隙中,延迟电路可确定什么时候 DS2430A 采样数

据线。对读数据时隙来说,如果发送的是“0”,那么延迟电路将决定 DS2430A 数据线保持为低

的时间。如果数据位是“1”,则 DS2430A 将保持读时隙不变。

12 of 16

�DS2430A

读/写时序图

图 10

Write-1 Time Slot

Write-0 Time Slot

Read-data Time Slot

13 of 16

�DS2430A

存储器功能实例

例:向数据存储器单元 0006 和 0007 写入 2 个字节,然后读取数据存储器的全部数据。

主机工作状态

TX

RX

TX

TX

TX

TX

TX

RX

TX

TX

TX

RX

TX

RX

TX

TX

TX

数据 (LSB 在先)

Reset

Presence

CCh

0Fh

06h

Reset

Presence

CCh

AAh

06h

Reset

Presence

CCh

55h

A5h

TX

TX

RX

TX

TX

TX

RX

TX

RX

Reset

Presence

CCh

F0h

00h

Reset

Presence

说明

复位脉冲 (480µs 至 960µs)

在线应答脉冲

发送“Skip ROM”命令

发送“Write Scratchpad”命令

起始地址 = 06h

向暂存器写入 2 个字节的数据

复位脉冲

在线应答脉冲

发送“Skip ROM” 命令

发送“Read Scratchpad”命令

起始地址 = 06h

读暂存器数据并进行校验

复位脉冲

在线应答脉冲

发送“Skip ROM”命令

发送“Copy Scratchpad”命令

发送确认字节

总线主机保持数据线为高电平 10ms,为从器件把数

据从暂存器写入 EEPROM 提供能源。

复位脉冲

在线应答脉冲

发送“Skip ROM”命令

发送“Read Memory”命令

起始地址 = 00h

读 EEPROM 数据页

复位脉冲

在线应答脉冲

14 of 16

�DS2430A

ABSOLUTE MAXIMUM RATINGS*

Voltage on DATA to Ground

Operating Temperature Range

Storage Temperature Range

Soldering Temperature

*

-0.5V to +7.0V

-40°C to +85°C

-55°C to +125°C

See J-STD-020A Specification

This is a stress rating only and functional operation of the device at these or any other conditions

above those indicated in the operation sections of this specification is not implied. Exposure to

absolute maximum rating conditions for extended periods of time may affect reliability.

DC ELECTRICAL CHARACTERISTICS

PARAMETER

Logic 1

Logic 0

Output Logic Low @ 4mA

Output Logic High

Input Load Current (DATA pin)

Programming Current

CAPACITANCE

PARAMETER

Capacitance

EEPROM

PARAMETER

Write/Erase Cycles

Data Retention(at 85°

C)

SYMBOL

VIH

VIL

VOL

VOH

IL

IP

MIN

2.2

-0.3

0.1

VPUP

5

SYMBOL

CD

MIN

TYP

SYMBOL

NCYCLE

tDR

MIN

100k

10

AC ELECTRICAL CHARACTERISTICS

PARAMETER

Time Slot

Write 1 Low Time

Write 0 Low Time

Read Low Time

Read Data Valid

Release Time

Read Data Setup

Recovery Time

Reset Time High

Reset Time Low

Presence Detect High

Presence Detect Low

Programming Time

(-40°C to +85°C; VPUP = 2.8V to 6.0V)

SYMBOL

tSLOT

tLOW1

tLOW0

tLOWR

tRDV

tRELEASE

tSU

tREC

tRSTH

tRSTL

tPDH

tPDL

tPROG

MIN

60

1

60

1

0

1

480

480

15

60

15 of 16

TYP

TYP

MAX

+0.8

0.4

6.0

15

500

UNITS

V

V

V

V

µA

µA

MAX

800

UNITS

pF

NOTES

1, 6

1, 9

1

1, 2

3

10

(tA = +25°C)

NOTES

7

(VPUP = 5.0V; tA = +25°C)

MAX

UNITS

years

NOTES

10

(-40°C to +85°C; VPUP=2.8V to 6.0V)

TYP

15

15

MAX

120

15

120

15

45

1

960

60

240

10

UNITS

µs

µs

µs

µs

µs

µs

µs

µs

µs

µs

µs

µs

ms

NOTES

13

13

11, 12

5

4

8

�DS2430A

注释:

1) 所有电压均以地为参考。

2) VPUP = 外部上拉电压。

3) 为输入负载到参考地的电流。

4) 在复位脉冲的高电平结束之前,不能开始其它复位操作或通信过程。

5) 读数据建立时间是指主机为读取数据而必须将 1-Wire 总线拉低的时间。在下降沿 1µs 内数据

应保证有效。

6) VIH 是外部上拉电阻和 VPUP 的函数。

7) 首次加电时,数据引脚的电容可能会达到 800pF。如果采用一个 5kΩ上拉电阻将数据线拉高至

VPUP,则上电 5µs 之后该寄生电容就不会对正常通信产生影响了。

8) 复位低电平时间(tRSTL)的最大值应被限制在 960µs 以内,这样中断信号可以工作;否则可能会

掩盖或屏蔽中断脉冲。

9) 在某些低电压情况下,VILMAX 可能必须降至 0.5V,以保证有效的在线应答脉冲。

10) Copy Scratchpad 命令最多需要 10ms,在此期间 1-Wire 总线电压不能低于 2.8V。

11) 上拉电阻的阻值取决于 1-Wire 总线的通讯速度和总线负载的特性,最佳值范围为 1.5kΩ到

5kΩ。

12) 主机的读时隙最佳采样点应尽可能靠近 15µs 的 tRDV,但不能超过 tRDV。执行读 1 时隙时,这

样做会给上拉电阻留出足够的时间来使总线恢复为高电平;执行读 0 时隙时,这将确保在最快

的 1-Wire 器件释放总线前执行读操作。

13) 主机发出的低脉冲的持续时间最小值为 1µs,但应尽可能的窄。这样,1-Wire 器件无论写 1 还

是读 1,就都能保证上拉电阻在数据线被采样之前将数据线恢复到高电平状态。

Maxim北京办事处

北京8328信箱 邮政编码100083

免费电话:800 810 0310

电话:010-6211 5199

传真:010-6211 5299

Maxim不对Maxim产品以外的任何电路使用负责,也不提供其专利许可。Maxim保留在任何时间、没有任何通报的前提下修改产品资料和规格的权利。电气

特性表中列出的参数值(最小值和最大值)均经过设计验证,数据资料其它章节引用的参数值供设计人员参考。

Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

©

2007 Maxim Integrated

16

Maxim标志和Maxim Integrated是Maxim Integrated Products, Inc.的商标。

�

很抱歉,暂时无法提供与“DS2430AP+T&R”相匹配的价格&库存,您可以联系我们找货

免费人工找货- 国内价格

- 1+8.08599

- 10+7.46399

- 30+7.33959