Click here to ask about the production status of specific part numbers.

MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA,

Delta-Sigma ADC with I2C Interface

General Description

Benefits and Features

The MAX11261 is a 6-channel, 24-bit delta-sigma ADC

that achieves exceptional performance while consuming

very low power. Sample rates up to 16ksps allow precision

DC measurements. The device also features a 64-entry,

on-chip FIFO to offload the host processor. The

MAX11261 communicates through an I2C-compatible serial interface and is available in a small, wafer-level package (WLP).

● Analog Supply

• 2.7V to 3.6V

The MAX11261 offers a 6.2nV/√Hz noise programmable

gain amplifier (PGA) with gain settings from 1x to 128x.

The integrated PGA provides isolation of the signal inputs

from the switched capacitor sampling network. The PGA

also enables the MAX11261 to interface directly with highimpedance sources without compromising the available

dynamic range.

The MAX11261 operates from a single 2.7V to 3.6V analog supply. The digital supply range is 1.7V to 2.0V (internal LDO off) and 2.0V to 3.6V (internal LDO on) enabling

communication with 1.8V, 2.5V, 3V, or 3.3V logic.

Applications

●

●

●

●

●

Wearable Electronics

Medical Equipment

Weigh Scales

Pressure Sensors

Battery-Powered Instrumentation

● Digital Supply

• Internal LDO Disabled—1.7V to 2.0V

• Internal LDO Enabled—2.0V to 3.6V

● 3ppm INL (typ)

● PGA

• Gains of 1, 2, 4, 8, 16, 32, 64, 128

• Low-Noise Mode, 6.2nV/√Hz Noise

• Low-Power Mode, 10nV/√Hz Noise

● Input-Referred Noise

• PGA Low-Noise Mode, Gain of 64 at 1ksps

Continuous, 0.15μVRMS

●

●

●

●

●

●

●

●

●

●

●

●

●

Fully Differential Signal and Reference Inputs

Internal System Clock of 8.192MHz

I2C-Compatible Serial Interface

Supports Standard, Fast-Mode, and Fast-Mode Plus

I2C Specifications

64-Entry, On-Chip FIFO

Hardware Interrupt for Input Monitoring and FIFO

Usage

On-Demand Self and System Gain and Offset

Calibration

User-Programmable Offset and Gain Registers

Two Power-Down Modes (SLEEP and STANDBY)

Low Power Dissipation

ESD Rating: ±2.5kV (HBM), 750V (CDM)

-40°C to +85°C Operating Temperature Range

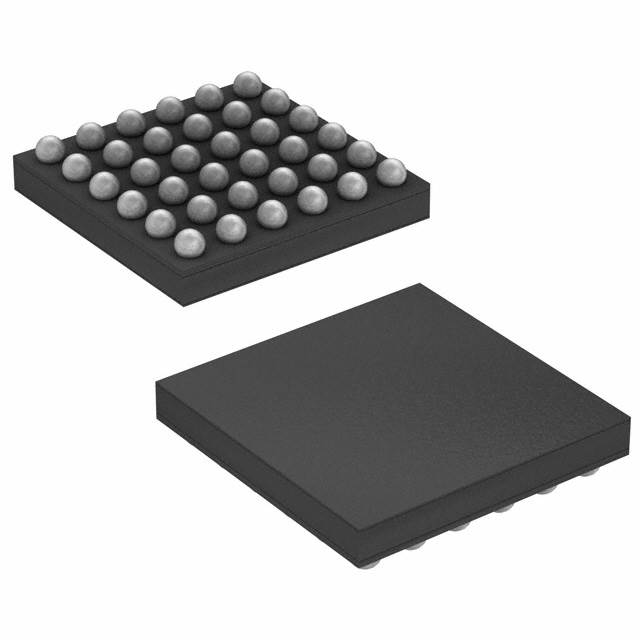

6 x 6 Bump, 0.4mm Pitch, 2.838mm x 2.838mm x

0.5mm WLP

Ordering Information appears at end of data sheet.

19-100250; Rev 1; 11/20

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Typical Application Circuit

2.7V TO 3.6V

2.0V TO 3.6V

REF

10nF

1µF

1µF

AIN0P

REFN

REFP

AVDD

DVDD

1nF

C0G

SYNC

RSTB

ADR0

AIN0N

ADR1

MAX11261

SCL

µC

SDA

AIN5P

1nF

C0G

RDYB_INTB

AIN5N

GPO0

GPO5 GPOGND CAPP

CAPN

CAPREG AVSS DGND

220nF

0603

X7R

1nF

C0G

RESISTIVE BRIDGE MEASUREMENT CIRCUIT, I2C CONFIGURATION

www.maximintegrated.com

Maxim Integrated | 2

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Absolute Maximum Ratings

AVDD to AVSS ...................................................... -0.3V to +3.9V

DVDD to DGND..................................................... -0.3V to +3.9V

AVSS to DGND ..................................................... -0.3V to +0.3V

Analog Inputs: ..............................................................................

GPOGND to AVSS or DGND ................................ -0.3V to +0.3V

(AIN_P, AIN_N, CAPP, CAPN, REFP, REFN) to AVSS ..-0.3V to

the lower of +3.9V or (VAVDD + 0.3V)

GPO_ to GPOGND or AVSS or DGND .... -0.3V to to the lower of

+3.9V or (VAVDD + 0.3V)

Digital Inputs:................................................................................

(RSTB, SYNC, SCL, SDA, ADR0, ADR1) to DGND ... 0.3V to the

lower of +3.9V or (VDVDD + 0.3V)

Digital Outputs: .............................................................................

(RDYB_INTB, SDA, SYNC) to DGND ... -0.3V to (VDVDD + 0.3V)

CAPREG to DGND ................................................ -0.3V to +2.1V

Maximum Continuous Current into Any Pins Except GPO_

and GPOGND Pins ........................................................±50mA

Maximum Continuous Current into GPO_

and GPOGND Pins ........................................................150mA

Continuous Power Dissipation (TA = +70°C; WLP;

derate 21.7mW/°C above +70°C)................................1736mW

Operating Temperature Range .............................-40°C to +85°C

Junction Temperature ....................................................... +150°C

Storage Temperature Range ..............................-55°C to +150°C

Soldering Temperature (reflow) ........................................ +260°C

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the

device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

Package Information

36 WLP

Package Code

N362B2+2

Outline Number

21-0742

Land Pattern Number

Refer to Application Note 1891

THERMAL RESISTANCE, FOUR-LAYER BOARD

Junction to Ambient (θJA)

46°C/W

Junction to Case (θJC)

N/A

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages.

Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different

suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a

four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/

thermal-tutorial.

www.maximintegrated.com

Maxim Integrated | 3

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Electrical Characteristics

(VAVDD = 3.6V, VAVSS = 0V, VDVDD = 2.0V to 3.6V, VREFP - VREFN = VAVDD, DATA RATE = 1ksps, PGA low-noise mode, singlecycle conversion mode (SCYCLE = 1). TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1))

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

STATIC PERFORMANCE (SINGLE-CYCLE CONVERSION MODE)

PGA gain of 128,

single-cycle mode

at 1ksps data rate

Noise Voltage (Referred

to Input)

Vn

PGA gain of 128,

single-cycle mode

at 12.8ksps data

rate

PGA gain of 128,

continuous mode at

64ksps data rate

Integral Nonlinearity

ZERR

Zero Drift

ZDrift

Full-Scale Error (Note 2

and Note 3)

FSE

Common-Mode

Rejection

0.19

PGA low-power

mode

0.26

PGA low-noise

mode

0.83

PGA low-power

mode

1.16

PGA low-noise

mode

0.83

PGA low-power

mode

1.16

μVRMS

INL

Zero Error

Full-Scale Error Drift

PGA low-noise

mode

3

After system zero-scale calibration

After system full-scale calibration

FSEDrift

CMR

15

ppm

1

μV

50

nV/°C

2

ppmFSR

0.05

ppm

FSR/°C

DC rejection

110

130

50Hz/60Hz rejection (Note 4)

110

130

DC rejection with PGA gain 128

80

95

dB

AVDD, AVSS DC

Supply Rejection Ratio

PSRRA

DC rejection

75

95

dB

AVDD, AVSS DC

SupplyRejection Ratio

PSRRA

50Hz/60Hz rejection (Note 4)

75

95

dB

AVDD, AVSS DC

Supply Rejection Ratio

PSRRA

DC rejection with PGA gain 128

65

75

dB

DVDD DC Supply

Rejection Ratio

DC rejection

103

115

PSRRD

50Hz/60Hz rejection (Note 4)

103

115

DC rejection with PGA gain 128

86

110

dB

PGA

Gain Setting

Noise-Spectral Density

www.maximintegrated.com

1

NSD

128

Low-noise mode

6.2

Low-power mode

10

V/V

nV/√Hz

Maxim Integrated | 4

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Electrical Characteristics (continued)

(VAVDD = 3.6V, VAVSS = 0V, VDVDD = 2.0V to 3.6V, VREFP - VREFN = VAVDD, DATA RATE = 1ksps, PGA low-noise mode, singlecycle conversion mode (SCYCLE = 1). TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1))

PARAMETER

SYMBOL

Gain Error, Not

Calibrated

GERR

CONDITIONS

MIN

0.75

Gain = 2

1.2

Gain = 4

2

Gain = 8

3

Gain = 16

4.5

Gain = 32

6

Gain = 64

5.5

Gain = 128

Output Voltage Range

TYP

Gain = 1

UNITS

%

2

VAVSS

+ 0.3

VOUTRNG

MAX

VAVDD

- 0.3

V

MUX

Channel-to-Channel

Isolation

ISOCH-CH

DC

140

Voltage between GPO_ and GPOGND <

200mV, GPOGND connected to AVSS

3.5

Per output

30

dB

GENERAL-PURPOSE OUTPUTS

Resistance (On)

RON

Maximum Current (On)

IMAX

Total from all outputs into GPOGND

bump (Note 4)

90

ILEAK1

Current into the GPOGND pin with one

individual GPO_ pin connected to 3V

0.4

ILEAK6

Current into the GPOGND pin with all

GPO_ pins connected to 3V

13

Leakage Current (Off)

10

Ω

mA

nA

100

AUTOSCAN TIMER

Timer Resolution

ASTRES

Accuracy

ASTACC

4

ms

Over voltage and temperature (Note 4)

5

10

TPUPSLP

SLEEP state (full power-down) to LDO

wake-up, VAVDD = 2.7V, VDVDD = 2.0V,

CAPREG = 220nF

23

45

TPUPSBY

STANDBY state (analog blocks powered

down, LDO on) to Active

4

%

POWER-UP DELAYS (Note 4)

Power-Up Time

RSTB Fall to RDYB ‘1’

tR2

μs

RDYB transition from '0' to '1' on falling

edge of RSTB (Note 4)

8

300

ns

ANALOG INPUTS/REFERENCE INPUTS

Common-Mode Input

Voltage Range, VCM =

(VAIN_P + VAIN_N)/2

CMIRNG

Direct (PGA bypassed)

VAVSS

VAVDD

V

Common-Mode Input

Voltage Range, VCM =

(VAIN_P + VAIN_N)/3

CMIRNG

PGA

VAVSS

+ 0.3

VAVDD

-1.3

V

www.maximintegrated.com

Maxim Integrated | 5

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Electrical Characteristics (continued)

(VAVDD = 3.6V, VAVSS = 0V, VDVDD = 2.0V to 3.6V, VREFP - VREFN = VAVDD, DATA RATE = 1ksps, PGA low-noise mode, singlecycle conversion mode (SCYCLE = 1). TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1))

PARAMETER

Absolute Input Voltage

Range

DC Input Leakage

SYMBOL

CONDITIONS

MIN

TYP

MAX

VABSRNG

Direct (PGA bypassed)

VAVSS

VAVDD

VABSRNG

PGA

VAVSS

+ 0.3

VAVDD

-1.3

V

SLEEP state enabled

±0.1

nA

GDIFF

Direct (PGA bypassed)

±11.6

μA/V

Differential Input Current

IDIFF

PGA enabled

±1.0

nA

Common-Mode Input

Conductance

GCM

Direct (PGA bypassed)

±1.0

μA/V

Common-Mode Input

Current

ICM

PGA enabled

±10

nA

Reference Differential

Input Resistance

RREF

Active state

26

kΩ

Reference Differential

Input Current

IREF_PD

STANDBY and SLEEP state

±1

nA

Direct (PGA bypassed)

2.5

PGA

0.25

Differential Input

Conductance

Input Capacitance

IINLEAK

UNITS

CIN

CPGAIN

Voltage Range (AINP AINN)

VIN(DIFF)

AINP, AINN Sampling

Rate

fS

REFP, REFN Voltage

Range

VRABSRNG

REFP – REFN

Differential Voltage

Range

Unipolar

Bipolar

pF

0

VREF

-VREF

+VREF

4.096

(Note 5)

VREF

1.5

REFP, REFN Sampling

Rate

V

MHz

VAVDD

V

VAVDD

V

4.096

MHz

Current

1.1

μA

Initial Tolerance

±10

%

Drift

0.3

%/°C

Bandwidth (-3dB)

0.203 x

DATA

RATE

Hz

Settling Time (Latency)

5/DATA

RATE

s

SENSOR FAULT DETECT CURRENTS

DIGITAL SINC FILTER RESPONSE

LOGIC INPUTS

VIMAX_I2C

Input Current

www.maximintegrated.com

Maximum input voltage of SDA and SCL

IDIGILEAK

Leakage current

VDVDD

V

±1

μA

Maxim Integrated | 6

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Electrical Characteristics (continued)

(VAVDD = 3.6V, VAVSS = 0V, VDVDD = 2.0V to 3.6V, VREFP - VREFN = VAVDD, DATA RATE = 1ksps, PGA low-noise mode, singlecycle conversion mode (SCYCLE = 1). TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1))

PARAMETER

SYMBOL

Input Low Voltage

VIL

Input High Voltage

VIH

Input Hysteresis

CONDITIONS

MIN

TYP

MAX

UNITS

0.3 x

VDVDD

V

0.7 x

VDVDD

VHYS

V

200

mV

LOGIC OUTPUTS

VOMAX_I2C

Maximum output voltage of SDA

Output Low Level

VOL

IOL = 1mA

Output High Level

(RDYB, DOUT)

VOH

IOH = 1mA

Floating State Leakage

Current

Floating State Output

Capacitance

VDVDD

V

0.4

V

0.9 x

VDVDD

V

IDIGOLEAK

±10

CDIGO

9

μA

pF

POWER REQUIREMENTS

Negative Analog Supply

Voltage

VAVSS

0

Positive Analog Supply

Voltage

VAVDD

2.7

3.6

CAPREG is not being driven by external

supply

2.0

3.6

DVDD and CAPREG bumps connected

together on the circuit board

1.7

2.0

Voltage developed internally from DVDD

using a subregulator; When CAPREG pin

is driven externally, ensure that it is

connected directly to DVDD pin.

1.7

2.0

I/O Supply Voltage

CAPREG Supply

Voltage

Analog Supply Current

VDVDD

VCAPREG

IAVDD

V

V

Direct

2.2

3

PGA low-power mode

3.5

4.6

PGA low-noise mode

4.2

5.65

VDVDD = 2.0V, LDO enabled

0.65

1.1

VDVDD = VCAPREG = 2.0V, LDO disabled

0.58

1

DVDD Operating

Current

IDVDD(CNV)

AVDD Sleep Current

IAVDD(SLP)

VAVDD = 3.466V, VAVSS = 0V, VDVDD =

2.0V

DVDD Sleep Current

IDVDD(SLP)

VDVDD = 2.0V

0.3

AVDD Standby Current

IAVDD(SBY)

VAVDD = 3.465V, VAVSS = 0V, VDVDD =

2.0V

1.5

DVDD Standby Current

IDVDD(SBY)

VDVDD = 2.0V, LDO enabled

50

VDVDD = VCAPREG = 2.0V, LDO disabled

2.5

www.maximintegrated.com

V

V

mA

mA

μA

1

μA

μA

175

μA

Maxim Integrated | 7

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Electrical Characteristics (continued)

(VAVDD = 3.6V, VAVSS = 0V, VDVDD = 2.0V to 3.6V, VREFP - VREFN = VAVDD, DATA RATE = 1ksps, PGA low-noise mode, singlecycle conversion mode (SCYCLE = 1). TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1))

PARAMETER

SYMBOL

UVLO Threshold Lowto-High

VLH

UVLO Threshold Highto-Low

VHL

UVLO Hysteresis

UVLO Delay Low-toHigh or High-to-Low

UVLO Glitch

Suppression

VHYS

TDEL

TP

MIN

TYP

MAX

AVDD, DVDD supply undervoltage

lockout

CONDITIONS

0.8

1.2

1.65

CAPREG supply undervoltage lockout

0.7

1.0

1.35

AVDD, DVDD supply undervoltage

lockout

0.6

1.1

1.5

CAPREG supply undervoltage lockout

0.5

0.95

1.3

AVDD, DVDD supply undervoltage

lockout

4

CAPREG supply undervoltage lockout

5

AVDD, DVDD supply undervoltage

lockout

10

CAPREG supply undervoltage lockout

3.5

AVDD, DVDD supply undervoltage

lockout

10

CAPREG supply undervoltage lockout

10

Note 4 applies to minimum value

0.1

UNITS

V

V

%

μs

ns

Serial Clock Frequency

fSCL

1

MHz

Bus Free Time Between

STOP and START

Condition

tBUF

0.5

μs

Hold Time (Repeated)

START Condition (After

This Period, First Clock

Pulse Is Generated)

tHD;STA

0.26

μs

SCL Pulse-Width Low

tLOW

0.5

μs

SCL Pulse-Width High

tHIGH

0.26

μs

Setup Time for

Repeated START

Condition

tSU;STA

0.26

μs

Data Hold Time

tHD;DAT

0

μs

Data Setup Time

tSU;DAT

50

ns

SDA and SCL Receiving

Rise Time

tr

(Note 4)

SDA and SCL Receiving

Fall Time

tf

(Note 4)

SDA Transmitting Fall

Time

Setup Time for STOP

Condition

Bus Capacitance

Allowed

www.maximintegrated.com

120

ns

20 x

VDVDD/

5.5

120

ns

tf

20 x

VDVDD/

5.5

120

ns

tSU;STO

0.26

Cb

(Note 4)

μs

550

pF

Maxim Integrated | 8

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Electrical Characteristics (continued)

(VAVDD = 3.6V, VAVSS = 0V, VDVDD = 2.0V to 3.6V, VREFP - VREFN = VAVDD, DATA RATE = 1ksps, PGA low-noise mode, singlecycle conversion mode (SCYCLE = 1). TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1))

PARAMETER

SYMBOL

Pulse Width of

Suppressed Spike

CONDITIONS

MIN

tSP

TYP

MAX

UNITS

50

ns

Note 1: Limits are 100% tested at TA = +25°C, unless otherwise noted. Limits over the operating temperature range and relevant

supply voltage range are guaranteed by design and characterization.

Note 2: Full-scale error includes errors from gain and offset or zero-scale error.

Note 3: ppmFSR is parts per million of full-scale range.

Note 4: These specifications are guaranteed by design, characterization, or I2C protocol.

Note 5: Reference common mode (VREFP + VREFN)/2 ≤ (VAVDD + VAVSS)/2 + 0.1V.

SDA

tf

tLOW

tSU;DAT

tr

tf

tHD;STA

tSP

tBUF

tr

SCL

tSU;STA

tHD;STA

S

tHD;DAT

tHIGH

tSU;STO

Sr

P

S

Figure 1. I2C Timing Diagram

www.maximintegrated.com

Maxim Integrated | 9

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Typical Operating Characteristics

(VAVDD = +3.6V, VAVSS = 0V, VDVDD = +2.0V, VREFP - VREFN = VAVDD; TA = TMIN to TMAX, LDO enabled, PGA enabled, unless

otherwise noted. Typical values are at TA = +25°C.)

www.maximintegrated.com

Maxim Integrated | 10

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Typical Operating Characteristics (continued)

(VAVDD = +3.6V, VAVSS = 0V, VDVDD = +2.0V, VREFP - VREFN = VAVDD; TA = TMIN to TMAX, LDO enabled, PGA enabled, unless

otherwise noted. Typical values are at TA = +25°C.)

www.maximintegrated.com

Maxim Integrated | 11

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Typical Operating Characteristics (continued)

(VAVDD = +3.6V, VAVSS = 0V, VDVDD = +2.0V, VREFP - VREFN = VAVDD; TA = TMIN to TMAX, LDO enabled, PGA enabled, unless

otherwise noted. Typical values are at TA = +25°C.)

www.maximintegrated.com

Maxim Integrated | 12

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Bump Configuration

TOP VIEW

(BUMP SIDE DOWN)

MAX11261

1

2

3

4

5

6

A

AIN0P

AIN1P

AIN2P

AIN3P

AIN4P

AIN5P

B

AIN0N

AIN1N

AIN2N

AIN3N

AIN4N

AIN5N

C

AVSS

REFP

REFN

CAPN

CAPP

AVSS

D

AVDD

GPO0

SYNC

GPO4

RSTB

GPO

GND

E

RDYB_

INTB

SDA

ADR0

GPO1

GPO2

GPO3

F

SCL

GPO5

ADR1

DGND

CAP

REG

DVDD

+

WLP 6 x 6

0.4mm PITCH

0.5mm HEIGHT

Bump Descriptions

PIN

NAME

A1

AIN0P

Positive Analog Input 0. A 1nF C0G capacitor should be added between

differential input pin pairs.

IN/Analog

A2

AIN1P

Positive Analog Input 1. A 1nF C0G capacitor should be added between

differential input pin pairs

IN/Analog

A3

AIN2P

Positive Analog Input 2. A 1nF C0G capacitor should be added between

differential input pin pairs.

IN/Analog

A4

AIN3P

Positive Analog Input 3. A 1nF C0G capacitor should be added between

differential input pin pairs.

IN/Analog

A5

AIN4P

Positive Analog Input 4. A 1nF C0G capacitor should be added between

differential input pin pairs.

IN/Analog

A6

AIN5P

Positive Analog Input 5. A 1nF C0G capacitor should be added between

differential input pin pairs.

IN/Analog

B1

AIN0N

Negative Analog Input 0

IN/Analog

B2

AIN1N

Negative Analog Input 1

IN/Analog

B3

AIN2N

Negative Analog Input 2

IN/Analog

B4

AIN3N

Negative Analog Input 3

IN/Analog

B5

AIN4N

Negative Analog Input 4

IN/Analog

B6

AIN5N

Negative Analog Input 5

IN/Analog

www.maximintegrated.com

FUNCTION

TYPE

Maxim Integrated | 13

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Bump Descriptions (continued)

PIN

NAME

FUNCTION

TYPE

C1, C6

AVSS

Analog Ground

C2

REFP

Positive Reference Input

IN/Analog

C3

REFN

Negative Reference Input

IN/Analog

C4

CAPN

PGA Filter Input. Connect 1nF C0G capacitor between CAPP and CAPN.

IN/Analog

C5

CAPP

PGA Filter Input. Connect 1nF C0G capacitor between CAPP and CAPN.

IN/Analog

D1

AVDD

Positive Analog Supply

D2

GPO0

Analog Switch Normally Open Terminal/General-Purpose Output 0. Register

controlled, close position connects GPO0 to GPOGND. Current sink only.

D3

SYNC

Synchronization Pin for Multiple Devices. At power-up, the device defaults to a

master (CTRL3:SYNC = 1) and the SYNC pin output is in high impedance state

(CTRL3:SYNCZ = 1). When the device is configured as a master and the register

CTRL3:SYNCZ is set to 0, the SYNC pin is changed to an active-low, open-drain

output pin. Set CTRL:SYNC to 0 puts the device in slave mode and the SYNC pin

is an input. An external pullup resistor is required if the SYNC function is used.

D4

GPO4

Analog Switch Normally Open Terminal/General-Purpose Output 4. Register

controlled, close position connects GPO4 to GPOGND. Current sink only.

D5

RSTB

Active-Low Power-On-Reset Input

D6

GPOGND

AGND

PWR

OUT/Analog

IN/OUT/

Digital

OUT/Analog

IN/Digital

Analog Switch/General-Purpose Output, GND Terminal

OUT/Analog

Active-Low Open-Drain Output. A pullup resistor to DVDD is required. The typical

resistor value is 10kΩ.

E1

RDYB_INTB

In sequencer modes 1, 2, and 3: RDYB_INTB goes low when a new conversion

result is available in the FIFO. When the FIFO entries are completely read out,

RDYB_INTB returns high if no FIFO usage interrupt is asserted. The RDYB_INTB

also goes low when there is at least one FIFO usage interrupt.

OUT/Digital

In sequencer mode 4: RDYB_INTB indicates the input comparison result and

FIFO usage interrupt.

I2C Serial Data

IN/OUT/I2C

E2

SDA

E3

ADR0

I2C Address Select Line 0

E4

GPO1

Analog Switch Normally Open Terminal/General-Purpose Output 1. Register

controlled, close position connects GPO1 to GPOGND. Current sink only.

OUT/Analog

E5

GPO2

Analog Switch Normally Open Terminal/General-Purpose Output 2. Register

controlled, close position connects GPO2 to GPOGND. Current sink only.

OUT/Analog

E6

GPO3

Analog Switch Normally Open Terminal/General-Purpose Output 3. Register

controlled, close position connects GPO3 to GPOGND. Current sink only.

OUT/Analog

F1

SCL

I2C Serial Clock Input

IN/Digital/I2C

F2

GPO5

Analog Switch Normally Open Terminal/General-Purpose Output 5. Register

controlled, close position connects GPO5 to GPOGND. Current sink only.

F3

ADR1

I2C Address Select Line 1

F4

DGND

Digital Ground

F5

CAPREG

F6

DVDD

www.maximintegrated.com

IN/Digital

OUT/Digital

INDigital

DGND

1.8V Subregulator Output. Connects to DVDD when driven externally by a 1.8V

supply. Connect a 220nF to DGND.

PWR

Digital Power Supply

PWR

Maxim Integrated | 14

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Functional Diagrams

AVDD

DVDD

AVDD

AVSS

DGND

CLOCK

GENERATOR

1µA

TIMING

AIN0P

SYNC

AIN0N

ADR0

64-ENTRY

FIFO

ADR1

SCL

MUX

DELTA-SIGMA

ADC

PGA

DIGITAL

FILTER

SERIAL

INTERFACE

SDA

RDYB_INTB

RSTB

HIGH-PASS

FILTER, TRIP

COMPARATOR

AIN5P

AIN5N

1.8V

REGULATOR

GPOGND

1µA

AVSS

CAPP CAPN

www.maximintegrated.com

REFP

REFN

CAPREG

GPO0

GPO5

Maxim Integrated | 15

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Detailed Description

The MAX11261 is a 24-bit, delta-sigma ADC that achieves exceptional performance consuming minimal power. Sample

rates up to 16ksps support precision DC measurements. The built-in sequencer supports scanning of selected analog

channels, auto wake-up, programmable conversion delay, and math operations to automate sensor monitoring.

The fourth-order, delta-sigma modulator is unconditionally stable and measures the six differential input voltages. To

prevent overdriving, the modulator is monitored for overrange conditions and is reported in the status register. The digital

filter is a variable decimation-rate SINC filter with overflow monitoring reported in the status register.

The programmable gain differential amplifier (PGA) is low noise and is programmable from 1 to 128. The PGA buffers

the modulator and provides a high-impedance input to the analog channels.

The device stores the conversion results in a 64-entry FIFO. The FIFO interrupts wake up the host processor less

frequently to reduce the system power consumption. The device also features an autonomous scan mode to monitor the

input activity. The device only interrupts the host when the input is out of a configured range.

System Clock

The MAX11261 incorporates a highly stable internal oscillator that provides the system clock. The system clock is

trimmed to 8.192MHz, providing digital and analog timing.

Voltage Reference Inputs

The MAX11261 provides differential inputs REFP and REFN for an external reference voltage. Connect the external

reference directly across the REFP and REFN bumps to obtain the differential reference voltage. The VREFP voltage

should always be greater than the VREFN voltage, and the common-mode voltage range is between 0.75V and VAVDD 0.75V.

Analog Inputs

The MAX11261 measures six pairs of differential analog inputs (AIN_P, AIN_N) in direct connection or buffered through

the PGA. See the CTRL2: Control Register 2 (Read/Write) table for programming and enabling the PGA or direct connect

mode. The default configuration is direct connect with the PGA powered down.

Bypass/Direct Connect

The MAX11261 offers the option to bypass the PGA and route the analog inputs directly to the modulator. This option

lowers the power of the device since the PGA is powered down.

Programmable Gain Amplifier (PGA)

The integrated PGA provides gain settings from 1x to 128x (Figure 2). Direct connection is available to bypass the PGA

and directly connect to the modulator. The PGA’s absolute input voltage range is CMIRNG and the PGA output voltage

range is VOUTRNG, as specified in the Electrical Characteristics.

www.maximintegrated.com

Maxim Integrated | 16

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

AINP

R3

A1

CAPP

R1

CCAPP/N

(C0G CAPACITOR)

R2

R1

R3

CAPN

A2

AINN

Figure 2. Simplified Equivalent Diagram of the PGA

ANALOG INPUTS

PGA OUTPUT

VAVDD

VAVDD - 0.3V

OUTPUT VOLTAGE RANGE = GAIN

x INPUT VOLTAGE RANGE

VAVDD - 1.3V

COMMON-MODE

INPUT VOLTAGE

INPUT VOLTAGE RANGE

VAVSS + 0.4V

≤ VREF

VAVSS + 0.3V

VAVSS

Figure 3. Analog Input Voltage Range Compared to PGA Output Range

Note that linearity and performance degrade when the specified input common-mode voltage of the PGA is exceeded.

The input common-mode range and output common-mode range are shown in Figure 3. The following equations describe

the relationship between the analog inputs and PGA output.

AINP = Positive input to the PGA

AINN = Negative input to the PGA

CAPP = Positive output of PGA

CAPN = Negative output of PGA

VCM = Input common mode

GAIN = PGA gain

VREF = ADC reference input voltage

www.maximintegrated.com

Maxim Integrated | 17

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

VIN = VAINP - VAINN

Note: Input voltage range is limited by the reference voltage, as described by VIN ≤ ±VREF/GAIN:

VCM =

(VANP + VAINN)

2

VCAPP = VCM + GAIN x (VAINP - VCM)

VCAPN = VCM - GAIN x (VCM - VAINN)

PGA High Current

When VAVDD voltage is above 2.9V and PGA is enabled, high IAVDD current could be observed on the MAX11261 if the

PGA outputs are driven out of normal operating range and then rapidly driven back within the range during continuous

conversion. The current can be as high as 30mA, depending on the AVDD supply voltage and PGA output voltage.

To trigger the PGA high-current state, drive the PGA output from normal low-side compliance range (> VAVSS + 0.3V) to

less than (VAVSS + 40mV), and then drive back into compliance range (> VAVSS + 0.3V) with a slew rate greater than

0.7V/μs while the device is performing continuous conversion.

The high-current state can also be triggered when interrupting a self-calibration in progress by starting a new conversion

command when the PGA is enabled, which internally creates the trigger condition.

The PGA high-current state cannot be triggered with VAVDD supply voltage below 2.9V.

When PGA high-current state is triggered, IAVDD current could be 4.5 times as high as the normal IAVDD current.

Exit Condition

PGA high-current state can always be exited by changing the MAX11261 to STANDBY or SLEEP state.

It will be automatically recovered when the MAX11261 is configured in mode 1 single-cycle conversion mode, mode 2,

mode 3, or mode 4 if AutoScan Delay > 0. In these modes, the device automatically goes to STANDBY or SLEEP mode

after the conversion.

When PGA high current state is triggered in mode 1 continuous conversion mode or mode 4 AutoScan Delay = 0, it can

be recovered by issuing firmware command to cycle STANDBY or SLEEP state. To force the MAX11261 into STANDBY

or SLEEP state, either issue a power-down command or write to one of the CTRL registers.

Input Voltage Range

The ADC input range is programmable for bipolar (-VREF to +VREF) or unipolar (0 to VREF) ranges. The U/B bit in the

CTRL1 register configures the MAX11261 for unipolar or bipolar transfer functions.

Data Rates

Table 1 lists the available data rates for the MAX11261, RATE[3:0] setting of the conversion command (see the Modes

and Registers section). The single-cycle mode has an overhead of 48 digital master clocks that is approximately 5.86μs

from a typical digital master clock frequency of 8.192MHz. The single-cycle effective column contains the data rate values

including the 48 clock startup delays. The 48 clocks are to stabilize the modulator startup. In continuous conversion

mode, the output data rate is five times the single-cycle rate up to a maximum of 16ksps. During continuous conversions,

the output sample data requires five 24-bit cycles to settle to a valid conversion from an input step, PGA gain changes,

or a change of input channel through the multiplexer.

If self-calibration operation is used, 48 additional master clocks are required to process the data per conversion. Likewise,

system calibration takes an additional 48 master clocks to complete.

If both self and system-calibration are used, it takes an additional 80 master clocks to complete. If self and/or system

calibration are used, the effective data rate will be reduced by these additional clock cycles per conversion.

Table 1. Available Programmable Data Rates

DATA RATE (sps)

www.maximintegrated.com

Maxim Integrated | 18

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Table 1. Available Programmable Data Rates (continued)

RATE[3:0]

CONTINUOUS

SINGLE

CYCLE

CONVERSION

ONLY

CONVERSION

PLUS SELFCALIBRATION*

CONVERSION PLUS SELF-CALIBRATION PLUS

SYSTEM CALIBRATION*

0000

1.9

50

50.01

49.99

49.98

0001

3.9

62.5

62.51

62.48

62.47

0010

7.8

100

99.98

99.92

99.88

0011

15.6

125

124.95

124.86

124.80

0100

31.2

200

199.80

199.57

199.41

0101

62.5

250

249.66

249.29

249.05

0110

125

400

398.98

398.05

397.44

0111

250

500

498.34

496.89

495.93

1000

500

800

796.11

792.41

789.97

1001

1000

1000

991.86

986.13

982.35

1010

2000

1600

1578.72

1564.26

1554.77

1011

4000

2000

1974.16

1951.60

1936.84

1100

8000

3200

3114.26

3058.48

3022.39

1101

16000**

4000

3895.78

3808.89

3753.08

1110

Not available

6400

6135.27

5922.49

5788.64

1111

Not available

12800

11776.90

11017.10

10562.79

*The effective data rate is lower when the calibration is enabled due to additional MAC (multiply/accumulate) operations

required after the conversion is complete to perform the calibration adjustment.

**Only supported in Fast-Mode Plus.

Noise Performance

The MAX11261 provides exceptional noise performance. SNR is dependent on data rate, PGA gain, and power mode.

Bandwidth is reduced at low data rates; both noise and SNR are improved proportionally. Table 2 and Table 3 summarize

the noise performance for both single cycle and continuous operation versus data rate, PGA gain, and power mode.

Table 2. Noise vs. PGA Mode and Gain (Single-Cycle Conversion)

SINGLE-CYCLE CONVERSION MODE

INPUT-REFERRED NOISE VOLTAGE (mVRMS) vs. PGA GAIN SETTING

1

2

4

8

16

32

64

128

DATA RATE

(sps)

LP

LN

LP

LN

LP

LN

LP

LN

LP

LN

LP

LN

LP

LN

LP

LN

50

0.81

0.58

0.38

0.27

0.18

0.13

0.10

0.07

0.09

0.07

0.08

0.06

0.08

0.06

0.08

0.06

62.5

0.88

0.63

0.48

0.34

0.21

0.15

0.12

0.09

0.09

0.07

0.08

0.06

0.08

0.05

0.08

0.05

100

1.18

0.84

0.61

0.44

0.30

0.21

0.17

0.12

0.12

0.08

0.09

0.07

0.09

0.07

0.10

0.07

125

1.24

0.89

0.59

0.42

0.31

0.22

0.18

0.13

0.12

0.08

0.10

0.07

0.10

0.07

0.10

0.07

200

1.38

0.99

0.68

0.49

0.35

0.25

0.21

0.15

0.15

0.10

0.12

0.08

0.11

0.08

0.11

0.08

250

1.38

0.99

0.72

0.52

0.39

0.28

0.23

0.16

0.16

0.11

0.13

0.09

0.12

0.09

0.12

0.09

400

1.63

1.16

0.85

0.61

0.45

0.32

0.27

0.19

0.19

0.14

0.16

0.12

0.15

0.11

0.16

0.11

500

1.79

1.28

0.93

0.66

0.48

0.34

0.29

0.21

0.21

0.15

0.18

0.13

0.17

0.12

0.18

0.13

800

2.12

1.51

1.10

0.79

0.61

0.43

0.36

0.26

0.27

0.20

0.24

0.17

0.23

0.16

0.23

0.16

1,000

2.38

1.70

1.25

0.89

0.69

0.49

0.41

0.29

0.31

0.22

0.27

0.19

0.26

0.18

0.26

0.19

www.maximintegrated.com

Maxim Integrated | 19

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Table 2. Noise vs. PGA Mode and Gain (Single-Cycle Conversion) (continued)

1,600

3.21

2.29

1.67

1.19

0.89

0.64

0.56

0.40

0.41

0.29

0.36

0.26

0.35

0.25

0.35

0.25

2,000

3.76

2.69

1.95

1.39

1.04

0.74

0.65

0.47

0.48

0.34

0.43

0.30

0.41

0.29

0.42

0.30

3,200

4.41

3.15

2.28

1.63

1.25

0.89

0.78

0.55

0.58

0.41

0.51

0.36

0.49

0.35

0.49

0.35

4,000

5.18

3.70

2.68

1.91

1.48

1.06

0.91

0.65

0.69

0.49

0.60

0.43

0.58

0.41

0.59

0.42

6,400

7.34

5.24

3.83

2.73

2.08

1.48

1.29

0.92

0.98

0.70

0.86

0.61

0.81

0.58

0.83

0.59

12,800

10.84

7.74

5.59

3.99

3.01

2.15

1.85

1.32

1.37

0.98

1.23

0.88

1.17

0.83

1.16

0.83

LP = low power, LN = low noise

Table 3. Noise vs. PGA Mode and Gain (Continuous Conversion)

CONTINUOUS CONVERSION MODE

INPUT-REFERRED NOISE VOLTAGE (mVRMS) vs. PGA GAIN SETTING

1

2

4

8

16

32

64

128

DATA RATE

(sps)

LP

LN

LP

LN

LP

LN

LP

LN

LP

LN

LP

LN

LP

LN

LP

LN

15.6

0.45

0.32

0.20

0.14

0.11

0.08

0.06

0.04

0.04

0.03

0.03

0.02

0.03

0.02

0.03

0.02

31.2

0.58

0.41

0.26

0.18

0.13

0.10

0.08

0.06

0.05

0.04

0.04

0.03

0.04

0.03

0.04

0.03

62.5

0.68

0.48

0.34

0.25

0.18

0.13

0.10

0.07

0.07

0.05

0.06

0.04

0.06

0.04

0.06

0.04

125

0.86

0.61

0.44

0.32

0.23

0.16

0.14

0.10

0.10

0.07

0.08

0.06

0.08

0.06

0.08

0.06

250

1.14

0.82

0.56

0.40

0.30

0.22

0.18

0.13

0.14

0.10

0.11

0.08

0.11

0.08

0.11

0.08

500

1.47

1.05

0.76

0.54

0.41

0.29

0.25

0.18

0.19

0.13

0.16

0.11

0.16

0.11

0.16

0.11

1,000

1.99

1.42

1.03

0.73

0.56

0.40

0.35

0.25

0.26

0.19

0.23

0.16

0.21

0.15

0.22

0.16

2,000

2.73

1.95

1.40

1.00

0.76

0.54

0.47

0.34

0.36

0.26

0.31

0.22

0.30

0.21

0.30

0.21

4,000

3.68

2.63

1.86

1.33

1.03

0.73

0.64

0.45

0.49

0.35

0.42

0.30

0.40

0.28

0.41

0.29

8,000

4.57

3.26

2.36

1.69

1.30

0.93

0.81

0.58

0.61

0.43

0.53

0.38

0.52

0.37

0.52

0.37

16,000

5.22

3.73

2.66

1.90

1.48

1.06

0.93

0.67

0.68

0.49

0.61

0.44

0.58

0.41

0.60

0.43

LP = low power, LN = low noise

I2C Protocol

The I2C-compatible serial interface consists of the standard I2C signals: SCL and SDA. The SCL and the SDA pins

are bidirectional lines, connected to a positive supply voltage through a current source or a pullup resistor. The data is

clocked into the MAX11261 from the SDA pin on the rising edge of SCL. Data is clocked out of the MAX11261 on the

SDA pin on the falling edge of SCL. The SCL/SDA have an open-drain pad for wired-AND connection on the bus. Fast

Mode Plus protocol is supported at maximum SCL clock rate of 1MHz. Each device on the I2C bus is recognized by

a unique device address and can operate as a transmitter and a receiver. The interface is backward compatible with

Standard mode and Fast mode.

Due to the variety of different devices (bipolar, CMOS, nMOS) that can be connected to the I2C bus, the input reference

levels are set as 30% and 70% of VDVDD. The data on the SDA line must be stable during the high period of SCL. The

HIGH or LOW state of SDA can only change when SCL is LOW for a normal byte transfer except for START and STOP

conditions.

All transactions begin with a START (S) and are terminated by a STOP (P). A high-to-low transaction on the SDA line

while SCL is high defines a START condition. A low-to-high transition on the SDA line while SCL is high defines a

STOP condition. The START and STOP are always generated by the I2C master. Every byte on the SDA line must be

8 bits long. The number of bytes that can be transmitted is unrestricted. Each byte must be followed by an acknowledge

(ACK). Data is transferred with MSB first. The MAX11261 always sends out an ACK in response to the master’s request

for reading or writing data. If the MAX11261 receives a not acknowledge (NACK) from the master it will reset the I2C

interface and wait for another START condition.

www.maximintegrated.com

Maxim Integrated | 20

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

SCL (Serial Clock)

The SCL pin synchronizes data communication between the host device and the MAX11261. Data is latched into the

MAX11261 on the rising edge of SCL and data is shifted out of the MAX11261 on the falling edge of SCL. The MAX11261

does not support SCL clock stretching.

SDA (Serial Data Input/Output)

The SDA line is considered an input when the master is transmitting the data to the MAX11261. The SDA line will be

used as an output when the MAX11261 has data to be sent onto the I2C bus during a register read by the host master.

The slave in the MAX11261 implements mandatory requirements as specified in the I2C standard, which are detections

of START and STOP conditions and support for ACK/NACK. This slave only supports 7-bit addressing and does not

support general call address.

RDYB_INTB (Data Ready and Interrupt)

In sequencer modes 1, 2, and 3, RDYB_INTB indicates the ADC conversion status and the availability of the conversion

result. When RDYB_INTB is low, a conversion result is available. When RDYB_INTB is high, a conversion is in progress

and the data for the current conversion is not available. RDYB_INTB is driven high after a complete FIFO read.

RDYB_INTB resets to high four master clock cycles prior to the next FIFO register update.

If data was read, then RDYB_INTB transitions from high to low at the output data rate. If the previous data was not

read, the RDYB_INTB transitions from low to high for four master clock cycles and then transitions from high to low. In

continuous mode, RDYB_INTB remains high for the first four conversion results and on the 5th result, RDYB_INTB goes

low.

For sequencer mode 2 and sequencer mode 3 the RDYB_INTB behavior for a multichannel conversion can be controlled

by the SEQ:RDYBEN bit. The default value of SEQ:RDYBEN is ‘0’. When set to ‘0’, RDYB_INTB for a multichannel

conversion behaves the same as a single-channel operation. The RDYB_INTB toggles high to low after each channel is

ready to update its corresponding data register. After the channel data is read, the RDYB_ INTB will reset back to ‘1’. If

the channel data is not read and the next channel is ready to update its data, the RDYB_INTB will toggle low to high four

cycles before the data update (similar to a single-channel case), and then toggle high to low indicating the new channel’s

conversion data is available. If ‘N’ channels are enabled, RDYB_INTB will toggle high to low ‘N’ times. If SEQ:RDYBEN

is set to ‘1’, the RDYB_INTB event for each channel is suppressed. The RDYB_INTB toggles high to low when the last

channel is ready to update its corresponding data register and a single high-to-low transition happens.

In sequencer modes 1, 2, and 3, RDYB_INTB is also ORing the FIFO usage interrupt outputs.

RDYB_INTB is used as an interrupt in sequencer mode 4, so it has no significance in terms of indicating data availability

when operating in sequencer mode 4.

The STAT:SRDY[5:0] bits get set to ‘1’ when their corresponding channel finishes converting irrespective of the RDYBEN

setting for sequencer modes 2, 3, and 4. The conversion status is available by reading STAT:MSTAT bit. This stays high

as long as the modulator is converting.

www.maximintegrated.com

Maxim Integrated | 21

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

CONVERT COMMANDS

SCL/SDA

N x t CNV

SCYCLE = '1',

CONTSC = '0'

N x t CNV

DATA NOT RETRIEVED

RDYB

t CNV

SCYCLE = '1',

CONTSC = '1'

DATA

RETRIEVED

RDYB

tINIT

tCNV +tINIT

SCYCLE = 0,

CONTSC = x

RATE[3:0] 13

RDYB

5 tCNV

SCYCLE = '0',

CONTSC = 'x'

RDYB

tCNV

RATE[3:0] • 13

NOTE

OTE: RATE[3:0] 13, tINIT = 3µs.

Figure 4. RDYB

I2C Sequence

The master needs to send out the first byte with a valid device address. The last bit of the first byte is a R/W bit and

the master needs to send a '0' in this bit. The device will ignore a '1' sent in this bit. This is followed by a COMMAND

byte for the MAX11261 as described in the command structure. The MAX11261 then responds to the command request

depending on the MODE bit in the command.

Writing a Command to the MAX11261 for Conversion/Calibration/Power-Down

1. I2C START.

2. I2C WRITE.

a. Send Device Address with a '0' in bit 8 indicating that the master will send a command byte followed by the device

address. (8’b011xxxx_0)

b. Check ACK.

c. Send a command byte to convert/power down/calibrate. (8’b10_01_xxxx)

d. Check ACK.

3. I2C STOP.

Sequence to Execute I2C Write Operation

1. I2C START.

2. I2C WRITE.

a. Send Device Address with a '0' in bit 8 indicating the master will send a command byte followed by the device

address. (8’b011xxxx_0)

b. Check ACK.

c. Send a command byte to the Write registers. (8’b11_reg_addr[4:0]_0)

d. Check ACK.

www.maximintegrated.com

Maxim Integrated | 22

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

e. Send the 8-bit register data MSB first.

f. Check ACK.

g. Check ACK.

3. I2C STOP.

Sequence to Execute I2C Read Operation

1. I2C START.

2. I2C WRITE.

a. Send Device Address with a '0' in bit 8 indicating that the master will send a command byte followed by the device

address. (8’b011xxxx_0)

b. Check ACK.

c. Send a command byte to the Read registers (8’b11_reg_addr[4:0]_1)

d. Check ACK.

3. I2C Repeat START.

4. I2C WRITE.

a. Send Device Address with a '1' in bit 8 indicating that the master will read the register data out.

b. Check ACK.

5. I2C READa. Receive 8 bits of data.

a. Send ACK.

b. Receive 8 bits of data.

c. Send NACK.

6. I2C STOP.

I2C Timing Characteristics

The I2C timing diagram is shown in Figure 1. The bus timing requirements are specified in I2C Timing Requirements

table. The data is sampled on the positive edge of SCL and launched on negative edge of SCL for ACK and DATA reads.

This gives a sufficient hold time for the master to sample the data.

I2C Device Addressing Scheme

The I2C slave has a 7-bit long device address. The device address is followed by a R/W bit which is low for a write

command and high for a read command.

The first three most significant bits of the device address are always 011. Slave address bits A[4:1] correspond by the

matrix in Table 4 to the states of the device address bumps AD0 and AD1.

The AD0 and AD1 bumps can be connected to any of the three signals: DGND, DVDD, and SDA giving three possible

addresses for each bump allowing up to nine devices connected to the bus (see Figure 5).

SCL

SDA

0

1

1

A4

A3

A2

A1

R/W

ACK

Figure 5. I2C Slave Address

www.maximintegrated.com

Maxim Integrated | 23

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Table 4. I2C Device Address Mapping (up to 9 Devices Selected on the I2C Bus Using

the Following Addressing Scheme; I2C Addresses Are Not Contiguous)

ADDRESS PINS

DEVICE ADDRESS

ADR1

ADR0

A4

A3

A2

A1

A0

DGND

DGND

A7

A6

0

0

0

0

R/W

DGND

DVDD

0

0

0

1

R/W

DGND

SDA

0

0

1

1

R/W

DVDD

DGND

0

1

0

0

R/W

DVDD

DVDD

0

1

0

1

R/W

DVDD

SDA

0

1

1

1

R/W

SDA

DGND

1

1

0

0

R/W

SDA

DVDD

1

1

0

1

R/W

SDA

SDA

1

1

1

1

R/W

0

A5

1

1

Modes and Registers

The MAX11261 interface operates in two fundamental modes, either to issue a conversion command or to access

registers. The mode of operation is selected by a command byte. Every I2C transaction to the MAX11261 starts with

a command byte. The command byte begins with the MSB (B7) set to ‘1’. The next bit (B6) determines whether a

conversion command is sent or register read/write access is requested.

Command Byte

The conversion command sets the mode of operation (conversion, calibration, or power-down), as well as the conversion

speed of the MAX11261. The register read/write command specifies the register address, as well as the direction of the

access (read or write).

Table 5. Command Byte Definition

B7 (MSB)

B6

B5

B4

B3

B2

B1

B0

Conversion Command

1

0

MODE1

MODE0

RATE3

RATE2

RATE1

RATE0

Register Read/Write

1

1

RS4

RS3

RS2

RS1

RS0

R/W

Table 6. Command Byte Decoding

BIT NAME

DESCRIPTION

The MODE bits are used to set the functional operation of the MAX11261 according to the following decoding.

MODE[1:0]

MODE1

MODE0

DESCRIPTION

0

0

Unused

0

1

Power-down performed based on the CTRL1:PD[1:0] setting.

1

0

Calibration performed based on the CTRL1:CAL[1:0] setting.

1

1

Sequencer mode. The operation is based on the configuration of the SEQ register.

RATE[3:0]

These bits determine the conversion speed of the MAX11261. The decoding is shown in Table 1.

RS[4:0]

Register address as shown in Table 9.

R/W

The R/W bit enables either a read or a write access to the address specified in RS[4:0]. If R/W is set to ‘0’, then data

is written to the register. If the bit is set to ‘1’, then data is read from the register.

www.maximintegrated.com

Maxim Integrated | 24

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Channel Sequencing

Changing SEQUENCER Modes

Mode Exit

(See Table 9.)

To exit any of the four sequencer modes, program the following sequence:

1. Issue a power-down command to exit the conversion process to STANDBY or SLEEP, as defined in

CTRL1:PD[1:0]:a. Write a conversion command byte see Table 5.) and set MODE[1:0] of the command byte to ‘01’2)

Wait for STAT:PDSTAT[1:0] = ‘01’ (SLEEP) or STAT:PDSTAT[1:0]= ‘10’ (STANDBY).

Note: In all sequencer modes, the default exit state is SLEEP with the following exceptions where the exit state is defined

by CTRL1:PD[1:0]:

● Sequencer mode 1 continuous conversion (CTRL1:SCYCLE = ‛0’)

● Sequencer mode 1 continuous single-cycle conversion (CTRL1:SCYCLE = ‛1’ and CTRL1:CONTSC = ‛1’)

Mode Change

To change sequencer modes or to update the SEQ register program the following sequence:

1. Perform Sequencer Mode Exit (see the Mode Exit section).

2. Set up the following registers: SEQ, CTRL1.

a. Set SEQ:MODE[1:0] to select the new sequencer mode.

b. Set CTRL1:PD[1:0] to STANDBY or SLEEP state to set the desired exit state if a conversion command with

MODE[1:0] set to ‘01’ is issued during the conversion.

3. Write the command byte (see Table 5).

a. Set MODE[1:0] of command byte to “11” (sequencer mode).

4. Wait for STAT:PDSTAT[1:0] = “00” to confirm conversion mode.

SEQUENCER Mode 1—Single-Channel Conversion with GPO Control and MUX Delays

This mode is used for single-channel conversions where the sequencer is disabled. [[Sequence Mode 1 Timing Diagram]]

illustrates the timing. To support high-impedance source networks, the conversion delay (SEQ:MDREN) feature must be

enabled. The states of the GPO bumps are configured using the GPO_DIR registers and can be modified anytime during

mode 1 operation. The values of the CHMAP0/CHMAP1 registers and DELAY:GPO[7:0] bits are ignored in this mode.

SEQUENCER MODE 1

DEL

CHANNEL CONVERSION

SEQ:MDREN· DELAY:MUX

SEQ:MUX[2:0]

Figure 6. Sequencer Mode 1 Timing Diagram

Programming Sequence

Mode Entry

1. Set up the following registers: SEQ, DELAY, CTRL1, GPO_DIR.

a. SEQ:MODE[1:0] = ‘00’ for sequencer mode 1.

b. SEQ:MUX[2:0] to select the channel for conversion.

c. Enable SEQ:MDREN to delay conversion start to allow for input settling. Set DELAY:MUX[7:0] to the desired

www.maximintegrated.com

Maxim Integrated | 25

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

conversion delay.

d. Set CTRL1:SCYCLE for either single-cycle (no latency) or continuous conversion.

e. If single-cycle conversion is selected, set CTRL1:CONTSC to ‘1’ if continuous single-cycle conversion is desired.

f. Set CTRL1:PD[1:0] to STANDBY or SLEEP state to set the desired exit state if a conversion command with

MODE[1:0] set to ‘01’ is issued during the conversion.

g. Set register GPO_DIR to enable or disable the desired GPO bumps.

2. Write a conversion command (see Table 5).

a. Set the data rate using bits RATE[3:0] of the command byte.

b. Set MODE[1:0] of the command byte to ‘11’ for sequencer mode.

3. Monitor RDYB_INTB for availability of conversion results in the FIFO register (see Figure 4 for RDYB timing).

Mode Exit

1. In single-cycle conversion mode (CTRL1:SCYCLE = ’1’) the sequencer exits into SLEEP state.

2. In continuous conversion mode (CTRL1: SCYCLE = ’0’ or (CTRL:SCYCLE = ’1’ and CTRL1:CONTSC = ’1’)),

conversions continue nonstop until the mode is exited. To interrupt and exit continuous conversion or continuous

single-cycle conversion, follow the Changing SEQUENCER Modes - Mode Exit section to put the part into STANDBY

or SLEEP state based on CTRL1:PD[1:0] set in step 1f of the Mode Entry section.

Changing Input Channel During Continuous Single-Cycle Conversion in Mode 1

1. Issue a conversion command with MODE[1:0] set to ‘01’ to exit the conversion process to STANDBY or SLEEP state

(see the Changing SEQUENCER Modes - Mode Exit section).

2. Monitor STAT:PDSTAT = ‘10’ or ‘01’ to confirm exit to STANDBY or SLEEP state.

3. Set SEQ:MUX[2:0] to select the new channel for conversion.

4. Write a conversion command (see Table 5) and set MODE[1:0] of the command byte to ‘11’.

SEQUENCER Mode 2 – Multichannel Scan with GPO Control and MUX Delays

This mode is used to sequentially convert a programmed set of channels in a preset order. Figure 7 illustrates the timing.

The states of the GPO bumps are configured using the GPO_DIR register and can be modified anytime during mode

2 operation. In mode 2, register bits CHMAP0:CHn_ ORD[2:0], CHMAP1:CHn_ORD[2:0], CHMAP0:CHn_EN, and

CHMAP1:CHn_EN are used to select channels and conversion order. Bits DELAY:GPO[7:0], CHMAP0:CHn_ GPO[2:0],

CHMAP0:CHn_GPOEN, CHMAP1:CHn_ GPO[2:0], and CHMAP1:CHn_GPOEN are ignored in this mode. The bit

CTRL1:CONTSC is ignored and bit CTRL1:SCYCLE = ‘0’ is invalid in this mode.

SEQUENCER MODE 2

CHANNEL

CONVERSION

DEL

SEQ:MDREN •

DELAY:MUX

CHANNEL

CONVERSION

DEL

SEQ:MDREN •

DELAY:MUX

CHANMAP:ORD[2:0] = 001

CHANNEL

CONVERSION

DEL

SEQ:MDREN •

DELAY:MUX

CHANMAP:ORD[2:0] = 010

CHANNEL

CONVERSION

DEL

SEQ:MDREN •

DELAY:MUX

CHANMAP:ORD[2:0] = 011

CHANNEL

CONVERSION

DEL

SEQ:MDREN •

DELAY:MUX

CHANMAP:ORD[2:0] = 100

CHANNEL

CONVERSION

DEL

SEQ:MDREN •

DELAY:MUX

CHANMAP:ORD[2:0] = 101

CHANMAP:ORD[2:0] = 110

Figure 7. Sequencer Mode 2 Timing Diagram

Programming Sequence

Mode Entry

1. Set up the following registers: SEQ, CHMAP0, CHMAP1, DELAY, GPO_DIR, CTRL1.

a. SEQ:MODE[1:0] = ‘01’ for sequencer mode 2.

b. If desired, set SEQ:RDYBEN to ‘1’ to signal data ready only when all channel conversions are completed.

c. Enable SEQ:MDREN to delay conversion start to allow for input settling. Set DELAY:MUX[7:0] to the desired

www.maximintegrated.com

Maxim Integrated | 26

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

conversion delay.

d. Set CHMAP0 and CHMAP1 to select the channels and channel order for conversion.

e. Set CTRL1:PD[1:0] to STANDBY or SLEEP state to set the desired exit state if a conversion command with

MODE[1:0] set to ‘01’ is issued during the conversion.

f. Set register GPO_DIR to enable or disable the desired GPO bumps.

g. Set CTRL1:SCYCLE = ‘1’ for single-cycle conversion mode.

2. Write a conversion command (see Table 5).

a. Set the data rate using bits RATE[3:0] of the command byte.

b. Set MODE[1:0] of the command byte to ‘11’.

3. Monitor RDYB_INTB (if SEQ:RDYBEN = ’0’) and bits STAT:SRDY[5:0] for availability of per channel conversion

results in FIFO registers.

Mode Exit

1. This mode exits to SLEEP state upon completion of sequencing all channels.

2. To interrupt current sequencing perform mode exit, see the Changing SEQUENCER Modes—Mode Exit section. This

device is put in STANDBY or SLEEP state based on CTRL1:PD[1:0] set in step 1e of the Mode Entry section.

SEQUENCER Mode 3 – Scan, with Sequenced GPO Controls

This mode is used to sequentially convert a programmed set of channels in a preset order and sequence the GPO

bumps concurrently. The GPO bumps are used to bias external circuitry such as bridge sensors; the common reference

(GPOGND) is typically ground. After all channel conversions have completed, the MAX11261 automatically powers down

into SLEEP mode. Figure 8 illustrates the sequencer mode 3 timing diagram for a 3-channel scan. Register GPO_DIR is

ignored in this mode, as the output controls are controlled by the sequencer.

www.maximintegrated.com

Maxim Integrated | 27

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

SEQUENCER MODE 3 TIMING

MUX SELECTS CHANNEL

CONVERSION

STARTS

GPO/GPIO ACTIVATED

SCAN

CHANNEL #1

DEL1

DEL2

DEL1 – PROGRAMMED DELAY USING BITS

DELAY:GPO[7:0] TO PROVIDE SUFFICIENT

SETTLING TIME FOR THE SENSOR BEFORE THE

FIRST CHANNEL IS CONVERTED.

CONVERSION

ENDS

TCONVERT

DEL2 – PROGRAMMED DELAY USING BITS

DELAY:MUX[7:0] FOR SENSOR AND ANALOG

INPUT SETTLING AFTER THE MULTIPLIER

SELECTS THE CHANNEL FOR CONVERSION.

SEQ:MDREN • DELAY:MUX

DELAY:GPO

CHANMAP:ORD[2:0] = 001

GPO/GPIO

ACTIVATED

SCAN

CHANNEL #2

(TCONVERT AND DEL1)

END TRIGGER

MUX SELECTS CHANNEL

CONVERSION

STARTS

DEL2

CONVERSION

ENDS

TCONVERT

CHANMAP:ORD[2:0]

= 010

GPO/GPIO

ACTIVATED

SCAN

CHANNEL #3

(TCONVERT AND DEL1)

END TRIGGER

MUX SELECTS CHANNEL

CONVERSION

STARTS

DEL2

CONVERSION

ENDS

TCONVERT

CHANMAP:ORD[2:0] = 011

Figure 8. Sequencer Mode 3 Timing Diagram for a 3-Channel Scan

Programming Sequence

Mode Entry

1. Set up the following registers: SEQ, CHMAP0, CHMAP1, DELAY, CTRL1, CTRL3.

a. SEQ:MODE[1:0] = ”10” for sequencer mode 3.

b. If desired, set SEQ:RDYBEN to ‘1’ to signal data ready only when all channel conversions are completed.

c. Enable SEQ:MDREN if conversion start is to be delayed to allow for input settling. Set DELAY:MUX[7:0] to the

desired conversion delay.

d. Set CHMAP0 and CHMAP1 to enable the channels for conversion and the channel conversion order. Map the

corresponding GPO bumps to a channel.

e. Enable SEQ:OCDREN for adding a delay before the multiplexer selects this channel for conversion. Set

DELAY:GPO to a delay value sufficient for the bias to settle.

f. Set CTRL1:PD[1:0] to STANDBY or SLEEP state (desired exit state if an IMPD command is issued during the

conversion).

g. Set CTRL1:SCYCLE = ‘1’ for single conversion mode.

2. Write the command byte (see Table 5).

a. Set the data rate using bits RATE[3:0] of the command byte.

b. Set MODE[1:0] of command byte to “11”.

3. Monitor RDYB_INTB (if SEQ:RDYBEN = ‘0’) and bits STAT:SRDY[5:0] for availability of per-channel conversion

results in FIFO registers.

www.maximintegrated.com

Maxim Integrated | 28

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Mode Exit

1. This mode exits to SLEEP state upon completion of sequencing all channels and output controls.

2. To interrupt current sequencing, perform mode exit. See the Changing SEQUENCER Modes - Mode Exit section.

The device is put in STANDBY or SLEEP state based on CTRL1:PD[1:0] set in step 1) of the Mode Entry section.

The bit CTRL1:CONTSC is ignored and bit CTRL1:SCYCLE = ‘0’ is invalid in this mode.

SEQUENCER Mode 4 – Autoscan with GPO Controls (CHMAP) and Interrupt

This mode features a programmable timer to wake the MAX11261 from SLEEP and power down the MAX11261 between

operations.

The MAX11261 automatically cycles through a sequence of delay, power-up, operate the GPO, scan selected channels,

perform math operations, and power-down into SLEEP state. See Figure 9.

The duty cycle is programmed by DELAY:AUTOSCAN[7:0]. The programmed value must be greater than “0x00”,

otherwise power-down is skipped and followed immediately by another scan cycle. This sequence continues until the

conversion is halted. The autoscan delay is from 4ms to 1024ms.

To generate SYNC signals for other slave devices, the master must configure AUTOSCAN[7:0] greater than “0x00”,

otherwise the SYNC signal cannot be generated.

In this mode, a register INT_STAT read will clear RDYB_ INTB if the FIFO usage interrupts are not triggered. If any of

the FIFO usage interrupts is triggered, RDYB_INTB will keep asserted. The user can disable the FIFO usage interrupts

to allow only the input comparison to generate interrupts.

The behavior of the RDYB_INTB pin ignores the SEQ:RDYBEN bit.

FULL

POWER-DOWN

SEQUENCER

MODE 3

MATH

POWER-UP

AUTOSCAN

DELAY

DELAY:AUTOSCAN

SEQUENCER

MODE 3

FULL

POWER-DOWN

MATH

POWER-UP

AUTOSCAN

DELAY

SEQUENCER

MODE 3

FULL

POWER-DOWN

MATH

DELAY:AUTOSCAN

Figure 9. Sequencer Mode 4 Timing Diagram

The GPOs are operated by the sequencer and programmed by CHMAPx registers. GPO_DIR register is ignored in

this mode. A DELAY:GPO[7:0] value of ‘0x00’ represents no delay. This mode also utilizes the channel MUX delay if

enabled by setting the SEQ:MDREN bit to ‘1’. The value programmed into the DELAY:MUX[7:0] register will be used to

delay the start of the conversion after selecting the channel. If the CTRL1:CONTSC bit is ‘1’, it is ignored in this mode.

CTRL1:SCYCLE bit of ‘0’ is invalid in this mode.

Math Operation: Conversion Result Processing and Out-Of-Range (OOR) Bit Generation

There are three options to process the conversion results to detect if a channel input signal is changing. They are

controlled by the HPF:CMP_MODE[1:0] register. The conversion result processing is shown in Figure 10.

In the following section, n indicates the channel number, N indicates a specific sample, and N-1 indicates the previous

sample of the same channel.

1. CMP_MODE[1:0] = 0b00. Compare the current result DATAn(N) with the user-programmable low limit (LIMIT_LOWn)

and the high limit (LIMIT_HIGHn). If the conversion result is within LIMIT_LOWn and LIMIT_HIGHn, there is no OOR

generated. Otherwise, an OOR is generated.

2. CMP_MODE[1:0] = 0b01. Subtract the current result DATAn(N) by the previous result DATAn(N-1). Then compare

the resultant with the user-programmable low limit (LIMIT_LOWn) and the high limit (LIMIT_ HIGHn). If the resultant

is within LIMIT_LOWn and LIMIT_HIGHn, there is no OOR generated. Otherwise an OOR is generated. After writing

www.maximintegrated.com

Maxim Integrated | 29

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

HPF register with HPF:CMP_MODE[1:0] = 0b01, the comparator is initialized and the first conversion does not detect

the OOR condition.

3. CMP_MODE[1:0] = 0b10. This option enables the highpass digital filter, generating a highpass filter output based

on the user-programmable cutoff frequency register HPF:FREQUENCY[2:0]. Compare the HPF output with the userprogrammable low limit (LIMIT_LOWn) and the high limit (LIMIT_HIGHn). If the HPF output is within LIMIT_LOWn

and LIMIT_HIGHn, there is no OOR generated. Otherwise an OOR is generated. Writing to the HPF register with

HPF:CMP_MODE[1:0] = 0b10 resets the highpass filter. The highpass filter cutoff frequency is calculated as shown

in Table 7.

4. CMP_MODE[1:0] = 0b11 is reserved.

MAX11261 CONVERSION RESULT PROCESSING

CMP_MODE[1:0]

0

1

CHANNEL n

CONVERSION

RESULT

LIMIT_HIGHn

COMP

DATAn(N-1)

OOR

LIMIT_LOWn

DATAn(N)

2

3

Z-1

K

HIGHPASS DIGITAL FILTER TO

REMOVE BASELINE DRIFT

Figure 10. Conversion Result Math Operation

Table 7. HPF Cutoff Frequency vs. HPF:FREQUENCY[2:0] Register Values

HPF:FREQUENCY[2:0]

CUTOFF FREQUENCY (Hz)

0

Scan Rate/39.0625

1

Scan Rate/78.125

2

Scan Rate/156.25

3

Scan Rate/312.5

4

Scan Rate/625

5

Scan Rate/1250

6

Scan Rate/2500

7

Scan Rate/5000

Unipolar Mode Not Supported

The math operations performed in this mode prevent using unipolar ranges. Only bipolar ranges and two’s complement

numbers are used. The LIMIT_LOWn, LIMIT_HIGHn registers are bipolar two’s complement values.

www.maximintegrated.com

Maxim Integrated | 30

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

Programming Sequence

Mode Entry

1. Set up the following registers: SEQ, CHMAP0, CHMAP1, DELAY.

a. SEQ:MODE[1:0] = ”11” for sequencer mode 4.

b. Enable SEQ:MDREN if conversion start is to be delayed to allow for input settling. Write to DELAY:MUX[7:0] to

set conversion delay.

c. Set HPF:MODE[1:0], LIMIT_LOWn, and LIMIT_ HIGHn registers to desired values.

d. Set CHMAP0 and CHMAP1 to enable the channels for conversion and the channel conversion order. Map the

GPO bump to a channel and enable it for the conversion process.

e. Enable SEQ:GPODREN for adding a delay (DEL1) before the multiplexer selects the first channel for conversion.

See [[Sequencer Mode 3 Timing Diagram for a Three-Channel Scan]] for timing. Set DELAY:GPO to a delay

value sufficient for the bias to settle.

f. Set CTRL1:PD[1:0] to STANDBY or SLEEP state (desired exit state if an IMPD command is issued during the

conversion).

g. Set CTRL1:SCYCLE = ‘1’ for single-conversion mode.

2. Write the command byte (see Table 5).

a. Set the data rate using bits RATE[3:0] of the command byte.

b. Set MODE[1:0] of the command byte to “11”.

3. This mode is perpetual; monitor interrupt signal RDYB_INTB for different interrupt requests.

a. Per-channel conversion data ready is available by reading bits STAT:SRDY[5:0] for analog input channel 5 to

channel 0.

b. Do not overwrite SEQ:MODE[1:0] during mode 4 operation. Write new SEQ:MODE[1:0] during mode exit; see

Mode Exit steps 1a and 1b.

Mode Exit

1. To exit to another sequencer mode:

a. Write SEQ:MODE[1:0] to the desired sequencer mode.

b. Issue a conversion command.

2. To exit to STANDBY or SLEEP state:

a. Follow the Changing SEQUENCER Modes—Mode Exit section to STANDBY or SLEEP state based on

CTRL1:PD[1:0] set in step 1f of the Mode Entry section.

AUTOSCAN Delay

Program delay using bits DELAY:AUTOSCAN[7:0] for selecting the scan rate. This is a power-saving feature for

throttling system power consumption. During the autoscan delay period, the MAX11261 is powered down and woken up

automatically.

Supplies and Power-On Sequence

The MAX11261 requires two power supplies, AVDD and DVDD. These power supplies can be sequenced in any order.

The analog supply (AVDD) powers the analog inputs and the modulator. The DVDD supply powers the I2C interface. The

low-voltage core logic can either be powered by the integrated LDO (default) or through DVDD. Figure 11 shows the two

possible schemes. CAPREG denotes the internally generated supply voltage. If the LDO is used, the DVDD operating

voltage range is from 2.0V to 3.6V. If the core logic is directly powered by DVDD (DVDD and CAPREG connected

together), the DVDD operating voltage range is from 1.7V to 2.0V.

www.maximintegrated.com

Maxim Integrated | 31

�MAX11261

24-Bit, 6-Channel, 16ksps, 6.2nV/√Hz PGA, DeltaSigma ADC with I2C Interface

DVDD OPERATING BETWEEN 2.0V TO 3.6V

LDO ENABLED (SET CTRL2:LDOEN = ‘1’) AND BYPASS

CAPREG TO DGND WITH 220nF

AVDD

DVDD OPERATING BETWEEN 1.7V TO 2.0V

LDO DISABLED (SET CTRL2:LDOEN = ‘0’) AND

CONNECT CAPREG TO DVDD AT BOARD LEVEL

DVDD

LDO

ANALOG

AVDD

DVDD

LDO

MAX11261

DIGITAL

INTERFACE

INPUTS

AND

OUTPUTS

2V DIGITAL

LOGIC

CAPREG

ANALOG

MAX11261

DIGITAL

INTERFACE

INPUTS

AND

OUTPUTS

2V DIGITAL

LOGIC

CAPREG

220nF

0603

X7R

DGND

Figure 11. Digital Power Architecture

AVDD

DVDD

CAPREG

VLH

VHL

VHYS

TP

TDEL

TP

TDEL

PORB

Figure 12. Undervoltage Lockout Characteristic Voltage Levels and Timing

Power-On Reset and Undervoltage Lockout

A global power-on reset (POR) is triggered until AVDD, DVDD, and CAPREG cross a minimum threshold voltage (VLH),

as shown in Figure 12.