Click here to ask about the production status of specific part numbers.

MAX11410A

General Description

The MAX11410A is a low-power, multichannel, 24-bit

delta-sigma (Δ-Σ) ADC with features and specifications

that are optimized for precision sensor measurement.

The input section includes a low-noise programmable

gain amplifier (PGA) with very high input impedance and

available gains from 1x to 128x to optimize the overall

dynamic range. Input buffers provide isolation of the

signal inputs from the switched-capacitor sampling

network when the PGA is not in use, making the ADC

easy to drive even with high-impedance sources.

Several integrated features simplify precision sensor

applications. The programmable matched current sources

provide excitation for resistive sensors. An additional

current sink and current source aid in detecting broken

sensor wires. The 10-channel input multiplexer provides

the flexibility needed for complex, multi-sensor measurements.

GPIOs reduce isolation components and ease control of

switches or other circuitry.

When used in single-cycle mode, the digital filter settles

within a single conversion cycle. The available FIR digital

filter allows single-cycle settling in 16ms while providing

more than 90dB simultaneous rejection of 50Hz and 60Hz

line noise.

The integrated on-chip oscillator requires no external

components. If needed, an external clock source may be

used instead. Control registers and conversion data are

accessed through the SPI-compatible serial interface.

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Benefits and Features

●● High Resolution and Low Noise for Signal Sources

with Wide Dynamic Range

• 24-Bit Resolution

• PGA with 1, 2, 4, 8, 16, 32, 64, and 128 Gain

Options

• 90dB Simultaneous 60Hz and 50Hz Power Line

Rejection

• 3ppm Typical INL with No Missing Codes

●● Optimized Features for More Efficient System Design

• 10 Analog Inputs May Be Used for Single-Ended/

Fully Differential in Any Combination

• Two Dedicated/One Shared Differential Voltage

Reference Inputs

• On-Demand Offset and Gain Self-Calibration

●● Low Power for Efficient Systems

• 2.7V to 3.6V Analog Supply Range

• 1.7V to 3.6V I/O Supply Range

• VPOR

Sleep Wake-Up Time

CFILTER = 0

PGA Power-Up Time

240

µs

1.25

ms

0.25

CFILTER = 20nF

2

CFILTER = 100nF

10

ms

After changing gain settings to Gain = 1.

CFILTER = 0.

0.25

After changing gain settings to Gain = 1.

CFILTER = 100nF.

10

After changing gain settings to Gain = 128.

CFILTER = 0.

2

Input Multiplexer

Power-Up Time

Settled to 21 bits with 10pF load

2

µs

Input Multiplexer

Channel-to-Channel

Settling Time

Settled to 21 bits with 2K external source

resistor

2

µs

Active generator; settled within 1% of final

value; CLOAD = 1µF

10

125K passive generator; settled within 1%

of final value; CLOAD = 1µF

575

20K passive generator; settled within 1% of

final value; CLOAD = 1µF

90

Active generator; settled within 1% of final

value; CLOAD = 1µF

10

125K passive generator; settled within 1%

of final value; CLOAD = 1µF

605

20K passive generator; settled within 1% of

final value; CLOAD = 1µF

100

PGA Settling Time

VBIAS Power-Up Time

VBIAS Settling Time

ms

ms

ms

Matched Current Source

Startup Time

110

µs

Matched Current Source

Settling Time

12.5

µs

www.maximintegrated.com

Maxim Integrated │ 12

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Electrical Characteristics (continued)

(AVDD = +3.3V, VDDIO = +1.8V, VREFP - VREFN = AVDD, TA = TMIN to TMAX, unless otherwise noted., TA = +25°C for typical specifications, unless otherwise noted, (Note 1))

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

POWER SPECIFICATIONS

Analog Supply

AVDD

2.7

3.6

V

Interface Supply

VDDIO

1.7

3.6

V

AVDD Currents

Sleep mode

0.5

3

Standby mode

115

150

Bypass mode, IDAC, VBIAS sources off,

AVDD = VREF = VIN = 3.6V, SINC4 filter,

continuous conversions at 60sps.

390

550

Buffered mode, IDAC, VBIAS sources off,

AVDD = VREF = VIN = 3.6V, SINC4 filter,

continuous conversions at 60sps.

425

600

µA

PGA enabled, IDAC, VBIAS sources off,

AVDD = VREF = VIN = 3.6V, SINC4 filter,

continuous conversions at 60sps.

TA = -40°C to +105°C

VDDIO Operating

Current

700

PGA enabled, IDAC, VBIAS sources off,

AVDD = VREF = VIN = 3.6V, SINC4 filter,

continuous conversions at 60sps.

TA = -40°C to +125°C.

520

750

All modes of operation

0.3

2

VDDREG Current

48

AVDD Duty-Cycle

Power Mode

µA

µA

Bypass mode, IDAC, VBIAS sources off,

AVDD = VREF = VIN = 3.6V, SINC4 filter,

continuous conversions at 15sps.

280

380

Buffered mode, IDAC, VBIAS sources off,

AVDD = VREF = VIN = 3.6V, SINC4 filter,

continuous conversions at 15sps.

300

400

PGA enabled, IDAC, VBIAS sources off,

AVDD = VREF = VIN = 3.6V, SINC4 filter,

continuous conversions at 15sps.

400

580

µA

SPI TIMING SPECIFICATIONS

SCLK Frequency

fSCLK

0

SCLK Period

tSCLK

125

ns

SCLK Pulse-Width High

tCH

50

ns

SCLK Pulse-Width Low

tCL

50

ns

www.maximintegrated.com

8

MHz

Maxim Integrated │ 13

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Electrical Characteristics (continued)

(AVDD = +3.3V, VDDIO = +1.8V, VREFP - VREFN = AVDD, TA = TMIN to TMAX, unless otherwise noted., TA = +25°C for typical specifications, unless otherwise noted, (Note 1))

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CSB Fall to SCLK Fall

Setup Time

tCSS0

CSB falling edge to the 1st SCLK falling

edge

40

ns

CSB Rise to SCLK Fall

Hold Time

tCSH1

Applies to the last active SCLK falling edge

3

ns

CSB Rise to SCLK Fall

tCSA

Applies to last active SCLK falling edge,

aborted sequence

12

ns

CSB Pulse-Width High

tCSPW

40

ns

100

ns

SCLK Fall to CS Fall

tCSF

DIN to SCLK Rise Setup

Time

tDS

40

ns

DIN to SCLK Rise Hold

Time

tDH

2

ns

DOUT Propagation

Delay

tDOT

DOUT Enable Time

tDOE

DOUT Disable Time

Bus Capacitance

Applies to the last active SCLK falling edge

Delay from the falling clock edge to the

transition on DOUT

40

ns

40

ns

tDOZ

25

ns

CB

20

pF

±1

µA

0.3 x

VDDIO

V

0

LOGIC INPUTS AND OUTPUTS (NON-GPIO)

Input Current

Leakage current

Input Low Voltage

VIL

Input High Voltage

VIH

Input Hysteresis

0.7 x

VDDIO

VHYS

200

Input Capacitance

VOL

IOL = 1mA, VDDIO = 1.8V and 3.6V

Output High Level

VOH

IOL = 1mA, VDDIO = 1.8V and 3.6V

High-Z Output

Capacitance

www.maximintegrated.com

mV

5

Output Low Level

High-Z Leakage Current

V

Note 2

pF

0.1 x

VDDIO

0.9 x

VDDIO

V

V

-100

+100

9

nA

pF

Maxim Integrated │ 14

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Electrical Characteristics (continued)

(AVDD = +3.3V, VDDIO = +1.8V, VREFP - VREFN = AVDD, TA = TMIN to TMAX, unless otherwise noted., TA = +25°C for typical specifications, unless otherwise noted, (Note 1))

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

±1

µA

0.3 x

VDDIO

V

GENERAL-PURPOSE INPUT AND OUTPUT (GPIO)

Input Current

Leakage current

Input Low Voltage

VIL

Input High Voltage

VIH

Input Hysteresis

0.7 x

VDDIO

VHYS

200

Output Low Level

VOL

IOL = 1mA, AVDD = 2.7V and 3.6V

Output High Level

VOH

IOL = 1mA, AVDD = 2.7V and 3.6V

Low-Side Power Switch

Current

GPIO output voltage = 1V

Low-Side Power Switch

Impedance

GPIO output voltage = 1V

mV

0.1 x

AVDD

V

0.9 x

AVDD

V

25

mA

Internal Clock Output

Frequency

2.3347

Internal Clock Output

Duty Cycle

40

External Clock Input

Frequency

External Clock Input

Duty Cycle

V

2.4576

35

Ω

2.5805

MHz

60

%

2.4576

30

MHz

70

%

Note 1: Limits are 100% production tested at TA = +25°C. Limits over the operating temperature range are guaranteed by design

and characterization.

Note 2: These specifications are not fully tested and are guaranteed by design and/or characterization.

Note 3: Gain error does not include zero-scale errors. It is calculated as (full-scale error – offset error). After calibration, gain error is

on the order of the noise.

Note 4: ppmFS is parts per million of full scale.

Note 5: After calibration, the offset voltage is on the order of the noise.

www.maximintegrated.com

Maxim Integrated │ 15

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Typical Operating Characteristics

(VAVDD = 3.3V, VREF = 2.5V, internal clock, TA = +25°C unless otherwise noted.)

16.8sps NOISE HISTOGRAM

PGA = 32,

FIR FILTER,

INPUT REFERRED,

SHORTED INPUTS,

VCM = AVDD/2

250

200

NUMBER OF OCCURRENCES

NUMBER OF OCCURRENCES

200

toc1

150

100

50

59.8sps NOISE HISTOGRAM

toc2

PGA = 128,

FIR FILTER,

INPUT REFERRED,

SHORTED INPUTS,

VCM = AVDD/2

1800

1600

NUMBER OF OCCURRENCES

16.8sps NOISE HISTOGRAM

250

150

100

50

1400

1200

toc3

PGA = 32,

SINC FILTER,

INPUT REFERRED

SHORTED INPUTS,

VCM = AVDD/2

1000

800

600

400

200

-0.5

0.0

0.5

INPUT VOLTAGE (µV)

1.0

-0.9

59.8sps NOISE HISTOGRAM

NUMBER OF OCCURRENCES

1800

1600

1400

PGA = 128,

SINC FILTER,

INPUT-REFERRED

SHORTED INPUTS,

VCM = AVDD/2

1000

800

600

400

-1.0

-0.5

0.0

0.5

INPUT VOLTAGE (µV)

GAIN ERROR vs. TEMPERATURE

0.06

1.0

PGA = 32

0

PGA = 128

0

50

100

150

0.0075

PGA = 128

PGA = 1

0.0025

0

PGA = 32

-0.005

-0.0075

50

www.maximintegrated.com

100

PGA = 32

FIR FILTER, 16sps, SINGLE CYCLE,

CALIBRATED AT EACH TEMPERATURE

-50

150

0

-0.01

-50

0

50

100

TEMPERATURE (°C)

150

50

100

TEMPERATURE (°C)

150

ANALOG ACTIVE SUPPLY CURRENT

vs. TEMPERATURE

toc09

500

FIR FILTER, 16sps, SINGLE CYCLE,

CALIBRATED AT EACH TEMPERATURE

-0.0025

-0.04

TEMPERATURE (°C)

-4

-10

toc08

0.01

GAIN ERROR (%)

GAIN ERROR (%)

PGA = 32

PGA = 128

0

0

-2

GAIN ERROR vs. TEMPERATURE

0

-50

2

TEMPERATURE (°C)

toc07

PGA = 1

-0.02

4

-6

0.005

0.02

PGA = 1

PGA = 128

-8

-50

1.1

8

PGA = 1

-5

0.0

0.6

INPUT VOLTAGE (µV)

toc06

6

5

-0.6

OFFSET VOLTAGE vs. TEMPERATURE

FIR FILTER, 16sps, SINGLE CYCLE,

CALIBRATED AT ROOM TEMPERATURE

10

-15

FIR FILTER, 16sps, SINGLE CYCLE,

CALIBRATED AT ROOM TEMPERATURE

0.04

-1.0

10

-10

200

-0.06

0

0.9

toc5

20

15

1200

0

0.0

0.5

INPUT VOLTAGE (µV)

OFFSET VOLTAGE vs. TEMPERATURE

toc4

OFFSET VOLTAGE (μV)

2000

-0.5

OFFSET VOLTAGE (μV)

-1.0

0

ANALOG SUPPLY CURRENT (μA)

0

PGA = 128

450

PGA = 32

400

PGA = 1

350

BUFFER MODE

300

250

AVDD = 2.7V

NORMAL MODE

-50

0

50

100

150

TEMPERATURE (°C)

Maxim Integrated │ 16

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Typical Operating Characteristics (continued)

(VAVDD = 3.3V, VREF = 2.5V, internal clock, TA = +25°C unless otherwise noted.)

PGA = 32

PGA = 1

350

BUFFER MODE

300

AVDD = 3.3V

NORMAL MODE

-50

0

50

100

500

450

PGA = 32

400

350

BUFFER MODE

300

250

150

PGA = 1

0

ANALOG STANDBY CURRENT

vs. TEMPERATURE

AVDD = 3.6V

110

12

100

8

INL (ppm)

AVDD = 3.6V

0.6

0.4

0.2

0

AVDD = 2.7V

-50

0

AVDD = 3.3V

90

50

100

INL vs. INPUT VOLTAGE

toc14

15

PGA = 1

AVDD = 2.7V

70

-50

0

50

10

+125°C

+105°C

-40°C

4

5

+25°C

+105°C

0

-40°C

-4

100

-8

150

+25°C

-2.5 -2 -1.5 -1 -0.5

TEMPERATURE (°C)

30

0

0.5

1

1.5

2

-10

-0.09

2.5

INTERNAL OSCILLATOR FREQUENCY

vs. TEMPERATURE

toc16

OSCILLATOR FREQUENCY (MHz)

10

0

-10

-20

0.004

0.012

DIFFERENTIAL INPUT (V)

www.maximintegrated.com

0.02

toc18

106

AVDD = 3.0V

2.45

AVDD = 2.7V

AVDD = 3.3V

2.44

104

PGA = 32

102

100

98

2.43

PGA = 128

96

AVDD = 3.6V

2.42

FIR FILTER, 16sps,

SINGLE CYCLE

94

-50

0

0.09

PGA = 1

108

2.46

2.41

-0.004

-0.03

0

0.03

0.06

DIFFERENTIAL INPUT (V)

110

2.47

+25°C

-0.012

-0.06

DC CMRR vs. TEMPERATURE

CALIBRATED AT EACH TEMPERATURE

toc17

2.48

PGA = 128

20

-30

-0.02

-5

DIFFERENTIAL INPUT (V)

INL vs. INPUT VOLTAGE

toc15

PGA = 32

0

80

150

TEMPERATURE (°C)

CMRR (dB)

ANALOG STANDBY CURRENT (μA)

AVDD = 3.3V

0.8

150

INL vs. INPUT VOLTAGE

16

INL (ppm)

100

20

toc13

120

60

1

TEMPERATURE (°C)

TEMPERATURE (°C)

130

50

toc12

1.2

AVDD = 3.6V

NORMAL MODE

-50

ANALOG SLEEP CURRENT

vs. TEMPERATURE

1.4

INL (ppm)

400

PGA = 128

550

450

toc11

600

PGA = 128

500

250

toc10

ANALOG SUPPLY CURRENT (μA)

ANALOG SUPPLY CURRENT (μA)

550

ANALOG QUIESCENT CURRENT

vs. TEMPERATURE

ANALOG SLEEP CURRENT (μA)

ANALOG QUIESCENT CURRENT

vs. TEMPERATURE

50

100

TEMPERATURE (°C)

150

92

-50

0

50

100

150

TEMPERATURE (°C)

Maxim Integrated │ 17

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Typical Operating Characteristics (continued)

(VAVDD = 3.3V, VREF = 2.5V, internal clock, TA = +25°C unless otherwise noted.)

DC PSRR vs. GAIN

toc19

150

SINC, 60sps

110

FIR, 16sps

100

IDAC1

251.2

251

IDAC0

250.8

90

80

251.4

0

50

100

250.6

150

-50

0

CURRENT SOURCE MISMATCH CURRENT (μA)

NUMBER OF OCCURRENCES

35

30

25

20

15

10

5

-0.06

-0.02

0.02

0.06

60

-0.04

-0.06

-0.08

-50

0

50

www.maximintegrated.com

0

150

0

0.5

1

2.5

3

toc26

2.5

60

55

3

toc27

IIN2

50

IIN3

45

40

IIN2, IIN3 (nA)

35

30

25

0

1.5

2

(VIN2 - VIN3) (V)

ABSOLUTE INPUT CURRENT vs.

INPUT VOLTAGE (TA = +125°C)

IIN3

35

30

25

20

15

10

BUFFERED MODE,

VREF1P - VREF1N = 2.5V

5

(VIN2 , VIN3) (V)

100

IIN2

10

BUFFERED MODE,

VREF1P - VREF1N = 2.5V

2

BUFFERED MODE,

VREF1P - VREF1N = 2.5V

5

IDAC0 = IDAC1 = 250µA

40

15

1.5

25

10

-0.14

15

1

30

15

-0.12

20

0.5

35

20

-0.1

20

0

IIN3

40

45

25

toc24

IIN2

45

-0.02

50

30

0

60

50

60

IIN2, IIN3 (nA)

IIN2, IIN3 (nA)

toc25

35

5

toc23

55

ABSOLUTE INPUT CURRENT

vs. INPUT VOLTAGE (TA = +105°C)

IIN3

10

-2.75 -2.25 -1.75 -1.25 -0.75 -0.25 0.25 0.75

ABSOLUTE INPUT CURRENT vs.

INPUT VOLTAGE (TA = -40°C)

0

55

40

0

150

0.02

-0.16

0.1

IIN2

45

10

TEMPERATURE (°C)

ABSOLUTE INPUT CURRENT

vs. INPUT VOLTAGE (TA = +25°C)

50

15

INITIAL ACCURACY (%)

0.04

MISMATCH ERROR (%)

55

100

MATCHED CURRENT

SOURCE MISMATCH DRIFT

toc22

IDAC = 250µA

TA = +25°C

-0.1

50

IIN2, IIN3 (nA)

50

40

20

TEMPERATURE (°C)

MATCHED CURRENT SOURCE

MISMATCH HISTOGRAM

45

25

5

IDAC0 = IDAC1 = 250µA

GAIN (V/V)

0

NUMBER OF OCCURRENCES

CURRENT SOURCE (μA)

DC PSRR (dB)

FIR, 40sps

120

IDAC0 = IDAC1 = 250µA

TA = +25°C

30

251.6

130

toc21

35

toc20

251.8

SINC, 120sps

SINC, 240sps

140

MATCHED CURRENT SOURCE

ACCURACY HISTOGRAM

MATCHED CURRENT SOURCE DRIFT

0

0.5

1

BUFFERED MODE,

VREF1P - VREF1N = 2.5V

5

1.5

(VIN2 , VIN3) (V)

2

2.5

0

0

0.5

1

1.5

2

2.5

3

(VIN2 - VIN3) (V)

Maxim Integrated │ 18

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

AIN0/REF0P

1

AIN1/REF0N

2

AIN2

3

AIN3

4

REF2 N

REF2 P

GND

VDDIO

CAPREG

25

24

23

22

REF1 P

27

26

REF1 N

28

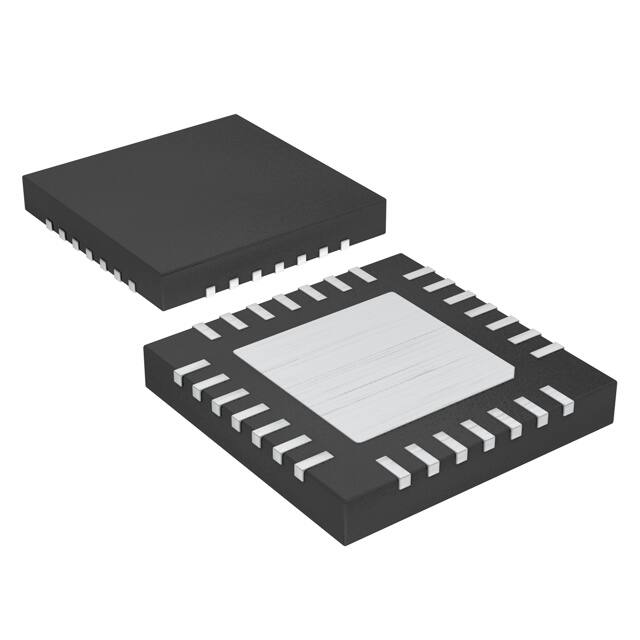

Pin Configuration

+

MAX11410A

21

GPIO_0

20

VDDREG

19

SCLK

18

CSB

14

13

AGND

AVDD

12

AIN9

DOUT/INTB

11

15

10

7

AIN7

AIN4

AIN8

GPIO1

9

DIN

16

8

17

6

AIN6

5

AIN5

CAPP

CAPN

Pin Description

PIN

NAME

FUNCTION

REF

SUPPLY

TYPE

AIN0/REF0P

Channel 0 Analog Input/Positive Differential Reference 0 Input.

When used as an analog input, may serve as either the positive or

negative differential input. May also serve as current source output.

When used as a reference input, REF0P must be more positive

than REF0N.

AVDD

Analog Input

2

AIN1/REF0N

Channel 1 Input/Negative Differential Reference 0 Input. When

used as an analog input, may serve as either the positive or

negative differential input. May also serve as current source

output. When used as a reference input, REF0P must be more

positive than REF0N.

AVDD

Analog Input

3

AIN2

Channel 2 Input. May serve as either the positive or negative

differential input. May also serve as current source output.

AVDD

Analog Input

4

AIN3

Channel 3 Input. May serve as either the positive or negative

differential input. May also serve as current source output.

AVDD

Analog Input

5

CAPP

PGA Output. Connect 1nF capacitor across CAPP and CAPN.

AVDD

Output

6

CAPN

PGA output. Connect 1nF capacitor across CAPP and CAPN

AVDD

Output

7

AIN4

Channel 4 Input. May serve as either the positive or negative

differential input. May also serve as current source output.

AVDD

Analog Input

8

AIN5

Channel 5 Input. May serve as either the positive or negative

differential input. May also serve as current source output.

AVDD

Analog Input

9

AIN6

Channel 6 Input. May serve as either the positive or negative

differential input. May also serve as current source output.

AVDD

Analog Input

MAX11410A

1

www.maximintegrated.com

Maxim Integrated │ 19

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Pin Description (continued)

PIN

MAX11410A

NAME

FUNCTION

REF

SUPPLY

TYPE

10

AIN7

Channel 7 Input. May serve as either the positive or negative

differential input. May also serve as current source output.

AVDD

Analog Input

11

AIN8

Channel 8 Input. May serve as either the positive or negative

differential input. May also serve as current source output.

AVDD

Analog Input

12

AIN9

Channel 9 Input. May serve as either the positive or negative

differential input. May also serve as current source output.

AVDD

Analog Input

13

AGND

Analog Ground Voltage for AVDD Supply. Connect AGND and GND

together.

N/A

Ground

14

AVDD

Analog Supply Voltage, +2.7V to +3.6V with respect to AGND.

AVDD

Power

This pin serves a dual function. Serial Data Output: the device will

drive this pin in response to a serial clock at SCLK, when data is

read from the internal registers. In addition to the serial data output

function, the DOUT/INTB pin also indicates an enabled interrupt

condition has occurred when the pin is asserted low. To view the

interrupt state on DOUT/INTB, enable CSB.

VDDIO

Digital Output

15

DOUT/INTB

16

GPIO1

Register-Controlled, General-Purpose Input/Output.

AVDD

Digital I/O

DIN

Serial Data Input. Data present at DIN is shifted in to the part’s internal

registers in response to a serial clock at SCLK, either when the part is

accessed for an internal register write or for a command operation.

VDDIO

Digital Input

18

CSB

Chip Select Bar. Active-Low Logic Input. Use CSB to select the IC

for access via the serial interface. CSB is used for frame

synchronization for communications when SCLK is continuous. CSB

transitioning from low to high is used to reset the SPI interface.

VDDIO

Digital Input

19

SCLK

Serial Clock. Logic Input. Apply an external serial clock to this input

to issue commands to or access data.

VDDIO

Digital Input

20

VDDREG

Digital Regulator Supply, Connect to AVDD.

AVDD

Power

Register-Controlled General-Purpose Input/Output and External

Clock Signal Input. When external clock mode is selected (EXTCLK

= 1), provide a 2.4576MHz clock signal at CLK. Other frequencies

can be used, but the data rate and digital filter notch frequencies

scale accordingly.

AVDD

Digital I/O

Digital Regulator Output. Connect a 100nF capacitor from

CAPREG to AGND.

AVDD

Power

Digital Interface Supply (+1.8V to +3.6V).

VDDIO

Power

N/A

Ground

17

21

GPIO0

22

CAPREG

23

VDDIO

24

GND

25

REF2P

Positive Differential Reference 2 Input. REF2P must be more

positive than REF2N.

AVDD

Analog Input

26

REF2N

Negative Differential Reference 2 Input. REF2P must be more

positive than REF2N.

AVDD

Analog Input

27

REF1P

Positive Differential Reference 1 input. REF1P must be more

positive than REF1N.

AVDD

Analog Input

28

REF1N

Negative Differential Reference 1 input. REF1P must be more

positive than REF1N.

AVDD

Analog Input

www.maximintegrated.com

Ground Reference for VDDIO. Connect to AGND.

Maxim Integrated │ 20

�MAX11410A

Detailed Description

This low-power, multichannel, 24-bit Δ-Σ ADC has

features and specifications that are optimized for

precision measurement of sensors and other analog

signal sources.

The input section includes a low-noise PGA with very

high input impedance and available gains from 1x

to 128x to optimize the overall dynamic range. Lowpower input buffers may be enabled to provide isolation of the signal source from the modulator's switchedcapacitor sampling network when the PGA is

not in use, reducing the supply current requirements

compared to the PGA.

Several integrated features simplify precision sensor

applications. The programmable matched current sources

provide excitation for resistive sensors; 16 different

current levels are available, allowing sensor full-scale

range to be tuned for optimum signal-to-noise ratio. An

additional current sink and current source supply small

current levels to aid in detecting broken sensor wires. The

5-channel differential/10-channel single-ended multiplexer

provides the flexibility needed for complex multisensor

measurements. GPIOs reduce isolation components and

ease control of switches or other circuitry.

The ADC can operate in continuous conversion mode at

data rates up to 1920sps, and in single-cycle conversion

mode at rates up to 480sps. When used in single-cycle

mode, the digital filter settles within a single conversion

cycle. The available FIR digital filter allows single-cycle

settling in 16ms, while providing more than 90dB

simultaneous rejection of 50Hz and 60Hz line noise.

The integrated on-chip oscillator requires no external

components. If needed, an external clock source may be

used instead. Control registers and conversion data are

accessed through the SPI-compatible serial interface.

Analog Inputs

The ten analog inputs (AIN0–AIN9) are configurable for

differential/single-ended operation. For each conversion,

the input multiplexer can be configured such that any of

the 10 analog inputs or AVDD can be used as the positive

input. Additionally, any of the 10 analog inputs or AGND

can be used as the negative input for the differential measurement. The multiplexer outputs may either drive the

ADC inputs directly or drive low-power buffers. They then

drive the ADC or the PGA inputs.

AIN0 and AIN1 are internally connected to the reference

multiplexer. When used as reference inputs, they serve as

REF0P and REF0N.

www.maximintegrated.com

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Each of the two current sources (IDAC0 and IDAC1)

can be routed to any of the 10 analog inputs. The bias

voltage source (VBIAS) can be routed to any of analog

inputs AIN0–AIN7.

Signal Path Considerations

Three signal-path options are available to trade powersupply current against input impedance, gain, and input

voltage range by enabling the PGA or the input buffers,

or bypassing both and driving the modulator directly. The

PGA control register selects among these options, which

are summarized below.

Bypass (Direct Signal Path) Mode

In bypass mode, the multiplexer outputs are directly

connected to the ADC modulator inputs. In this mode,

the input buffer and the PGA are disabled for minimum

power-supply current. This mode allows input voltages

from VAGND - 30mV to VAVDD + 30mV, and adds

no amplifier noise to the signal. Input bias current is

typically 1µA/V, which is appropriate when driving with a

low source resistance.

For smaller signal amplitudes, digital gains of 2 and 4

are available when using the direct signal path. See the

Digital Gain section for more information.

Buffered Mode

In buffered mode, the multiplexer outputs drive the inputs

to the low-power signal buffers, which then drive the ADC

modulator inputs. Selecting buffered mode disables the

PGA. Input voltages from VAGND + 100mV to VAVDD 100mV are accepted in this mode, and no amplifier noise

is added to the signal. The input bias current, typically

61nA, is significantly less than that in the direct mode,

so higher source resistances may be accommodated

without causing appreciable errors. Enabling the input

buffers increases the power supply current by 35µA (typ)

compared to the bypassed (direct signal path) mode.

As with the bypassed mode, digital gains of 2 and 4 are

available when using the buffered mode. See the Digital

Gain section for more information.

PGA Mode

The PGA provides gains of 1, 2, 4, 8, 16, 32, 64, or 128.

Selecting PGA mode enables the PGA, connects the

PGA inputs to the multiplexer outputs, connects the PGA

outputs to the ADC modulator inputs, and disables the

low-power input buffers. The PGA accepts input voltages

from VAGND + 100mV to VAVDD - 100mV for gains up to

16, and VAGND + 200mV to VAVDD - 200mV for gains

from 32 to 128. When enabled, the PGA supply current is

typically 130µA.

Maxim Integrated │ 21

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Input current in PGA mode is much lower than in the

Buffered or Direct modes, so the PGA mode is a good

choice for maintaining precision when source resistances

are high. Note that the input current in PGA mode is

dominated by multiplexer leakage current, and is highest

when the input voltage, including that of unused inputs,

is nearest AVDD or GND. For applications that are most

sensitive to the effects of input current, connect any

unused inputs to a voltage near AVDD/2.

Note that the maximum usable gain will be limited by

the reference voltage and input voltage. Ensure that the

differential input voltage multiplied by the PGA gain is less

than or equal to the reference voltage:

VIN x GAIN ≤ VREF

Where:

VIN = differential input voltage

GAIN = PGA gain

VREF = reference voltage

Also ensure that the input common-mode voltage (VCM)

falls within the acceptable common-mode voltage range

of the PGA:

Digital Gain

Programmable digital gain settings of 2 and 4 are available

in the Direct and Buffered modes. Select the desired

gain using the Gain bits of the PGA register. Digital gain

selections greater than or equal to 4 will result in digital

gain equal to 4. The input range is 0V to VREF/GAIN for

unipolar conversions or ±VREF/GAIN for bipolar conversions.

The modulator produces 32 bits of data, and for unity

gain, the 8 LSBs are truncated before the data is stored

in the 24-bit conversion data registers. Selecting a digital

gain of 2 causes the MSB and the 7 LSBs to be discarded,

thus producing 24 bits of data with an effective “gain” of 2.

Note that, for any data rate, the noise floor remains

constant, independent of the digital gain setting. Digital

gain is useful for systems whose input noise is dominated

by the source, or systems that can take advantage of

averaging multiple readings to improve effective

resolution. For cases when the output noise is below an

LSB, using digital gain can decrease the input-referred

noise at the expense of reduced dynamic range.

200mV + (VIN x GAIN)/2 ≤ VCM ≤ AVDD – 200mV (VIN x GAIN)/2 for gains of 32 to 128 or

100mV + (VIN x GAIN)/2 ≤ VCM ≤ AVDD - 100mV (VIN x GAIN)/2 for gains of 1 to 16

Where:

VCM = (AIN_P- AIN_N)/2

Figure 1. Digital Programmable Gain Example.

www.maximintegrated.com

Maxim Integrated │ 22

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Noise Performance

The input-referred noise depends on the selected data

rate, filter, input signal path (bypass, buffer, or PGA), and

the PGA gain (when selected). This is illustrated in the

tables below. Table 1 shows input-referred noise voltage

(in µVRMS). Table 2 shows effective resolution, which is

defined as:

Effective Resolution = Log2(FSR/rms noise), where

FSR is the full-scale input range (5V in bipolar mode with

a 2.5V reference), and

rms noise is the input-referred rms noise.

The third table shows noise-free resolution (NFR), which

is defined as:

NFR = Log2(FSR/p-p noise), where

FSR is the full-scale input range, (5V in bipolar mode with

a 2.5V reference), and

p-p noise is 6.6 times the input-referred rms noise.

Values shown are for continuous conversions. Singlecycle data rates are similar for the FIR filters, and are onefourth the continuous data rate for the SINC4 filter. Note

that higher PGA gain reduces the input-referred noise, but

because the input voltage range is reduced, the effective

resolution decreases.

Table 1. Input-Referred Noise (µVRMS) with VREF = 2.5V, AVDD = 3.3V, and Inputs Shorted

RATE

(sps)

BYPASS

BUFFER

PGA

1X

PGA

2X

PGA

4X

PGA

8X

PGA

16X

PGA

32X

PGA

64X

PGA

128X

FIR50/60

1

0.648

0.681

0.372

0.248

0.095

0.058

0.069

0.067

0.057

0.051

FIR50/60

2.1

3.241

3.128

3.489

1.747

0.807

0.430

0.187

0.109

0.078

0.057

FIR50/60

4.2

4.398

4.256

4.758

2.350

1.223

0.599

0.303

0.175

0.108

0.113

FIR50/60

8.4

4.511

4.428

5.259

2.529

1.326

0.684

0.373

0.218

0.152

0.139

FIR50/60

16.8

4.743

4.621

5.179

2.575

1.367

0.633

0.399

0.247

0.211

0.188

FIR50

1.3

1.716

1.741

1.589

0.833

0.388

0.169

0.082

0.065

0.068

0.055

FIR50

2.7

3.656

3.640

4.009

2.053

0.983

0.505

0.245

0.119

0.087

0.091

FIR50

5.3

4.374

4.315

4.912

2.480

1.252

0.631

0.312

0.185

0.127

0.121

FIR50

10.6

4.469

4.412

5.306

2.606

1.312

0.647

0.347

0.203

0.151

0.141

FIR50

21.3

4.604

4.511

5.363

2.655

1.351

0.680

0.386

0.230

0.232

0.199

FIR50

39.9

4.710

4.571

5.317

2.633

1.349

0.709

0.449

0.323

0.265

0.291

FIR60

1.3

1.721

1.765

1.470

0.794

0.370

0.160

0.072

0.072

0.056

0.068

FIR60

2.7

3.677

3.719

3.987

1.988

1.030

0.504

0.230

0.147

0.093

0.061

FIR60

5.3

4.303

4.417

4.951

2.473

1.220

0.636

0.309

0.168

0.141

0.121

FIR60

10.6

4.663

4.522

5.174

2.636

1.344

0.632

0.330

0.235

0.190

0.182

FIR60

21.3

4.781

4.672

5.449

2.780

1.336

0.760

0.369

0.268

0.219

0.225

FIR60

39.9

4.499

4.726

5.116

2.711

1.293

0.719

0.456

0.373

0.222

0.290

Sinc4

1.1

0.399

0.436

0.156

0.106

0.074

0.062

0.074

0.057

0.040

0.039

Sinc4

2.5

3.565

3.573

3.899

1.954

0.982

0.479

0.222

0.111

0.070

0.062

Sinc4

5

4.432

4.339

4.854

2.435

1.239

0.611

0.305

0.171

0.104

0.079

Sinc4

10

4.542

4.591

5.192

2.602

1.274

0.664

0.339

0.190

0.135

0.134

Sinc4

59.8

4.920

4.508

5.066

2.658

1.284

0.655

0.297

0.281

0.214

0.234

Sinc4

119.7

2.736

2.459

3.045

1.553

0.959

0.620

0.367

0.355

0.293

0.276

Sinc4

239.4

2.762

3.000

3.366

1.683

0.948

0.596

0.540

0.473

0.383

0.365

Sinc4

478.7

3.414

2.766

2.758

1.623

1.023

0.685

0.458

0.562

0.478

0.536

FILTER

Sinc4

957.4

4.434

3.840

4.503

2.462

1.603

1.104

0.774

1.082

0.692

0.725

Sinc4

1914.8

24.496

24.785

25.092

14.761

5.831

3.855

2.152

1.332

1.115

1.038

www.maximintegrated.com

Maxim Integrated │ 23

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Table 2. Effective Resolution with VREF = 2.5V, AVDD = 3.3V, and Inputs Shorted

FILTER

RATE

(sps)

BYPASS

BUFFER

PGA

1X

PGA

2X

PGA

4X

PGA

8X

PGA

16X

PGA

32X

PGA

64X

PGA

128X

FIR50/60

1

22.880

22.808

23.682

23.267

23.652

23.354

22.112

21.150

20.392

19.554

FIR50/60

2.1

20.557

20.608

20.451

20.449

20.563

20.470

20.672

20.455

19.934

19.395

FIR50/60

4.2

20.117

20.164

20.003

20.021

19.963

19.992

19.975

19.767

19.462

18.401

FIR50/60

8.4

20.080

20.107

19.859

19.915

19.847

19.800

19.677

19.448

18.971

18.097

FIR50/60

16.8

20.008

20.045

19.881

19.889

19.802

19.912

19.578

19.274

18.500

17.668

FIR50

1.3

21.475

21.454

21.585

21.518

21.620

21.820

21.863

21.205

20.131

19.432

FIR50

2.7

20.383

20.390

20.250

20.216

20.279

20.239

20.283

20.328

19.776

18.713

FIR50

5.3

20.125

20.144

19.957

19.943

19.929

19.917

19.934

19.690

19.230

18.302

FIR50

10.6

20.094

20.112

19.846

19.872

19.861

19.881

19.781

19.557

18.979

18.084

FIR50

21.3

20.051

20.080

19.831

19.845

19.819

19.809

19.627

19.371

18.358

17.585

FIR50

39.9

20.018

20.061

19.843

19.857

19.822

19.750

19.410

18.883

18.169

17.036

FIR60

1.3

21.470

21.433

21.698

21.587

21.688

21.902

22.059

21.053

20.422

19.137

FIR60

2.7

20.375

20.359

20.258

20.262

20.211

20.241

20.374

20.020

19.681

19.300

FIR60

5.3

20.148

20.110

19.946

19.947

19.967

19.906

19.946

19.824

19.078

18.300

FIR60

10.6

20.032

20.077

19.882

19.855

19.827

19.916

19.851

19.344

18.652

17.710

FIR60

21.3

19.996

20.030

19.808

19.778

19.835

19.649

19.693

19.153

18.447

17.405

FIR60

39.9

20.084

20.013

19.899

19.815

19.883

19.729

19.388

18.677

18.426

17.040

Sinc4

1.1

23.580

23.453

24.933

24.498

24.002

23.266

22.015

21.385

20.892

19.923

Sinc4

2.5

20.420

20.416

20.290

20.287

20.280

20.315

20.427

20.425

20.088

19.258

Sinc4

5

20.106

20.136

19.974

19.970

19.944

19.965

19.967

19.799

19.518

18.921

Sinc4

10

20.070

20.055

19.877

19.874

19.904

19.843

19.814

19.646

19.145

18.156

Sinc4

59.8

19.955

20.081

19.913

19.843

19.893

19.863

20.006

19.084

18.476

17.352

Sinc4

119.7

20.801

20.955

20.647

20.619

20.314

19.944

19.701

18.747

18.026

17.111

Sinc4

239.4

20.788

20.668

20.503

20.503

20.331

19.999

19.143

18.335

17.639

16.706

Sinc4

478.7

20.482

20.786

20.790

20.555

20.220

19.800

19.380

18.084

17.320

16.154

Sinc4

957.4

20.105

20.312

20.083

19.954

19.573

19.111

18.623

17.140

16.784

15.718

Sinc4

1914.8

17.639

17.622

17.604

17.370

17.710

17.307

17.148

16.840

16.096

15.200

www.maximintegrated.com

Maxim Integrated │ 24

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Table 3. Noise-Free Resolution with VREF = 2.5V, AVDD = 3.3V, and Inputs Shorted

FILTER

RATE

(sps)

BYPASS

BUFFER

PGA

1X

PGA

2X

PGA

4X

PGA

8X

PGA

16X

PGA

32X

PGA

64X

PGA

128X

FIR50/60

1

20.158

20.085

20.959

20.545

20.929

20.631

19.389

18.427

17.670

16.831

FIR50/60

2.1

17.835

17.886

17.728

17.726

17.841

17.748

17.950

17.732

17.211

16.672

FIR50/60

4.2

17.394

17.442

17.281

17.299

17.241

17.270

17.252

17.045

16.740

15.679

FIR50/60

8.4

17.358

17.384

17.136

17.192

17.124

17.078

16.955

16.726

16.248

15.375

FIR50/60

16.8

17.285

17.323

17.158

17.166

17.080

17.190

16.856

16.551

15.777

14.946

FIR50

1.3

18.752

18.731

18.863

18.795

18.898

19.098

19.140

18.483

17.409

16.709

FIR50

2.7

17.661

17.667

17.528

17.493

17.556

17.517

17.561

17.605

17.053

15.991

FIR50

5.3

17.402

17.422

17.235

17.221

17.207

17.195

17.211

16.967

16.508

15.579

FIR50

10.6

17.371

17.390

17.123

17.149

17.139

17.158

17.059

16.835

16.257

15.362

FIR50

21.3

17.328

17.358

17.108

17.122

17.096

17.087

16.904

16.649

15.636

14.863

FIR50

39.9

17.295

17.338

17.120

17.134

17.099

17.028

16.687

16.160

15.446

14.313

FIR60

1.3

18.747

18.711

18.976

18.864

18.966

19.179

19.337

18.331

17.699

16.414

FIR60

2.7

17.652

17.636

17.536

17.540

17.489

17.519

17.652

17.297

16.959

16.578

FIR60

5.3

17.426

17.388

17.223

17.225

17.244

17.184

17.224

17.101

16.355

15.577

FIR60

10.6

17.310

17.354

17.160

17.133

17.104

17.194

17.129

16.621

15.929

14.987

FIR60

21.3

17.274

17.307

17.085

17.056

17.113

16.926

16.970

16.431

15.724

14.683

FIR60

39.9

17.361

17.290

17.176

17.092

17.160

17.006

16.665

15.955

15.703

14.318

Sinc4

1.1

20.857

20.730

22.211

21.775

21.279

20.543

19.293

18.662

18.169

17.201

Sinc4

2.5

17.697

17.694

17.568

17.565

17.557

17.593

17.704

17.703

17.366

16.536

Sinc4

5

17.383

17.414

17.252

17.247

17.222

17.242

17.244

17.076

16.796

16.199

Sinc4

10

17.348

17.332

17.155

17.152

17.182

17.121

17.092

16.924

16.423

15.433

Sinc4

59.8

17.232

17.358

17.190

17.121

17.170

17.141

17.284

16.362

15.753

14.629

Sinc4

119.7

18.079

18.233

17.924

17.896

17.592

17.221

16.979

16.025

15.303

14.388

Sinc4

239.4

18.065

17.946

17.780

17.780

17.608

17.277

16.421

15.612

14.916

13.983

Sinc4

478.7

17.760

18.063

18.067

17.833

17.498

17.077

16.657

15.362

14.597

13.431

Sinc4

957.4

17.383

17.590

17.360

17.231

16.851

16.389

15.900

14.417

14.061

12.995

Sinc4

1914.8

14.917

14.900

14.882

14.647

14.987

14.584

14.426

14.118

13.374

12.478

www.maximintegrated.com

Maxim Integrated │ 25

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Reference Inputs

Modulator Duty-Cycle Mode

There are three selectable differential reference voltage inputs. Select the reference input using bits

REF_SEL in the CTRL register. Either VREFP,

VREFN, or both may be buffered, as determined by the

REFBUFP_EN and REFBUFN_EN bits. With the reference buffer disabled, the input current is a few microamps

(2.1µA/V, typ). Enabling a reference buffer reduces the

reference input current to 65nA, typ. With the buffer

enabled, the common-mode voltage range for VREFP

and VREFN is between 100mV and VAVDD - 100mV. With

the buffer disabled, the common-mode range is between

GND and VAVDD.

Selectable buffers allow flexibility in using resistive voltage

references. For example, if a voltage reference is generated

by driving a current through a grounded reference

resistor, VREFN may be unbuffered, allowing it to be connected

directly to GND, while VREFP is buffered, helping reduce

the effect of input bias current on the reference voltage.

Low-Power Considerations

Several operating modes help to optimize power and

performance. As discussed in the Signal Path

Considerations section, applications that do not require

the gain or low input bias current available in PGA mode

can reduce supply current by 130µA by disabling the

PGA. For low-impedance sources, the input buffers

may be disabled for further power savings. Similarly, the

reference buffers may be disabled when the source

resistance is low. The modulator has a selectable dutycycle mode for low power at lower sampling rates. The IC

may be placed into sleep mode between conversions to

reduce the average power-supply current.

In addition to its normal operating mode, the modulator

can be operated in a 1/4 duty-cycle mode to reduce power

consumption for a given data rate at the expense of noise.

The noise performance of a Δ-Σ ADC generally improves

when increasing the OSR (lowering the output data rate)

because more samples of the internal modulator can be

averaged to yield one conversion result. In applications

where power consumption is critical, the improved noise

performance at low data rates may not be required. For

these applications, the internal duty-cycling mode can

yield significant power savings by periodically entering

a low-power state between conversions. In principle,

the modulator runs in normal mode with a duty cycle

of 25%, performing one “normal” conversion and then

automatically entering a low-power state for three

consecutive conversion cycles. The noise performance

in duty-cycle mode is therefore comparable to the noise

performance in normal mode at four times the data rate.

The duty-cycle mode can be selected using direct, buffered, or PGA signal paths. Neither the input buffers nor

PGA are duty cycled while in duty-cycle mode.

Select duty-cycle mode using the CONV_TYPE bits in the

CONV_START register. To minimize current consumption

in duty-cycle mode, set the signal path for an appropriate

low-power mode (see the Signal Path Considerations

section).

Sleep Mode

Sleep mode (controlled by the PD register) powers down

all analog circuitry including the internal oscillator, resulting

in 0.5µA typical current consumption. Exit sleep mode

either by writing to the PD register or (when enabled) by

using a GPIO trigger.

Table 4. Analog Supply Current Comparison for Various Operating Modes

(Typical Values Shown)

FUNCTION

SUPPLY CURRENT

INPUT RANGE

INPUT CURRENT

Normal Conversion, 60sps,

Buffers and PGA Off (Bypass Mode)

390µA

AGND - 30mV to AVDD + 30mV

1µA/V

Duty-Cycle Conversion, 15sps,

Buffers and PGA Off (Bypass Mode)

280µA

AGND - 30mV to AVDD + 30mV

1µA/V

Sleep Mode

0.5µA

Input Buffers

35µA

PGA

130µA

Reference Buffers Disabled

Reference Buffers Enabled (Each)

www.maximintegrated.com

N/A

AGND + 100mV to AVDD - 100mV

—

65nA

AGND + 100mV to AVDD - 100mV

1nA

—

AGND - 30mV to AVDD + 30mV

2.1µA/V

17.5µA

AGND + 100mV to AVDD - 100mV

61nA

Maxim Integrated │ 26

�MAX11410A

Circuit Settling Time

The input to the ADC will require some time to settle

after changing the state of the multiplexer, PGA, current

sources, and other analog components. When using the

sequencer, insert appropriate wait times when changing

the state of any of these components.

Input Multiplexer

Settling time for changes to the state of the input multiplexer

depends on several factors. These include the delay time

of the nonoverlap circuits and the on-resistance of the

multiplexer switches, but are dominated by the output

impedance of the external source, the impedance (cables,

protection components, etc.) between the external source

and the multiplexer, any input filter capacitance, the 10pF

capacitance on the input to the PGA and modulator blocks,

and whether or not the IDAC current sources or the VBIAS

source are being used. To obtain an accurate conversion,

wait until the multiplexer is fully settled before starting a

new conversion. With no added capacitance at the inputs,

the settling time after a multiplexer channel change with a

2kΩ source is typically 2µs.

PGA

PGA settling time is primarily limited by the external PGA

filter. A 100nF external capacitor across CAPP and CAPN

reduces noise by limiting the bandwidth of the PGA. This

results in a 2kHz single-pole lowpass filter at the PGA's

output. Settling to 22-bit accuracy (0.25ppm) requires

15.25 time constants or 1.21ms for a 2kHz bandwidth.

Therefore, the PGA typically dominates the settling time

of the input when changing multiplexer settings or changing

the PGA's gain.

Reference Multiplexer

Settling time for the reference input multiplexer is similar

to that of the input multiplexer but with less complexity,

as the reference multiplexer has fewer channels and

does not have the IDAC current sources or the VBIAS

source as possible inputs. The delay is still dependent on

the on-resistance of the reference multiplexer switches,

the impedance between the reference source and the

reference multiplexer, the output impedance of the

reference source, and the input capacitance of the modulator. For accurate conversions, it is important to wait until

the reference multiplexer is fully settled before starting a

new conversion.

Normally the reference should be located close to the

reference inputs, so the resistance between the source

www.maximintegrated.com

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

and the input should be negligible. If the reference

source is an active voltage reference, the source impedance

should be low enough to ignore. In some cases, the

reference source may be a resistor with a value of a

few kilohms. So long as the source resistance is less

than around 10kΩ, the settling time contribution from the

reference source resistance will be less than 1µs and can

generally be ignored.

Excitation Current Source

Enabling/disabling the current source(s) will require time

for any input capacitance to charge or discharge. This can

be especially important when external capacitors have

been added at the inputs for noise filtering.

VBIAS Source

The VBIAS source generates a bias voltage equal to

VDD/2. There are three VBIAS modes, controlled by the

VBIAS register field.

The first mode is an active bias generator featuring a

class AB output stage with a series 125kΩ resistor to

create a nominal output impedance of 125kΩ. The active

bias generator mode reduces current and channel to

channel crosstalk. In active mode, if the output is not

settled to VDD/2, the series resistor is bypassed by a

separate low-impedance class AB output stage to

decrease settling time. When the output settles to VDD/2,

the resistor is reasserted for improved noise filtering.

The second and third modes create the VBIAS with resistive

voltage-dividers to offer fixed output impedance (either

125kΩ or 20kΩ) at the expense of increased current

consumption. The 125kΩ mode offers increased supply

noise filtering at the expense of increased settling time.

The 20kΩ mode offers reduced settling time, but is higher

in current consumption and offers less supply noise filtering.

The bias voltage can be switched into the input channels

via the VBIAS_SEL register field.

Sensor Excitation Current Sources

The Matched Current Sources can be programmed to

provide 16 different levels of matched currents from

10μA to 1600μA with ±10% accuracy, 0.1% matching,

and 50ppm/°C temperature drift from -40°C to +85°C.

Either current source or both may be enabled, and each

current source may be connected to any one of the ten

analog inputs. Note that only one current source may be

connected to any input, and a current source may not be

connected to an input that has VBIAS connected to it.

Maxim Integrated │ 27

�MAX11410A

Burnout Currents

The internal, selectable 1μA, 5μA, and 10μA burnout

current source and sink may be used to detect a sensor

fault or wire break.

When enabled, the current source is connected to the

selected positive analog input (AINP) and the current sink

is connected to the selected negative analog input (AINN).

In case of an open circuit in the sensor input path, these

burn-out currents pull the positive input towards AVDD

and the negative input towards AGND, resulting in a fullscale reading. (Note that a full-scale reading may also

indicate that the sensor is overdriven or that the reference

voltage is absent.)

Calibration

The ADC can, on demand, automatically calibrate its

internal offset and gain errors as well as system offset

and gain errors, and store the calibration values in

dedicated registers. The calibration register value defaults

are zero (offset) and one (gain). Calibration values may

be calculated and stored automatically via a CAL_START

command or written directly to the registers through the

serial interface. The CAL_START command selects the

type of calibration to be performed (self-calibration, PGA

gain calibration, system calibration) and initiates the

calibration cycle. There is a separate gain calibration

register for each PGA gain.

Calibration values are applied to the conversion results

stored in the DATA registers according to the following

equation:

DATA[0:7] = SYS_GAIN_[A,B] x ( ( (Conversion SELF_OFF) x SELF_GAIN[1:128] ) - SYS_OFF_[A,B] )

where

DATA[0:7] is the ADC Data Result destination register,

selected by the DEST[3:0] register field,

Conversion is the ADC’s conversion result before calibration

results are applied,

SELF_GAIN[1:128] is the internal gain correction value

for the selected gain,

SELF_OFF is the internal offset correction value,

SYS_GAIN_[A,B] is the selected system gain correction

value, and

SYS_OFF_[A,B] is the selected system offset correction

value.

All calibration operations are performed at the filter

settings programmed into the LINEF[1:0] and RATE[3:0]

registers.

www.maximintegrated.com

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

There are two sets of system calibration registers, A and

B. Either A, B, or neither set can be applied to the ADC

conversion result, selectable by the SYSC_SEL register.

Note that calibration routines are performed using the

conversion rate, PGA gain, and filter settings in the control

registers. In general, slower conversion rates will exhibit

lower noise and will therefore produce more accurate

calibration.

Self-Calibration

In self-calibration, the required connections to zero

and full scale are made internally using the PGA gain

setting set in the GAIN register. Self-calibration is typically

sufficient to achieve offset and gain accuracy on the order

of the noise. When gain is 1, self calibration provides

20ppm of typical full-scale accuracy. The self-calibration

routine does not include external effects such as source

resistance of the signal driving the input pins, which can

change the offset and gain of the system. The range of

digital gain correction is from 0.5x to 2.0x. The range

of offset correction is ±VREF/4. The tables below show

example values for gain and offset calibration codes.

Table 5. Gain Calibration Codes

GAIN

CODE

Maximum Gain Correction

CODE DESCRIPTION

1.999999881

0xFFFFFF

1 LSB Greater Than Unity Gain

1 + 1/223

0x800001

Unity Gain

1.000000

0x800000

1 LSB Less Than Unity Gain

1 - 1/223

0x7FFFFF

Minimum Recommended Gain

Correction

0.5

0x400000

Zero Gain

0

0x000000

Table 6. Offset Calibration Codes

CODE DESCRIPTION

OFFSET

CODE

Maximum Offset

Correction

0.25VREF

0x7FFFFF

Positive 0.25LSB

(Bipolar) or 0.5LSB

(Unipolar)

0.25VREF/(223 - 1)

0x000001

Zero Offset Correction

0V

0x000000

Negative 0.25LSB

(Bipolar) or 0.5LSB

(Unipolar)

- 0.25VREF/(223 - 1)

0xFFFFFF

Minimum Offset

Correction

- 0.25VREF

(1+1/(223 - 1))

0x800000

Maxim Integrated │ 28

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

PGA Self-Calibration

To ensure the lowest possible gain error, eight separate

Self-Gain Calibration registers store the calibration

factors for each PGA gain from 1x to 128x. When

performing gain calibration, the register corresponding to

the currently selected PGA gain will be updated. Perform

a PGA gain calibration for each PGA gain setting that will

be used. Not doing so will yield errors for conversions

performed using the gains that have not been calibrated.

Self calibration will update the 1x self gain register.

System Offset and Gain Calibration

A system calibration enables calibration of system zero

scale and system full scale by presenting a zero-scale

signal or a full-scale signal to the selected input pins and

initiating a system zero-scale or system gain calibration

command. As an alternative to automatic generation of

the system calibration values, values may be directly

written to the internal calibration registers to achieve any

digital offset or scaling required. The range of digital offset

correction is ±VREF/4. The range of digital gain correction

is from 0.5x to 2.0x. The resolution of offset correction is

0.5 LSB.

Automatic system calibration requires applying the

appropriate external signals to the selected AIN inputs.

Therefore, the input multiplexer must be properly

configured prior to system calibration. Two sets of

system calibration coefficients may be created and stored

(SYS_OFF_A and SYS_GAIN_A, and SYS_OFF_B and

SYS_GAIN_B). Conversions may be performed using

either or neither of these sets of coefficients.

programming the CAL_START register with the appropriate

value. The SYS_OFF_A or SYS_OFF_B register then

updates with the value that corrects the chip zero scale.

Request a system gain calibration by presenting a system

full-scale signal level to the input pins and programming

the CAL_START register with the appropriate value. The

SYS_GAIN_A or SYS_GAIN_B register then updates with

the value that corrects the chip full scale. A system offset

calibration is required prior to system gain calibration to

ensure accurate gain calculation.

Sensitivity of Calibration Coefficients

Calibration needs to be repeated if external factors

change.

●● Both offset and gain calibration (PGA GAIN = 1)

should be performed if AVDD supply voltage changes.

●● Temperature change affects the calibration accuracy

to a much lesser extent (10°C change results in

0.2ppm offset error drift and 0.5ppm gain error drift).

●● For gain settings >1, the PGA has reduced sensitivity to supply changes compared to the modulator

(28ppm over supply range) but it is still comparable

to the Electrical Characteristics table specification.

Therefore, it is a good idea to recalibrate in the unlikely

case that the supply voltage changes from the minimum

AVDD to the maximum AVDD and vice versa. Note that

calibration is done at the currently selected data rate,

so for best results, set the data rate to a value equal

to or lower than the lowest rate that will be used for

conversions.

Request a system offset calibration by presenting a

system zero-scale signal level to the input pins and

Table 7a. Example of Self-Calibration

STEP

DESCRIPTION

REGISTER

COMMENTS

FILTER (0x08)

For best results, select a rate no faster than the rate that will be used for conversions. A slower rate will result in more accurate calibration. This will determine the

time required to execute a calibration.

1

Select Filter and

Rate

2

Select Clock

CTRL (0x11)

Source and Format.

For best results, select the clock source (internal or external) that will be used for

conversions. If external clock is selected, ensure that the external clock is operating

before beginning calibration. Format selection doesn’t affect results.

3

Start Calibration

Write XXXXX000 to CAL_START. Two conversions will execute at the rate

controlled by the FILTER register. The SELF_OFFSET and SELF_GAIN_1

registers will be updated.

www.maximintegrated.com

CAL_START

Maxim Integrated │ 29

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Table 7b. Example of PGA Gain Calibration

STEP

DESCRIPTION

REGISTER

COMMENTS

1

Select Filter and

Rate

FILTER (0x08)

For best results, select a rate no faster than the rate that will be used for conversions. A

slower rate will result in more accurate calibration. Filter selection doesn’t affect

results.

3

Select Gain and

Signal Path

PGA (0x0E)

For best results, select signal path that will be used for conversions. Gain selection

causes calibration value to be saved in the associated SELF_GAIN_ register and

applied whenever the associated gain is selected.

4

Select Clock

Source and Format

CTRL (0x11)

For best results, select the clock source (internal or external) that will be used for

conversions. If external clock is selected, ensure that the external clock is operating

before beginning calibration. Format selection does not affect results.

5

Select PGA Gain

and Start Calibration

CAL_START

Write XXXXX001 to CAL_START. One conversion will execute at the rate controlled

by the FILTER register. The SELF_GAIN__ register for the selected gain will be

updated.

Table 7c. Example of System Offset Calibration

STEP

DESCRIPTION

REGISTER

COMMENTS

1

Apply “System

Zero”

N/A

Apply the input voltage that should result in a conversion result of 0 to appropriate

analog input(s).

2

Select Filter and

Rate

CTRL (0x11)

For best results, select a rate no faster than the rate that will be used for conversions. A

slower rate will result in more accurate calibration.

3

Select Reference

Input

REF (0x09)

For best results, select a reference voltage equal to or near value that will be used

for conversions.

4

Set Input

Multiplexer

MUX_CNTRL0

(0x0B)

Select the inputs to which “system zero” is applied.

5

Select Gain and

Signal Path

PGA (0x0E)

For best results, select the signal path that will be used for conversions. Gain

selection doesn’t affect results.

6

Select Clock

Source and Format

CTRL (0x11)

For best results, select the clock source (internal or external) that will be used for

conversions. If external clock is selected, ensure that the external clock is operating

before beginning calibration. Format selection does not affect results.

7

Select System

Offset and Start

Calibration

CAL_START

Write XXXXX100 to store in SYS_OFF_A register or XXXXX110 to store in SYS_

OFF_B register.

www.maximintegrated.com

Maxim Integrated │ 30

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Table 7d. Example of System Gain Calibration

STEP

DESCRIPTION

REGISTER

COMMENTS

1

Apply “System FullN/A

Scale”

Apply an input voltage that should result in a full-scale conversion result to the

appropriate analog input(s).

2

Select Filter and

Rate

FILTER (0x08)

For best results, select a rate no faster than the rate that will be used for

conversions. A slower rate will result in more accurate calibration.

3

Select Reference

Input

CTRL (0x09)

For best results, select a reference voltage equal to or near value that will be used

for conversions.

4

Set Input

Multiplexer

MUX_CNTRL0

(0x0B)

Select inputs to which “system full-scale” is applied.

5

Select Gain and

Signal Path

PGA (0x0E)

For best results, select the signal path that will be used for conversions. Select the

gain that, when combined with the applied input voltage, yields a full-scale

conversion result .

6

Select Clock

Source and Format

CTRL (0x11)

For best results, select the clock source (internal or external) that will be used for

conversions. If external clock is selected, ensure that the external clock is

operating before beginning calibration. Format selection does not affect results.

7

Select System

Offset and Start

Calibration

CAL_START

Write XXXXX101 to store in SYS_GAIN_A register or XXXXX111 to store in SYS_

GAIN_B register.

GPIOs

Low-Side Power Switch

Two general-purpose digital IOs increase the ADC's flexibility.

When used as an output, a GPIO can be used as a

microcontroller interrupt, a control signal for a multiplexer

or multichannel switch, or a modulator clock output. GPIO

pins configured as outputs operate on the AVDD rail. Care

should be taken when using the GPIO pins in input mode

to avoid bringing the signal above VAVDD + 0.3V.

The GPIO pins can be configured to function as a lowside power switch with less than 35Ω on-resistance

(25mA switch current) to reduce system power consumption

in bridge sensor applications by powering down a bridge

circuit between conversions.

When configured as an input, a GPIO can be used as an

external clock input, an ADC start control, or a sequence

start control. When using GPIO0 as external clock input

(EXTCLK = 1), apply a 2.4576MHz clock signal to the

pin. Other frequencies can be used, but the data rate and

digital filter notch frequencies scale accordingly. GPIO

pins configured as inputs accept inputs at VDDIO levels

(not to exceed AVDD).

GP0_CTRL = 1000_0101 (switch normally open, closed

during ADC conversions)

The GPIO ports are configurable with the GP0_CTRL

and GP1_CTRL registers. The registers select whether

a GPIO will be used as an input or as an output, and if

used as an output, the output configuration (CMOS/opendrain).

www.maximintegrated.com

Select automatic low-side switch operation by setting the

GP_OSEL and GP_DIR register bits:

Manually control the low-side power switch by configuring a

GPIO as an open-drain output, and switch between state

Logic 0 and Logic 1:

GP0_CTRL = 1000_0100 (Logic 0, switch closed)

GP0_CTRL = 1000_0100 (Logic 1, switch open)

GP0_CTRL = 1000_0100 (Logic 0, switch closed)

Maxim Integrated │ 31

�MAX11410A

24-Bit, Multichannel, Low-Power

1.9ksps Delta-Sigma ADC with PGA

Conversion Data Formats

The conversion data format is selected by the FORMAT

and U_BN bits in the CTRL register, as shown in Pin

Description (continued)Figure 1a. The Unipolar/Bipolar

Select (U_BN) bit selects whether the input range is

bipolar or unipolar. A ‘1’ in this bit location selects unipolar input range and a ‘0’ selects bipolar input range. The

Format Select (FORMAT) bit controls the data format

when in bipolar mode (U_BN = 0). Unipolar data is always

in straight binary format. The FORMAT bit has no effect

in Unipolar mode (U_BN = 1). In bipolar mode, if the

FORMAT bit = 1, then the data format is offset binary. If

the FORMAT bit = 0, then the data format is two’s complement.

Digital Filter

The configurable digital filter has selectable notch frequencies (50 and 60, 50, 60, or SINC4) and selectable

data rates. The filter rejection and frequency response is

determined by the LINEF and RATE field settings in the

FILTER register.

The simultaneous 50Hz/60Hz rejection FIR filter provides

well over 90dB rejection of 50Hz and 60Hz at 16sps and

significant rejection of their harmonics. The 50Hz and

60Hz FIR filter settings provide a lower level of attenuation for those frequencies, but at a faster conversion time

than available with the simultaneous 50Hz/60Hz FIR filter.

The SINC4 setting enables a 4th-order SINC filter that

can operate at continuous data rates up to 1920sps, with

the first notch at the continuous data rate. The available

conversion rates are determined by the LINEF setting.

Note that data rate for a given RATE setting is determined

by the type of conversion selected in the CONV_START

or GP_CONV register, based on a nominal clock period

of 2.456MHz. In continuous conversion mode with LINEF

= 11, the digital filter has a settling time of 4x the sample

rate. The first sample will not be available until the expiration of that settling time. Subsequent samples will be

available at the listed sample rate. The filter sample rate

is determined by the combination of LINEF and RATE

settings, as well as the type of conversion launched by

the CONV_START command. Data rates and rejection

specifications for all settings are summarized below.

Table 8. Conversion Data Formats

MODE

BIPOLAR MODE

UNIPOLAR MODE

FORMAT

1

0

X

U_BN

0

0

1

Code Description

Input Voltage

(VAINP-VAINN)

Offset Binary

Two’s

Complement

Input Voltage

(VAINP-VAINN)