Click here for production status of specific part numbers.

MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

General Description

Features and Benefits

The MAX77813 is a high-efficiency step-up/step-down

(buck-boost) converter targeted for single-cell Li+/Li-ion

battery powered applications. The device maintains a

regulated output voltage from 2.6V to 5.14V across an

input voltage range of 2.3V to 5.5V. The device supports

up to 2A of output current in boost mode and up to 3A in

buck mode.

●● VIN Range: 2.30V to 5.5V

●● VOUT Range: 2.60V to 5.14V

(I2C Programmable in 20mV Steps)

●● Up to 2A Output Current in Boost Mode

(VIN = 3.0V, VOUT = 3.4V, ILIM = High)

●● Up to 3A Output Current in Buck Mode (ILIM = High)

●● Up to 97% Peak Efficiency

The device seamlessly transitions between buck and

boost modes. A unique control algorithm allows highefficiency, outstanding load, and line transient response.

●● SKIP Mode for Optimal Light Load Efficiency

●● 55µA (Typ) Low Quiescent Current

Dedicated enable and power-OK pins allow simple hardware control. An I2C serial interface is optionally used for

dynamic voltage scaling, system power optimization, and

fault read-back. The device supports two inductor current

limit options selected by the ILIM pin.

●● 3.4MHz High Speed I2C Serial Interface

●● Input Current Limit Selection Pin

●● Power-OK Output

●● 2.5MHz Switching Frequency

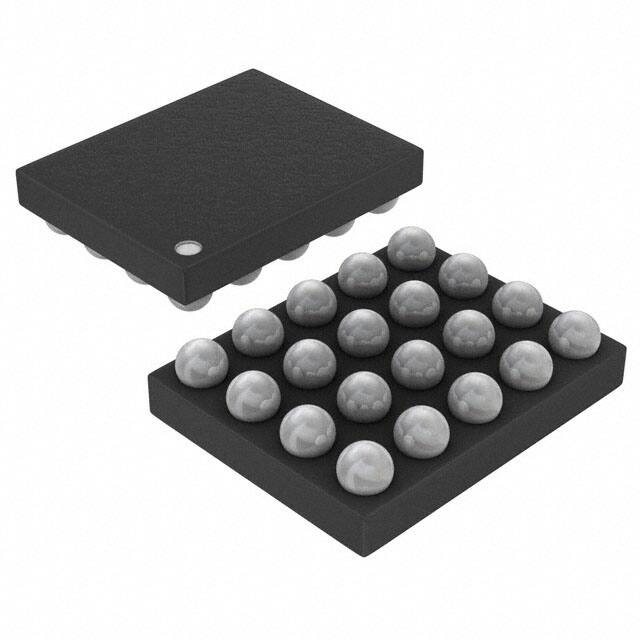

The MAX77813 is available in a 20-bump, 1.83mm x

2.13mm wafer-level package (WLP).

●● Protection Features

• Soft-Start

• Thermal Shutdown

• Overvoltage Protection

• Overcurrent Protection

Applications

●● Single-Cell Li+/Li-ion Battery Powered Devices

●● Handheld Scanners, Mobile Payment Terminals,

Security Cameras

●● AR/VR Headsets

●● 1.827mm x 2.127mm, 20-Bump WLP

Ordering Information appears at end of data sheet.

Typical Application Circuit

1μH

LX1

DC INPUT

2.3V TO 5.5V

BOOST TO BUCK

LINE TRANSIENT RESPONSE

LX2

MAX77813

IN

VSYS

10μF

1μF

OUT

OUTS

47μF

VOUT

2.6V TO 5.14V

2A (BOOST MODE)

3A (BUCK MODE)

IOUT = 1.5A

VOUT = 3.3V

VIN

PGND

SERIAL

HOST

ENABLE

BOOST

MODE

VIO

SDA

SCL

EN

POK

ILIM

POWER-OK

CURRENT LIMIT

SELECT

HIGH-EFFICIENCY BUCK-BOOST CONVERTER

WITH OPTIONAL I2C CONTROL IN TINY 20-BUMP WLP

19-8238; Rev 2; 3/19

3.4V

2.9V

500mV/div

BUCK MODE

BOOST

MODE

20mV/div

VOUT

100µs/div

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Absolute Maximum Ratings

SYS, VIO to GND..................................................-0.3V to +6.0V

IN, OUT to PGND..................................................-0.3V to +6.0V

PGND to GND.......................................................-0.3V to +0.3V

SCL, SDA to GND...................................... -0.3V to (VIO + 0.3V)

EN, ILIM, POK to GND........................... -0.3V to (VSYS + 0.3V)

FB to GND............................................... -0.3V to (VOUT + 0.3V)

LX1 to PGND..............................................-0.3V to (VIN + 0.3V)

LX2 to PGND.......................................... -0.3V to (VOUT + 0.3V)

LX1/LX2 Continuous RMS Current (Note 1).........................3.2A

Operating Junction Temperature Range........... -40°C to +125°C

Junction Temperature.......................................................+150°C

Storage Temperature Range............................. -65°C to +150°C

Soldering Temperature (Reflow).......................................+260°C

Note 1: LX1 and LX2 nodes have internal clamp diodes to PGNDBB and INBB. Applications that forward bias to these diodes should

ensure that the total power loss does not exceed the power dissipation limit of the IC package.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these

or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

device reliability.

Package Information

WLP

Package Code

W201F2+1

Outline Number

21-0771

Land Pattern Number

Refer to Application Note 1891

Thermal Resistance, Four-Layer Board:

Junction to Ambient Thermal Resistance (θJA)

55.49°C/W

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a “+”,

“#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing

pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board.

For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

www.maximintegrated.com

Maxim Integrated │ 2

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Buck-Boost Electrical Characteristics

(VSYS = VIN = +3.8V, VOUTS = VOUT = +3.3V, TJ = -40°C to +125°C, typical values are at TA ≈ TJ = +25°C, unless otherwise noted.)

(Note 4)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

5.50

V

GENERAL

Input Voltage Range

Shutdown Supply Current

Input Supply Current

VIN

2.30

ISHDN_25C

EN = low, TJ = +25°C

0.1

ISHDN_125C

EN = low, TJ = +125°C

1

IQ_SKIP

SKIP mode, no switching,

TJ = -40° to +85°C

55

IQ_PWM

FPWM mode, no load

µA

70

µA

6

mA

100

Ω

+165

°C

Active Discharge Resistance

RDISCHG

Thermal Shutdown Threshold

TSHDN

Rising, +20°C hysteresis

VOUT

I2C programmable (20mV Step)

2.60

5.14

VOUT_ACC1

FPWM mode, VOUT[6:0] = 0x28, no load,

TJ = +25°C

-1.0

+1.0

VOUT_ACC2

SKIP mode, VOUT[6:0] = 0x28,

no load, TJ = +25°C

-1.0

H-BRIDGE

Output Voltage Range

Output Voltage Accuracy

V

%

+4.5

Line Regulation

VIN = 2.63V to 5.5V

0.200

%/V

Load Regulation

(Note 5)

0.125

%/A

Line Transient Response

VOS1

VUS1

IOUT = 1.0A, VIN changes from 3.4V to

2.9V in 25µs (20mV/µs),

L = 1µH, COUT_NOM = 47µF (Note 5)

50

mV

Load Transient Response

VOS2

VUS2

VIN = 3.4V, IOUT changes from 10mA to

1.5A in 15µs, L = 1µH, COUT_NOM = 47µF

(Note 5)

50

mV

Output Voltage Ramp-Up

Slew Rate

BB_RU_SR = 0

20

BB_RU_SR = 1

40

Output Voltage Ramp-Down

Slew Rate

BB_RD_SR = 0

5

BB_RD_SR = 1

10

mV/µs

mV/µs

Typical Condition Efficiency

ηTYP

IOUT = 100mA (Note 5)

95

%

Peak Efficiency

ηPK

(Note 5)

97

%

LX1/2 Current Limit

ILIM_LX

ILIM = high

3.70

4.50

5.70

ILIM = low

1.2

1.80

2.65

A

High-Side PMOS ON

Resistance

RDSON(PMOS)

ILX = 100mA per switch

40

mΩ

Low-Side NMOS ON

Resistance

RDSON(NMOS)

ILX = 100mA per switch

55

mΩ

Switching Frequency

fSW

PWM mode, TJ = +25°C

www.maximintegrated.com

2.25

2.50

2.75

MHz

Maxim Integrated │ 3

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Buck-Boost Electrical Characteristics (continued)

(VSYS = VIN = +3.8V, VOUTS = VOUT = +3.3V, TJ = -40°C to +125°C, typical values are at TA ≈ TJ = +25°C, unless otherwise noted.)

(Note 4)

PARAMETER

Turn-On Delay Time

SYMBOL

LX1, LX2 Leakage Current

MIN

TYP

From EN asserting to LX switching with

bias ON

100

IOUT = 10mA, ILIM = high

120

IOUT = 10mA, ILIM = low

800

0A < IOUT < 2000mA

16

ILK_25C

VLX1/2 = 0V or 5.5V, VOUT = 5.5V,

VSYS = VIN = 5.5V, TJ = +25°C

0.1

ILK_125C

VLX1/2 = 0V or 5.5V, VOUT = 5.5V,

VSYS = VIN = 5.5V, TJ = +125°C

0.2

Rising threshold

80

Falling threshold

75

tON_DLY

Soft-Start Timer

Minimum Effective Output

Capacitance

CONDITIONS

tSS

CEFF(MIN)

MAX

UNITS

µs

µs

µF

1

µA

POWER-OK COMPARATOR

Output POK Trip Level

%

VSYS UNDERVOLTAGE LOCKOUT

VSYS Undervoltage Lockout

Threshold

VUVLO_R

VSYS rising

VUVLO_F

VSYS falling

2.375

2.50

2.625

2.05

V

LOGIC AND CONTROL INPUTS

Input Low Level

VIL

EN, ILIM, VSYS = 3.8V, TJ = +125°C

Input High Level

VIH

EN, ILIM, VSYS = 3.8V, TJ = -40°C

POK Output Low Voltage

VOL

ISINK = 1mA

IOZH_25C

TJ = +25°C

IOZH_125C

TJ = +125°C

POK Output High Leakage

0.4

1.2

V

V

0.4

-1

+1

0.1

V

µA

INTERNAL PULLDOWN RESISTANCE

EN

RPD

Pulldown resistance to GND

400

800

1600

kΩ

Note 2: Limits are 100% production tested at TJ = +25°C. The device is tested under pulsed load conditions such that TJ ≈ TA.

Limits over the operating temperature range are guaranteed through correlation using statistical quality control methods.

Note 3: Guaranteed by design. Not production tested.

www.maximintegrated.com

Maxim Integrated │ 4

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

I2C Electrical Characteristics

(VSYS = 3.8V, VVIO = 1.8V, TJ = -40°C to +125°C, typical values are at TA ≈ TJ = +25°C, unless otherwise noted.) (Note 4)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

3.6

V

POWER SUPPLY

VIO Voltage Range

VVIO

1.7

SCL, SDA Input High Voltage

VIH

0.7 x

VIO

SCL, SDA Input Low Voltage

VIL

SDA AND SCL I/O STAGES

SCL, SDA Input Hysteresis

0.3 x

VIO

0.05 x

VIO

VHYS

SCL, SDA Input Current

II

SDA Output Low Voltage

VOL

SCL, SDA Input Capacitance

CI

Output Fall Time from VVIO to

0.3 x VVIO

tOF

V

VVIO = 3.8V

-10

ISINK = 20mA

V

V

+10

µA

0.4

V

10

pF

120

ns

1000

kHz

I2C-COMPATIBLE INTERFACE TIMING (STANDARD, FAST, AND FAST-MODE PLUS) (Note 5)

Clock Frequency

Hold Time (REPEATED)

START Condition

fSCL

tHD;STA

0.26

µs

SCL Low Period

tLOW

0.5

µs

SCL High Period

tHIGH

0.26

µs

Setup Time REPEATED

START Condition

tSU_STA

0.26

µs

DATA Hold Time

tHD_DAT

0

µs

DATA Setup Time

tSU_DAT

50

ns

Setup Time for STOP

Condition

tSU_STO

0.26

µs

Bus-Free Time Between

STOP and START

tBUF

0.5

µs

Capacitive Load for Each

Bus Line

CB

Maximum Pulse Width

of Spikes that must be

suppressed by the input filter

www.maximintegrated.com

550

50

pF

ns

Maxim Integrated │ 5

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

I2C Electrical Characteristics (continued)

(VSYS = 3.8V, VVIO = 1.8V, TJ = -40°C to +125°C, typical values are at TA ≈ TJ = +25°C, unless otherwise noted.) (Note 4)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

3.4

MHz

I2C-COMPATIBLE INTERFACE TIMING (HIGH-SPEED MODE, CB = 100pF) (Note 5)

Clock Frequency

fSCL

Setup Time REPEATED

START Condition

tSU_STA

160

ns

Hold Time (REPEATED)

START Condition

tHD_STA

160

ns

CLK Low Period

tLOW

160

ns

CLK High Period

tHIGH

60

ns

DATA Setup Time

tSU_DAT

10

DATA Hold Time

tHD_DAT

ns

35

ns

SCL Rise Time (Note 3)

tRCL

TJ = +25°C

10

40

ns

Rise Time of SCL Signal after

REPEATED START Condition

and after Acknowledge Bit

tRCL1

TJ = +25°C

10

80

ns

SCL Fall Time

tFCL

TJ = +25°C

10

40

ns

SDA Rise Time

tRDA

TJ = +25°C

80

ns

SDA Fall Time

tFDA

TJ = +25°C

80

ns

Setup Time for STOP

Condition

Bus Capacitance

tSU_STO

160

ns

CB

100

Maximum Pulse Width

of Spikes that must be

suppressed by the input filter

10

pF

ns

I2C-COMPATIBLE INTERFACE TIMING (HIGH-SPEED MODE, CB = 400pF) (Note 5)

Clock Frequency

fSCL

1.7

MHz

Setup Time REPEATED

START Condition

tSU_STA

160

ns

Hold Time (REPEATED)

START Condition

tHD_STA

160

ns

tLOW

320

ns

SCL High Period

tHIGH

120

ns

DATA Setup Time

tSU_DAT

10

ns

DATA Hold Time

tHD_DAT

SCL Low Period

www.maximintegrated.com

75

ns

Maxim Integrated │ 6

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

I2C Electrical Characteristics (continued)

(VSYS = 3.8V, VVIO = 1.8V, TJ = -40°C to +125°C, typical values are at TA ≈ TJ = +25°C, unless otherwise noted.) (Note 4)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SCL Rise Time

tRCL

TJ = +25°C

20

80

ns

Rise Time of SCL Signal after

REPEATED START Condition

and after Acknowledge Bit

tRCL1

TJ = +25°C

20

160

ns

SCL Fall Time

tFCL

TJ = +25°C

20

80

ns

SDA Rise Time

tRDA

TJ = +25°C

160

ns

SDA Fall Time

tFDA

TJ = +25°C

160

ns

Setup Time for STOP

Condition

tSU_STO

Bus Capacitance

CB

Maximum Pulse Width

of Spikes that Must be

Suppressed by the Input Filter

tSP

160

ns

400

10

pF

ns

Note 4: Limits are 100% production tested at TJ = +25°C. The device is tested under pulsed load conditions such that TJ ≈ TA.

Limits over the operating temperature range are guaranteed through correlation using statistical quality control methods.

Note 5: Guaranteed by design. Not production tested.

www.maximintegrated.com

Maxim Integrated │ 7

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Typical Operating Characteristics

(VSYS = 3.8V, VOUT = 3.3V, IOUT = 0A, FPWM = 0, TA = +25°C, unless otherwise noted.)

QUIESCENT CURRENT vs.

SUPPLY VOLTAGE

70

toc01

SHUTDOWN CURRENT vs.

SUPPLY VOLTAGE

2.0

toc02

100

VOUT = 2.8V

VOUT = 3.3V

VOUT = 5V

50

45

40

1.5

80

TA = +85°C

1.0

0.5

TA = +25°C

0.0

TA = -40°C

2

3

4

5

-0.5

6

2

3

SUPPLY VOLTAGE (V)

toc04

5

50

40

30

VIN = 3.8V (FPWM = 1)

20

toc05

70

60

50

40

30

VIN = 3.8V (FPWM = 1)

0.1

1

LOAD REGULATION

2.8V OUTPUT

2.83

2.82

VIN = 3V

VIN = 3.8V

VIN = 4.5V

2.81

2.80

2.79

0.01

0.1

2.77

1

0.0

0.5

1.0

1.5

LOAD (A)

LOAD (A)

LOAD (A)

LOAD REGULATION

3.3V OUTPUT

LOAD REGULATION

5V OUTPUT

LINE REGULATION

2.8V OUTPUT

toc07

5.16

5.12

3.36

5.10

3.35

OUTPUT VOLTAGE (V)

5.14

3.37

VIN = 3V

VIN = 3.3V

VIN = 3.8V

VIN = 4.5V

3.34

3.33

3.32

5.04

5.02

5.00

4.98

1.0

LOAD (A)

www.maximintegrated.com

1.5

2.0

VIN = 3V

VIN = 3.8V

VIN = 4.5V

5.06

3.30

0.5

toc08

4.96

2.80

2.0

toc09

2.79

5.08

3.31

toc06

2.78

0

0.001

1

3.38

0.0

0.01

2.84

OUTPUT VOLTAGE (V)

3.39

0.1

VIN = 3.8V (FPWM = 1)

2.85

10

0.01

30

LOAD (A)

VIN = 3V

VIN = 3.8V

VIN = 4.5V

20

10

0

0.001

40

0

0.001

6

OUTPUT VOLTAGE (V)

60

80

EFFICIENCY (%)

EFFICIENCY (%)

4

90

VIN = 3V

VIN = 3.3V

VIN = 3.8V

VIN = 4.5V

70

50

10

EFFICIENCY vs. LOAD

5V OUTPUT

100

90

80

60

SUPPLY VOLTAGE (V)

EFFICIENCY vs. LOAD

3.3V OUTPUT

100

VIN = 3V

VIN = 3.8V

VIN = 4.5V

70

20

35

OUTPUT VOLTAGE (V)

EFFICIENCY (%)

55

SHUTDOWN CURRENT (µA)

QUIESCENT CURRENT (µA)

60

3.29

toc03

90

65

30

EFFICIENCY vs. LOAD

2.8V OUTPUT

2.78

IOUT = 500mA

IOUT = 1A

IOUT = 2A

2.77

2.76

2.75

0.0

0.5

1.0

LOAD (A)

1.5

2.0

2.74

2.5

3.5

4.5

5.5

SUPPLY VOLTAGE (V)

Maxim Integrated │ 8

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Typical Operating Characteristics (continued)

(VSYS = 3.8V, VOUT = 3.3V, IOUT = 0A, FPWM = 0, TA = +25°C, unless otherwise noted.)

LINE REGULATION

3.3V OUTPUT

3.32

toc10

5.04

3.30

IOUT = 500mA

IOUT = 1A

IOUT = 2A

3.29

3.28

3.27

5.00

4.98

IOUT = 500mA

IOUT = 1A

IOUT = 2A

4.96

4.94

2.5

3.5

4.5

5.5

4.92

2.5

3.5

SUPPLY VOLTAGE (V)

4.5

5.5

SUPPLY VOLTAGE (V)

MAXIMUM OUTPUT CURRENT vs.

SUPPLY VOLTAGE

4.5

STARTUP WAVEFORM

3.3V OUTPUT

toc12

toc13

VOUT = 2.8V

4.0

2V/div

VEN

VOUT = 3.3V

3.5

OUTPUT CURRENT (A)

toc11

5.02

OUTPUT VOLTAGE (V)

OUTPUT VOLTAGE (V)

3.31

3.26

LINE REGULATION

5V OUTPUT

3.0

VOUT

VOUT = 5V

2.5

2V/div

EN = 1

2.0

200mV/div

VLX

1.5

1.0

IIN

0.5

0.0

ILIM = HIGH

2

3

4

5

2A/div

VIN = 3.8V

6

40µs/div

SUPPLY VOLTAGE (V)

LOAD TRANSIENT RESPONSE

2.8V OUTPUT

LOAD TRANSIENT RESPONSE

3.3V OUTPUT

toc14

toc15

1A

1A

500mA/div

IOUT

500mA/div

IOUT

10mA

10mA

VOUT

VOUT

SLEW RATE = 0.99A/15µs

100µs/div

www.maximintegrated.com

100mV/div

100mV/div

SLEW RATE = 0.99A/15µs

100µs/div

Maxim Integrated │ 9

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Typical Operating Characteristics (continued)

(VSYS = 3.8V, VOUT = 3.3V, IOUT = 0A, FPWM = 0, TA = +25°C, unless otherwise noted.)

LOAD TRANSIENT RESPONSE

5V OUTPUT

LINE TRANSIENT RESPONSE

2.8V OUTPUT

toc16

toc17

IOUT = 1.5A

1A

3.4V

500mA/div

IOUT

10mA

VIN

VOUT

2.9V

500mV/div

100mV/div

VOUT

20mV/div

SLEW RATE = 20mV/µs

SLEW RATE = 0.99A/15µs

100µs/div

100µs/div

LINE TRANSIENT RESPONSE

5V OUTPUT

BOOST TO BUCK

LINE TRANSIENT RESPONSE

toc18

IOUT = 1.5A

IOUT = 1.5A

VOUT = 3.3V

3.9V

VIN

3.4V

500mV/div

VOUT

20mV/div

VIN

toc19

3.4V

2.9V

500mV/div

VOUT

20mV/div

SLEW RATE = 20mV/µs

SLEW RATE = 20mV/µs

100µs/div

100µs/div

SWITCHING WAVEFORM

3.3V OUTPUT

OUTPUT RIPPLE IN SKIP MODE

3.3V OUTPUT (IOUT = 100mA)

toc20

IOUT = 1A

toc21

IOUT = 100mA

1V/div

VLX

20mV/div

VOUT

FSW = 2.5MHz

100µs/div

www.maximintegrated.com

4µs/div

Maxim Integrated │ 10

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Typical Operating Characteristics (continued)

(VSYS = 3.8V, VOUT = 3.3V, IOUT = 0A, FPWM = 0, TA = +25°C, unless otherwise noted.)

OUTPUT RIPPLE IN PWM

3.3V OUTPUT (IOUT = 1A)

SHORT-CIRCUIT HICCUP AND RECOVERY

3.3V OUTPUT (ILIM = LOW)

toc22

toc23

SHORT APPLIED

IOUT = 1A

VOUT

10mV/div

VOUT

2V/div

RECOVERY/

SHORT REMOVED

HICCUP/RETRY

ILX

1A/div

20µs/div

20ms/div

SHORT-CIRCUIT AND RECOVERY

3.3V OUTPUT (ILIM = HIGH)

toc24

SHORT APPLIED

VOUT

RECOVERY/

SHORT REMOVED

2V/div

HICCUP/RETRY

ILX

2A/div

20ms/div

www.maximintegrated.com

Maxim Integrated │ 11

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Bump Configuration

TOP VIEW

(BUMP SIDE DOWN)

1

2

3

4

5

A

VSYS

ILIM

GND

SDA

SCL

B

OUTS

POK

GND

EN

VIO

C

OUT

LX2

GND

LX1

IN

D

OUT

LX2

GND

LX1

IN

+

20 WLP

(2.13mm x 1.83mm, 0.4mm PITCH)

Bump Description

PIN

NAME

A1

VSYS

System (Battery) Voltage Input. Bypass to GND with a 1µF capacitor.

A2

ILIM

Current Limit Selection Input. Connect to GND to set ILIM_BB to 1.8A. Connect to VVIO to set

ILIM_BB to 4.5A. Do not leave this pin unconnected.

A3, B3

GND

Ground. Connect to PGND on the PCB. See the PCB Layout Guidelines.

A4

SDA

I2C Serial Interface Data. This pin requires a pullup resistor (1.5k to 2.2k) to VIO.

Connect to GND if not used.

A5

SCL

I2C Serial Interface Clock. This pin requires a pullup resistor (1.5k to 2.2k) to VIO.

Connect to GND if not used.

B1

OUTS

B2

POK

B4

EN

Active-High Enable Input. This pin has an 800kΩ internal pulldown to GND.

B5

VIO

I2C Supply Voltage Input. Bypass to GND with a 0.1µF capacitor. Connect to GND if not used.

C1, D1

OUT

Output. Bypass to PGND with a 10V 47µF ceramic capacitor.

C2, D2

LX2

Switching Node 2

C3, D3

PGND

C4, D4

LX1

C5, D5

IN

www.maximintegrated.com

FUNCTION

Output sense.

Open-Drain Power-OK Output. Asserts high (high-Z) when buck-boost output reaches 80% of target.

Power Ground. Connect to GND on the PCB. See the PCB Layout Guidelines.

Switching Node1

Input. Bypass to PGND with a 10V 10µF capacitor.

Maxim Integrated │ 12

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

LX1

IN

1µH

LX2

HS1

HS2

OUT

10µF

CS

LS1

DRIVER

47µF

CS

LS2

DRIVER

PGND

MAX77813

CONTROL LOGIC

OUTS

ETR

OSC

COMP.

CF

R1

R2

PROT.

REF

SLOPE COMP.

PSM

REGISTER

CONTROL

Figure 1. Simplified Block Diagram

www.maximintegrated.com

Maxim Integrated │ 13

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Detailed Description

The MAX77813 is a synchronous step-up/down (buckboost) DC-DC converter with integrated switches. The

buck-boost operates on a supply voltage between 2.3V

and 5.5V. Output voltage is configurable through I2C from

2.60V to 5.14V in 20mV steps. Factory-default startup

voltage options of 3.3V and 3.4V are available (see the

Ordering Information table). The ILIM pin sets the buckboost switch current capacity.

●● Strap ILIM high to set 4.5A (typ) switch current. This

configuration supports up to 2A out in boost mode

and up to 3A out in buck mode.

●● Strap ILIM low to set 1.8A (typ) switch current. This

configuration supports up to 650mA in boost mode

and up to 800mA in buck mode.

Buck-Boost Control Scheme

The buck-boost converter operates using a 2.5MHz fixedfrequency pulse-width modulated (PWM) control scheme

with current-mode compensation. The buck-boost utilizes

an H-bridge topology using a single inductor and output

capacitor.

The H-bridge topology has three switching phases. See

Figure 2 for details.

●● Φ1 Switch period (Phase 1: HS1 = ON, LS2 = ON)

stores energy in the inductor. Inductor current ramps

up at a rate proportional to the input voltage divided by

inductance: VIN / L.

●● Φ2 Switch period (Phase 2: HS1 = ON, HS2 = ON)

ramps inductor current up or down depending on the

differential voltage across the inductor: (VIN - VOUT) / L.

●● Φ3 Switch period (Phase 3: LS1 = ON, HS2 = ON)

ramps inductor current down at a rate proportional to

the output voltage divided by inductance: (-VOUT / L).

Boost operation (VIN < VOUT) utilizes phase 1 and phase

2 within a single clock period. See the representation of

inductor current waveform for boost mode operation in

Figure 2.

Buck operation (VIN > VOUT) utilizes phase 2 and phase

3 within a single clock period. See the representation of

inductor current waveform for buck mode operation in

Figure 2.

BOOST OPERATION

BUCK-BOOST H-BRIDGE

TOPOLOGY

IN

Ф2

OUT

Ф2

Ф3

Ф3

HS1

Ф2

Charge/Discharge L

TSW

HS2

TSW

CLK

Ф3

Discharge L

CLK

BUCK OPERATION

L

LS1

CLK

LS2

Ф2

Ф1

Ф1

Charge L

Ф1

TSW

CLK

Ф2

TSW

CLK

CLK

Figure 2. Buck-Boost Block Diagram

www.maximintegrated.com

Maxim Integrated │ 14

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Enable Control (EN)

Raise the EN pin voltage above VIH threshold to enable

the buck-boost output. Lower EN below VIL threshold to

disable. EN has an internal 800kΩ (typ) pulldown resistor

to GND. Clear the EN bit using the I2C interface to disable

the internal pulldown (making EN high-impedance). The

EN_PD bit reset value is 1 (pulldown enabled). Therefore,

the internal pulldown resistor is present whenever the

MAX77813 starts up.

After the initial buck-boost startup, clear the EN bit

through I2C to disable the buck-boost output. Table 1

details the interaction between the EN pin and the EN bit.

Provide a valid VIO and set the EN pin logic-high to

enable the I2C serial interface. Serial reads and writes to

the EN bit may happen only while VIO is valid and EN is

logic-high. Lowering EN logic-low disables the buck-boost

(regardless of EN) and causes all registers to reset to

default values.

Table 1. EN Logic

EN

EN BIT

I2C SERIAL

INTERFACE

BUCK-BOOST

OUTPUT

Low

X

Disabled

Disabled

High

0

Enabled

Disabled

High

1 (default)

Enabled

Enabled

Peak Inductor Current

Limit Selection (ILIM)

Select the buck-boost’s cycle-by-cycle inductor current

limit (ILIM_LX) with the ILIM pin. Connect ILIM to VVIO

to set ILIM_LX to 4.5A (typ). Connect ILIM to GND to set

ILIM_LX to 1.8A (typ).

The device automatically changes ILIM_LX during the

following events:

●● Soft-start (ILIM_LX is temporarily reduced.). See SoftStart for details.

●● Burst mode (ILIM_LX is temporarily increased.). See

Burst Mode (Enhanced Load Response) for details.

Always drive the ILIM pin logic-high or low. Do not leave

ILIM unconnected.

Soft-Start

The device implements a soft-start by reducing the peak

inductor current limit (ILIM_LX) for a fixed time. The softstart time begins immediately after the startup delay

(tON_DLY). See Table 2 for details.

ILIM_LX reduces (according to Table 2) for tSS after the

buck-boost enables through either the EN pin or EN bit.

Reducing the inductor current limit during startup controls

inrush current from the supply input (IIN) and prevents

droop caused by upstream source impedance.

EN

VOUT

TON_DLY

TSS

ILIM_NORMAL

ILIM_SS

IL

Figure 3. Soft-Start

www.maximintegrated.com

Maxim Integrated │ 15

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Table 2. Soft-Start ILIM

ILIM (PIN)

I LIM_LX AFTER

SOFT-START (A)

I LIM_LX DURING

SOFT-START (A)

tSS SOFT-START TIME

(µS)

High

4.5

1.8

120

Low

1.8

1.8

800

Burst Mode (Enhanced Load Response)

The device implements a burst mode to service shortduration heavy load transients (burst loads). A summary

of burst mode operation follows:

●●

If a heavy load transient happens that requires peak

inductor current > ILIM_LX to maintain regulation,

then the buck-boost temporarily increases the peak

inductor current limit from ILIM_LX to ILIM_LX_HIGH.

(See Table 3.)

●●

If the heavy load causes peak inductor current >

ILIM_LX for longer than 800µs(typ), then burst mode

deactivates and peak inductor current limit returns to

ILIM_LX.

Table 3. ILIM Levels

ILIM (PIN)

INDUCTOR CURRENT LIMIT DURING

NORMAL OPERATION

ILIM_LX (A)

INDUCTOR CURRENT LIMIT DURING

BURST MODE

ILIM_LX_HIGH (A)

High

4.5

5.5

Low

1.8

2.3

EN

VOUT

TON_DLY

TSS

ILIM_LX

ILIM_LX_SS

IL

Figure 4. Short Circuit Waveform

www.maximintegrated.com

Maxim Integrated │ 16

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Power-OK (POK) Output

The device features an open-drain POK output to monitor

the output voltage. POK requires an external pullup resistor (typically 10kΩ to 100kΩ).

POK is active-high by default. Use the POK_POL bit to

change the POK polarity to active-low. See the Register

Map for details.

While POK_POL = 1 (active-high, default state), POK

goes high (high-impedance) after the buck-boost output

increases above 80% of the target regulation voltage.

POK goes low when the output drops below 75% of the

target or when the buck-boost is disabled.

Output Voltage Selection and

Slew Rate Control

Write the VOUT[6:0] bitfield through I2C to configure the

target output voltage (VOUT) between 2.60V and 5.14V

in 20mV steps. The default value of VOUT[6:0] is factoryprogrammable. See the Ordering Information for the

default VOUT associated with each orderable part number. Overwriting the default value through I2C sets a new

target VOUT until registers reset.

Changing the VOUT[6:0] bitfield while the buck-boost

output is enabled causes the device to respond in the

following way:

●●

VOUT ramps up at a rate set by RU_SR (20mV/μs or

40mV/μs) when the VOUT target is increased.

●●

VOUT ramps down at a rate set by RD_SR (5mV/μs

or 10mV/μs) when the VOUT target is decreased.

See the Register Map for details about the RU_SR and

RD_SR bits.

Output Overvoltage Protection (OVP)

The device has an internal output overvoltage protection

(OVP) circuit which monitors VOUT for overvoltage faults.

The buck-boost disables if the output exceeds the overvoltage threshold set by the OVP_TH[1:0] bitfield.

Disable OVP by programming OVP_TH[1:0] to 0b00

using I2C. The default OVP threshold is 0b11 (120% of

the target VOUT).

The OVP status bit continuously mirrors the status of the

OVP circuit. See the Register Map for details.

Thermal Shutdown

The device has an internal thermal protection circuit

which monitors die temperature. The buck-boost disables

if the die temperature exceeds TSHDN (165°C typ). The

buck-boost enables again after the die temperature cools

by approximately 20°C.

The TSHDN status bit continuously mirrors the status of

the thermal protection circuit. See the Register Map for

details.

I2C Serial Interface

The device features a revision 3.0 I2C-compatible, 2-wire

serial interface consisting of a bidirectional serial data line

(SDA) and a serial clock line (SCL). The MAX77813 is a

slave-only device that that relies on an external bus master to generate SCL. SCL clock rates from 0Hz to 3.4MHz

are supported. I2C is an open-drain bus, and therefore,

SDA and SCL require pullups (500Ω or greater).

The device’s I2C communication controller implements

7-bit slave addressing. An I2C bus master initiates communication with the slave by issuing a START condition

followed by the slave address. The slave address of the

device is shown in Table 4.

The device uses 8-bit registers with 8-bit register addressing. They support standard communication protocols: (1)

Writing to a single register (2) Writing to multiple sequential registers with an automatically incrementing data

pointer (3) Reading from a single register (4) Reading

from multiple sequential registers with an automatically incrementing data pointer. For additional information on the I2C protocols, refer to the MAX77813 I2C

Implementer’s Guide and/or the I2C specification that is

freely available on the internet.

Table 4. I2C Slave Address

ILIM (PIN)

INDUCTOR CURRENT LIMIT DURING

NORMAL OPERATION

ILIM_LX (A)

INDUCTOR CURRENT LIMIT DURING

BURST MODE

ILIM_LX_HIGH (A)

High

4.5

5.5

Low

1.8

2.3

www.maximintegrated.com

Maxim Integrated │ 17

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Applications Information

Output Capacitor Selection

Inductor Selection

Choose a 1μH inductor with a saturation current of 7A or

higher for ILIM = HIGH and a saturation current of 3.39A

or higher for ILIM = LOW.

Table 5 lists recommended inductors for the MAX77813.

Always choose the inductor carefully by consulting the

manufacturer’s latest released data sheet.

Input Capacitor Selection

Choose the input capacitor (CIN) to be a 10μF ceramic

capacitor that maintains at least 2μF of effective capacitance at its working voltage. Larger values improve the

decoupling of the buck-boost. CIN reduces the current

peaks drawn from the battery or input power source and

reduces switching noise in the device. Ceramic capacitors with X5R or X7R dielectric are highly recommended

due to their small size, low ESR, and small temperature

coefficients.

All ceramic capacitors derate with DC bias voltage

(effective capacitance goes down as DC bias goes up).

Generally, small case size capacitors derate heavily compared to larger case sizes (0603 case size performs better than 0402). Consider the effective capacitance value

carefully by consulting the manufacturer’s data sheet.

Sufficient output capacitance (COUT) is required to keep

the output voltage ripple small and the regulation loop

stable. Choose the effective COUT to be 16uF, minimum.

Considering the DC bias characteristic of ceramic capacitors, a 47μF 10V capacitor is recommended for most

applications.

Effective COUT is the actual capacitance value seen by

the buck-boost output during operation. Choose effective COUT carefully by considering the capacitor’s initial

tolerance, variation with temperature, and derating with

DC bias.

Ceramic capacitors with X5R or X7R dielectric are highly

recommended due to their small size, low ESR, and small

temperature coefficients. All ceramic capacitors derate

with DC bias voltage (effective capacitance goes down as

DC bias goes up). Generally, small case size capacitors

derate heavily compared to larger case sizes (0603 case

size performs better than 0402). Consider the effective

capacitance value carefully by consulting the manufacturer’s data sheet.

Table 5. Suggested Inductors for Buck Boost

MFGR.

SERIES

NOMINAL

INDUCTANCE

[µH]

TYPICAL DC

RESISTANCE

[mΩ]

CURRENT

RATING [A]

-30% (ΔL/L)

CURRENT

RATING [A]

ΔT = 40°C RISE

DIMENSIONS

LxWxH

[mm]

ILIM

SETTING

TDK

TFM201610GHM 1R0MTAA

1.0

50

3.8

3.0

2.0 x 1.6 x 1.0

Low

TOKO

DFE322512C

1.0

34

4.6

3.7

3.2 x 2.5 x 1.2

Low

Coilcraft

XAL4020-102MEB

1.0

13

8.7

9.6

4.0 x 4.0 x 2.1

High

www.maximintegrated.com

Maxim Integrated │ 18

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Serial Interface

Figure 5 shows an example of a typical I2C system. A

device on I2C bus that sends data to the bus in called

a “Transmitter”. A device that receives data from the

bus is called a “Receiver”. The device that initiates a

data transfer and generates SCL clock signals to control

the data transfer is a “Master”. Any device that is being

addressed by the master is considered a “Slave”. When

the MAX77813 I2C-compatible interface is operating, it is

a slave on the I2C bus and it can be both a transmitter

and a receiver.

The I2C-compatible 2-wire serial interface is used for

regulator on/off control, setting output voltages, and other

functions. See the Register Map for details.

The I2C serial bus consists of a bidirectional serial-data

line (SDA) and a serial clock (SCL). I2C is an open-drain

bus. SDA and SCL require pullup resistors (500Ω or

greater). Optional 24Ω resistors in series with SDA and

SCL help to protect the device inputs from high voltage

spikes on the bus lines. Series resistors also minimize

crosstalk and undershoot on the bus lines.

Bit Transfer

One data bit is transferred for each SCL clock cycle. The

data on SDA must remain stable during the high portion of

SCL clock pulse. Changes in SDA while SCL is high are

control signals (START and STOP conditions).

System Configuration

The I2C bus is a multi-master bus. The maximum number

of devices that can attach to the bus is only limited by bus

capacitance.

SDA

SCL

MASTER

TRANSMITTER /

RECEIVER

SLAVE

RECEIVER

SLAVE

TRANSMITTER

SLAVE

TRANSMITTER /

RECEIVER

MASTER

TRANSMITTER /

RECEIVER

Figure 5. Functional Logic Diagram for Communications Controller

SDA

SCL

DATA LINE STABLE DATA VALID

CHANGE OF DATA

ALLOWED

Figure 6. I2C Bit Transfer

www.maximintegrated.com

Maxim Integrated │ 19

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

START and STOP Conditions

interface until the next START condition, minimizing digital

noise and feed-through.

high. A master device initiates communication by issuing

a START condition. A START condition is a high-to-low

transition on SDA with SCL high. A STOP condition is a

low-to-high transition on SDA, while SCL is high.

Acknowledged

When I2C serial interface is inactive, SDA and SCL idle

A START condition from the master signals the beginning

of a transmission to the device. The master terminates

transmission by issuing a NOT-ACKNOWLEDGE followed by a STOP condition.

A STOP condition frees the bus. To issue a series of commands to the slave, the master may issue REPEATED

START (Sr) commands instead of a STOP command

in order to maintain control of the bus. In general, a

REPEATED START command is functionally equivalent

to a regular START command.

When a STOP condition or incorrect address is detected,

the device internally disconnects SCL from the I2C serial

S

Sr

The I2C slave address of the device is shown in Table 6.

SDA

Table 6. I2C Slave Address

tSU;STO

SCL

tHD;STA

Monitoring the acknowledge bits allows for detection

of unsuccessful data transfers. An unsuccessful data

transfer occurs if a receiving device is busy or if a system

fault has occurred. In the event of an unsuccessful data

transfer, the bus master should reattempt communication

at a later time.

Slave Address

P

tSU;STA

Both the I2C bus master and the device (slave) generate

acknowledge bits when receiving data. The acknowledge

bit is the last bit of each nine-bit data packet. To generate an ACKNOWLEDGE (A), the receiving device must

pull SDA low before the rising edge of the acknowledgerelated clock pulse (ninth pulse) and keep it low during

the high period of the clock pulse. To generate a NOTACKNOWLEDGE (nA), the receiving device allows SDA

to be pulled high before the rising edge of the acknowledge-related clock pulse and leaves it high during the

high period of the clock pulse.

SLAVE ADDRESS SLAVE ADDRESS SLAVE ADDRESS

(7 BIT)

(WRITE)

(READ)

tHD;STA

001 1000

0x30 (0011 0000)

0x31 (0011 0001)

Figure 7. START and STOP Conditions

S

SDA

0

0

1

1

0

0

0

R/nW

A

ACKNOWLEDGE

SCL

1

2

3

4

5

6

7

8

9

Figure 8. Slave Address Byte Example

www.maximintegrated.com

Maxim Integrated │ 20

�MAX77813

Clock Stretching

In general, the clock signal generation for the I2C bus is

the responsibility of the master device. I2C specification

allows slow slave devices to alter the clock signal by

holding down the clock line. The process in which a slave

device holds down the clock line is typically called clock

stretching. The device does not use any form of clock

stretching to hold down the clock line.

General Call Address

The device does not implement I2C specification “General

Call Address.” If the device sees “General Call Address

(00000000b)” it does not issue an ACKNOWLEDGE (A).

Communication Speed

The device provides I2C 3.0-compatible (3.4MHz) serial

interface.

●● I2C Revision 3 Compatible Serial Communications

Channel

• 0Hz to 100kHz (Standard mode)

• 0Hz to 400kHz (Fast mode)

• 0Hz to 1MHz (Fast-mode plus)

• 0Hz to 3.4MHz (High-speed mode)

●● Does not utilize I2C Clock Stretching

Operating in standard mode, fast mode, and fast-mode

plus does not require any special protocols. The main

consideration when changing the bus speed through

this range is the combination of the bus capacitance and

pullup resistors. Higher time constants created by the

bus capacitance and pullup resistance (C x R) slow the

bus operation. Therefore, when increasing bus speeds,

the pullup resistance must be decreased to maintain a

reasonable time constant. See the Pullup Resistor Sizing

www.maximintegrated.com

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

section of the I2C revision 3.0 specification for detailed

guidance on the pullup resistor selection. In general, for

bus capacitances of 200pF, a 100kHz bus needs 5.6kΩ

pullup resistors, a 400kHz bus needs about 1.5kΩ pullup

resistors, and a 1MHz bus needs 680Ω pullup resistors.

Note that the pullup resistor is dissipating power when the

open-drain bus is low. The lower the value of the pullup

resistor, the higher the power dissipation (V2/R).

Operating in high-speed mode requires some special considerations. For the full list of considerations, see the I2C

3.0 specification. The major considerations with respect to

the MAX77813 are:

●● I2C bus master use current source pullups to shorten

the signal rise times.

●● I2C slave must use a different set of input filters on

its SDA and SCL lines to accommodate for the higher

bus speed.

●● The communication protocols need to utilize the highspeed master code.

At power-up and after each STOP condition, the device

input filters are set for standard mode, fast mode, or

fast-mode plus (i.e., 0Hz to 1MHz). To switch the input

filters for high-speed mode, use the high-speed master

code protocols that are described in the Communication

Protocols section.

Communication Protocols

The device supports both writing and reading from its registers. The following sections show the I2C communication protocols for each functional block. The power block

uses the same communication protocols.

Maxim Integrated │ 21

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Writing to a Single Register

4) The master sends an 8-bit register pointer.

Figure 9 shows the protocol for the I2C master device to

write one byte of data to the device. This protocol is the

same as SMBus specification’s “Write Byte” protocol.

5) The slave acknowledges the register pointer.

6) The master sends a data byte.

7) The slave acknowledges the data byte. At the rising

edge of SCL, the data byte loads into its target register and the data becomes active.

The “Write Byte” protocol is as follows:

1) The master sends a START command (S).

2) The master sends the 7-bit slave address followed

by a write bit (R/nW = 0).

8) The master sends a STOP condition (P) or a REPEATED START condition (Sr). Issuing a P ensures

that the bus input filters are set for 1MHz or slower

operation. Issuing a REPEATED START (Sr) leaves

the bus input filters in their current state.

3) The addressed slave asserts an ACKNOWLEDGE

(A) by pulling SDA low.

LEGEND

MASTER TO

SLAVE

*P FORCES THE BUS FILTERS TO SWITCH

TO THEIR ≤1MHz MODE. Sr LEAVES THE

BUS FILTERS IN THEIR CURRENT STATE.

SLAVE TO

MASTER

1

7

1 1

8

1

8

S

SLAVE ADDRESS

0 A

REGISTER POINTER

A

DATA

R/nW

SDA

1

1

A P or Sr*

NUMBER

OF BITS

THE DATA IS LOADED INTO

THE TARGET REGISTER AND

BECOMES ACTIVE DURING

THIS RISING EDGE.

B1

B0

A

ACKNOWLEDGE

SCL

7

8

9

Figure 9. Writing to a Single Register with “Write Byte” Protocol

www.maximintegrated.com

Maxim Integrated │ 22

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Writing to Sequential Registers

5) The slave acknowledges the register pointer.

Figure 10 shows the protocol for writing to sequential

registers. This protocol is similar to the “Write Byte” protocol, except the master continues to write after it receives

the first byte of data. When the master is done writing, it

issues a STOP or REPEATED START.

6) The master sends a data byte.

7) The slave acknowledges the data byte. At the rising

edge of SCL, the data byte loads into its target register and the data becomes active.

8) Steps 6 to 7 are repeated as many times as the

master requires.

The “Writing to Sequential Registers” protocol is as follows:

1) The master sends a START command (S).

9) During the last acknowledge related clock pulse, the

slave issues an ACKNOWLEDGE (A).

2) The master sends the 7-bit slave address followed

by a write bit (R/nW = 0).

10) The master sends a STOP condition (P) or a REPEATED START condition (Sr). Issuing a P ensures

that the bus input filters are set for 1MHz or slower

operation. Issuing a REPEATED START (Sr) leaves

the bus input filters in their current state.

3) The addressed slave asserts an ACKNOWLEDGE

(A) by pulling SDA low.

4) The master sends an 8-bit register pointer.

LEGEND

MASTER TO SLAVE

*P FORCES THE BUS FILTERS TO SWITCH TO THEIR

≤1MHZ MODE. SR LEAVES THE BUS FILTERS IN

THEIR CURRENT STATE.

SLAVE TO MASTER

1

7

1 1

8

1

8

1

S

SLAVE ADDRESS

0 A

REGISTER POINTER X

A

DATA X

A

8

1

8

1

DATA X+1

A

DATA X+2

A

NUMBER

OF BITS

α

R/nW

NUMBER

OF BITS

α REGISTER POINTER = X + 2α

REGISTER POINTER = X + 1

8

1

8

1

1

DATA n-1

A

DATA n

A

P or Sr*

REGISTER POINTER = X + (N-2) α REGISTER POINTER = X + (N-1)

NUMBER

OF BITS

β

THE DATA IS LOADED INTO THE

TARGET REGISTER AND BECOMES

ACTIVE DURING THIS RISING

EDGE.

SDA

B1

B0

A

B9

ACKNOWLEDGE

SCL

7

8

9

DETAIL: α

1

THE DATA IS LOADED INTO THE

TARGET REGISTER AND BECOMES

ACTIVE DURING THIS RISING

EDGE.

SDA

B1

B0

A

ACKNOWLEDGE

SCL

7

8

9

DETAIL: β

Figure 10. Writing to Sequential Registers

www.maximintegrated.com

Maxim Integrated │ 23

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Reading from a Single Register

the slave that it wants more data – when the master has all

the data it requires, it issues a NOT-ACKNOWLEDGE (nA)

and a STOP (P) to end the transmission.

The I2C master device reads one byte of data to the

device. This protocol is the same as SMBus specification’s “Read Byte” protocol.

The “Continuous Read from Sequential Registers” protocol is as follows:

The “Read Byte” protocol is as follows:

1) The master sends a START command (S).

1) The master sends a START command (S).

2) The master sends the 7-bit slave address followed

by a write bit (R/nW = 0).

2) The master sends the 7-bit slave address followed

by a write bit (R/nW = 0).

3) The addressed slave asserts an ACKNOWLEDGE

(A) by pulling SDA low.

3) The addressed slave asserts an ACKNOWLEDGE

(A) by pulling SDA low.

4) The master sends an 8-bit register pointer.

4) The master sends an 8-bit register pointer.

5) The slave acknowledges the register pointer.

5) The slave acknowledges the register pointer.

6) The master sends a REPEATED START command

(Sr).

6) The master sends a REPEATED START command

(Sr).

7) The master sends the 7-bit slave address followed

by a read bit (R/nW = 1).

7) The master sends the 7-bit slave address followed

by a read bit (R/nW = 1).

8) The addressed slave asserts an ACKNOWLEDGE

(A) by pulling SDA low.

8) The addressed slave asserts an ACKNOWLEDGE

(A) by pulling SDA low.

9) The addressed slave places 8-bits of data on the bus

from the location specified by the register pointer.

9) The addressed slave places 8-bits of data on the bus

from the location specified by the register pointer.

10) The master issues an ACKNOWLEDGE (A) signaling

the slave that it wishes to receive more data.

10) The master issues a NOT-ACKNOWLEDGE (nA).

11) The master sends a STOP condition (P) or a REPEATED START condition (Sr). Issuing a P ensures

that the bus input filters are set for 1MHz or slower

operation. Issuing a REPEATED START (Sr) leaves

the bus input filters in their current state.

11) Steps 9 to 10 are repeated as many times as the

master requires. Following the last byte of data, the

master must issue a NOT-ACKNOWLEDGE (nA) to

signal that it wishes to stop receiving data.

12) The master sends a STOP condition (P) or a REPEATED START condition (Sr). Issuing a STOP (P)

ensures that the bus input filters are set for 1MHz or

slower operation. Issuing a REPEATED START (Sr)

leaves the bus input filters in their current state.

Reading from Sequential Registers

Figure 11 shows the protocol for reading from sequential

registers. This protocol is similar to the “Read Byte” protocol

except the master issues an ACKNOWLEDGE (A) to signal

*P FORCES THE BUS FILTERS TO SWITCH TO

THEIR ≤ 1MHz MODE. SR LEAVES THE BUS

FILTERS IN THEIR CURRENT STATE.

LEGEND

MASTER TO

SLAVE

1

7

S

SLAVE ADDRESS

R/

nW

SLAVE TO

MASTER

1 1

8

1 1

7

0 A

REGISTER POINTER X

A Sr

SLAVE ADDRESS

8

1

DATA X+1

A

Register Pointer = X + 1

8

DATA n-2

8

R/

nW

DATA X+2

1 1

8

1

1 A

DATA X

A

8

1

DATA X+3

A

1

A

Register Pointer = X + 2

1

A

Register Pointer =

X + (n-3)

8

DATA n-1

Register Pointer =

X + (n-2)

NUMBER

OF BITS

NUMBER

OF BITS

Register Pointer = X + 3

1

A

8

DATA n

Register Pointer =

X + (n-1)

1

1

nA

P or

Sr*

NUMBER

OF BITS

Figure 11. Reading Continuously from Sequential Registers

www.maximintegrated.com

Maxim Integrated │ 24

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Engaging HS-Mode for Operation

up to 3.4MHz

3) The master sends the 8-bit master code of

00001xxxb where xxxb are don’t care bits.

The “Engaging HS-Mode” protocol is as follows:

5) The master may now increase its bus speed up to

3.4MHz and issue any read/write operation.

Figure 12 shows the protocol for engaging HS-mode

operation. HS-mode operation allows for a bus operating

speed up to 3.4MHz.

1) Begin the protocol while operating at a bus speed of

1MHz or lower.

2) The master sends a START command (S).

4) The addressed slave issues a NOT-ACKNOWLEDGE (nA).

The master may continue to issue high-speed read/write

operations until a STOP (P) is issued. Issuing a STOP

(P) ensures that the bus input filters are set for 1MHz or

slower operation.

LEGEND

MASTER TO SLAVE

1

8

S

HS-MASTER CODE

SLAVE TO MASTER

1

1

nA Sr

ANY READ/WRITE PROTOCOL

Sr

FOLLOWED BY Sr

ANY READ/WRITE PROTOCOL

FOLLOWED BY Sr

FAST- MODE

Sr

ANY READ/WRITE PROTOCOL

P

HS-MODE

FAST-MODE

Figure 12. Engaging HS-Mode

Register Map

Register Reset Condition

Registers reset to their default values when either of the following conditions become true:

●● Undervoltage Lockout (VSYS < VUVLO_F)

●● Device Disabled (EN = logic low)

MAX77813 Registers

I2C Device Address: 0x18 (7-bit)

ADDRESS

NAME

ACCESS

0x00

DEVICE_ID

R

0x01

STATUS

R

0x02

CONFIG1

R/W

RESERVED RESERVED RU_SR

0x03

CONFIG2

R/W

RESERVED

0x04

VOUT

R/W

RESERVED

www.maximintegrated.com

MSB

LSB

RESET

OVP

OCP

—̶

0x00

AD

FPWM

0x0E

RESERVED

RESERVED

EN

TSHDN

RD_SR

POK

OVP_TH[1:0]

EN_PD POK_POL

VOUT[6:0]

RESERVED

0x70

varies

Maxim Integrated │ 25

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Register Details

DEVICE ID (0x00)

BIT

7

6

5

4

3

Field

RESERVED[7:0]

Reset

—

Access

2

1

0

Read Only

BITFIELD

BITS

RESERVED

DESCRIPTION

7:0

DECODE

Reserved. Bits for internal use only.

N/A

STATUS (0x01)

BIT

7

6

5

4

3

2

1

0

Field

RESERVED[3:0]

TSHDN

POK

OVP

OCP

Reset

0b0000

0b0

0b0

0b0

0b0

Read Only

Read Only

Read Only

Read Only

Read Only

Access

BITFIELD

RESERVED

BITS

3:0

DESCRIPTION

DECODE

Reserved. Reads are don’t care.

N/A

TSHDN

3

Thermal Shutdown Status

0 = Junction temperature OK (TJ < TSHDN)

1 = Thermal shutdown (TJ ≥ TSHDN)

POKn

2

Power-OK Status

0 = Output not OK (VOUT < 75% of target) or disabled.

1 = Output OK (VOUT > 80% of target)

OVP

1

Output Overvoltage Status

0 = Output OK (VOUT < the OVP threshold set by

OVP_TH[1:0]) or disabled.

1 = Output overvoltage. VOUT > the OVP threshold

set by OVP_TH[1:0].

OCP

0

Overcurrent Status

0 = Current OK

1 = Overcurrent

www.maximintegrated.com

Maxim Integrated │ 26

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

CONFIG1 (0x02)

BIT

7

6

5

4

3

2

1

0

Field

RESERVED

RU_SR

RD_SR

OVP_TH[1:0]

AD

FPWM

Reset

0b00

0b0

0b0

0b11

0b1

0b0

Read, Write

Read, Write

Read, Write

Read, Write

Read, Write

Read, Write

Access

BITFIELD

RESERVED

RU_SR

RD_SR

OVP_TH[1:0]

BITS

7:6

DESCRIPTION

DECODE

Reserved. Bit is a don’t care.

N/A

5

VOUT Rising Ramp Rate Control.

VOUT increases with this slope

whenever the output voltage target is

modified upwards while the converter is

enabled.

0 = +20mV/µs

1 = +40mV/µs

4

VOUT Falling Ramp Rate Control.

VOUT decreases with this slope

whenever the output voltage target

is modified downwards while the

converter is enabled.

0 = -5mV/µs

1 = -10mV/µs

VOUT Overvoltage Protection (OVP)

Threshold Control

00 = No OVP (protection disabled)

01 = 110% of VOUT target

10 = 115% of VOUT target

11 = 120% of VOUT target

3:2

AD

1

Output Active Discharge Resistor

Enable

0 = Disabled

1 = Enabled

FPWM

0

Converter Mode Control

0 = SKIP mode

1 = Forced PWM (FPWM) mode

www.maximintegrated.com

Maxim Integrated │ 27

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

CONFIG2 (0x03)

BIT

7

6

5

4

Field

RESERVED

BB_EN

EN_PD

POK_POL

RESERVED

Reset

0b0

0b1

0b1

0b1

0b0000

Read, Write

Read, Write

Read, Write

Read, Write

Read, Write

Access

BITFIELD

BITS

RESERVED

3

2

1

DESCRIPTION

7

DECODE

Reserved. Bit is a don’t care.

N/A

EN

6

Buck-boost output software enable

control. See Table 1.

While EN (pin) = logic low:

0 or 1 = Output disabled

While EN (pin = logic high:

0 = Output disabled

1 = Output enabled

PD

5

EN input pulldown resistor enable

control.

0 = Pulldown disabled

1 = Pulldown enabled

POK_POL

4

Power-OK (POK) output polarity

control.

0 = Active-low

1 = Active-high

3:0

Reserved. Bitfield is a don’t care.

N/A

RESERVED

0

VOUT (0x04)

BIT

7

6

5

4

3

2

1

Field

RESERVED

VOUT[6:0]

Reset

0b0

Varies (See the Ordering Information table)

Read, Write

Read, Write

Access

BITFIELD

RESERVED

VOUT

www.maximintegrated.com

BITS

7

6:0

DESCRIPTION

Reserved. Bit is a don’t care.

Output Voltage Control.

Sets the VOUT target. Configurable

in 20mV per LSB from 0x00

(2.60V) to 0x7F (5.14V).

The default value of this register is

preset. See the Ordering Information

table. Overwriting the default value

sets a new target output voltage.

0

DECODE

N/A

0x00 = 2.60V

0x01 = 2.62V

0x02 = 2.64V

…

0x23 = 3.30V

…

0x28 = 3.40V

…

0x7E = 4.12V

0x7F = 5.14V

Maxim Integrated │ 28

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Ordering Information

PART

DEFAULT

VOUT

PIN-PACKAGE

MAX77813EWP33+T

3.3V

20-Bump (5 x 4)

0.4mm Pitch

MAX77813EWP+T

3.4V

20-Bump (5 x 4)

0.4mm Pitch

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

www.maximintegrated.com

Maxim Integrated │ 29

�MAX77813

5.5V Input, 2A, High-Efficiency

Buck-Boost Converter

Revision History

REVISION

NUMBER

REVISION

DATE

0

10/18

Initial release

1

1/19

Grammar and content fixes

3/19

Updated the Electrical Characteristics table, Bump Description table, and Figure 1;

added the following sections: Burst Mode (Enhanced Load Response), Output Voltage

Selection and Slew Rate Control, Output Overvoltage Protection (OVP), Thermal

Shutdown, I2C Serial Interface, and Applications Information, updated Register Details

table

2

PAGES

CHANGED

DESCRIPTION

—

1–27

4, 12, 13,

16–18, 26

For pricing, delivery, and ordering information, please visit Maxim Integrated’s online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses

are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits)

shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.

© 2019 Maxim Integrated Products, Inc. │ 30

�